Изобретение относится к радио- измерительной технике и может быть использовано для оценки параметров гармонического сигнала - фазы и час тоты п шумах.

Цель изобретения - повышение точ- ности измерения фазы сигнала и рас ширение диапазона рабочих частот

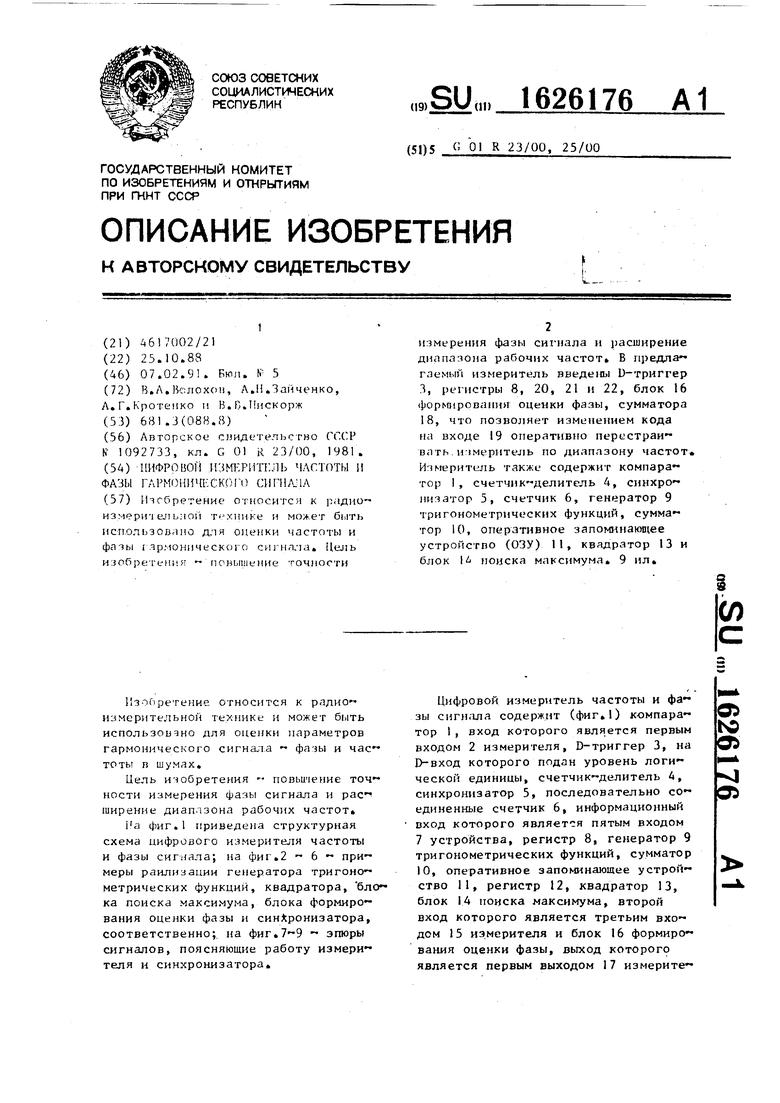

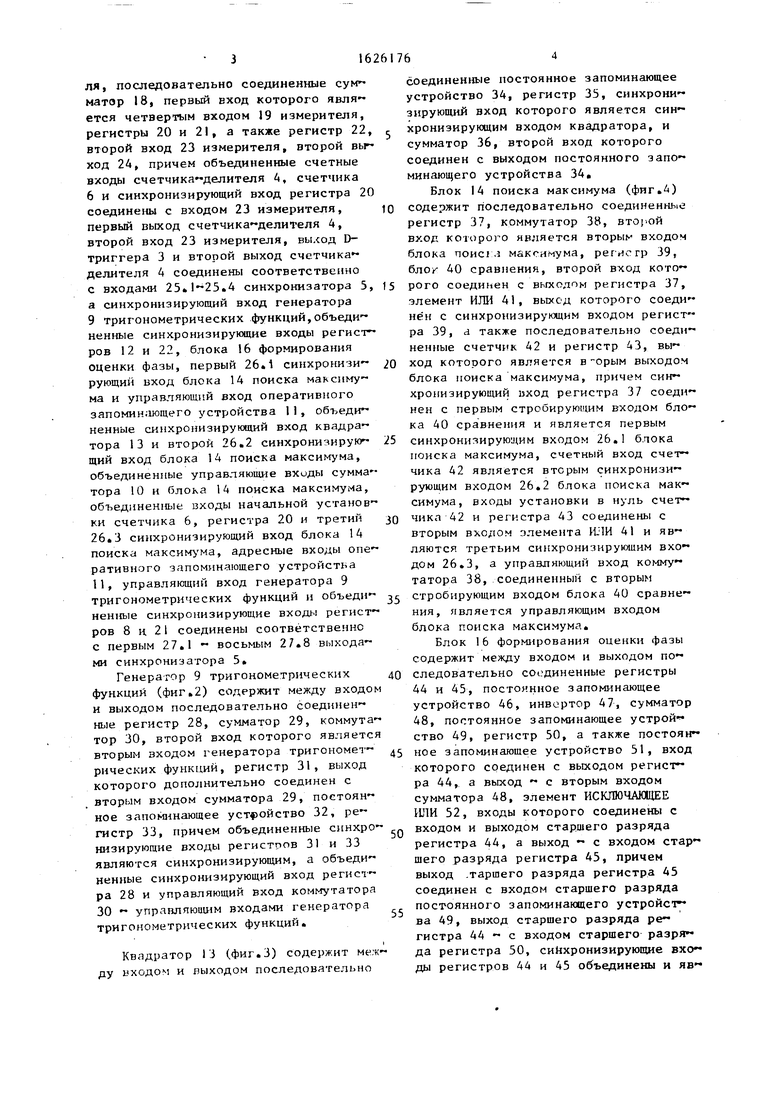

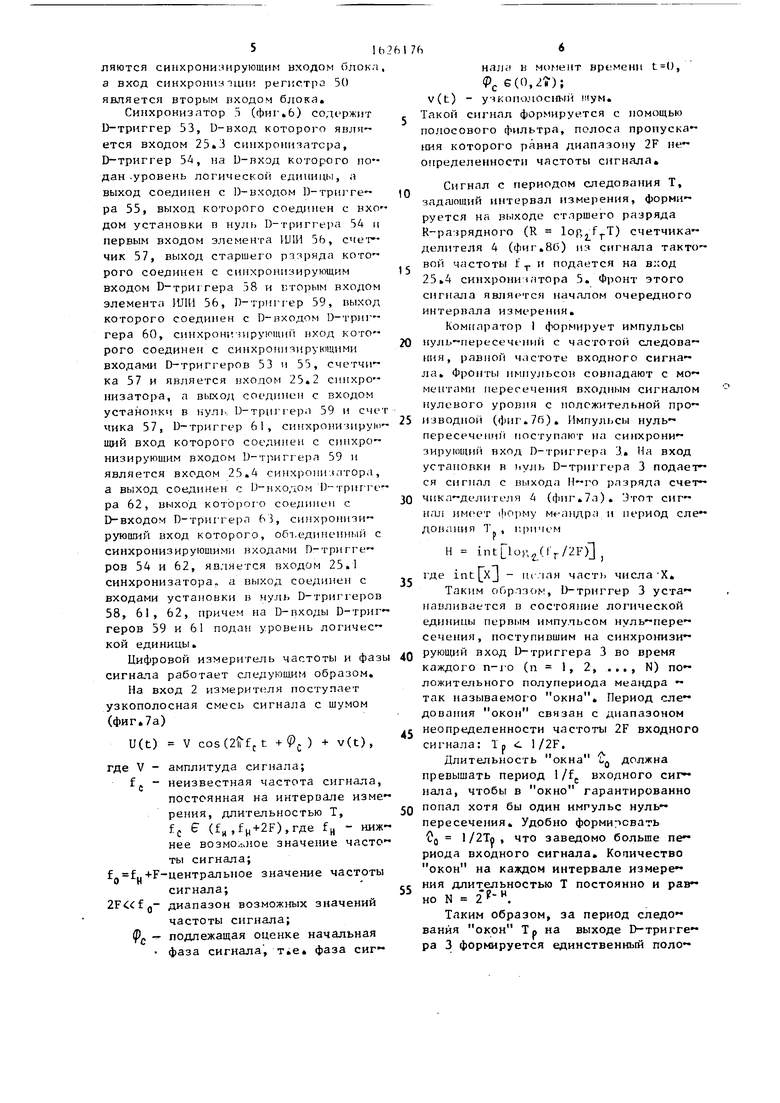

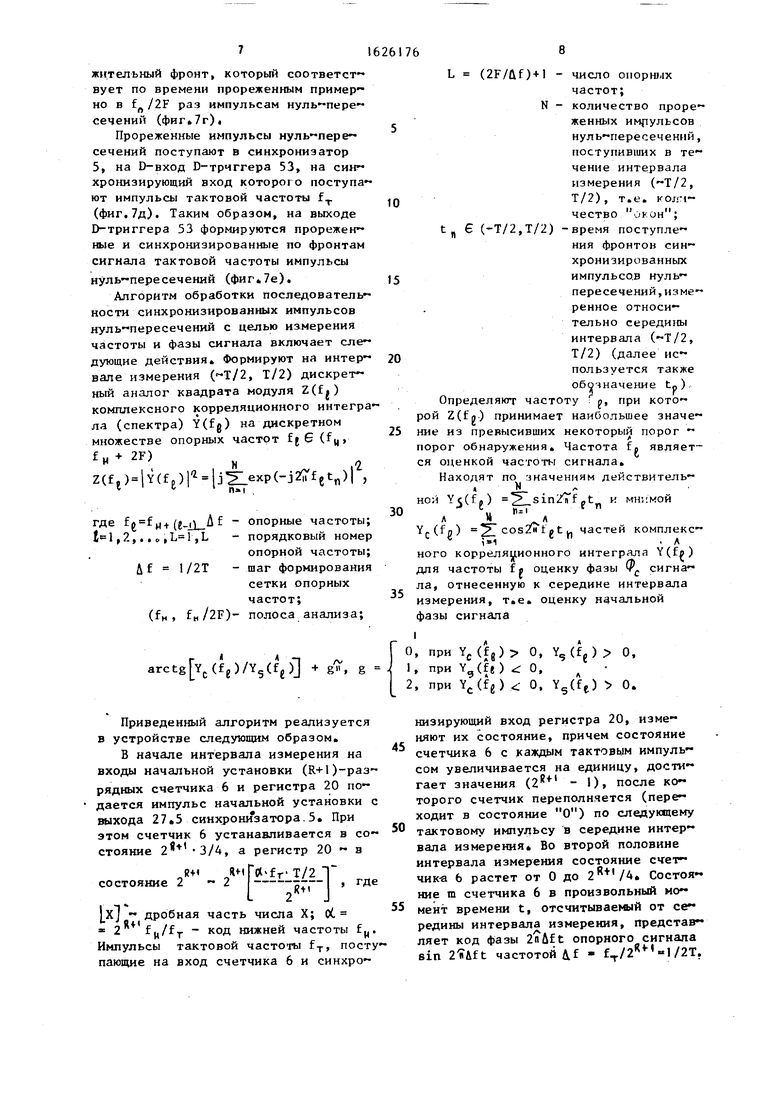

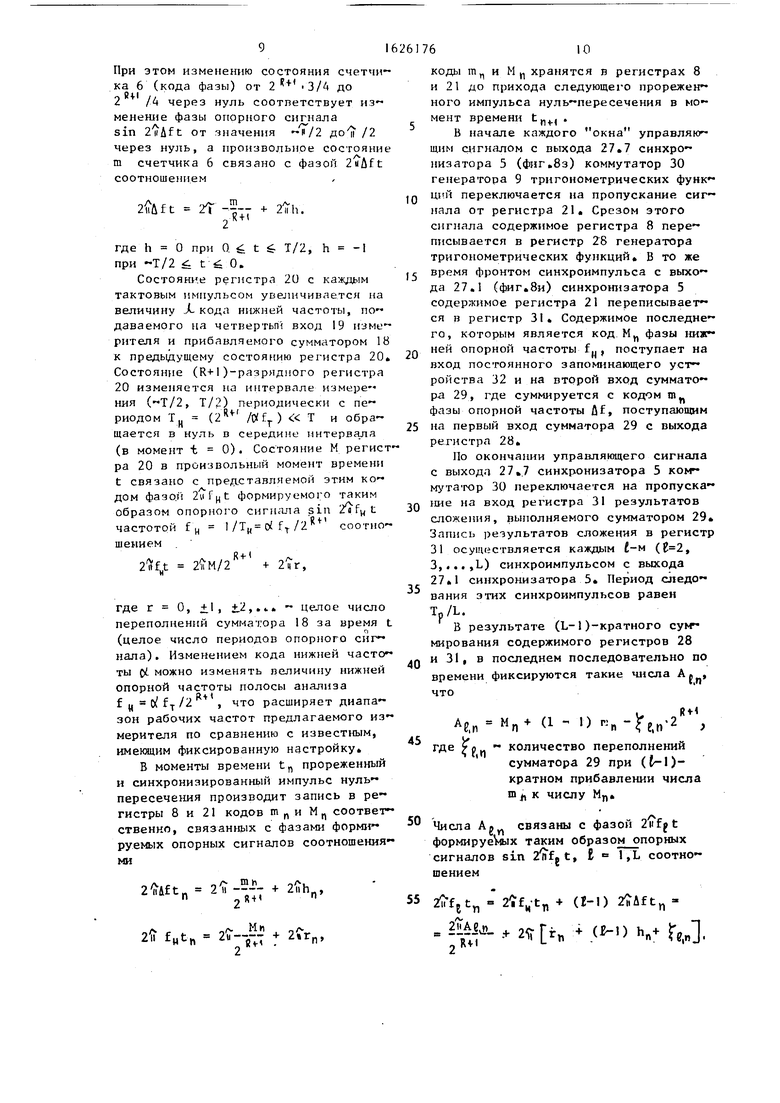

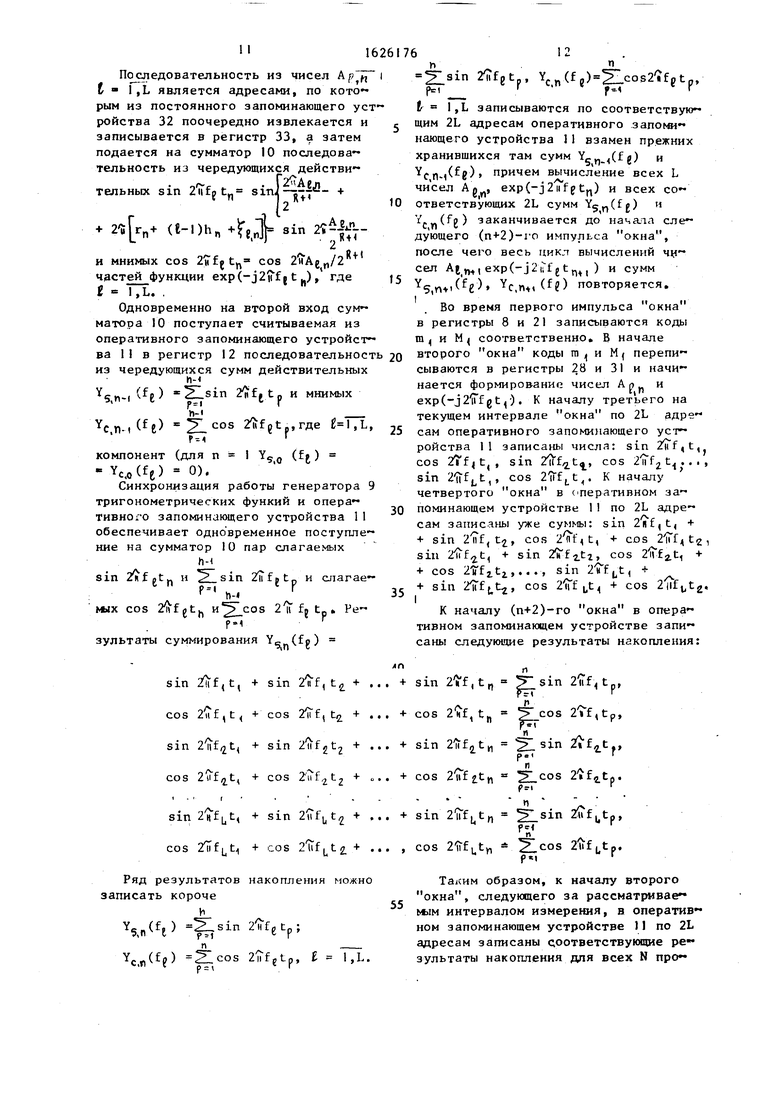

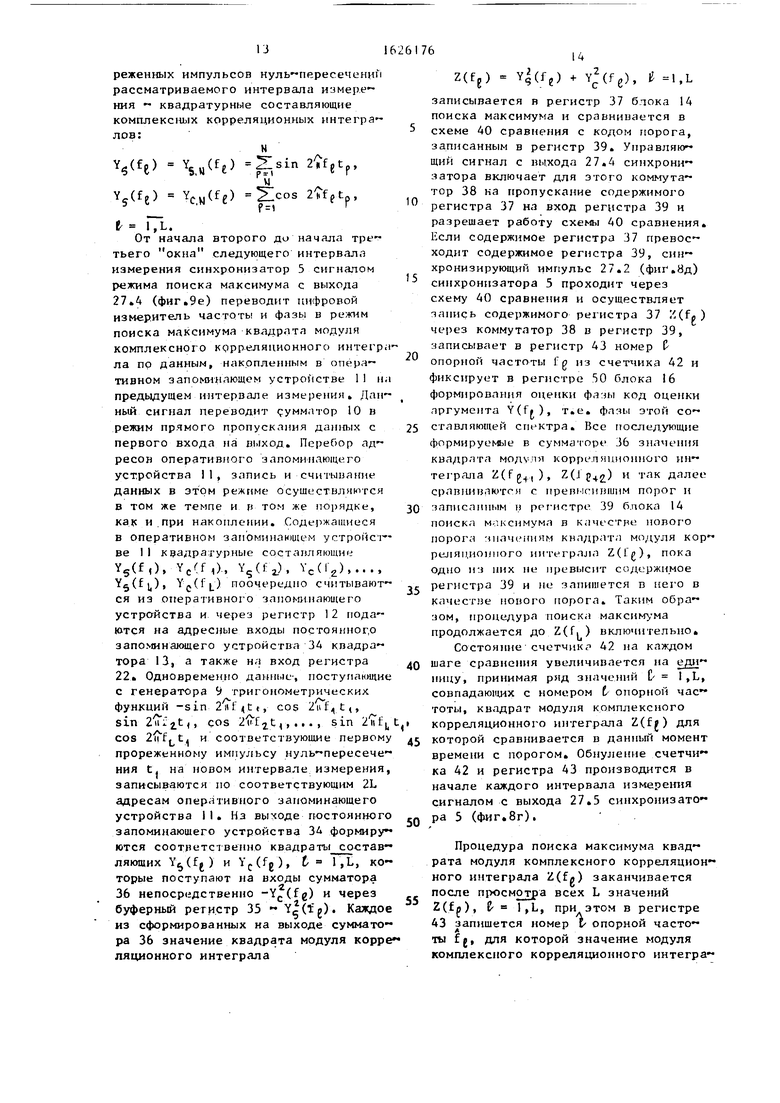

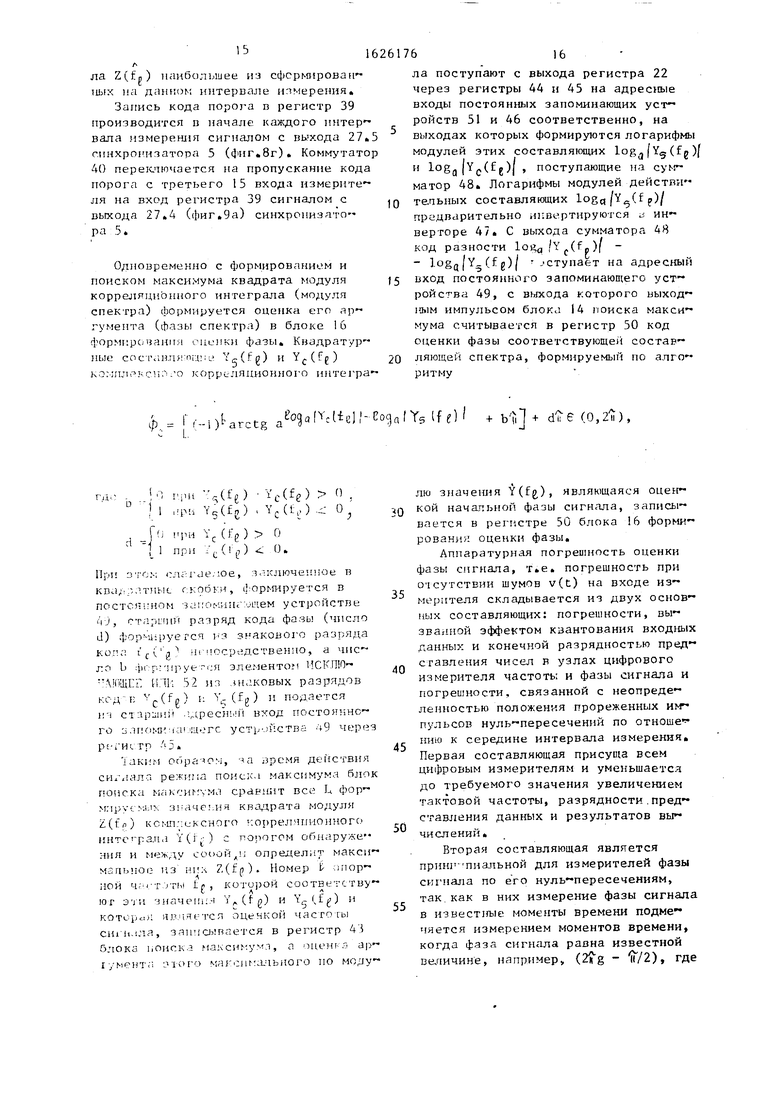

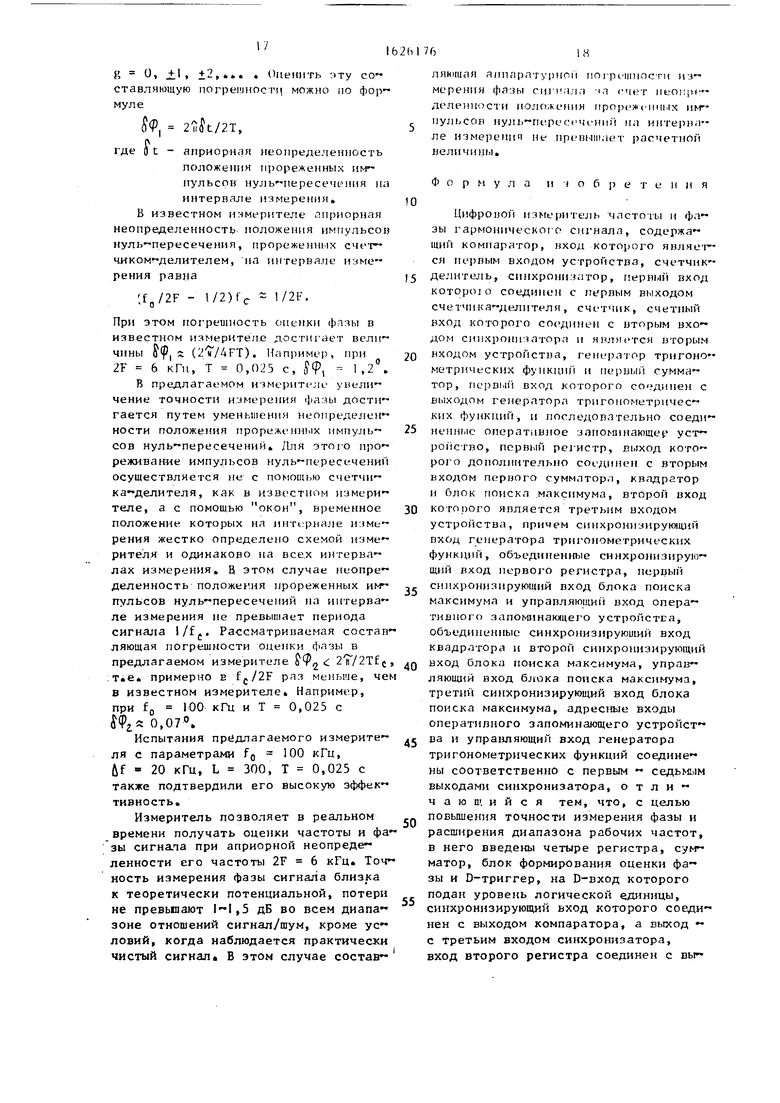

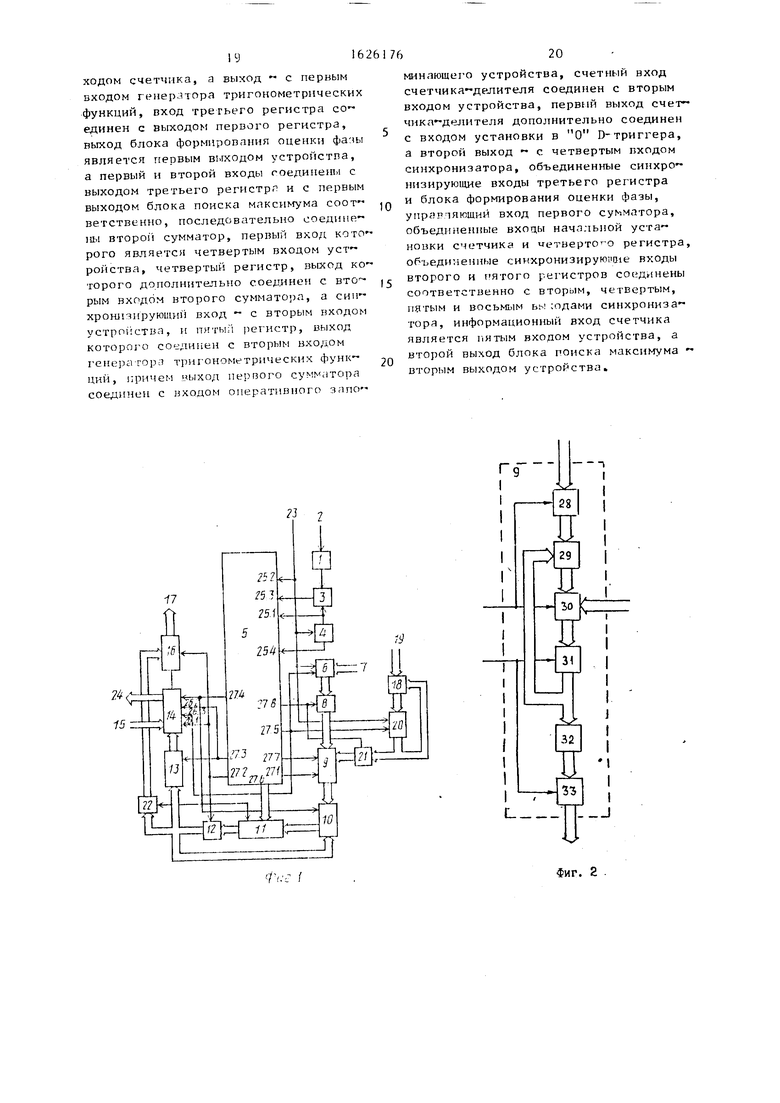

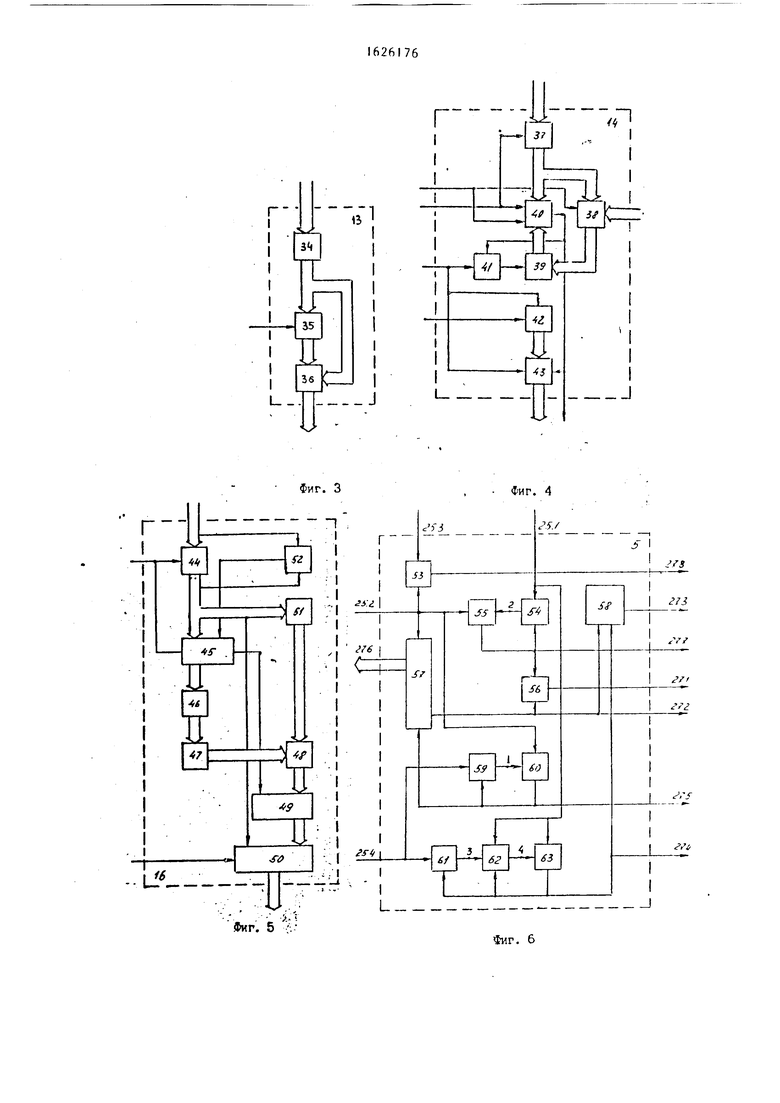

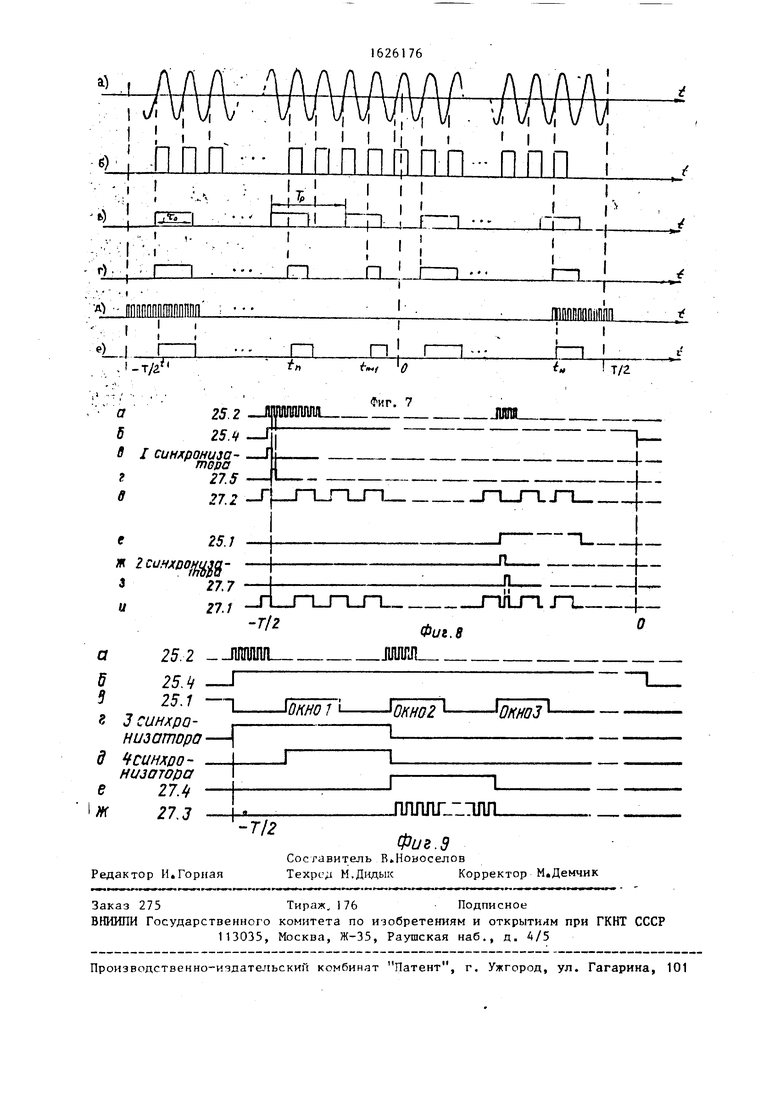

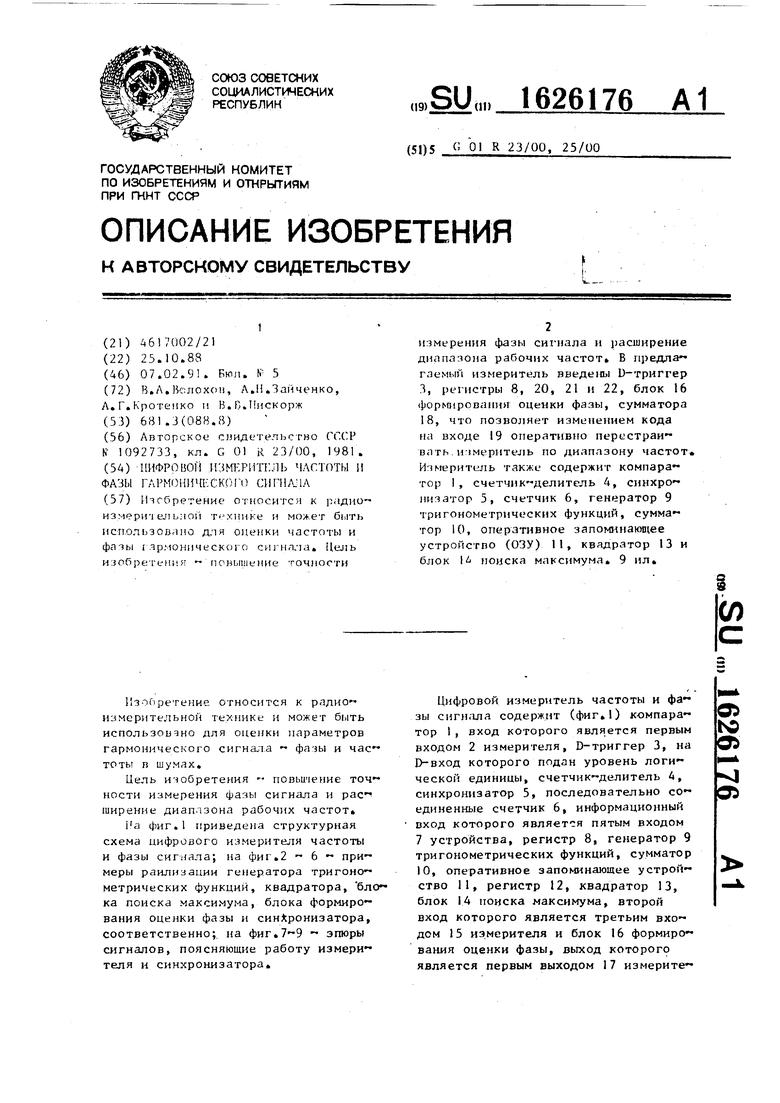

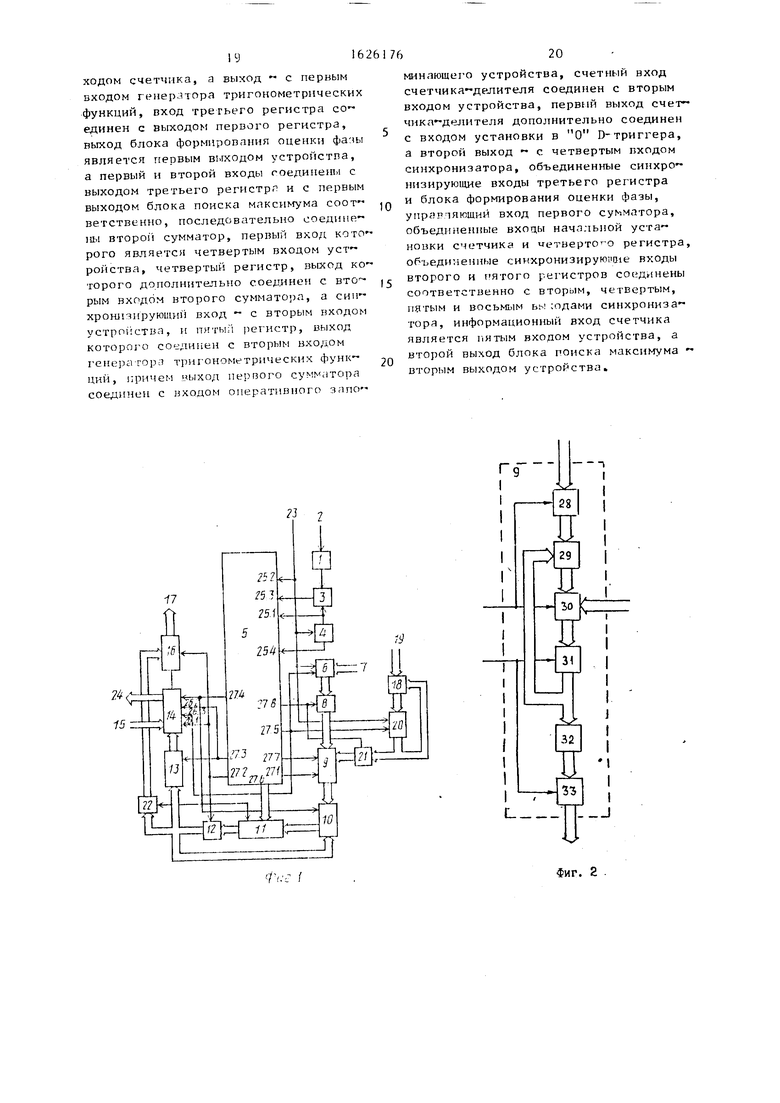

1 а фиг.1 приведена структурная схема цифрового измерителя частоты и фазы сигнала; на фиг.2 6 - примеры раилизацин генератора тригонометрических функции, квадратора, блока поиска максимума, блока формирования оценки фазы и синхронизатора, соответственно; на фиг.7-9 - эпюры сигналов, поясняющие работу измерителя и синхронизатора

Цифровой измеритель частоты и фазы сигнала содержит () компаратор 1, вход которого является первым входом 2 измерителя, D-триггер З, на D-вход которого подан уровень логической единицы, счетчик-делитель 4, синхронизатор 5, последовательно соединенные счетчик 6, информационный вход которого является пятым входом 7 устройства, регистр 8, генератор 9 тригонометрических функций, сумматор 10, оперативное запоминающее устройство 11, регистр 12, квадратор 13, блок 14 поиска максимума, второй вход которого является третьим входом 15 измерителя и блок 16 формирования оценки фазы, выход которого является первым выходом 17 измерителя, последовательно соединенные сум- матор 18, первый вход которого явля- ется четвертым входом 19 измерителя, регистры 20 и 21, а также регистр 22, второй вход 23 измерителя, второй выход 24, причем объединенные счетные входы счетчика-делителя 4, счетчика 6 и синхронизирующий вход регистра 20 соединены с входом 23 измерителя, первый выход счетчика-делителя 4, второй вход 23 измерителя, выход D- триггера 3 и второй выход счетчика- делителя 4 соединены соответственно с входами 25.1-25.4 синхронизатора 5, а синхронизирующий вход генератора 9 тригонометрических функций,объеди- ненные синхронизирующие входы регист- ров 12 и 22, блока 16 формирования оценки фазы, первый 26.1 синхронизи рующии вход блока 14 поиска максимума и управляющий вход оперативного запоминающего устройства 11, объединенные синхронизирующий вход квадратора 13 и второй 26.2 синхронизирую- щий вход блока 14 поиска максимума, объединенные управляющие вхиды сумматора 10 и блока 14 поиска максимума, объединенные входы начальной установки счетчика 6, регистра 20 и третий 26.3 синхронизирующий вход блока 14 поиска максимума, адресные входы оперативного запоминающего устройстьа 11, управляющий вход генератора 9 тригонометрических функций и объеди- ненные синхронизирующие входы регистров 8 и 21 соединены соответственно с первым 27.1 - восьмым 27.8 выходами синхронизатора 5

Генератор 9 тригонометрических функций (фиг.2) содержит между входом и выходом последовательно соединенные регистр 28, сумматор 29, коммутатор 30, второй вход которого является вторым входом генератора тригономет- рнческих функций, регистр 31, выход которого дополнительно соединен с вторым входом сумматора 29, постоянное запоминающее устройство 32, регистр 33, причем объединенные синхро- визирующие входы регистпов 31 и 33 являются синхронизирующим, а объединенные синхронизирующий вход регистра 28 и управляющий вход коммутатора 30 - управляющим входами генератора тригонометрических функций.

1

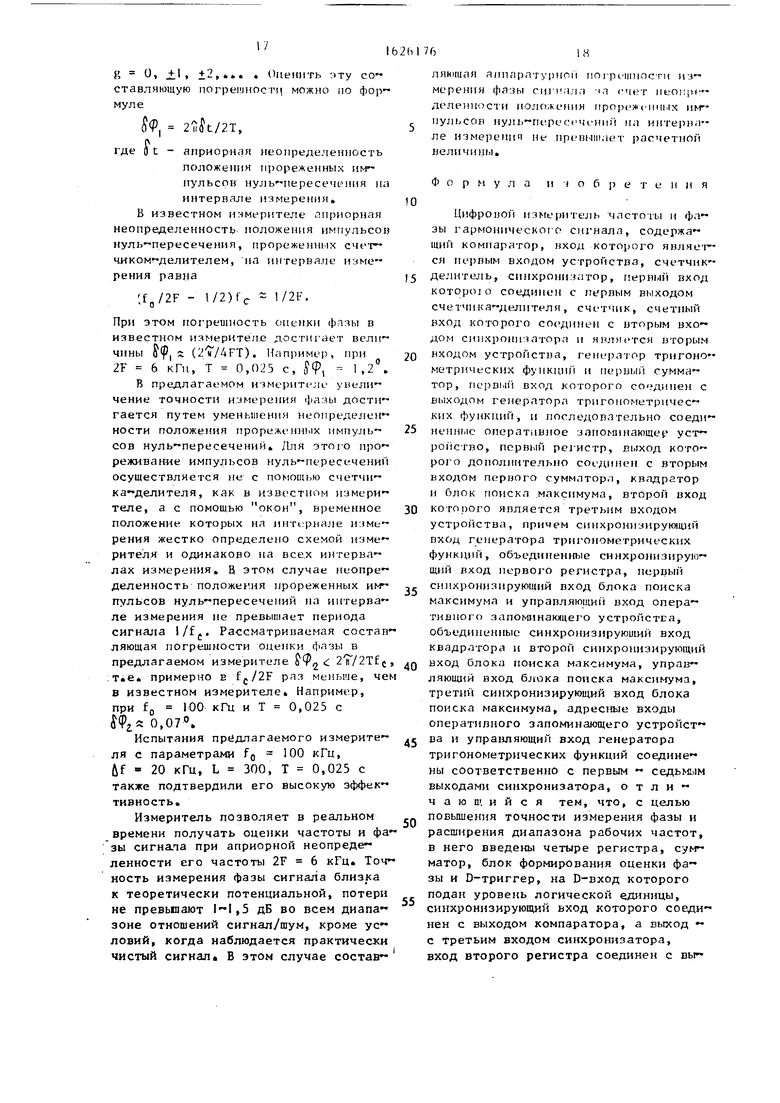

Квадратор 13 (фиг.З) содержит между входом и выходом последовательно

соединенные постоянное запоминающее устройство 34, регистр 35, синхронизирующий вход которого является синхронизирующим входом квадратора, и сумматор 36, второй вход которого соединен с выходом постоянного запоминающего устройства 34.

Блок 14 поиска максимума (фиг.4) содержит последовательно соединенные регистр 37, коммутатор 38, второй вход которого является вторым входом блока максимума, регистр 39, бло 40 сравнения, второй вход которого соединен с выходом регистра 37, элемент ИЛИ 41, выход которого соединён с синхронизирующим входом регистра 39 , а также последовательно соединенные счетчик 42 и регистр 43, выход которого является в -орым выходом блока поиска максимума, причем синхронизирующий вход регистра 37 соединен с первым стробирующим входом блока 40 сравнения и является первым синхронизирующим входом 26.1 бпока поиска максимума, счетный вход счетчика 42 является вторым синхронизирующим входом 26.2 бпока поиска максимума, входы установки в нуль счетчика 42 и регистра 43 соединены с вторым входом элемента ИЛИ 41 и являются третьим синхронизирующим входом 26.3, а управляющий вход коммутатора 38, соединенный с вторым стробирующим входом блока 40 сравнения, является управляющим входом блока поиска максимума.

Блок 16 формирования оценки фазы содержит между входом и выходом последовательно соединенные регистры 44 и 45, постоянное запоминающее устройство 46, инвертор 47, сумматор 48, постоянное запоминающее устройство 49, регистр 50, а также постоянное запоминающее устройство 51, вход которого соединен с выходом регистра 44, а выход - с вторым входом сумматора 48, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 52, входы которого соединены с входом и выходом старшего разряда регистра 44, а выход - с входом старшего разряда регистра 45, причем выход .таршего разряда регистра 45 соединен с входом старшего разряда постоянного запоминающего устройства 49, выход старшего разряда регистра 44 - с входом старшего разряда регистра 50, сийхронизирующие входы регистров 44 и 45 объединены и яв-

ляются синхронизирующим входом блока а вход синхроннатцни регистра 50 является вторым входом блока.

Синхронизатор 5 (фиг.6) содержит D-триггер 53, D-вход которого явлн- ется входом 25.J синхронизатора, D-триггер 54, на D-вход которого подан -уровень логической единицы, а выход соединен с 1)-входом D-трнгге- ра 55, выход которого соединен с вхо дом установки в нуль 1)-трнггера 54 и первым входом элемента Ш1И 56, счет- чик 57, выход старшего рччряда кото- рого соединен с синхронизирующим входом D-тршгера 58 и вторым входом элемента Ш1И 56, D-трмггер 59, выход которого соединен с D-входом D-триг- гера 60, синхрони шрующин вход которого соединен с синхронизирующими входами D-триггеров 53 ч 55, счетчика 57 и является вхоаом 25.2 синхронизатора, а выход соединен с входом установки в нуль D-триггера 59 и сче чика 57, D-триггер 61, синхронипирующий вход которого соединен с синхронизирующим входом D-триггера 59 и является входом 25.4 синхрони«атора, а выход соединен с D-входом D-триггера 62, выход которого соединен с D-входом D-триггера 63, синхронизирующий вход которого, объединенный с синхронизирующими входами П-тригге- ров 54 и 62, является входом 25.1 синхронизатора, а выход соединен с входами установки в нуль D-триггеров 58, 61, 62, причем на D-пходы D-триггеров 59 и 61 подан уровень логической единицы.

Цифровой измеритель частоты и фаз сигнала работает следующим образом.

На вход 2 измерителя поступает узкополосная смесь сигнала с шумом ()

U(t) V cos(2iTfct +ФС) + v(t),

где V - амплитуда сигнала;

fc - неизвестная частота сигнала, постоянная на интервале измерения, длительностью Т, fc е (Ј„,Јн+2Р),где Ј„ - нижнее возможное значение частоты сигнала; f f +Г-центральное значение частоты

сигнала; 2F«ffl- диапазон возможных значений

частоты сигнала;

РС - подлежащая оценке начальная фаза сигнала, т.е. фаза сиг

нал.;1 в момент времени , РС 6(0,2Г);

v(t) - учкополоснын шум. Такой сигнал формируется с помощью полосового фильтра, полоса пропускания которого равна диапазону 2F неопределенности частоты сигнала

Сигнал с периодом следования Т, задающий интервал измерения, формируется на выходе старшего разряда R-paзрядного (R log,frT) счетчика- делителя 4 (фиг.86) из сигнала такто-

вой частоты Ј т и подается на в::од 25.4 синхрони )атора 5. Фронт этого сигнала является началом очередного интервала измерения.

Компаратор 1 формирует импульсы

нуль-пересечений с частотой следования, равной частоте входного сигнала. Фронты импульсов совпадают с моментами пересечения входным сигналом нулевого уровня с положительной про-

изводнои (фиг.76). Импульсы нуль- пересечении поступают на синхронизирующий вход D-триггера З. На вход установки в нуль D-триггера З подается сигнал с выхода И-го разряда счет-

чика-дели геля 4 (). 3тот сигнал имеет форму меандра и период следования Т , причем

Н int L0 ; nr/2F) f

где - не 1ая часть числа-X.

Таким оОрчюм, D-триггер 3 устанавливается в состояние логической единицы первым импупьсом нуль-пересечения, поступившим на сннхронизи-

рующий вход D-триггера З во время каждого n-го (п 1, 2N) положительного полупериода меандра - так называемого окна. Период следования окон связан с диапазоном

неопределенности частоты 2F входного сигнала: 1 р . 1 /2F.

Длительность окна Јfl должна превышать период 1/fc входного сигнала, чтобы в окно гарантированно

попал хотя бы один импульс нуль- пересечения. Удобно формировать С0 1/2То, что заведомо больше периода входного сигнала. Копичество окон на каждом интервале измере-

ния длительностью Т постоянно и рав-

но N .

Таким образом, за период следования окон Тр на выходе D-тригге- ра 3 формируется единственный поло-

71

жнтельный фронт, который соответствует по времени прореженным пример но в fft/2F раз импульсам нуль-пере- сечении (),

Прореженные импульсы нуль-пересечений поступают в синхронизатор 5, на D-вход D-трчггера 53, на синхронизирующий вход которого поступают импульсы тактовой частоты fT (фиг.7д). Таким образом, на выходе D-триггера 53 формируются прореженные и синхронизированные по фронтам сигнала тактовой частоты импульсы нуль-пересечений ().

Алгоритм обработки последовательности синхронизированных импульсов нуль-пересечений с целью измерения частоты и фазы сигнала включает следующие действия4 Формируют на интервале измерения (Т/2, Т/2) дискретный аналог квадрата модуля Z(f) комплексного корреляционного интеграла (спектра) Y(fg) на дискретном множестве опорных частот fj6 (fM, f H -t- 2F)

Z(f.HY(fe)| ()|,

v n,

где f ц+( f ,2,..„,,L -

ДЈ 1/2Т - (гн fи/2F)-

0

6176

5

0

5

В

L (2F/uf)+l - число опорных

частот;

N - количество прореженных импульсов нуль-пересечений, поступивших в течение интервала измерения (-Т/2, Т/2), т.е. колч- чество

tn € (-T/2,T/2) -время поступления фронтов синхронизированныхимпульсов нуль- пере сечений, из меренное относительно середины интервала (-Т/2, Т/2) (далее используется также обозначение t«)

Определяют частоту гр, при которой Z(fn) принимает наибольшее значение из превысивших некоторый порог - порог обнаружения. Частота f являет0

5

ся оценкой частоты сигнала.

Находят по значениям действитель-

ной Yc(f.) sinZ7fet и мнимой и

AН..А

Vf« 5 osZ7t

- д

ного корреляционного интеграла Y(fp) для частоты fe оценку фазы ™с сигнала, отнесенную к середине интервала

eLn

gt частей комплексизмерения, т.е. фазы сигнала I

оценку начальной

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой обнаружитель-измеритель частоты | 1988 |

|

SU1597760A2 |

| Цифровой обнаружитель-измеритель частоты | 1986 |

|

SU1370584A2 |

| Устройство для автоподстройки частоты и цифровой обнаружитель-измеритель частоты | 1982 |

|

SU1092733A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Измеритель коэффициента шума | 1988 |

|

SU1524014A1 |

| Устройство для взвешивания движущихся объектов | 1990 |

|

SU1789877A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ЧАСТОТЫ И ВРЕМЕННОЙ ЗАДЕРЖКИ РАДИОСИГНАЛА | 1992 |

|

RU2048683C1 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

Изсбрртение относится к радио™ измррн 1 ель.юн технике и быть использовано для оценки частоты и фаты г чрмоническсн о cm нлла. Цель изобрегениг - повышение точности измерения фазы сигнала и расширение диапазона рабочих частот В предла- гземый измеритель введены U-триггер Т, регистры 8, 20, 21 и 22, блок 16 формирования оценки фазы, сумматора 18, что позволяет изменением кода на входе 19 оперативно перестраи- вать измеритель по диапазону частот Измеритель также содержит компаратор 1, счетчнк-делитель 4, сннхро- низатор 5, счетчик 6, генератор 9 тригонометрических функций, сумма - тор 10, оперативное запоминакэдее устройство (ОЗУ) 11, квадратор 13 и блок 14 поиска максимума. 9 ил

r iд -. 0, при Yc(fg) 0, Y,(f.) О,

arctg Yc(fg)/Yg(fЈ)J + gtt, g 1 1, при Yg(fj) 0.

2, при Yc(fg) c- 0, Ys(fe) 0.

Приведенный алгоритм реализуется в устройстве следующим образом.

В начале интервала измерения на входы начальной установки (R+l)-paa- рядных счетчика 6 и регистра 20 подается импульс начальной установки с выхода синхронизатора.5. При этом счетчик 6 устанавливается в со- -3/4, а регистр 20 - в

стояние

состояние 2

R+

9

н

fd-fr-

где

- дробная часть числа X; 0(,

,R+

2 код нижней частоты fH. Импульсы тактовой частоты fT, поступающие на вход счетчика 6 и синхро

45

50

55

низирующий вход регистра 20, изменяют их состояние, причем состояние счетчика 6 с каждым тактовым импульсом увеличивается на единицу, достигает значения (2Rtl - 1), после которого счетчик переполняется (переходит в состояние О) по следующему тактовому импульсу в середине интервала измерения Во второй половине интервала измерения состояние счет- чик-а 6 растет от 0 до Состоя- ние m счетчика 6 в произвольный мо мент времени t, отсчитываемый от се редины интервала измерения, представ ляет код фазы 2nuft опорного сигнала sin 2f&ft частотой Ь. f - «1 /2Т.

При этом изменению состояния счетчика 6 (кода фазы) от (-3/4 до

2 к / / /ч через нуль соотпетствует изменение фазы опорного сигнала sin от значения -7/2 до н /2 через нуль, а произвольное состояние m счетчика 6 связано с фазой 27uft соотношением

2faf t 2Т -2 + 27и.

где h 0 при 0 Ј t Ј Т/2, h -I при -Т/2 t 6 0.

Состояние регистра 20 с каждым тактовым импульсом увеличивается на величину X кода нижней частоты, подаваемого на четвертый вход 19 измерителя и прибавляемого сумматором 18 к предыдущему состоянию регистра 20 Состояние (R-H )-разрядного регистра 20 изменяется на интервале измерения (-Т/2, Т/2) периодически с периодом Тн (2RV( /tffr) « Т и обращается в нуль в середине интервала (в момент t 0). Состояние М регист ра 20 в произвольный момент времени t связано с представляемой этим кодом фазой формируемого таким образом опорного сигнала sin 2e fH t частотой fH ( fT /2Rv соотношением

R4- (

2fiM/2 + 27r,

где г 0, il , Ј2,. 4. - целое число переполнений сумматора 18 за время t (целое число периодов опорного сигнала) . Изменением кода нижней частоты можно изменять величину нижней опорной частоты полосы анализа fи tffT/2 , что расширяет диапазон рабочих частот предлагаемого измерителя по сравнению с известным, имеющим фиксированную настройку

В моменты времени tn прореженный и синхронизированный импульс нуль- пересечения производит запись в регистры 8 и 21 кодов m n и Мп соответственно, связанных с фазами формируемых опорных сигналов соотношения ми

2fcftn- + 2fihn,

2fi fHtn - 2Г-Ј + ,

0

5

5

0

5

0

5

0

коды mn и Мп хранятся в регистрах 8 и 21 до прихода следующего прореженного импульса нуль-пересечения в момент времени tnf, .

В начале каждого окна управляющим сигналом с выхода 27.7 синхронизатора 5 () коммутатор 30 генератова 9 тригонометрических функ цпй переключается на пропускание сигнала от регистра 21. Срезом этого сигнала содержимое регистра 8 переписывается в регистр 28 генератора тригонометрических функций. В то же время фронтом синхроимпульса с выхода 27.1 (фиг.Зи) синхронизатора 5 содержимое регистра 21 переписывается в регистр 31. Содержимое последнего, которым является код Мп фазы нижней опорной частоты f.., поступает на вход постоянного запоминающего устройства 32 и на второй вход сумматора 29, где суммируется с кодом mn фазы опорной частоты ДЈ, поступающим на первый вход сумматора 29 с выхода регистра 28

По окончании управляющего сигнала с выхода синхронизатора 5 коммутатор 30 переключается на пропускание на вход регистра 31 результатов сложения, выполняемого сумматором 29. Запись результатов сложения в регистр 31 осуществляется каждым Ј-м (, 3,...,L) синхроимпульсом с выхода 27.1 синхронизатора 5. Период следования этих синхроимпульсов равен

Tp/L.

В результате (L-1)-кратного суммирования содержимого регистров 28 и 31, в последнем последовательно по времени фиксируются такие числа А. , что

R+ 4

Ае,п мп+ - -Је,п-2 ,

где fn - количество переполнений сумматора 29 при (t-1)- кратном прибавлении числа шл к числу Мл.

Числа Agn связаны с фазой 2nfpt формируеУых таким образом опорных сигналов sin 2 n fjt, I 1,L соотношением

55

2toetn 2 fM-tn + U-O 27Aftn

& к С

г„ +.(«-) Ч Гв,п.

Последовательность из чисел АР , i

« f

I m 1,L является адресами, по которым из постоянного запоминающего устройства 32 поочередно извлекается и записывается в регистр 33, а затем подается на сумматор 10 последовательность из чередующихся действительных sin 2irfjtn si.ru-«;, +

+ (t-l)hn 4j sin i |

и мнимых cos 2 iTf j tn cos 2иАЈг,/2 частей функции exp(-j2|Tf«t J/ где « - 771. .

Одновременно на второй вход сумматора 10 поступает считываемая из оперативного запоминающего устройст-

sin

27fe

n

Ycn(fe)21cos2 fgtp, Mr

10

8Lp c.

fr I,L записываются по соответствую- 5 щим 2L адресам оперативного запоминающего устройства 11 взамен прежних хранившихся там сумм (fg) и YenH(fj), причем вычисление всех L чисел Agn, ехр() и всех соответствующих 2L сумм Y5n(fЈ) и YC (fg) заканчивается до начала следующего (п+2)-го импульса окна, после чего весь цикл вычислений чи- сел Aj)m, exp(-j2irfettH, ) и сумм 15 Y5,mi( fe) YC,TH. (f) повторяется.

Во время первого импульса окна в регистры 8 и 21 записываются коды m ,, и М соответственно. В начале

ва 11 в регистр 12 последовательность 20 второго окна коды га и М{ перепииз чередующихся сумм действительных и-

4n-,(fe

W

sin

и мнимых

fc.n-|(fe 21 cos 2/&fetp,rfle ,L

rtf

1 Y

s,o

(ff)

компонент (для п « (fe) 0).

Синхронизация работы генератора 9 тригонометрических функий и оперативного запоминающего устройства 11 обеспечивает одновременное поступление на сумматор 10 пар слагаемых

И-( sin и sin и слагавеЧ н

рч

мых cos

2frf

h-«

:etp

еЧ и

cos 2 н f,

e tp

зультаты суммирования Y (fg)

сываются в регистры 28 и 31 и начинается формирование чисел А п и exp(-j2irf g t -). К началу третьего на текущем интервале окна по 2L адре25 сам оперативного запоминающего устройства 11 записаны числа: sin ,t, cos ), sin 2/i( f/it(l, cos 2lTf2 t .. , sin 2fi fLt,, cos 2frfLt. К началу четвертого окна в оперативном за30 поминающем устройстве 1 по 2L адресам записаны уже суммы: sin 2nf,t4 + + sin 27f(t2, cos t, + cos 2lTf4 tg i sin , + sin , cos 21ГЈгЦ + -t- cos 21Tf2.t1,..., sin , +

35 + sin , cos 2lTf + cos 2nft,tz.

Ре-к началу (п+2)-го окна в оперативном запоминающем устройстве записаны следующие результаты накопления:

11

2fif, t, + sin f, tu + ... + sin 2/iTf, t „ lsin cp

2 нЈ,С( + cos 2/iTf, t2 + ... + cos Zftf, tn LCOS ,tp,

и

2/ii f/2t, + sin 2 tif2t2 + ... + sin 2/iifatn sin 2«fit,

n Zfaflt, + cos + o.. + cos S.cos .

, . . .-- „ . -

2/« flat, + sin + ... + sin 2lTfL|tn 2L.sin ,

n1

cos 2/iffljt1 + cos 2

Uf.tfc

Ряд результатов накоплении можно записать короче

Ь

(fe) sin 27fetp;

Yc,r(f) Z.cos 2iTfetp, t - T71.

sin

27fe

n

Ycn(fe)21cos2 fgtp, Mr

8Lp c.

fr I,L записываются по соответствую- щим 2L адресам оперативного запоминающего устройства 11 взамен прежних хранившихся там сумм (fg) и YenH(fj), причем вычисление всех L чисел Agn, ехр() и всех соответствующих 2L сумм Y5n(fЈ) и YC (fg) заканчивается до начала следующего (п+2)-го импульса окна, после чего весь цикл вычислений чи- сел Aj)m, exp(-j2irfettH, ) и сумм Y5,mi( fe) YC,TH. (f) повторяется.

Во время первого импульса окна в регистры 8 и 21 записываются коды m ,, и М соответственно. В начале

0 второго окна коды га и М{ перепиL.

n1

cos

2W. tn Z.CQS 2iifLtp. p«i

Таким образом, к началу второго окна, следующего за рассматривав мым интервалом измерения, в оперативном запоминающем устройстве 11 по 2L адресам записаны соответствующие ре« зультаты накопления для всех N про-

реженных импульсов нуль-пересечении рассматриваемого интервала измере- ния - квадратурные составляющие комплексных корреляционных интегра- лов:

N

Vfe - Wfe ,sin eV

VI

Vfe} Yc,vj(fe IEcos , Ј TL.

От начала второго до начала третьего окна следующего интервала измерения синхронизатор 5 сигналом режима поиска максимума с выхода 27.4 (фиг.9е) переводит цифровой измеритель частоты и фазы в режим поиска максимума квадрата модуля комплексного корреляционного интегр.| ла по данным, накопленным в оперативном запоминающем устройстве 1 1 H.I предыдущем интервале измерения. Данный сигнал переводит сумматор 10 в режим прямого пропускания данных с первого входа на выход. Перебор адресов оперативного запоминающего устройства 11, запись и считывание данных в этом режиме осуществляются в том же темпе и в том же порядке, как и при накоплении. Содержащиеся в оперативном запоминающем устройстве II квадратурные составляющие Y5(f,), Yc

YC

ся из оперативного запоминающего

устройства и через регистр 12 подаются на адресные входы постоянного запоминающего устройства 34 квадратора 13, а также на вход регистра 22. Одновременно данные-, поступающие с генератора 9 тригонометрических функций -sin , cog , sin .to cos C,, .,. , sin cos 2 n f t и соответствующие первому прореженному импульсу нуль-пересечения t. на новом интервале измерения, записываются по соответствующим 2L адресам оперативного запоминающего устройства I I. На выходе постоянного запоминающего устройства 34 формируются соответственно квадраты состав ляющих ) и Yc(fg), I l,L, которые поступают на входы сумматора 36 непосредственно -Yc(fg) и через буферный регистр 35 - Y|(). Каждое из сформированных на выходе сумматора 36 значение квадрата модуля корре ляционного интеграла

rf,), Ys(fa), YC(12),...,

(fL) поочередно считывают

Z(fg) Y|(fg) + Y(fe), i 1,L

0

5

0

5

0

5

0

5

0

5

записывается я регистр 37 бтока 14 поиска максимума и сравнивается в схеме 40 сравнения с кодом порога, записанным в регистр 39. Управляющий сигнал с выхода 27.4 синхронизатора включает для этого коммутатор 38 на пропускание содержимого регистра 37 на вход регистра 39 и разрешает работу схемы 40 сравнения. Если содержимое регистра 37 превосходит содержимое регистра 39, синхронизирующий импульс 27.2 (фиГ.Нд) синхронизатора 5 проходит через схему 40 сравнения и осуществляет тянись содержимого регистра 37 X(fe) через коммутатор 38 в регистр 39, записывает в регистр 43 номер t опорной частоты fg из счетчика 42 и фиксирует в регистре 50 блока 16 формирования оценки ф.эчы код оценки аргумента Y(f§), т.е. флчы этой составляющей спектра. Все последующие формируемые в сумматоре 36 значения квадрата корреляционного интеграла Z(fg+(), Z(j p4j.) и так далее сравниваются с превысившим порог и записанным и регистре 39 бпока 14 поиска максимума в качестве нового порога значениям кнадр.пм модуля кор реляционного интеграла Z(fg), пока одно из них не превысит содержимое регистра 39 и не запишется в него в качестве нового порога. Таким образом, процедура поиска максимума продолжается до Z(f, ) включительно. Состояние счетчика 42 на каждом шаге сравнения увеличивается на еди- ницу, принимая ряд значений I/ I,L, совпадающих с номером t опорной частоты, квадрат модуля комплексного корреляционного интеграла Z(fj) для которой сравнивается в данный момент времени с порогом. Обнуление счетчика 42 и регистра 43 производится в начале каждого интервала измерения сигналом с выхода 27.5 синхронизатора 5 (фиг.8г),

Процедура поиска максимума квадрата модуля комплексного корреляцион ного интеграла 2(fg) заканчивается после просмотра всех L значений Z(fp), Ъ - 1,L, при этом в регистре 43 запишется номер / опорной частоты iЈ, для которой значение модуля комплексного корреляционного интегра

л

ла Z(fp) наибольшее из сформированных на данном интервале измерения Запись кода порога в регистр 39 производится в начале каждого интервала измерения сигналом с выхода 27.5 синхронизатора 5 (Фиг.вг). Коммутатор 40 переключается на пропускание кода порога с третьего 15 входа измерите-

ля на вход регистра 39 сигналом с выхода 27.4 (фиг.9а) синхронизатора 5.

Одновременно с формированием и поиском максимума квадрата модуля корреляционного интеграла (модуля спектра) формируется оценка его аргумента (фазы спектра) в блоке 16 формирована i оценки фазы. Квадратурные COCIMHTU п,д ,. Yg(fg) и Yc(fe) ко:;пл }- сч. /о корреляционного интеграф Гг-Otarctg a lYel eJ -eogafY5lfe)

- I

та- .JO iVu -V,(fg) Yc(fe) 0 , 1 ,-РЬ Y5(fe) , Yc(tt,) - 0

при Vc(fp ) О

при . L ( 1 q ) . 0.

При зто, сл гае Ое, тг-ключенное в квл, .чтнг с г too 1-й, Нормируется в nocTCHi HOM за::ог-.инс ji ieM устройстве i), T-I;IL IIH ратряд кода фачь; (число d) формируется .я знакового разряда кога i ( (i П и срйдственпо, а число Ь pi элементе НСКПЮ- М(|ЩЕП tiT. 52 in знаковых разрядов юд к vc(fg) i- yu;(fg) подается in ci дресшч вход постоянного ь лног-о i и «..тс ycTjj-mcTBi ч-9 че:рез р:-ги. rp L5

икнг , а время действия резина поиск.i максимума блок поиска макс иь хма срарннт вссд L фор- млрч-- к.п -и ляг; ил ква чрата модуля

i(ffl) КСМП (;КСНОГО ЧОрреЛЧПЦОИНОГС

интс ран.1 Y(i ) с попогом обнаруже нил и между сооой/j определит макси- мзаьное из них Z(fp). Номер I ,пор- пои ч- г j riii if, которой соответству-

tЛл

юг O JH чначош.- i (fg) и Y(fg) и KOTLJJCIJ: ягн-итсл оценкой часгпгы сшн .ла, чяш. сьтг.ется в регистр 4i б.чока ьоиск я , а )ценг л ар- i/мгчпа LMOTO маг ин-а-тьного но моду76

16

0

ла поступают с выхода регистра 22 через регистры 44 и 45 на адресные входы постоянных запоминающих устройств 51 и 46 соответственно, на выходах которых формируются логарифмы модулей этих составляющих (f«) и loga |YC(Јg)| , поступающие на сумматор 48 Логарифмы модулей действи- тепьных составляющих logq p)/ предварительно инвертируются j инверторе 47. С выхода сумматора 48 код разности loga /Y c(f . )f - - loga|Y(fg)| . ступает на адресный вход постоянного запоминающего уст- 49, с выхода которого выходным импульсом блока 14 поиска максимума считывается в регистр 50 код оценки фазы соответствующей составляющей спектра, формируемый по алгоритму

+ b1i + (0,27),

лю значения Y(fg), являющаяся оцен- кой начапьной фазы сигнала, записывается в регистре 50 блока 16 формирования оценки фазы.

Аппаратурная погрешность оценки фазы сигнала, т.е. погрешность при отсутствии шумов v(t) на входе измерителя складывается из двух основных составляющих: погрешности, вызванной эффектом квантования входных данных и конечной разрядностью представления чисел в узлах цифрового измерителя частоты и фазы сигнала и погрешности, связанной с неопределенностью положения прореженных импульсов нуль-пересечений по отноше - нию к середине интервала измерения. Первая составляющая присуща всем цифровым измерителям и уменьшается до требуемого значения увеличением тактовой частоты, разрядности пред ставления данных и результатов вычислений.

Вторая составляющая является принг пна.пьной для измерителей фазы сигнала по его нуль-пересечениям, так как в них измерение фазы сигнала в известные моменты времена подме чяется измерением моментов времени, когда фаза сигнала равна известной величине, например, (2lfg - ), где

S 0, + , +2,... . Оценить :)ту co- ставляющую погрешности можно но формуле

Дф, ,

где 0 t - априорная неопределенность положения прореженных и NT- ПУЛЬСОВ нуль-пересечения на интервале измерения, В известном измерителе априорная неопределенность положения импульсов нуль-пересечения, прореженных счетчиком-делителем, на интервале измерения равна

:fn/2F - l/2)fc 1/2F.

При этом погрешность опенки фазы в известном измерителе достигает величины ф, г (21T/4FT). Например, при 2F 6 кГц, Т 0,025 с, JP, 1,2°.

В предлагаемом измерителе увеличение точности измерения фачы достигается путем уменьшения неопределенности положения прореженных импуль- сов нуль-пересечений Для этого прореживание импульсов нуль-пересечений осуществляется не с помощью счетчика-делителя, как в известном измерителе, а с помощью окон, временное положение которых на пнтгрнале измерения жестко определено схемой измерителя и одинаково на всех интервалах измерения. В этом случае неопределенность положения прореженных им- пульсов нуль-пересечений на интервале измерения не превышает периода сигнала l/fc. Рассматриваемая составляющая погрешности оценки фазы в предлагаемом измерителе ф . 2Т/2ТЈс т.е. примерно Е fc/2F раз меньше, че в известном измерителе Например, при f0 100 кГц и Т 0,025 с $Фгя 0,07°.

Испытания предлагаемого измерите- ля с параметрами f0 100 кГц, ftf 20 кГц, L 300, Т 0,025 с также подтвердили его высокую эффективность.

Измеритель позволяет в реальном времени получать оценки частоты и фазы сигнала при априорной неопреде- ленности его частоты 2F 6 кГц. Точность измерения фазы сигнала близка к теоретически потенциальной, потери не превышают ,5 дБ во всем диапазоне отношений сигнал/шум, кроме ус ловий, когда наблюдается практически чистый сигнал. В этом случае состав

ллкицая аппаратурной погрешности измерения фазы сип .ч.ча ч.т счет неопределенности поло/кення прором-нных пульсоп нуль-перигечгний на интервале измерения не превышает расчетной величины.

Формула изобретения

Цифровой измеритель частоты и фазы гармонического сигнала, содержащий компаратор, вход которого являет ся первым входом устройства, счетчик делитель, синхронизатор, первый вход KOTOpoio соединен с первым выходом счетчика-делителя, счетчик, счетный вход которого соединен с вторым входом синхронизатора и является вторым входом устройства, генератор тригонометрических функций и первый сумматор, первый вход которого соединен с выходом генератора тригонометрических функций, и последовательно соединенные оперативное запоминающее устройство, первый регистр, выход которого дополнительно соединен с вторым входом первого сумматора, квадратор и блок поиска максимума, второй вход которого является третьим входом устройства, причем синхронизирующий вход генератора тригонометрических функций, объединенные синхронизирующий вход первого регистра, первый синхронизирующий вход блока поиска максимума и управляющий вход оперативного запоминающего устройстса, объединенные синхронизирующий вход квадратора и второй синхронизирующий вход блока поиска максимума, управляющий вход блока поиска максимума, третий синхронизирующий вход блока поиска максимума, адресные входы оперативного запоминающего устройства и управляющий вход генератора тригонометрических функций соединены соответственно с первым - седьмым выходами синхронизатора, отличающийся тем, что, с целью повышения точности измерения фазы и расширения диапазона рабочих частот, в него введены четыре регистра, сумматор, блок формирования оценки фазы и D-триггер, на D-вход которого подан уровень логической единицы, синхронизирующий вход которого соединен с выходом компаратора, а выход с третьим входом синхронизатора, вход второго регистра соединен с вы ходом счетчика, а выход - с первым входом генератора тригонометрических функций, вход третьего регистра соединен с выходом первого регистра, выход блока формирования оценки фазы является первым выходом устройства, а первый и второй входы соединены с выходом третьего регистра и с первым выходом блока поиска максимума соответственно, последовательно соедини ны второй сумматор, первый вход кото рого является четвертым входом уст- ройства, четвертый регистр, выход которого дополнительно соединен с вто рым входом второго сумматора, а синхронизирующий вход - с вторым входом устройства, и пятый регистр, выход которого соединен с вторым входом генерп гор;; тригонометрических функций, причем УЫХОД первого сумматора соединен с входом оперативного запо-

17

0

5

0

минающего устройства, счетный вход счетчика-делителя соединен с вторым входом устройства, первый выход счетчика-делителя дополнительно соединен с входом установки в О D-триггера, а второй выход - с четвертым входом синхронизатора, объединенные синхронизирующие входы третьего регистра и блока формирования оценки фазы, упраятяюший вход первого сумматора, объединенные входы начальной установки счетчика и четвертого регистра, объединенные синхронизирующее входы второго и пятого регистров соединены соответственно с вторым, четвертым, пятым и восьмым ьысодами синхронизатора, информационный вход счетчика является пятым входом устройства, а второй выход блока поиска максимума - вторым выходом устройства.

Фиг. 2 .

Г

Ј МИф

1

1

, 9 аи

1

е

9 19291

а)

J

а25.2

б25, V

в/ синхрониза- твра

г27.5

В27.2

с25.}

ж гсинхоощщр 27.7

и

-Г/2 25.2ПГОШПЛВ25.4 -Г

г J синхра- Г

низатора-|

д Чсинхоо- - низатора

е 27.4 - Ж 27.3 -И

10КНО 1 ОКН02 1 QKHQ3

J

-Г/2

L

ллллг ша

г.5

Составитель В.Новоселов

Техред М.Дидык Корректор М.Демчик

Редактор И Горная

Заказ 275Тираж. 176Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. А/5

- -- - - - ..

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Фиг. 7

.ЛИИ.

п

п

-ITULTT. П|

Фиг.8°

JUUITJl

J

L

ллллг ша

| Устройство для автоподстройки частоты и цифровой обнаружитель-измеритель частоты | 1982 |

|

SU1092733A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-02-07—Публикация

1988-10-25—Подача