Изобретение относится к измерительной технике и технике автоматического регулирования, в частности, к преобразователям угла в код, и может быть использовано в системах где требуется измерять положение с высокой точностью. Изобретение целесообразно использовать при проектировании специализированных интегральных схем датчиков положения.

Известен способ цифрового преобразования угла в код с коррекцией ошибки преобразования [1] основанный на том, что значения выходного кода образуют суммированием выходного кода основного канала амплитудного цифрового преобразования угла следящего типа и выходного кода корректирующего канала, при этом соответствующие значения выходного кода корректирующего канала формируют при вращении ротора датчика угла основного канала преобразования с постоянной угловой скоростью, равной половине ее максимального рабочего значения, путем аналого-цифрового преобразования тахометрического сигнала основного канала преобразования, интегрирования переменной составляющей преобразованного тахометрического сигнала и регистрации проинтегрированного сигнала. Недостатком данного технического решения является требование наличия дополнительного канала для коррекции кода угла.

Известен способ цифрового преобразования угла в код с коррекцией ошибки преобразования [2] основанный на том что для коррекции ошибки преобразования используется два канала преобразования (два датчика) с различными спектрами пространственной погрешности. Вычисляются разности первого и второго кодов угла, по которым определяют амплитуды и фазы пространственных гармоник погрешности первого датчика, формируют первую поправку как сумму пространственных гармоник погрешности первого датчика для угла, соответствующего первому коду угла, формируют выходной код, прибавляя первую поправку к первому коду угла. Недостатком данного решения является то что для коррекции ошибки преобразования требуется два датчика с разным спектром ошибки, что в случае реализации на уровне интегрального датчика положения со встроенной сенсорной системой невозможно технически.

Известен преобразователь угол-код [3] реализованный в микросхеме обработки сигналов с синусно-косинусных датчиков положения. В тракте обработки данной микросхемы реализован прямой алгоритм коррекции синусно-косинусного сигнала, включающий коррекцию смещения (в том числе и по датчику температуры), разбаланса амплитуд и фазового сдвига. Корректированный сигнал поступает на преобразователь угол-код. Описанная конструкция широко применяется для коррекции ошибки преобразователей угол-код, но применима только для преобразователей с независимым преобразованием синусно-косинусного сигнала на дискретных АЦП и кроме того не может компенсировать 3-ю и 4-ю гармоники (связанную с нелинейными искажениями), а компенсируют только первую и вторую гармоники.

Известно довольно много методов коррекции сигналов преобразователей различного типа основанных на коррекции ошибки преобразования умножением выхода датчика на корректирующий полином с различными степенями, чем выше степень - тем точнее можно минимизировать ошибку преобразования. Данный метод универсален и применим для преобразователей различного типа, в том числе и преобразователей угол-код. Подобный метод описан, например, в [4], [5] и в различных модификациях используется в огромном количестве устройств. Недостатками данного метода является либо его ресурсоемкость при конвейерной аппаратной реализации (требует умножителей и чем больше степень полинома, тем больше требований к разрядности) либо невысокое быстродействие при программной реализации с использованием последовательного вычислителя (например, на основе микроконтроллера).

Известен метод цифровой коррекции ошибки преобразования для синусно-косинусных преобразователей угол-код [6] включающий два АЦП преобразующих аналоговые синусный и косинусный сигналы в цифровой код, с выходов АПЦ сигналы поступают на вход блока коррекции смещения, разбаланса амплитуд и фазы, с выхода блока коррекции сигналы поступают на детектор разбаланса смещения, разбаланса усилений и фазы, с выхода детектора на вход блока коррекции поступают сигналы пропорциональные соответствующим разбалансам. Скорректированный сигнал после коррекции разбалансов поступает на блок коррекции гармонических искажений (3-я гармоника синусного и косинусного сигнала) и далее на преобразователь угол-код. Данное решение применимо только для преобразователей, в которых синусно-косинусные сигналы преобразуются в цифровой код и лишь затем поступают на преобразователь угол-код, и не применимо для целого класса следящих преобразователей угол-код где отсутствует промежуточное преобразование синусного и косинусного сигналов в цифровой код [7, 8].

Задачей изобретения является повышение точности преобразователей угла в код с получением корректирующих коэффициентов с использованием только кода угла, а именно устранении нелинейностей с периодами кратными 1, 2, 3, 4 относительно периода сигнала (первая, вторая, третья и четвертая гармоники).

Поставленная задача решается благодаря тому, что код угла преобразователя суммируется с набором поправочных значений, полученных из данного кода угла:

- для 1-го поправочного значения путем преобразования CORDIC в режиме поворот со сдвигом на фиксированное значение, сигнал берется с выхода SIN блока CORDIC;

- для 2-го поправочного значения путем сдвига кода угла влево на один разряд и преобразования CORDIC в режиме поворот со сдвигом на фиксированное значение, сигнал берется с выхода SIN блока CORDIC;

- для 3-го поправочного значения путем преобразования CORDIC в режиме поворот со сдвигом на фиксированное значение, сигнал берется с выхода SIN блока CORDIC, умножением на 3, с последующим вычитанием из этого значения другого значения, полученного путем сдвига кода угла на один разряд влево и преобразования CORDIC в режиме поворот со сдвигом на фиксированное значение, сигнал берется с выхода COS блока CORDIC, вычитанием данного значения из значения соответствующего максимальному для блока CORDIC, сдвига вправо на один разряд, умножение на выход SIN первого блока CORDIC с последующим сдвигом на 2 разряда влево, сигнал берется с выхода вичитателя;

- для 4-го поправочного значения путем сдвига кода угла влево на два разряда и преобразования CORDIC в режиме поворот со сдвигом на фиксированное значение, сигнал берется с выхода SIN блока CORDIC.

Между совокупностью существенных признаков заявленного изобретения и достигаемым техническим результатом существует причинно-следственная связь, а именно, блок цифровой коррекции кода угла позволяет обеспечить коррекцию нелинейностей кода угла имеющих гармонический характер с периодами кратными периоду кода угла, а именно устранить первую, вторую, третью и четвертую гармоники.

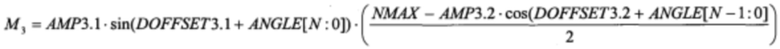

Математически техническая сущность предложенного изобретения описывается системой выражений:

ϕ1=АМР1⋅sin(DOFFSET1+ANGLE[N:0])

ϕ2=АМР2⋅sin(DOFFSET2+ANGLE[N-1:0])

ϕ3=3⋅NMAX⋅АМР3.1⋅sin(DOFFSET3.1+ANGLE[N:0])-4⋅M3

ϕ4=AMP4⋅sin(DOFFSET4+ANGLE[N-2:0])

ANGLE_CORR=ANGLE[N:0]+ϕ1+ϕ2+ϕ3+ϕ4

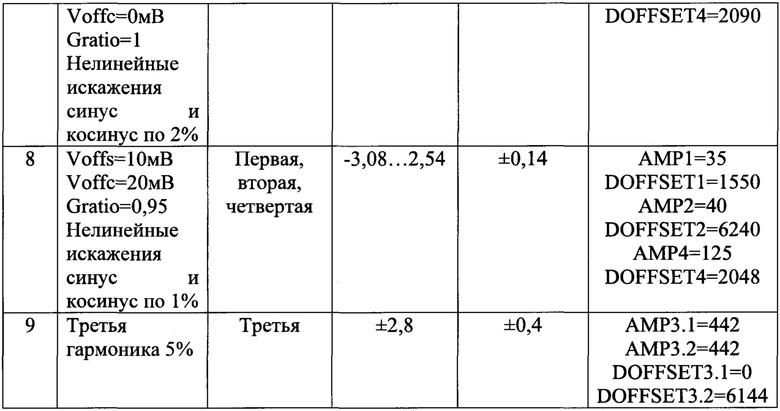

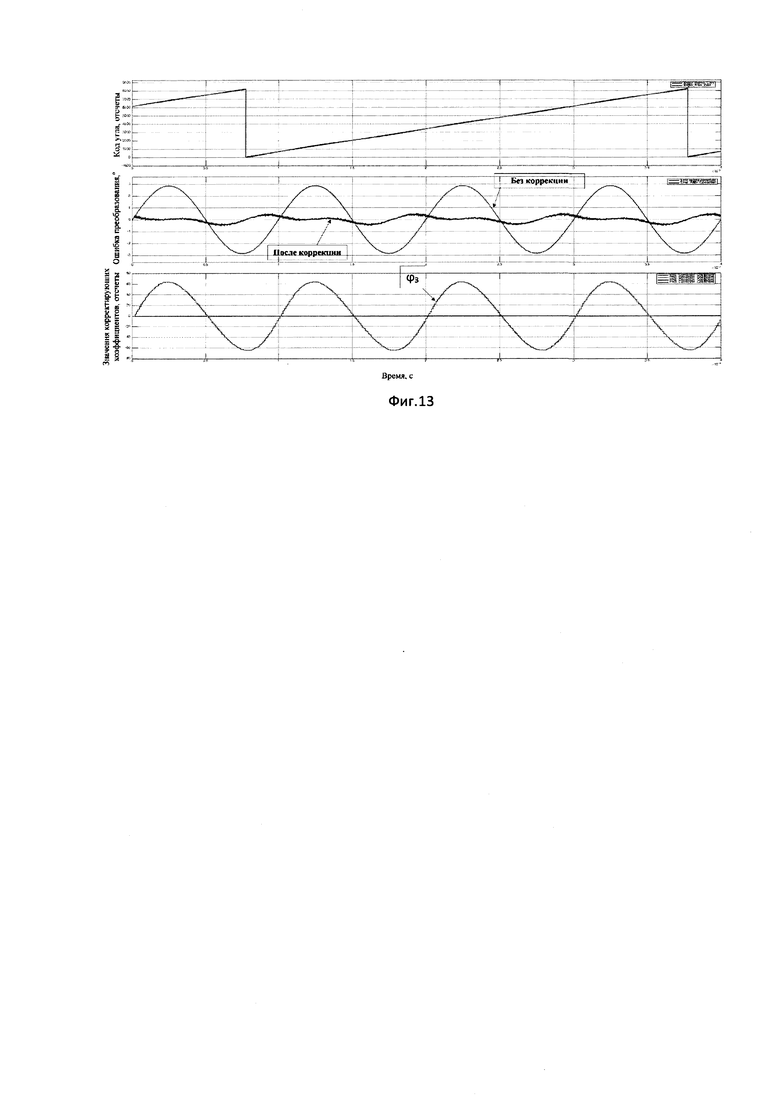

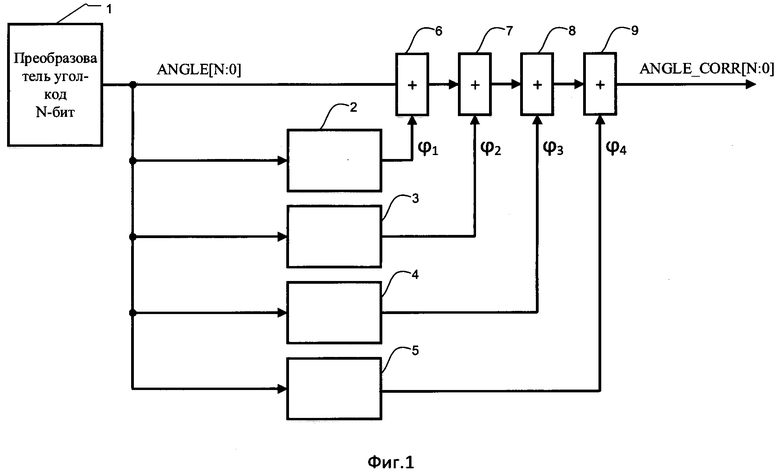

Техническая сущность предложенного изобретения поясняется чертежами, где фиг. 1 содержит структурную схему блока коррекции кода угла преобразователя угол-код, фиг. 2 содержит структурную схему формирования первого поправочного значения, фиг. 3 содержит структурную схему формирования второго поправочного значения, фиг. 4 содержит структурную схему формирования третьего поправочного значения, фиг. 5 содержит структурную схему формирования четвертого поправочного значения, на фиг. 6-13 приведены графики демонстрирующие работу устройства.

Структура схемы коррекции ошибки приведена на фиг. 1. и содержит:

1 - преобразователь угол-код;

2 - блок формирования 1-го поправочного значения;

3 - блок формирования 2-го поправочного значения

4 - блок формирования 3-го поправочного значения;

5 - блок формирования 4-го поправочного значения;

6 - первый сумматор;

7 - второй сумматор;

8 - третий сумматор;

9 - четвертый сумматор.

С выхода преобразователя угол-код 1 сигнал поступает на блоки формирования поправочных значений ϕ1-ϕ4 2-5, с выхода каждого из которых сигналы поступают на входы соответствующих сумматоров 6-9.

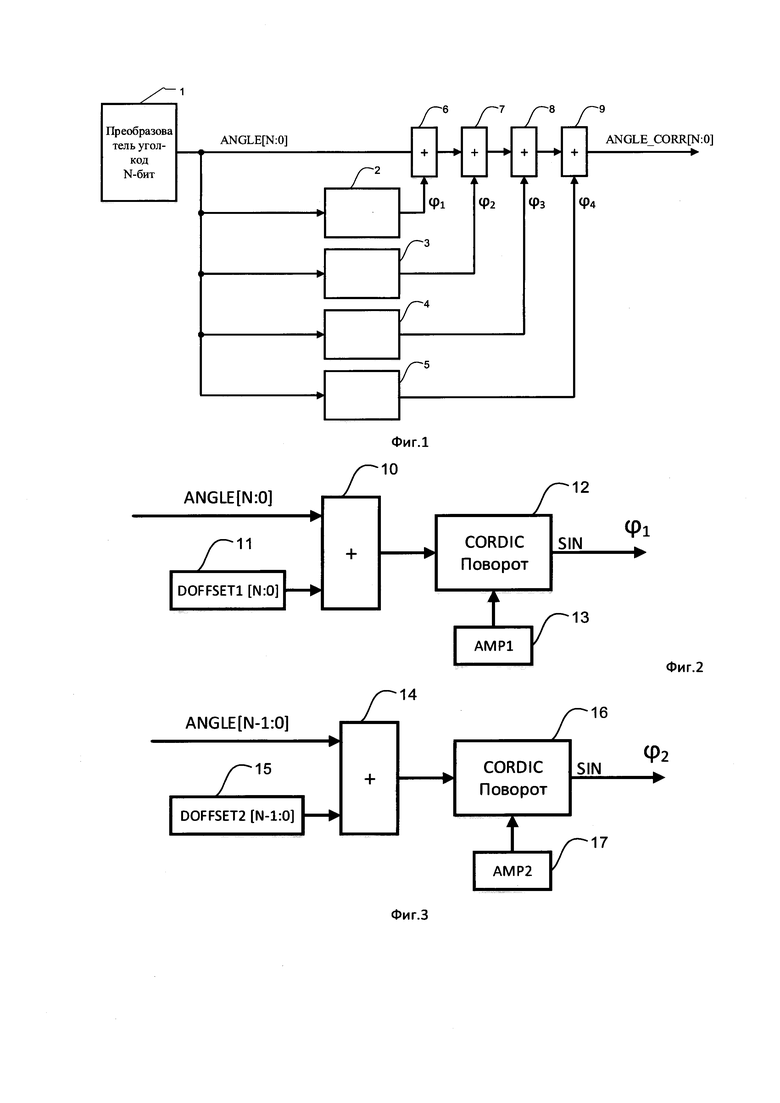

Структурная схема блока формирования 1-го поправочного значения показана на фиг. 2 и содержит:

10 - сумматор;

11 - регистр сдвига начального значения;

12 - блок CORDIC в режиме поворот;

13 - регистр амплитуды выходного сигнала.

Код угла сдвигается на фиксированное значение путем сложения с регистром сдвига начального значения 11. После чего смещенный код угла поступает на вход блока CORDIC в режиме «поворот», амплитуда выходного сигнала блока CORDIC задается регистром 13. Выход SIN блока 12 является первым поправочным значением ϕ1 кода угла.

Структурная схема блока формирования 2-го поправочного значения показана на фиг. 3 и содержит:

14 - сумматор;

15 - регистр сдвига начального значения;

16 - блок CORDIC в режиме поворот;

17 - регистр амплитуды выходного сигнала.

Код угла без старшего бита, сдвигается на фиксированное значение путем сложения на сумматоре 14 с регистром сдвига начального значения 15. После чего смещенный код угла поступает на вход блока CORDIC в режиме «поворот», амплитуда выходного сигнала блока CORDIC задается регистром 17. Выход SIN блока 16 является вторым поправочным значением ϕ2 кода угла.

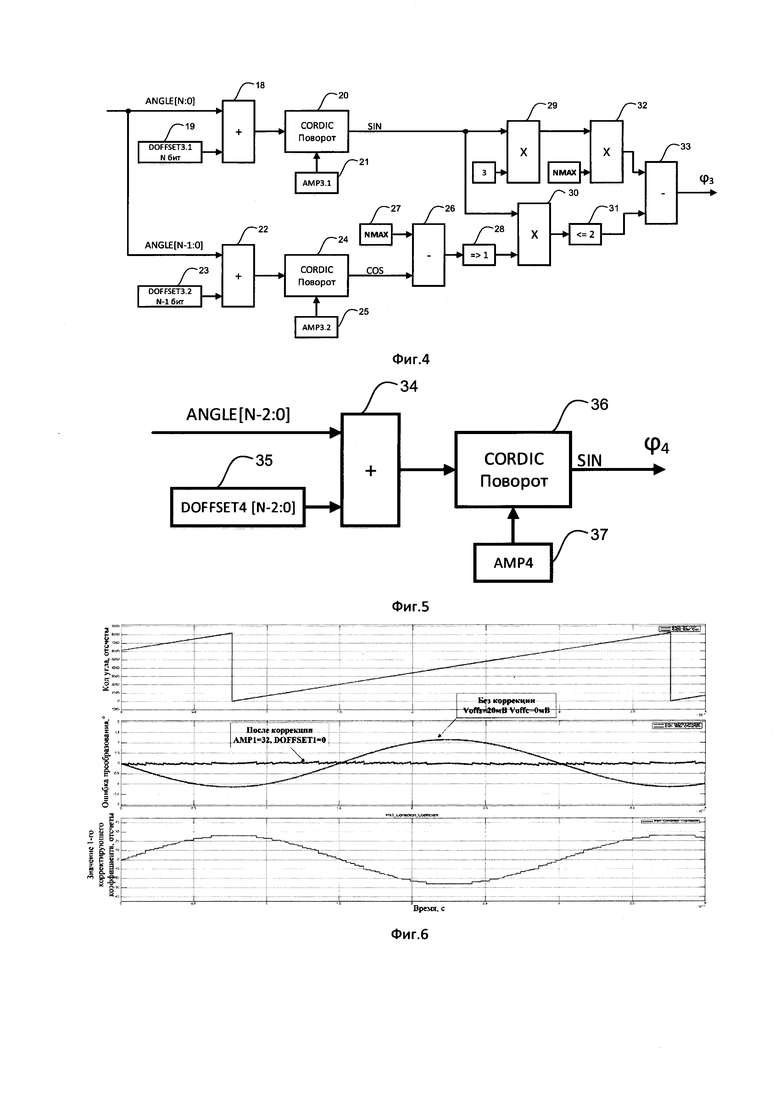

Структурная схема блока формирования 3-го поправочного значения показана на фиг. 4 и содержит:

18 - сумматор 1;

19 - регистр 1 сдвига начального значения;

20 - блок 1 CORDIC в режиме поворот;

21 - регистр амплитуды 1 3-го поправочного значения;

22 - сумматор 2;

23 - регистр 2 сдвига начального значения;

24 - блок 2 CORDIC в режиме поворот;

25 - регистр амплитуды 2 3-го поправочного значения;

26 - вычитатель 1;

27 - регистр максимального значения амплитуды NMAX;

28 - регистр сдвига на 1 разряд вправо;

29 - умножитель 1;

30 - умножитель 2;

31 - регистр сдвига на 2 разряда влево;

32 - компенсирующий умножитель;

33 - вычитатель 2.

Код угла сдвигается на фиксированное значение путем сложения на сумматоре 18 с регистром 1 сдвига начального значения 19. После чего смещенный код угла поступает на вход блока CORDIC 20 в режиме «поворот», амплитуда выходного сигнала SIN блока CORDIC задается регистром 21. Код угла без старшего бита, сдвигается на фиксированное значение путем сложения на сумматоре 22 с регистром сдвига начального значения 23. После чего смещенный код угла поступает на вход блока CORDIC 24 в режиме «поворот», амплитуда выходного сигнала COS блока CORDIC задается регистром 25. Выход COS подается на вычитатель 26 где вычитается из регистра максимального значения NMAX 27. С выхода вычитателя сигнал поступает на регистр сдвига на один разряд вправо 28 и далее на умножитель 30 где перемножается с выходом SIN блока CORDIC 20, с выхода умножителя сигнал сдвигается на регистре 31 на два разряда влево. Выход SIN блока CORDIC 20 умножается на 3 на умножителе 29 и далее поступает на вход компенсирующего умножителя 32 (для компенсации разницы амплитуд между двумя ветвями блока связанной с целочисленным представлением данных) и далее на вход вычитателя 33. На второй вход вычитателя 33 поступает сигнал с выхода регистра сдвига 31. Выход вычитателя 33 является третьим поправочным значением ϕ3 кода угла.

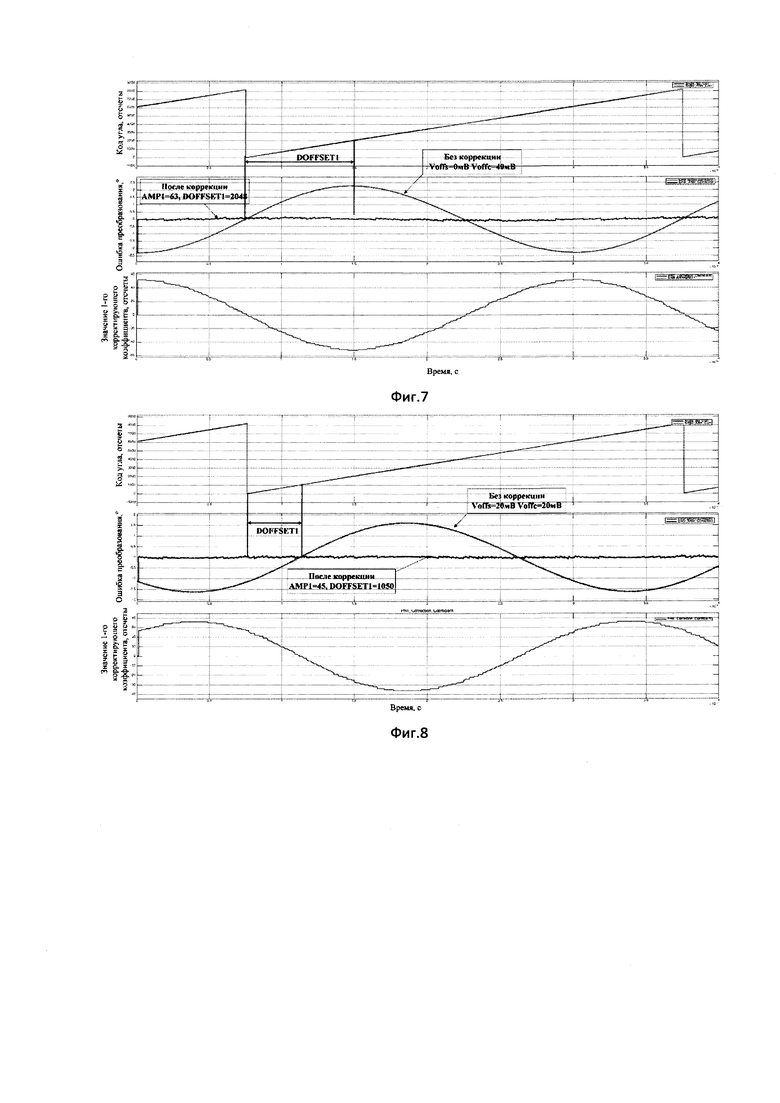

Структурная схема блока формирования 4-го поправочного значения показана на фиг. 5 и содержит:

34 - сумматор;

35 - регистр сдвига начального значения;

36 - блок CORDIC в режиме поворот;

37 - регистр амплитуды выходного сигнала.

Код угла без двух старших бит, сдвигается на фиксированное значение путем сложения на сумматоре 34 с регистром сдвига начального значения 35. После чего смещенный код угла поступает на вход блока CORDIC 36 в режиме «поворот», амплитуда выходного сигнала блока CORDIC задается регистром 37. Выход SIN блока 36 является четвертым поправочным значением ϕ4 кода угла.

Предложенная конструкция позволяет скорректировать ошибку угла, вызванную неидеальностью сенсорой системы и аналогового тракта обработки и имеющие периодический характер.

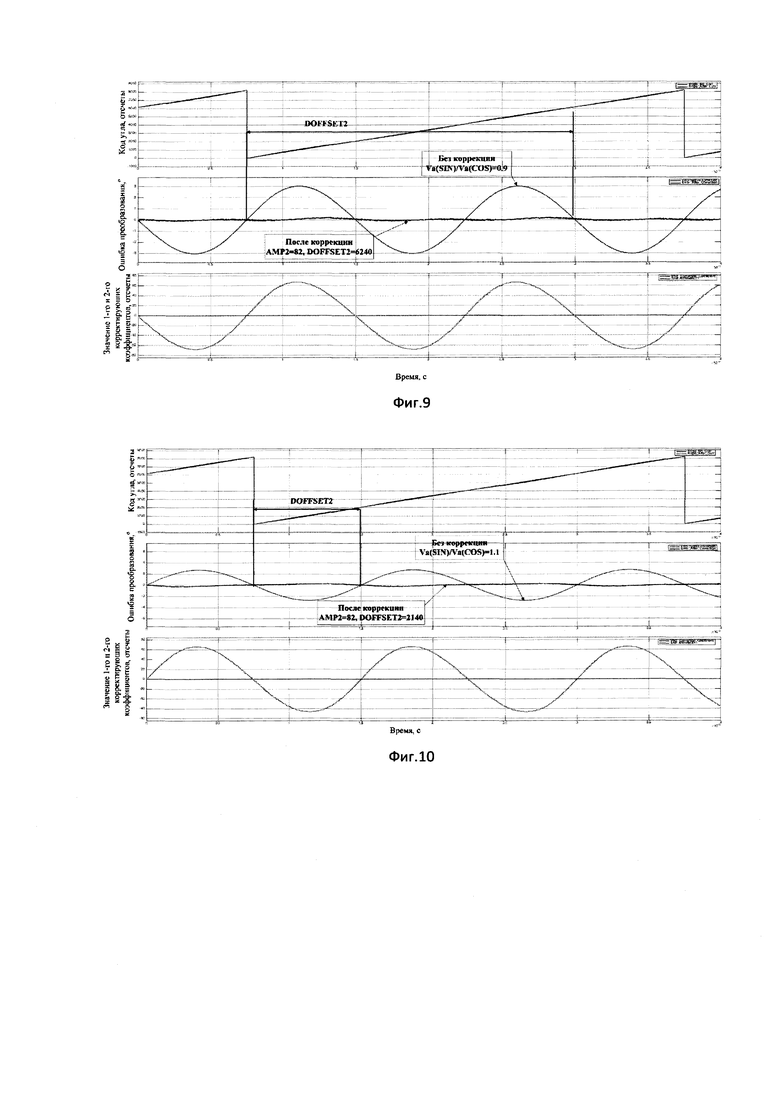

На фиг. 6-8 показаны графики, демонстрирующие работу системы коррекции ошибки для компенсации нелинейности 1-го порядка (первая гармоника), вызванные, например, постоянным напряжением смещения в синусном и/или косинусном каналах. Показаны графики для случаев наличия постоянного напряжения смещения (амплитуда сигнала 1 В, разрешение преобразователя 13 бит или 0.05°):

- 20 мВ только на синусном канал;

- 40 мВ только на косинусном канале;

- по 20 мВ на синусном и косинусном каналах.

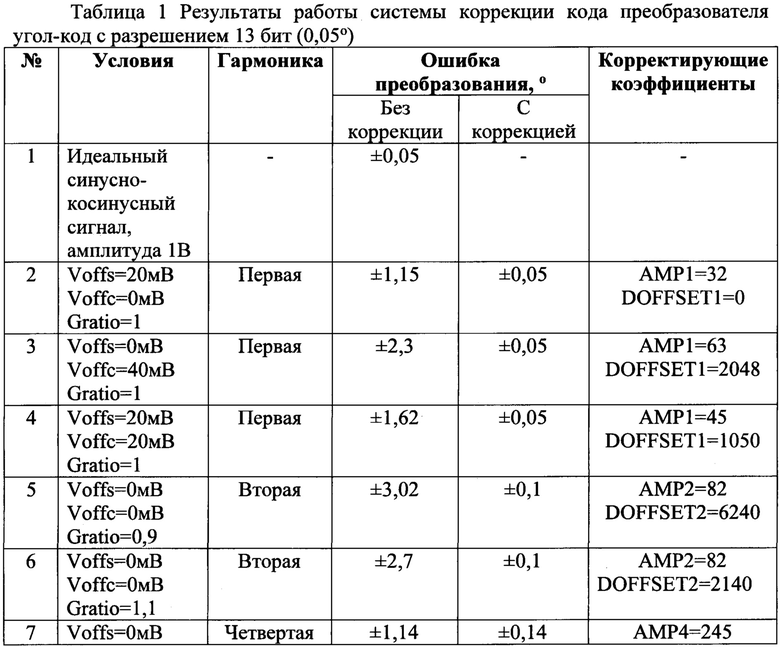

Результаты работы системы коррекции показаны в таблице 1. Система компенсирует ошибку нелинейности первого порядка более чем в 20 раз (от значений 2-5° до уровня 0,1° для преобразователя с разрешением 13 бит).

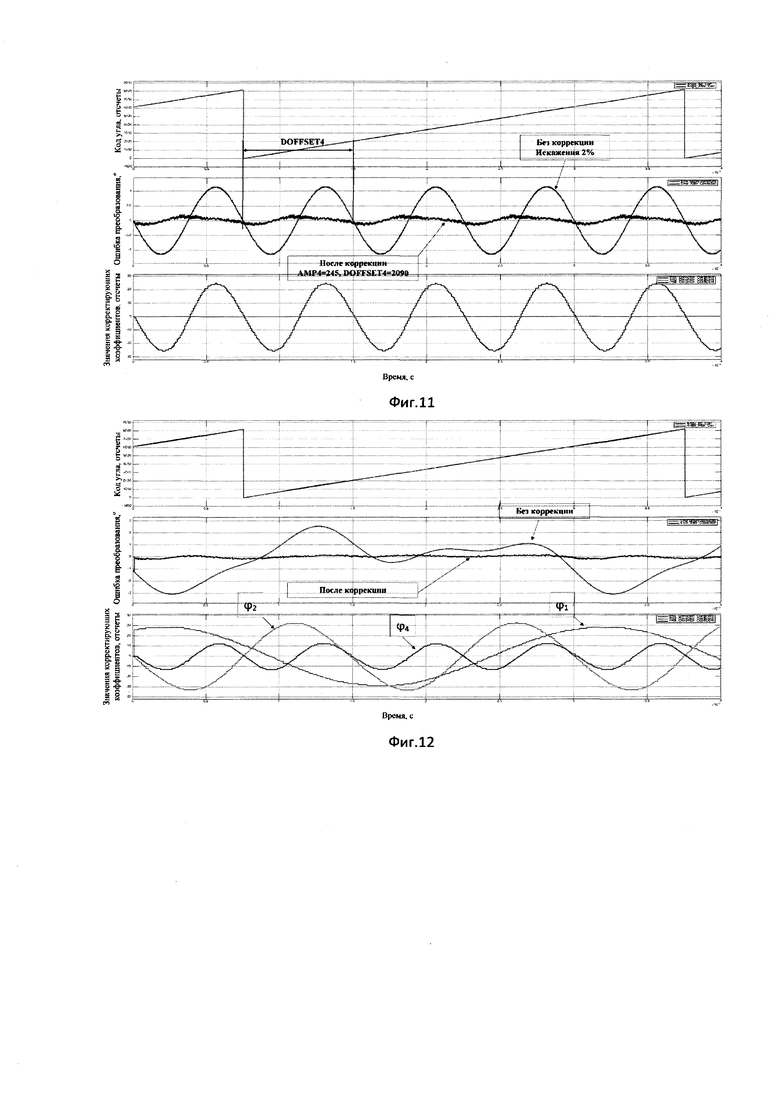

На фиг. 9, 10 показаны графики, демонстрирующие работу системы коррекции ошибки для компенсации нелинейности 2-го порядка (вторая гармоника), вызванные, например, различием амплитуд в синусном и косинусном канале. Результаты работы системы коррекции для случаем различия амплитуд синусного и косинусного каналов 0,9 и 1,1 показаны в таблице 1. Система компенсирует ошибку нелинейности второго порядка более чем в 20 раз (от значений порядка 6° до уровня 0,2° для преобразователя с разрешением 13 бит).

На фиг. 11 показаны графики работы системы коррекции для компенсации нелинейности 4-го порядка. Такие нелинейности вызваны нелинейными искажениями в аналоговом тракте преобразователей угол-код. На рисунке показана ошибка преобразования, вызванная нелинейными искажениями в синусном и косинусном каналах на уровне 2%, которая составляет ±1,14°. Подобранные корректирующие коэффициенты позволяют снизить ошибку практически в 10 раз.

На фиг. 12 показаны результаты работа системы коррекции для компенсации нелинейности вызванной всеми описанными выше факторами (смещение, различие амплитуд, нелинейные искажения) и включающие гармоники первого, второго и четвертого порядков. Подбором коэффициентов 1, 2 и 4-го каналов удалось снизить ошибку преобразования в 20 раз.

На фиг. 13 показаны результаты работы системы коррекции для компенсации нелинейности третьего порядка (вызванной, например, механическими факторами) на уровне 5%. Подбором коэффициентов удалось снизить ошибку преобразования в 7 раз.

Приведенные в таблице 1 данные показывают эффективность предложенной системы коррекции - ошибка преобразования снижается в 7-20 раз и более.

Алгоритм получения корректирующих коэффициентов предполагает начальный прогон преобразователя угол-код (датчика углового положения) на весь оборот с построением кривой ошибки сравнением с эталонным датчиком. По кривой ошибки определяют корректирующие коэффициенты. При наличии нескольких гармоник для определения амплитудных коэффициентов каждой гармоники АМР1-АМР4 можно использовать преобразование Фурье.

Для повышения точности вычисления корректирующих коэффициентов можно использовать блоки CORDIC с разрешением, существенно превышаемым необходимое для коррекции ошибки, с последующим сдвигом вправо на требуемое количество разрядов.

Технико-экономический эффект от предложенного изобретения заключается в повышении точности датчиков углового положения. Изобретение наиболее эффективно при интегральной реализации для коррекции ошибки преобразования в составе интегральных микросхем датчиков углового положения.

Источники информации

1. Патент РФ 2488958

2. Патент РФ 2235422

3. Статья «Интегральный процессор положения для прецизионных систем управления перемещением подвижных узлов и механизмов». Журнал «Компоненты и технологии», №7, 2016, стр. 81-85.

4. Статья «А Temperature Compensation Algorithm Based on Curve Fitting and Spline Interpolation». Chemical Engineering Transactions, 2016, №51, стр. 1345-1350.

5. Статья «PDF-Based Progressive Polynomial Calibration Method for Smart Sensors Linearization». IEEE TRANSACTIONS ON INSTRUMENTATION AND MEASUREMENT, 2009, том 58, №9, стр. 3245-3252.

6. Патент США 7250881

7. Полезная модель РФ 167428

8. Патент РФ 2659468

| название | год | авторы | номер документа |

|---|---|---|---|

| СЛЕДЯЩИЙ СИНУСНО-КОСИНУСНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД СО ВСТРОЕННОЙ ЦИФРОВОЙ КОРРЕКЦИЕЙ ОШИБКИ ПРЕОБРАЗОВАНИЯ | 2020 |

|

RU2741075C1 |

| Цифровой анализатор спектра | 1985 |

|

SU1322172A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Преобразователь угла поворота вала в код | 1990 |

|

SU1758875A1 |

| ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 2013 |

|

RU2541856C2 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| СПОСОБЫ И УСТРОЙСТВА ПОВЫШЕНИЯ ИНДЕКСА УГЛОВОЙ МОДУЛЯЦИИ | 2012 |

|

RU2493646C2 |

| Устройство для измерения линейных перемещений объекта | 1989 |

|

SU1740992A1 |

| Следящая система | 1987 |

|

SU1631513A1 |

| СЛЕДЯЩИЙ СИНУСНО-КОСИНУСНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД | 2017 |

|

RU2659468C1 |

Изобретение относится к измерительной технике и технике автоматического регулирования, в частности к преобразователям угла в код, и может быть использовано в системах, где требуется измерять положение с высокой точностью. Техническим результатом предлагаемого изобретения является повышение точности преобразователей угла в код, в том числе устранение нелинейности с нечетным периодом (3-я гармоника). Устройство коррекции ошибки преобразователя угол-код содержит четыре блока вычисления корректирующих коэффициентов (для первой, второй, третьей и четвертой гармоник), построенных на основе преобразования нескорректированного кода угла (со сдвигом на нужное число разрядов слева) в соответствующие корректирующие коэффициенты на основе CORDIC-преобразователей в режиме «поворот», причем для третьей гармоники используются формула тройного угла для синуса и формула понижения степени для квадрата синуса. Выходы блоков вычисления корректирующих коэффициентов складываются с кодом преобразователя угол-код и выход последнего сумматора является скорректированным кодом угла. 1 табл., 13 ил.

Устройство коррекции ошибки преобразования кода угла, содержащее первый сумматор для сложения кода угла с первым корректирующим значением, второй сумматор для сложения кода угла со вторым корректирующим значением, третий сумматор для сложения кода угла с третьим корректирующим значением, четвертый сумматор для сложения кода угла с четвертым корректирующим значением, первый вход первого сумматора соединен с выходом преобразователя угол-код, выход первого сумматора соединен с первым входом второго сумматора, выход второго сумматора соединен с первым входом третьего сумматора, выход третьего сумматора соединен с первым входом четвертого сумматора, отличающееся тем, что код с выхода преобразователя складывается с первым регистром сдвига начального значения на пятом сумматоре, после чего поступает на вход первого блока CORDIC в режиме поворот, на вход установки амплитуды первого блока CORDIC поступает сигнал с первого регистра амплитуды, выход синуса первого блока CORDIC является первым корректирующим значением и поступает на второй вход первого сумматора, код с выхода преобразователя сдвигается на один разряд влево и складывается со вторым регистром сдвига начального значения на шестом сумматоре, после чего поступает на вход второго блока CORDIC в режиме поворот, на вход установки амплитуды второго блока CORDIC поступает сигнал со второго регистра амплитуды, выход синуса второго блока CORDIC является вторым корректирующим значением и поступает на второй вход второго сумматора, код с выхода преобразователя складывается с третьим регистром сдвига начального значения на седьмом сумматоре, после чего поступает на вход третьего блока CORDIC в режиме поворот, на вход установки амплитуды третьего блока CORDIC поступает сигнал с третьего регистра амплитуды, сигнал с выхода синуса третьего блока CORDIC поступает на первый умножитель, где умножается на 3, выход первого умножителя поступает на второй умножитель где умножается на значение регистра максимального значения амплитуды, выход второго умножителя поступает на первый вход первого вычитателя, код с выхода преобразователя сдвигается на один разряд влево, далее складывается с четвертым регистром сдвига начального значения на восьмом сумматоре, после чего поступает на вход четвертого блока CORDIC в режиме поворот, на вход установки амплитуды четвертого блока CORDIC поступает сигнал с четвертого регистра амплитуды, сигнал с выхода косинуса четвертого блока CORDIC вычитается из регистра максимального значения амплитуды, далее сдвигается на один разряд вправо и далее умножается на выход синуса третьего блока CORDIC, выход умножителя сдвигается на два разряда влево и далее поступает на второй вход первого вычитателя, выход вычитателя является третьим корректирующим значением и поступает на второй вход третьего сумматора, код с выхода преобразователя сдвигается на два разряда влево и складывается с пятым регистром сдвига начального значения на девятом сумматоре, после чего поступает на вход пятого блока CORDIC в режиме поворот, на вход установки амплитуды пятого блока CORDIC поступает сигнал с пятого регистра амплитуды, выход синуса пятого блока CORDIC является четвертым корректирующим значением и поступает на второй вход четвертого сумматора, выход четвертого сумматора является скорректированным кодом преобразователя угол-код.

| СПОСОБ ПРИГОТОВЛЕНИЯ ЗЕФИРА | 0 |

|

SU167428A1 |

| СЛЕДЯЩИЙ СИНУСНО-КОСИНУСНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД | 2017 |

|

RU2659468C1 |

| СПОСОБ ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ УГЛА | 2012 |

|

RU2488958C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 2003 |

|

RU2235422C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| US 7250881 B2, 31.07.2007 | |||

| US 20060077083 A1, 13.04.2006. | |||

Авторы

Даты

2021-01-15—Публикация

2020-06-16—Подача