Изобретение относится к вычислительной технике и может найти применение при создании специализированных и универсальных высокопроизводительных вычислительных машин и систем,

Целью изобретения является повышение производительности за счет уменьшения времени при переключении с процесса на процесс в мультипрограммном режиме работы.

Поставленная цель достигается за счет того, что при организации мультипрограммного режима работы исключаются временные потери, связанные с интерпретацией команд внутреннего языка. Переключение с процесса на процесс осуществляется за одну микрокоманду. Кроме того, данное устройство позволяет избежать излишних временных затрат на управление очередью процессов, ожидающих постановки в one- ративной памяти за счет обеспечения каждому процессу возможности работать со своей областью сверхоперативной памяти, хранящей обрабатываемые им данные (контекст процесса).

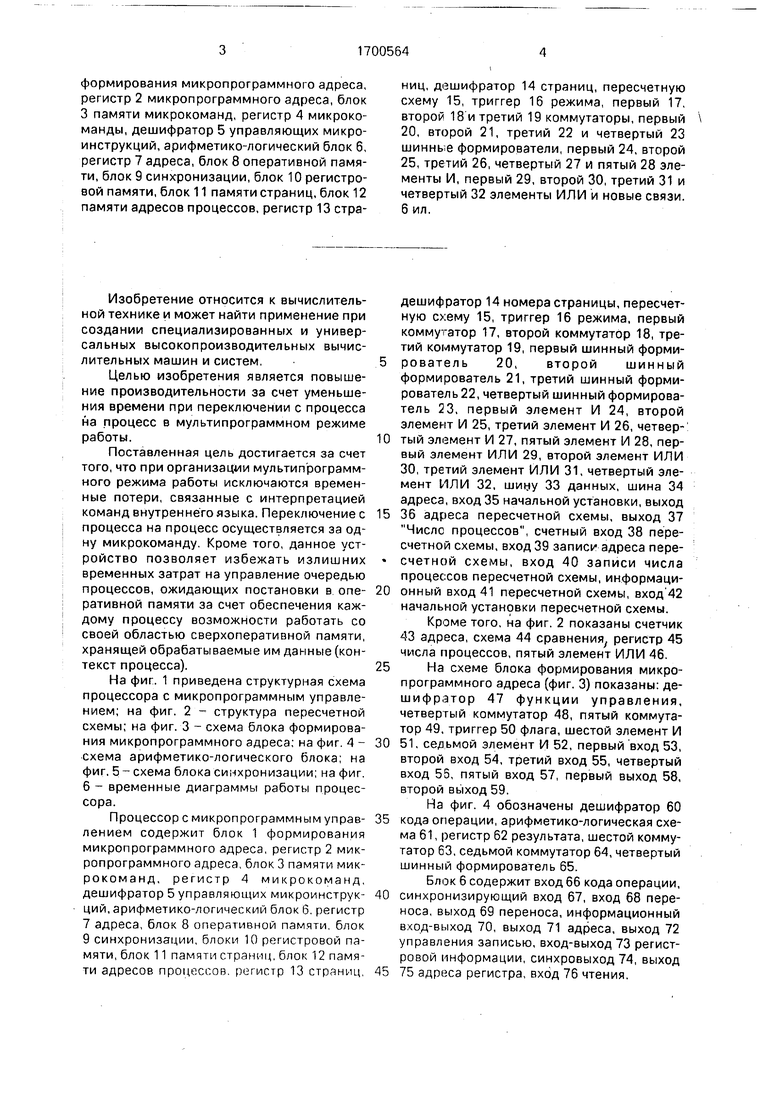

На фиг. 1 приведена структурная схема процессора с микропрограммным управлением; на фиг. 2 - структура пересчетной схемы; на фиг. 3 - схема блока формирования микропрограммного адреса; на фиг. 4схема арифметико-логического блока; на фиг. 5 - схема блока синхронизации; на фиг.

6- временные диаграммы работы процессора.

Процессор с микропрограммным управ- лением содержит блок 1 формирования микропрограммного адреса, регистр 2 микропрограммного адреса, блок 3 памяти мик- рокоманд, регистр 4 микрокоманд, дешифратор 5 управляющих микроинструк- ций, арифметико-логический блок 6. регистр

7адреса, блок 8 оперативной памяти, блок 9 синхронизации,блоки 10 регистровой памяти, блок 11 памяти страниц, блок 12 памяти адресов процессов регистр 13 страниц,

дешифратор 14 номера страницы, пересчетную схему 15, триггер 16 режима, первый коммутатор 17, второй коммутатор 18, третий коммутатор 19, первый шинный формирователь 20, второй шинный формирователь 21, третий шинный формирователь 22, четвертый шинный формирователь 23, первый элемент И 24, второй элемент И 25, третий элемент И 26, четвертый элемент И 27, пятый элемент И 28, первый элемент ИЛИ 29, второй элемент ИЛИ 30, третий элемент ИЛИ 31, четвертый элемент ИЛИ 32, шину 33 данных, шина 34 адреса, вход 35 начальной установки, выход 36 адреса пересчетной схемы, выход 37 Числе процессов, счетный вход 38 пересчетной схемы, вход 39 записи адреса пересчетной схемы, вход 40 записи числа процессов пересчетной схемы, информационный вход 41 пересчетной схемы, вход 42 начальной установки пересчетной схемы.

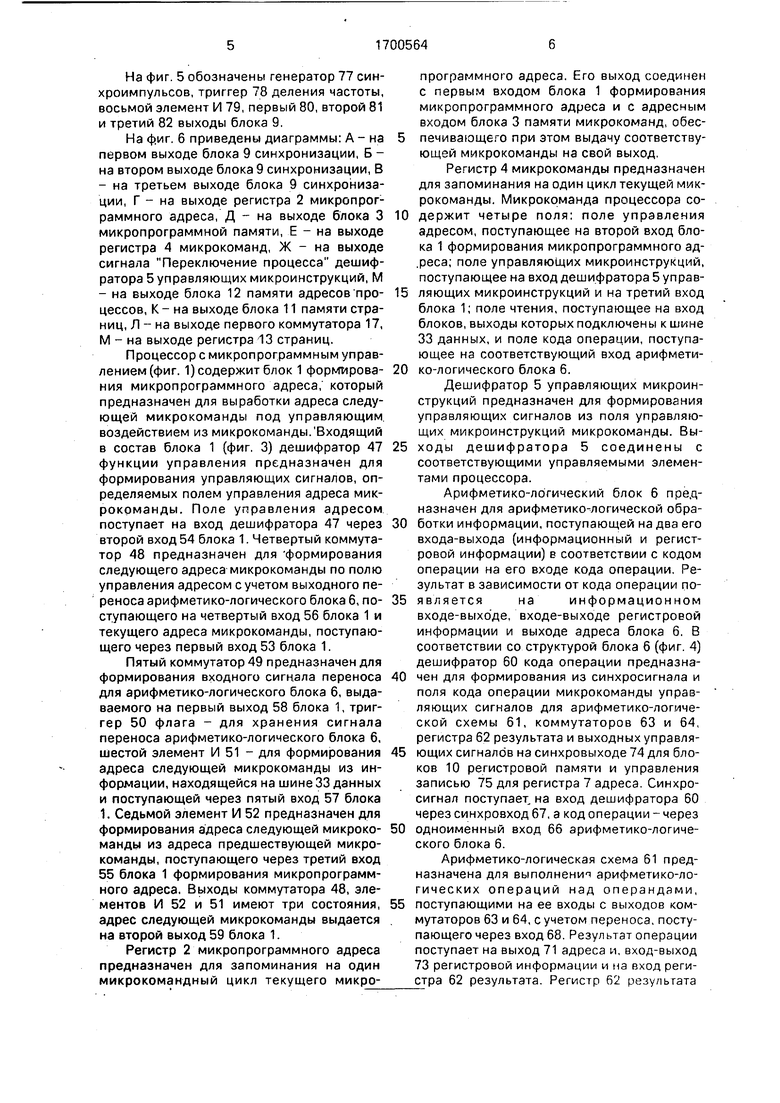

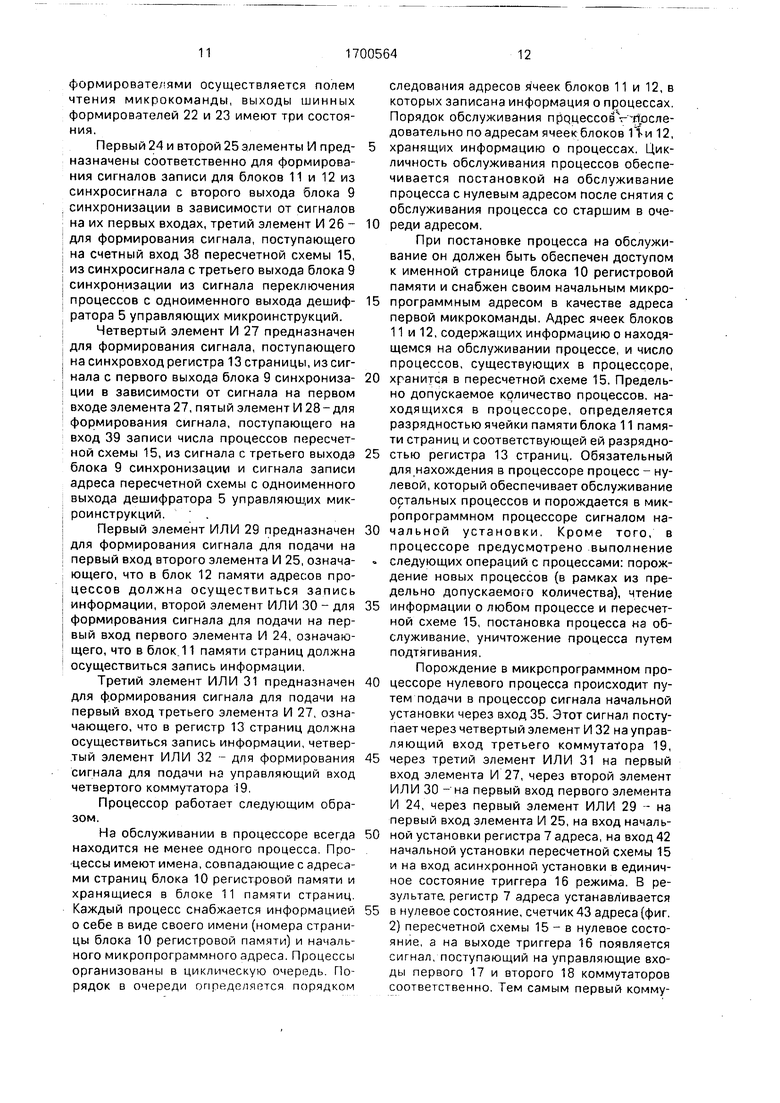

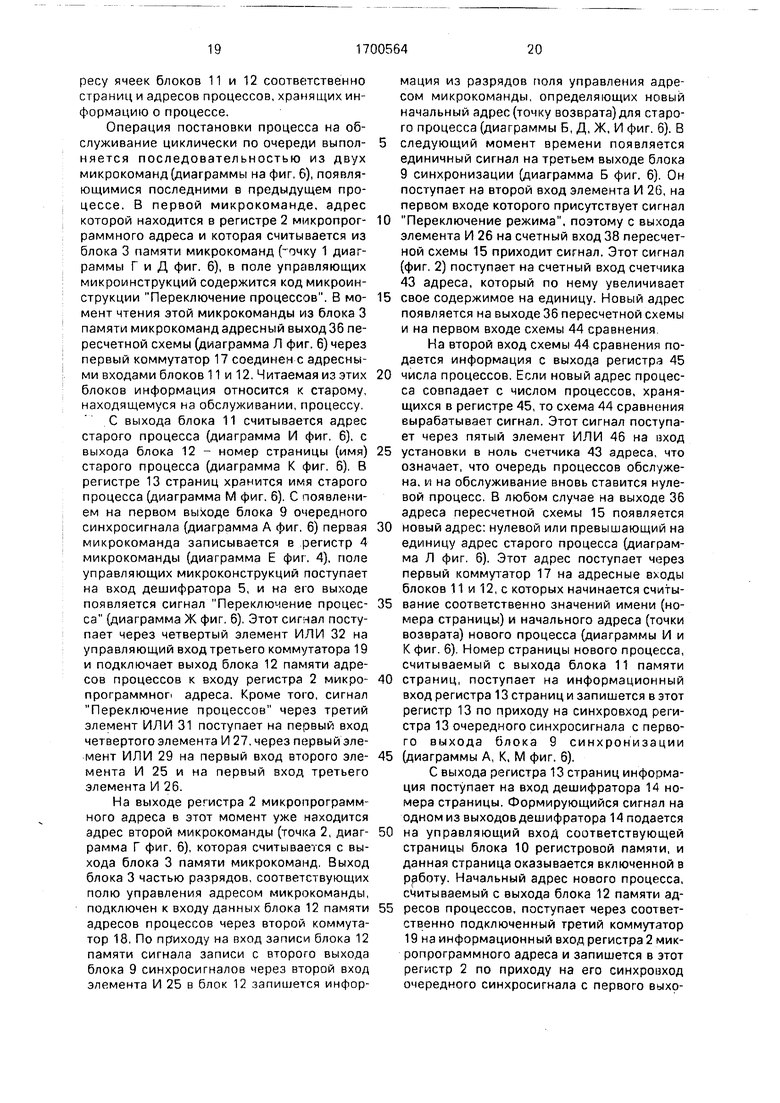

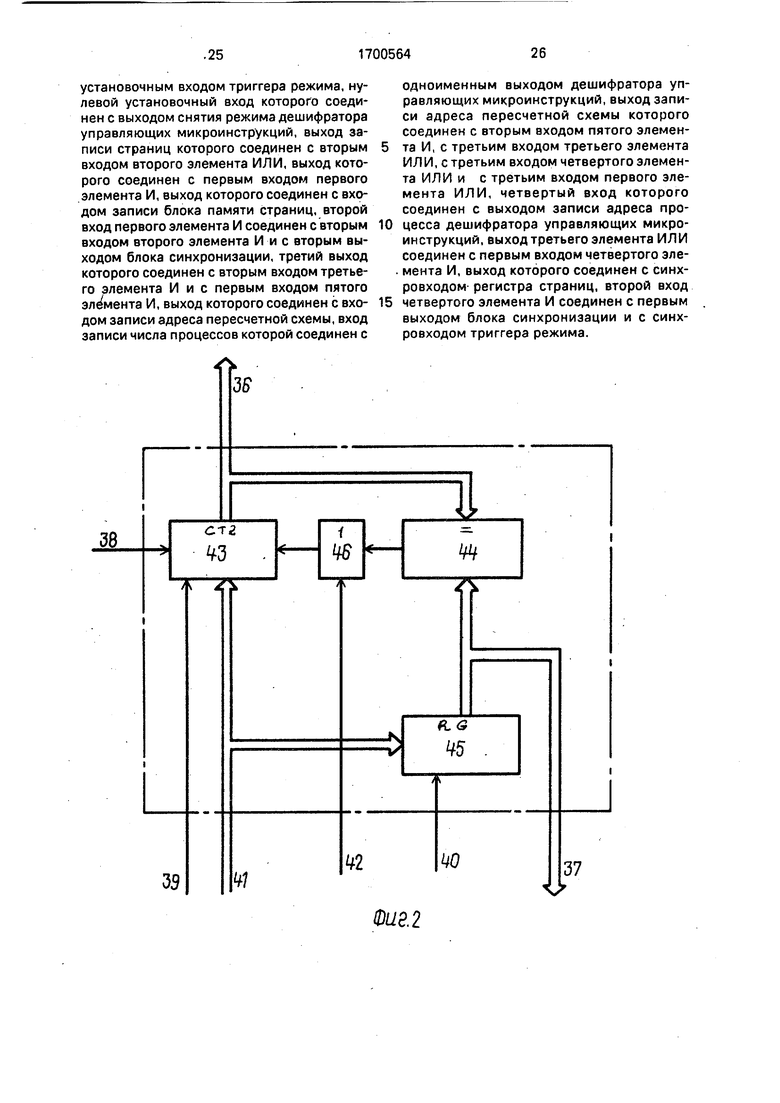

Кроме того, на фиг. 2 показаны счетчик 43 адреса, схема 44 сравнения, регистр 45 числа процессов, пятый элемент ИЛИ 46.

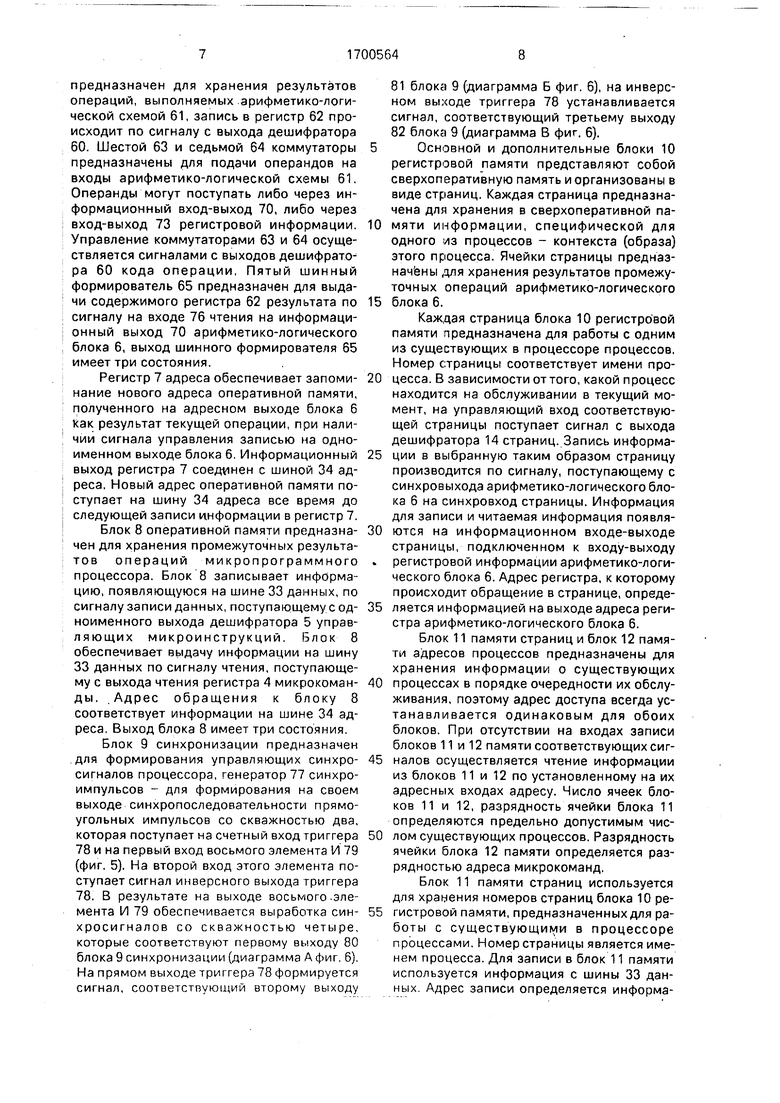

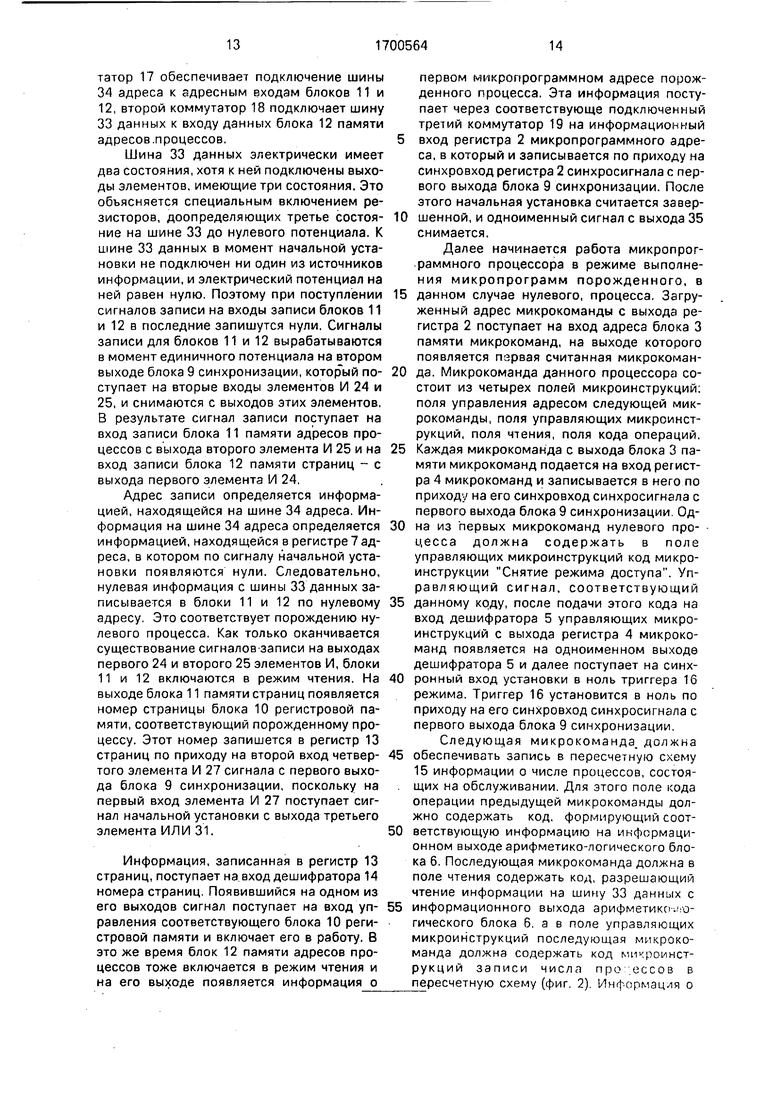

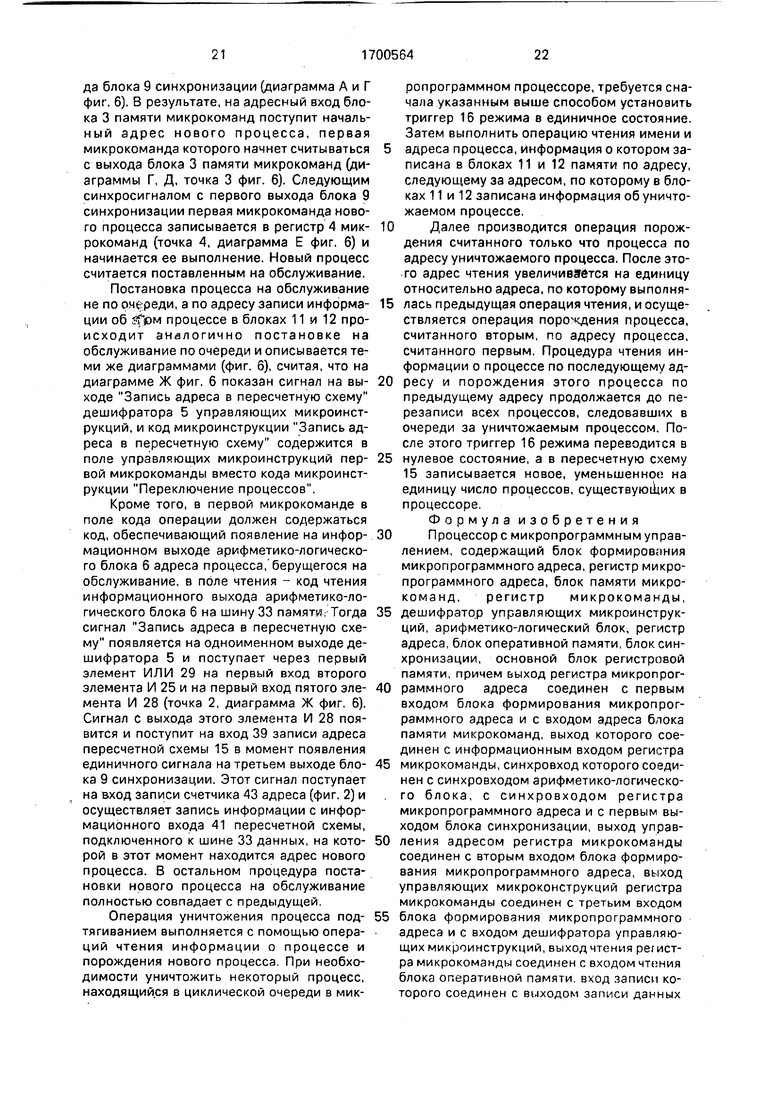

На схеме блока формирования микропрограммного адреса (фиг. 3) показаны: дешифратор 47 функции управления, четвертый коммутатор 48, пятый коммутатор 49, триггер 50 флага, шестой элемент И 51, седьмой элемент И 52, первый вход 53, второй вход 54, третий вход 55, четвертый вход 55, пятый вход 57, первый выход 58, второй выход 59.

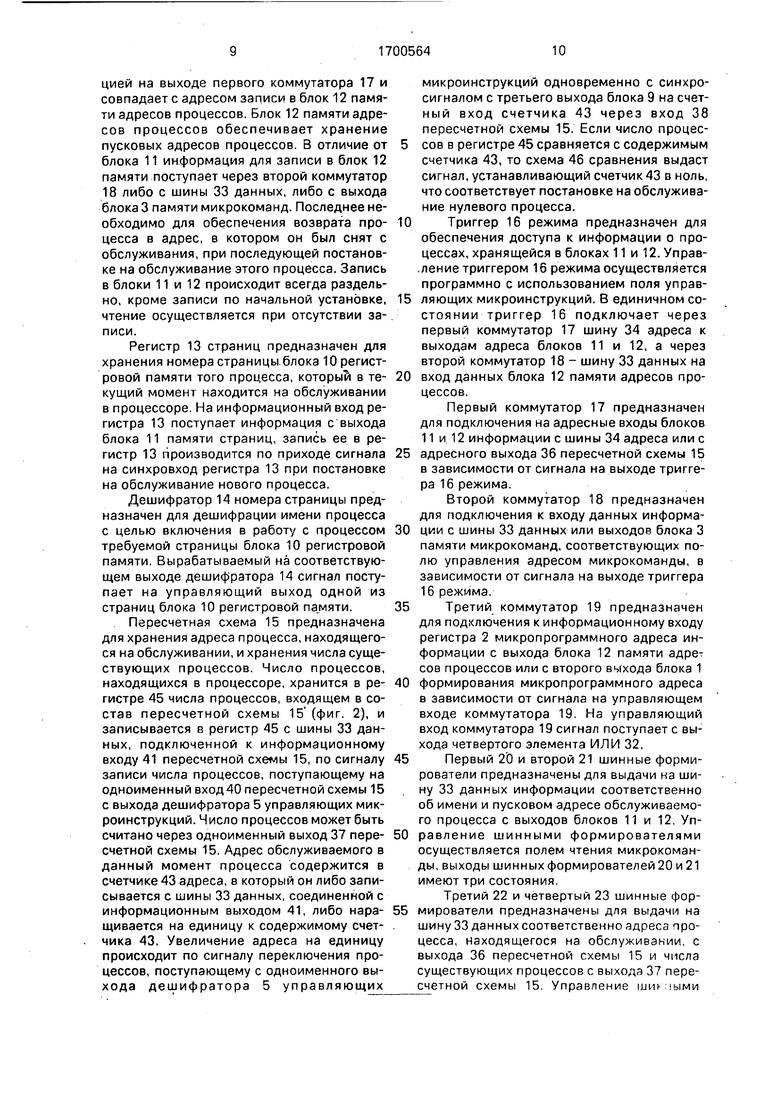

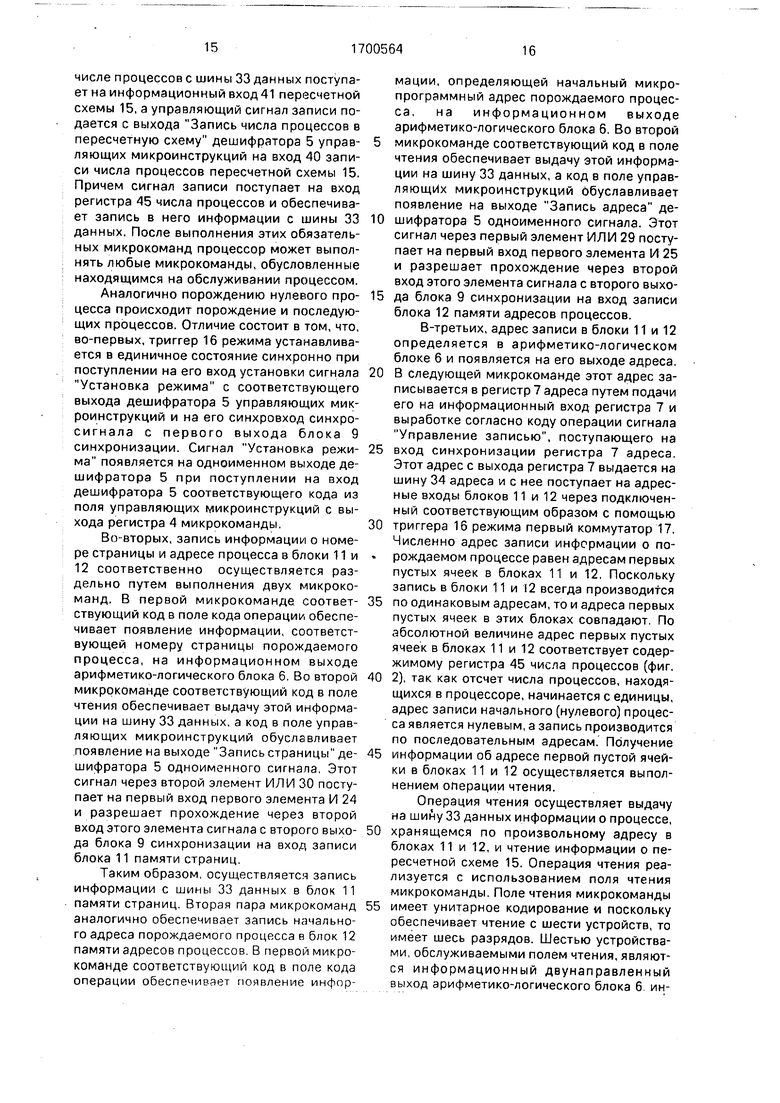

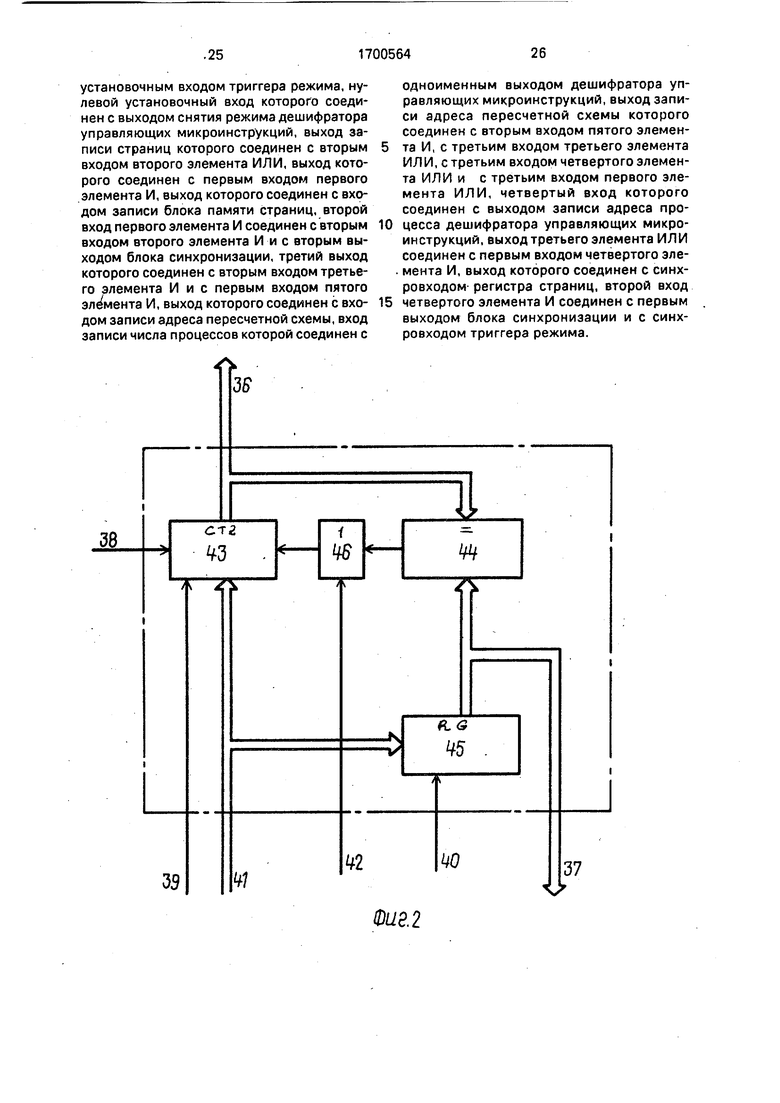

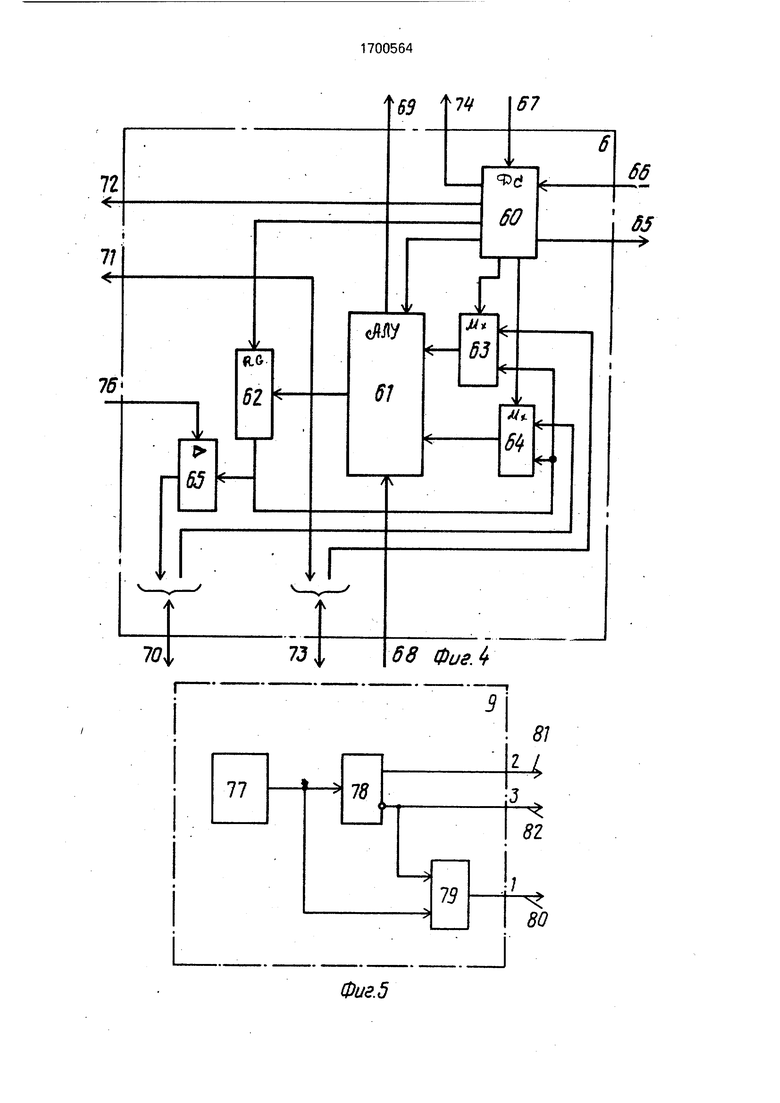

На фиг. 4 обозначены дешифратор 60 кода операции, арифметико-логическая схема 61, регистр 62 результата, шестой коммутатор 63, седьмой коммутатор 64, четвертый шинный формирователь 65.

Блок 6 содержит вход 66 кода операции, синхронизирующий вход 67, вход 68 переноса, выход 69 переноса, информационный вход-выход 70, выход 71 адреса, выход 72 управления записью, вход-выход 73 регистровой информации, синхровыход 74, выход 75 адреса регистра, вход 76 чтения.

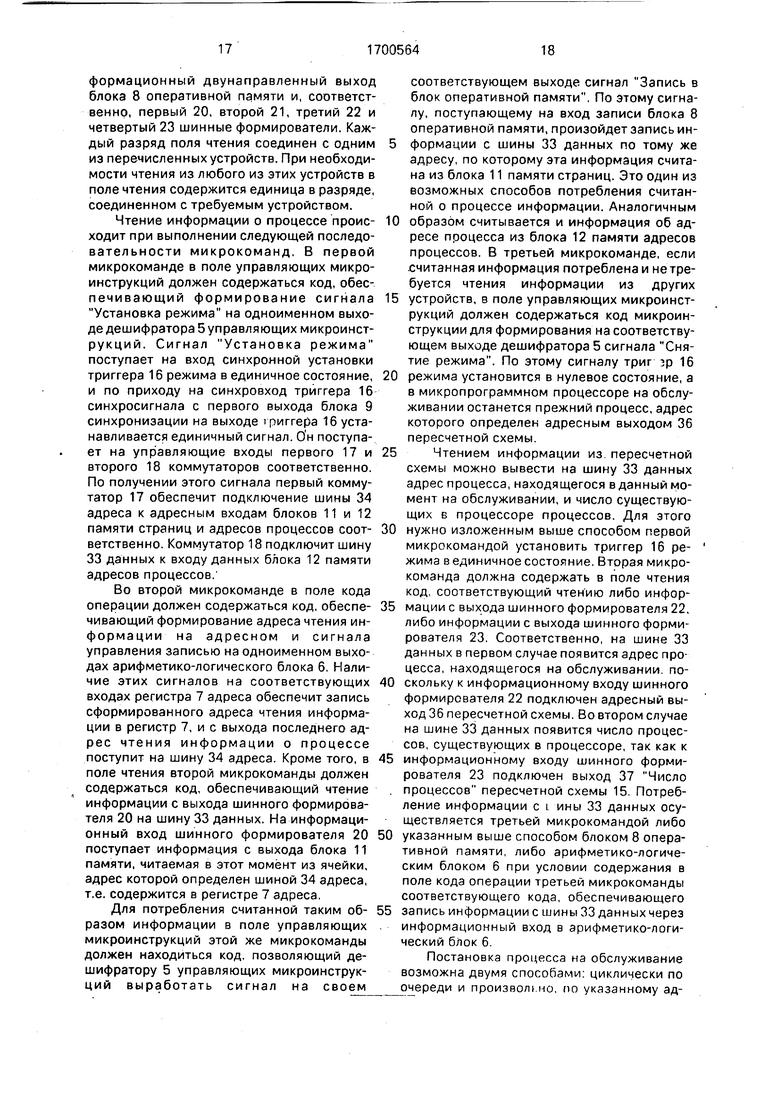

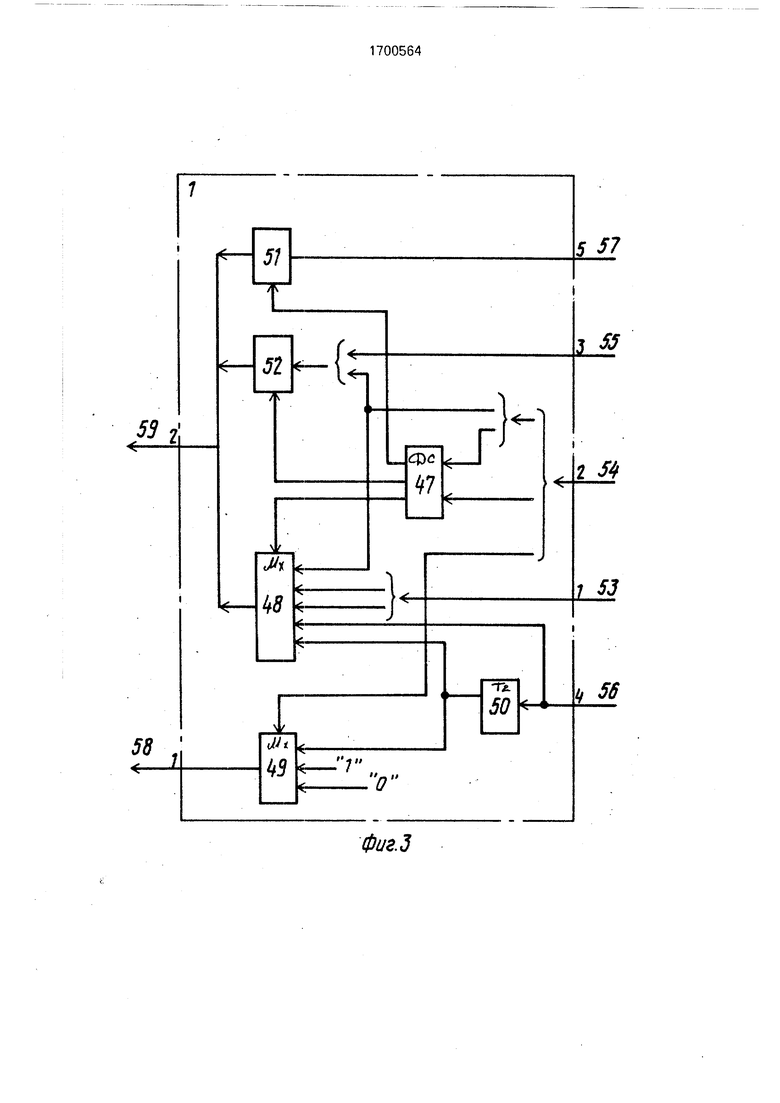

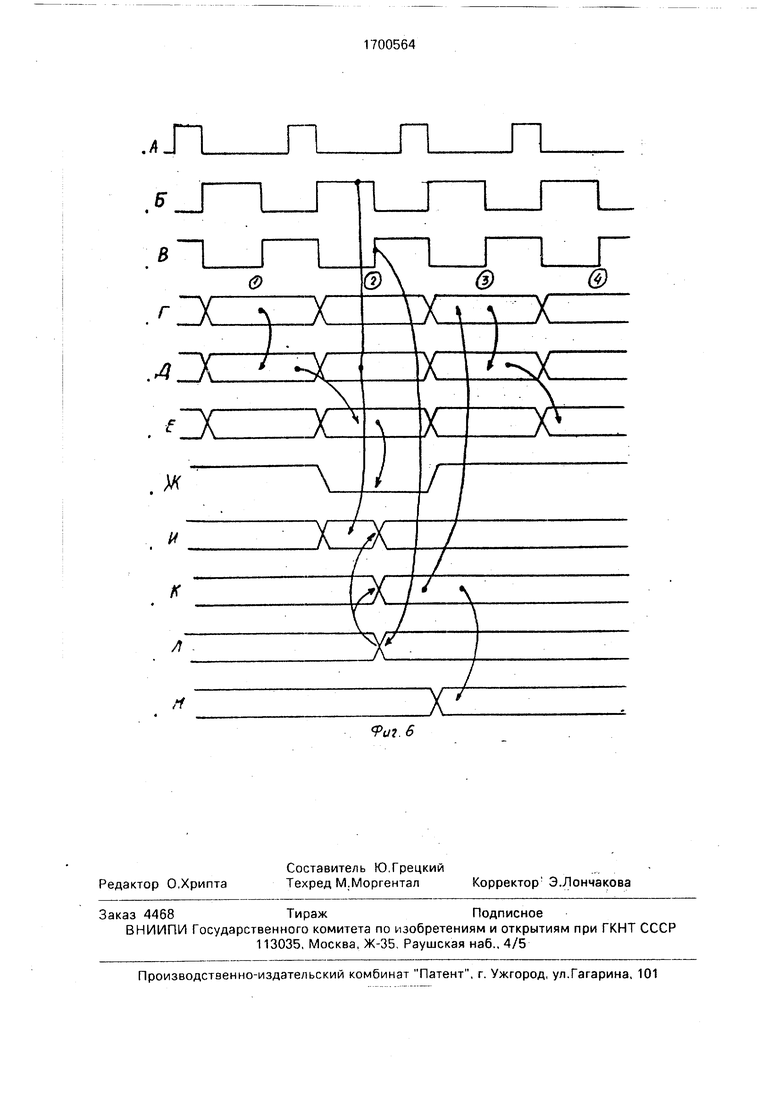

На фиг. 5 обозначены генератор 77 синхроимпульсов, триггер 78 деления частоты, восьмой элемент И 79, первый 80, второй 81 и третий 82 выходы блока 9.

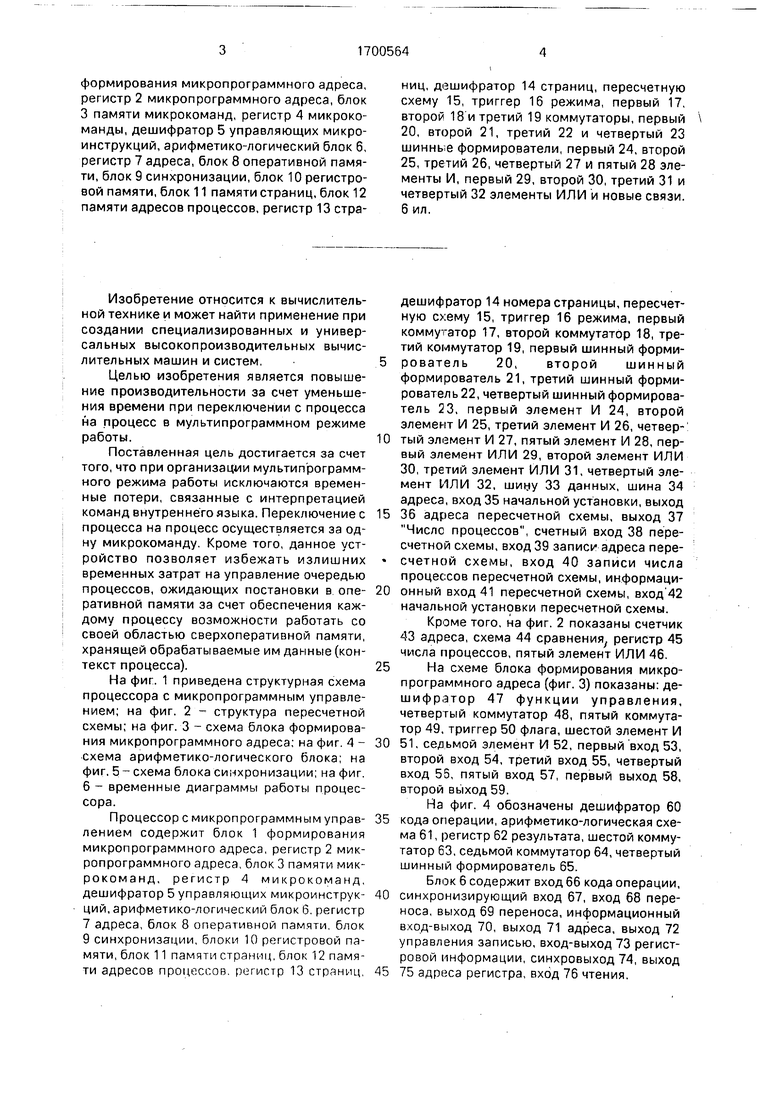

На фиг. 6 приведены диаграммы: А - на первом выходе блока 9 синхронизации, Б - на втором выходе блока 9 синхронизации, В

-на третьем выходе блока 9 синхронизации, Г-на выходе регистра 2 микропрограммного адреса, Д - на выходе блока 3 микропрограммной памяти, Е - на выходе регистра 4 микрокоманд, Ж - на выходе сигнала Переключение процесса дешифратора 5 управляющих микроинструкций, М

-на выходе блока 12 памяти адресов процессов, К- на выходе блока 11 памяти страниц, Л - на выходе первого коммутатора 17, М - на выходе регистра 13 страниц.

Процессор с микропрограммным управлением (фиг. 1) содержит блок 1 формирования микропрограммного адреса, который предназначен для выработки адреса следующей микрокоманды под управляющим воздействием из микрокоманды. Входящий в состав блока 1 (фиг. 3) дешифратор 47 функции управления предназначен для формирования управляющих сигналов, определяемых полем управления адреса микрокоманды. Поле управления адресом поступает на вход дешифратора 47 через второй вход 54 блока 1. Четвертый коммутатор 48 предназначен для формирования следующего адреса микрокоманды по полю управления адресом с учетом выходного переноса арифметико-логического блока 6, поступающего на четвертый вход 56 блока 1 и текущего адреса микрокоманды, поступающего через первый вход 53 блока 1.

Пятый коммутатор 49 предназначен для формирования входного сигнала переноса для арифметико-логического блока 6, выдаваемого на первый выход 58 блока 1, триггер 50 флага - для хранения сигнала переноса арифметико-логического блока 6, шестой элемент И 51 - для формирования адреса следующей микрокоманды из информации, находящейся на шине 33 данных и поступающей через пятый вход 57 блока 1. Седьмой элемент И 52 предназначен для формирования адреса следующей микрокоманды из адреса предшествующей микрокоманды, поступающего через третий вход 55 блока 1 формирования микропрограммного адреса. Выходы коммутатора 48, элементов И 52 и 51 имеют три состояния, адрес следующей микрокоманды выдается на второй выход 59 блока 1.

Регистр 2 микропрограммного адреса предназначен для запоминания на один микрокомандный цикл текущего микропрограммного адреса. Его выход соединен с первым входом блока 1 формирования микропрограммного адреса и с адресным входом блока 3 памяти микрокоманд, обес- 5 печивающего при этом выдачу соответствующей микрокоманды на свой выход.

Регистр 4 микрокоманды предназначен для запоминания на один цикл текущей микрокоманды. Микрокоманда процессора со- 0 держит четыре поля: поле управления адресом, поступающее на второй вход блока 1 формирования микропрограммного ад- ,реса; поле управляющих микроинструкций, поступающее на вход дешифратора 5 управ- 5 ляющих микроинструкций и на третий вход блока 1; поле чтения, поступающее на вход блоков, выходы которых подключены к шине 33 данных, и поле кода операции, поступающее на соответствующий вход арифмети0 ко-логического блока 6.

Дешифратор 5 управляющих микроинструкций предназначен для формирования управляющих сигналов из поля управляющих микроинструкций микрокоманды. Вы5 ходы дешифратора 5 соединены с соответствующими управляемыми элементами процессора.

Арифметико-логический блок 6 предназначен для арифметико-логической обра0 ботки информации, поступающей на два его входа-выхода (информационный и регистровой информации) в соответствии с кодом операции на его входе кода операции. Результат в зависимости от кода операции по5 является на информационном входе-выходе, входе-выходе регистровой информации и выходе адреса блока 6. В соответствии со структурой блока 6 (фиг. 4) дешифратор 60 кода операции предназна0 чен для формирования из синхросигнала и поля кода операции микрокоманды управляющих сигналов для арифметико-логической схемы 61, коммутаторов 63 и 64, регистра 62 результата и выходных управля5 ющих сигналов на синхровыходе 74 для блоков 10 регистровой памяти и управления записью 75 для регистра 7 адреса. Синхросигнал поступает на вход дешифратора 60 через синхровход 67, а код операции - через

0 одноименный вход 66 арифметико-логического блока 6.

Арифметико-логическая схема 61 предназначена для выполнения арифметико-логических операций над операндами,

5 поступающими на ее входы с выходов коммутаторов 63 и 64, с учетом переноса, поступающего через вход 68. Результат операции поступает на выход 71 адреса и, вход-выход 73 регистровой информации и на вход регистра 62 результата. Регистр 62 результата

предназначен для хранения результатов операций, выполняемых арифметико-логической схемой 61, запись в регистр 62 происходит по сигналу с выхода дешифратора 60. Шестой 63 и седьмой 64 коммутаторы предназначены для подачи операндов на входы арифметико-логической схемы 61, Операнды могут поступать либо через информационный вход-выход 70, либо через вход-выход 73 регистровой информации. Управление коммутаторами 63 и 64 осуществляется сигналами с выходов дешифратора 60 кода операции, Пятый шинный формирователь 65 предназначен для выдачи содержимого регистра 62 результата по сигналу на входе 76 чтения на информационный выход 70 арифметико-логического блока 6, выход шинного формирователя 65 имеет три состояния.

Регистр 7 адреса обеспечивает запоминание нового адреса оперативной памяти, полученного на адресном выходе блока 6 как результат текущей операции, при наличии сигнала управления записью на одноименном выходе блока 6, Информационный выход регистра 7 соединен с шиной 34 адреса, Новый адрес оперативной памяти поступает на шину 34 адреса все время до следующей записи информации в регистр 7. Блок 8 оперативной памяти предназначен для хранения промежуточных результатов операций микропрограммного процессора. Блок 8 записывает информацию, появляющуюся на шине 33 данных, по сигналу записи данных, поступающему с одноименного выхода дешифратора 5 управляющих микроинструкций. Блок 8 обеспечивает выдачу информации на шину 33 данных по сигналу чтения, поступающему с выхода чтения регистра 4 микрокоманды. Адрес обращения к блоку 8 соответствует информации на шине 34 адреса. Выход блока 8 имеет три состояния.

Блок 9 синхронизации предназначен для формирования управляющих синхросигналов процессора, генератор 77 синхроимпульсов - для формирования на своем выходе синхропоследовательности прямоугольных импульсов со скважностью два, которая поступает на счетный вход триггера 78 и на первый вход восьмого элемента И 79 (фиг, 5). На второй вход этого элемента поступает сигнал инверсного выхода триггера 78. В результате на выходе восьмого элемента И 79 обеспечивается выработка синхросигналов со скважностью четыре, которые соответствуют первому выходу 80 блока 9 синхронизации (диаграмма А фиг 6) На прямом выходе триггера 78 формируется сигнал, соответствующий второму выходу

81блока 9 (диаграмма Б фиг. 6), на инверсном выходе триггера 78 устанавливается сигнал, соответствующий третьему выходу

82блока 9 (диаграмма В фиг. 6).

Основной и дополнительные блоки 10

регистровой памяти представляют собой сверхоперативную память и организованы в виде страниц. Каждая страница предназначена для хранения в сверхоперативной па0 мяти информации, специфической для одного из процессов - контекста (образа) этого процесса. Ячейки страницы предназначены для хранения результатов промежуточных операций арифметико-логического

5 блока 6.

Каждая страница блока 10 регистровой памяти предназначена для работы с одним из существующих в процессоре процессов, Номер страницы соответствует имени про0 цесса. В зависимости оттого, какой процесс находится на обслуживании в текущий момент, на управляющий вход соответствующей страницы поступает сигнал с выхода дешифратора 14 страниц. Запись информа5 ции в выбранную таким образом страницу производится по сигналу, поступающему с синхровыхода арифметико-логического блока 6 на синхровход страницы. Информация для записи и читаемая информация появля0 ются на информационном входе-выходе страницы, подключенном к входу-выходу регистровой информации арифметико-логического блока 6. Адрес регистра, к которому происходит обращение в странице, опреде5 ляется информацией на выходе адреса регистра арифметико-логического блока 6.

Блок 11 памяти страниц и блок 12 памяти адресов процессов предназначены для хранения информации о существующих

0 процессах в порядке очередности их обслуживания, поэтому адрес доступа всегда устанавливается одинаковым для обоих блоков. При отсутствии на входах записи блоков 11 и 12 памяти соответствующих сиг5 налов осуществляется чтение информации из блоков 11 и 12 по установленному на их адресных входах адресу. Число ячеек блоков 11 и 12, разрядность ячейки блока 11 определяются предельно допустимым чис0 лом существующих процессов. Разрядность ячейки блока 12 памяти определяется разрядностью адреса микрокоманд.

Блок 11 памяти страниц используется для хранения номеров страниц блока 10 ре5 гистровой памяти, предназначенныхдля работы с существующими в процессоре процессами. Номер страницы является именем процесса. Для записи в блок 11 памяти используется информация с шины 33 данных Адрес записи определяется информацией на выходе первого коммутатора 17 и совпадает с адресом записи в блок 12 памяти адресов процессов. Блок 12 памяти адресов процессов обеспечивает хранение пусковых адресов процессов. В отличие от блока 11 информация для записи в блок 12 памяти поступает через второй коммутатор 18 либо с шины 33 данных, либо с выхода блока 3 памяти микрокоманд. Последнее необходимо для обеспечения возврата процесса в адрес, в котором он был снят с обслуживания, при последующей постановке на обслуживание этого процесса. Запись в блоки 11 и 12 происходит всегда раздельно, кроме записи по начальной установке, чтение осуществляется при отсутствии записи.

Регистр 13 страниц предназначен для хранения номера страницы блока 10 регистровой памяти того процесса, который в текущий момент находится на обслуживании в процессоре. На информационный вход регистра 13 поступает информация с выхода блока 11 памяти страниц, запись ее в регистр 13 производится по приходе сигнала на синхровход регистра 13 при постановке на обслуживание нового процесса.

Дешифратор 14 номера страницы предназначен для дешифрации имени процесса с целью включения в работу с процессом требуемой страницы блока 10 регистровой памяти, Вырабатываемый на соответствующем выходе дешифратора 14 сигнал поступает на управляющий выход одной из страниц блока 10 регистровой .

Пересчетная схема 15 предназначена для хранения адреса процесса, находящегося на обслуживании, и хранения числа существующих процессов. Число процессов, находящихся в процессоре, хранится в регистре 45 числа процессов, входящем в состав пересчетной схемы 15 (фиг. 2), и записывается в регистр 45 с шины 33 данных, подключенной к информационному входу 41 пересчетной схемы 15, по сигналу записи числа процессов, поступающему на одноименный вход 40 пересчетной схемы 15 с выхода дешифратора 5 управляющих микроинструкций. Число процессов может быть считано через одноименный выход 37 пересчетной схемы 15. Адрес обслуживаемого в данный момент процесса содержится в счетчике 43 адреса, в который он либо записывается с шины 33 данных, соединенной с информационным выходом 41, либо наращивается на единицу к содержимому счетчика 43, Увеличение адреса на единицу происходит по сигналу переключения процессов, поступающему с одноименного выхода дешифратора 5 управляющих

микроинструкций одновременно с синхросигналом с третьего выхода блока 9 на счетный вход счетчика 43 через вход 38 пересчетной схемы 15. Если число процес- 5 сов в регистре 45 сравняется с содержимым счетчика 43, то схема 46 сравнения выдаст сигнал, устанавливающий счетчик 43 в ноль, что соответствует постановке на обслуживание нулевого процесса.

0 Триггер 16 режима предназначен для обеспечения доступа к информации о процессах, хранящейся в блоках 11 и 12. Управ- .ление триггером 16 режима осуществляется программно с использованием поля управ5 ляющих микроинструкций. В единичном состоянии триггер 16 подключает через первый коммутатор 17 шину 34 адреса к выходам адреса блоков 11 и 12, а через второй коммутатор 18 - шину 33 данных на

0 вход данных блока 12 памяти адресов процессов.

Первый коммутатор 17 предназначен для подключения на адресные входы блоков 11 и 12 информации с шины 34 адреса или с

5 адресного выхода 36 пересчетной схемы 15 в зависимости от сигнала на выходе триггера 16 режима.

Второй коммутатор 18 предназначен для подключения к входу данных информа0 ции с шины 33 данных или выходов блока 3 памяти микрокоманд, соответствующих полю управления адресом микрокоманды, в зависимости от сигнала на выходе триггера 16 режима.

5 Третий коммутатор 19 предназначен для подключения к информационному входу регистра 2 микропрограммного адреса информации с выхода блока 12 памяти адресов процессов или с второго выхода блока 1

0 формирования микропрограммного адреса в зависимости от сигнала на управляющем входе коммутатора 19. На управляющий вход коммутатора 19 сигнал поступает с выхода четвертого элемента ИЛИ 32.

5Первый 20 и второй 21 шинные формирователи предназначены для выдачи на шину 33 данных информации соответственно об имени и пусковом адресе обслуживаемого процесса с выходов блоков 11 и 12. Уп0 равление шинными формирователями осуществляется полем чтения микрокоманды, выходы шинных формирователей 20 и 21 имеют три состояния.

Третий 22 и четвертый 23 шинные фор5 мирователи предназначены для выдачи на шину 33 данных соответственно адреса процесса, находящегося на обслуживании, с выхода 36 пересчетной схемы 15 и числа существующих процессов с выхода 37 пересчетной схемы 15. Управление или ыми

формирователями осуществляется полем чтения микрокоманды, выходы шинных формирователей 22 и 23 имеют три состояния.

Первый 24 и второй 25 элементы И предназначены соответственно для формирования сигналов записи для блоков 11 и 12 из синхросигнала с второго выхода блока 9 синхронизации в зависимости от сигналов на их первых входах, третий элемент И 26 - для формирования сигнала, поступающего на счетный вход 38 пересчетной схемы 15, из синхросигнала с третьего выхода блока 9 синхронизации из сигнала переключения процессов с одноименного выхода дешифратора 5 управляющих микроинструкций.

Четвертый элемент И 27 предназначен для формирования сигнала, поступающего на синхровход регистра 13 страницы, из сигнала с первого выхода блока 9 синхронизации в зависимости от сигнала на первом входе элемента 27, пятый элемент И 28 - для формирования сигнала, поступающего на вход 39 записи числа процессов пересчетной схемы 15, из сигнала с третьего выхода блока 9 синхронизации и сигнала записи адреса пересчетной схемы с одноименного выхода дешифратора 5 управляющих микроинструкций.

Первый элемент ИЛИ 29 предназначен для формирования сигнала для подачи на первый вход второго элемента И 25, означающего, что в блок 12 памяти адресов процессов должна осуществиться запись информации, второй элемент ИЛИ 30 - для формирования сигнала для подачи на первый вход первого элемента И 24, означающего, что в блок 11 памяти страниц должна осуществиться запись информации.

Третий элемент ИЛИ 31 предназначен для формирования сигнала для подачи на первый вход третьего элемента И 27, означающего, что в регистр 13 страниц должна осуществиться запись информации, четвертый элемент ИЛИ 32 - для формирования сигнала для подачи на управляющий вход четвертого коммутатора 19.

Процессор работает следующим образом.

На обслуживании в процессоре всегда находится не менее одного процесса. Процессы имеют имена, совпадающие с адресами страниц блока 10 регистровой памяти и хранящиеся в блоке 11 памяти страниц Каждый процесс снабжается информацией о себе в виде своего имени (номера страницы блока 10 регистровой памяти) и начального микропрограммного адреса. Процессы организованы в циклическую очередь Порядок в очереди определяется порядком

следования адресов ячеек блоков 11 и 12, в которых записана информация о процессах. Порядок обслуживания пррцессов -т(рсле- довательно по адресам ячеек блоков 1%и 12,

хранящих информацию о процессах. Цикличность обслуживания процессов обеспечивается постановкой на обслуживание процесса с нулевым адресом после снятия с обслуживания процесса со старшим в оче0 реди адресом.

При постановке процесса на обслуживание он должен быть обеспечен доступом к именной странице блока 10 регистровой памяти и снабжен своим начальным микро5 программным адресом в качестве адреса первой микрокоманды. Адрес ячеек блоков 11 и 12, содержащих информацию о находящемся на обслуживании процессе, и число процессов, существующих в процессоре,

0 хранится в пересчетной схеме 15. Предельно допускаемое количество процессов, находящихся в процессоре, определяется разрядностью ячейки памяти блока 11 памяти страниц и соответствующей ей разрядно5 стью регистра 13 страниц. Обязательный для нахождения в процессоре процесс - нулевой, который обеспечивает обслуживание остальных процессов и порождается в микропрограммном процессоре сигналом на0 чальной установки. Кроме того, в процессоре предусмотрено выполнение следующих операций с процессами: порождение новых процессов (в рамках из предельно допускаемого количества), чтение

5 информации о любом процессе и пересчетной схеме 15, постановка процесса на обслуживание, уничтожение процесса путем подтягивания.

Порождение в микропрограммном про0 цессоре нулевого процесса происходит путем подачи в процессор сигнала начальной установки через вход 35. Этот сигнал поступает через четвертый элемент И 32 на управ- ляющий вход третьего коммутатора 19,

5 через третий элемент ИЛИ 31 на первый вход элемента И 27, через второй элемент ИЛИ 30 - на первый вход первого элемента И 24, через первый элемент ИЛИ 29 - на первый вход элемента И 25, на вход началь0 ной установки регистра 7 адреса, на вход 42 начальной установки пересчетной схемы 15 и на вход асинхронной установки в единичное состояние триггера 16 режима. В результате, регистр 7 адреса устанавливается

5 в нулевое состояние, счетчик 43 адреса {фиг. 2) пересчетной схемы 15 - в нулевое состояние, а на выходе триггера 16 появляется сигнал, поступающий на управляющие входы первого 17 и второго 18 коммутаторов соответственно. Тем самым первый коммутатор 17 обеспечивает подключение шины 34 адреса к адресным входам блоков 11 и 12, второй коммутатор 18 подключает шину 33 данных к входу данных блока 12 памяти адресов.процессов.

Шина 33 данных электрически имеет два состояния, хотя к ней подключены выходы элементов, имеющие три состояния. Это объясняется специальным включением резисторов, доопределяющих третье состоя- ние на шине 33 до нулевого потенциала. К шине 33 данных в момент начальной установки не подключен ни один из источников информации, и электрический потенциал на ней равен нулю. Поэтому при поступлении сигналов записи на входы записи блоков 11 и 12 в последние запишутся нули. Сигналы записи для блоков 11 и 12 вырабатываются в момент единичного потенциала на втором выходе блока 9 синхронизации, котор ый по- ступает на вторые входы элементов И 24 и 25, и снимаются с выходов этих элементов, В результате сигнал записи поступает на вход записи блока 11 памяти адресов процессов с выхода второго элемента И 25 и на вход записи блока 12 памяти страниц - с выхода первого элемента И 24.

Адрес записи определяется информацией, находящейся на шине 34 адреса. Информация на шине 34 адреса определяется информацией, находящейся в регистре 7 адреса, в котором по сигналу начальной установки появляются нули. Следовательно, нулевая информация с шины 33 данных записывается в блоки 11 и 12 по нулевому адресу. Это соответствует порождению нулевого процесса. Как только оканчивается существование сигналов-записи на выходах первого 24 и второго 25 элементов И, блоки 11 и 12 включаются в режим чтения. На выходе блока 11 памяти страниц появляется номер страницы блока 10 регистровой памяти, соответствующий порожденному процессу. Этот номер запишется в регистр 13 страниц по приходу на второй вход четвер- того элемента И 27 сигнала с первого выхода блока 9 синхронизации, поскольку на первый вход элемента И 27 поступает сигнал начальной установки с выхода третьего элемента ИЛИ 31.

Информация, записанная в регистр 13 страниц, поступает на вход дешифратора 14 номера страниц. Появившийся на одном из его выходов сигнал поступает на вход уп- равления соответствующего блока 10 регистровой памяти и включает его в работу. В это же время блок 12 памяти адресов процессов тоже включается в режим чтения и на его выходе появляется информация о

первом микропрограммном адресе порожденного процесса. Эта информация поступает через соответствующе подключенный третий коммутатор 19 на информационный вход регистра 2 микропрограммного адреса, в который и записывается по приходу на синхровход регистра 2 синхросигнала с первого выхода блока 9 синхронизации. После этого начальная установка считается завершенной, и одноименный сигнал с выхода 35 снимается.

Далее начинается работа микропрограммного процессора в режиме выполнения микропрограмм порожденного, в данном случае нулевого, процесса. Загруженный адрес микрокоманды с выхода регистра 2 поступает на вход адреса блока 3 памяти микрокоманд, на выходе которого появляется парвая считанная микрокоманда. Микрокоманда данного процессора состоит из четырех полей микроинструкций: поля управления адресом следующей микрокоманды, поля управляющих микроинструкций, поля чтения, поля кода операций. Каждая микрокоманда с выхода блока 3 памяти микрокоманд подается на вход регистра 4 микрокоманд и записывается в него по приходу на его синхровход синхросигнала с первого выхода блока 9 синхронизации. Одна из первых микрокоманд нулевого про- цесса должна содержать в поле управляющих микроинструкций код микроинструкции Снятие режима доступа. Управляющий сигнал, соответствующий данному коду, после подачи этого кода на вход дешифратора 5 управляющих микроинструкций с выхода регистра 4 микрокоманд появляется на одноименном выходе дешифратора 5 и далее поступает на синхронный вход установки в ноль триггера 16 режима. Триггер 16 установится в ноль по приходу на его синхровход синхросигнала с первого выхода блока 9 синхронизации.

Следующая микрокоманда должна обеспечивать запись в пересчетную схему 15 информации о числе процессов, состоящих на обслуживании. Для этого поле кода операции предыдущей микрокоманды должно содержать код, формирующий соответствующую информацию на информационном выходе арифметико-логического блока 6. Последующая микрокоманда должна в поле чтения содержать код, разрешающий чтение информации на шину 33 данных с информационного выхода арифметики . -о- гического блока 6, а в поле управляющих микроинструкций последующая микрокоманда должна содержать код микроинструкций записи числа про весов в пересчетную схему (фиг. 2). Информация о

числе процессов с шины 33 данных поступает на информационный вход 41 пересчетной схемы 15, а управляющий сигнал записи подается с выхода Запись числа процессов в пересчетную схему дешифратора 5 управляющих микроинструкций на вход 40 записи числа процессов пересчетной схемы 15. Причем сигнал записи поступает на вход регистра 45 числа процессов и обеспечивает запись в него информации с шины 33 данных. После выполнения этих обязательных микрокоманд процессор может выполнять любые микрокоманды, обусловленные находящимся на обслуживании процессом. Аналогично порождению нулевого процесса происходит порождение и последующих процессов. Отличие состоит в том, что, во-первых, триггер 16 режима устанавливается в единичное состояние синхронно при поступлении на его вход установки сигнала Установка режима с соответствующего выхода дешифратора 5 управляющих микроинструкций и на его синхровход синхросигнала с первого выхода блока 9 синхронизации. Сигнал Установка режима появляется на одноименном выходе дешифратора 5 при поступлении на вход дешифратора 5 соответствующего кода из поля управляющих микроинструкций с выхода регистра 4 микрокоманды.

Во-вторых, запись информации о номере страницы и адресе процесса в блоки 11 и 12 соответственно осуществляется раздельно путем выполнения двух микрокоманд. В первой микрокоманде соответствующий код в поле кода операции обеспечивает появление информации, соответствующей номеру страницы порождаемого процесса, на информационном выходе арифметико-логического блока 6. Во второй микрокоманде соответствующий код в поле чтения обеспечивает выдачу этой информации на шину 33 данных, а код в поле управляющих микроинструкций обуславливает появление на выходе Запись страницы дешифратора 5 одноименного сигнала. Этот сигнал через второй элемент ИЛИ 30 поступает на первый вход первого элемента И 24 и разрешает прохождение через второй вход этого элемента сигнала с второго выхода блока 9 синхронизации на вход записи блока 11 памяти страниц.

Таким образом, осуществляется запись информации с шины 33 данных в блок 11 памяти страниц. Вторая пара микрокоманд аналогично обеспечивает запись начального адреса порождаемого процесса в блок 12 памяти адресов процессов В первой микрокоманде соответствующий код в поле кода операции обеспечивает появление информации, определяющей начальный микропрограммный адрес порождаемого процесса, на информационном выходе арифметико-логического блока 6. Во второй

микрокоманде соответствующий код в поле чтения обеспечивает выдачу этой информации на шину 33 данных, а код в поле управляющих микроинструкций Обуславливает появление на выходе Запись адреса дешифратора 5 одноименного сигнала. Этот сигнал через первый элемент ИЛИ 29 поступает на первый вход первого элемента И 25 и разрешает прохождение через второй вход этого элемента сигнала с второго выхо5 да блока 9 синхронизации на вход записи блока 12 памяти адресов процессов.

В-третьих, адрес записи в блоки 11 и 12 определяется в арифметико-логическом блоке 6 и появляется на его выходе адреса.

0 В следующей микрокоманде этот адрес записывается в регистр 7 адреса путем подачи его на информационный вход регистра 7 и выработке согласно коду операции сигнала Управление записью, поступающего на

5 вход синхронизации регистра 7 адреса. Этот адрес с выхода регистра 7 выдается на шину 34 адреса и с нее поступает на адресные входы блоков 11 и 12 через подключенный соответствующим образом с помощью

0 триггера 16 режима первый коммутатор 17. Численно адрес записи информации о порождаемом процессе равен адресам первых пустых ячеек в блоках 11 и 12, Поскольку запись в блоки 11 и 12 всегда производится

5 по одинаковым адресам, то и адреса первых пустых ячеек в этих блоках совпадают По абсолютной величине адрес первых пустых ячеек в блоках 11 и 12 соответствует содержимому регистра 45 числа процессов (фиг.

0 2), так как отсчет числа процессов, находящихся в процессоре, начинается с единицы, адрес записи начального (нулевого) процесса является нулевым, а запись производится по последовательным адресам. Получение

5 информации об адресе первой пустой ячейки в блоках 11 и 12 осуществляется выполнением операции чтения.

Операция чтения осуществляет выдачу на шину 33 данных информации о процессе,

0 хранящемся по произвольному адресу в блоках 11 и 12, и чтение информации о пересчетной схеме 15. Операция чтения реализуется с использованием поля чтения микрокоманды. Поле чтения микрокоманды

5 имеет унитарное кодирование и поскольку обеспечивает чтение с шести устройств, то имеет шесь разрядов. Шестью устройствами, обслуживаемыми полем чтения, являются информационный двунаправленный выход арифметико-логического блока 6 информационный двунаправленный выход блока 8 оперативной памяти и, соответственно, первый 20, второй 21, третий 22 и четвертый 23 шинные формирователи. Каждый разряд поля чтения соединен с одним из перечисленных устройств. При необходимости чтения из любого из этих устройств в поле чтения содержится единица в разряде, соединенном с требуемым устройством.

Чтение информации о процессе проис- ходит при выполнении следующей последо- вательности микрокоманд, В первой микрокоманде в поле управляющих микроинструкций должен содержаться код, обеспечивающий формирование сигнала Установка режима на одноименном выходе дешифратора 5 управляющих микроинст- рукций. Сигнал Установка режима поступает на вход синхронной установки триггера 16 режима в единичное состояние, и по приходу на синхровход триггера 16 синхросигнала с первого выхода блока 9 синхронизации на выходе фиггера 16 устанавливается единичный сигнал. О н поступает на управляющие входы первого 17 и второго 18 коммутаторов соответственно. По получении этого сигнала первый коммутатор 17 обеспечит подключение шины 34 адреса к адресным входам блоков 11 и 12 памяти страниц и адресов процессов соот- ветственно. Коммутатор 18 подключит шину 33 данных к входу данных блока 12 памяти адресов процессов.1

Во второй микрокоманде в поле кода операции должен содержаться код, обеспе- чивающий формирование адреса чтения ин- формации на адресном и сигнала управления записью на одноименном выходах арифметико-логического блока 6. Наличие этих сигналов на соответствующих входах регистра 7 адреса обеспечит запись сформированного адреса чтения информации в регистр 7, и с выхода последнего адрес чтения информации о процессе поступит на шину 34 адреса. Кроме того, в поле чтения второй микрокоманды должен содержаться код, обеспечивающий чтение информации с выхода шинного формирователя 20 на шину 33 данных. На информационный вход шинного формирователя 20 поступает информация с выхода блока 11 памяти, читаемая в этот момент из ячейки, адрес которой определен шиной 34 адреса, т.е. содержится в регистре 7 адреса.

Для потребления считанной таким об- разом информации в поле управляющих микроинструкций этой же микрокоманды должен находиться код, позволяющий дешифратору 5 управляющих микроинструкций выработать сигнал на своем

соответствующем выходе сигнал Запись в блок оперативной памяти. По этому сигналу, поступающему на вход записи блока 8 оперативной памяти, произойдет запись информации с шины 33 данных по тому же адресу, по которому эта информация считана из блока 11 памяти страниц. Это один из возможных способов потребления считанной о процессе информации. Аналогичным образом считывается и информация об адресе процесса из блока 12 памяти адресов процессов. В третьей микрокоманде, если считанная информация потреблена и не требуется чтения информации из других устройств, в поле управляющих микроинструкций должен содержаться код микроинструкции для формирования на соответствующем выходе дешифратора 5 сигнала Снятие режима. По этому сигналу триг эр 16 режима установится в нулевое состояние, а в микропрограммном процессоре на обслуживании останется прежний процесс, адрес которого определен адресным выходом 36 пересчетной схемы.

Чтением информации из пересчетной схемы можно вывести на шину 33 данных адрес процесса, находящегося в данный момент на обслуживании, и число существующих в процессоре процессов. Для этого нужно изложенным выше способом первой микрокомандой установить триггер 16 режима в единичное состояние. Вторая микрокоманда должна содержать в поле чтения код, соответствующий чтению либо информации с выхода шинного формирователя 22, либо информации с выхода шинного формирователя 23. Соответственно, на шине 33 данных в первом случае появится адрес процесса, находящегося на обслуживании, поскольку к информационному входу шинного формирователя 22 подключен адресный выход 36 пересчетной схемы. Во втором случае на шине 33 данных появится число процессов, существующих в процессоре, так как к информационному входу шинного формирователя 23 подключен выход 37 Число процессов пересчетной схемы 15. Потребление информации с L ины 33 данных осуществляется третьей микрокомандой либо указанным выше способом блоком 8 оперативной памяти, либо арифметико-логическим блоком 6 при условии содержания в поле кода операции третьей микрокоманды соответствующего кода, обеспечивающего запись информации с шины 33 данных через информационный вход в арифметико-логический блок 6.

Постановка процесса на обслуживание возможна двумя способами: циклически по очереди и произвол( но, по указанному адресу ячеек блоков 11 и 12 соответственно страниц и адресов процессов, хранящих информацию о процессе.

Операция постановки процесса на обслуживание циклически по очереди выполняется последовательностью из двух микрокоманд (диаграммы на фиг, 6), появляющимися последними в предыдущем процессе. В первой микрокоманде, адрес которой находится в регистре 2 микропрограммного адреса и которая считывается из блока 3 памяти микрокоманд (очку 1 диаграммы Г и Д фиг. 6), в поле управляющих микроинструкций содержится код микроинструкции Переключение процессов. В момент чтения этой микрокоманды из блока 3 памяти микрокоманд адресный выход 36 пересчетной схемы (диаграмма Л фиг. 6) через первый коммутатор 17 соединен с адресными входами блоков 11 и 12. Читаемая из этих блоков информация относится к старому, находящемуся на обслуживании, процессу. С выхода блока 11 считывается адрес старого процесса (диаграмма И фиг. 6), с выхода блока 12 - номер страницы (имя) старого процесса (диаграмма К фиг. 6). В регистре 13 страниц хранится имя старого процесса (диаграмма М фиг. 6). С появлением на первом выходе блока 9 очередного синхросигнала (диаграмма А фиг. 6) первая микрокоманда записывается в регистр 4 микрокоманды (диаграмма Е фиг, 4), поле управляющих микроконструкций поступает на вход дешифратора 5, и на его выходе появляется сигнал Переключение процесса (диаграмма Ж фиг. 6). Этот сигнал поступает через четвертый элемент ИЛИ 32 на управляющий вход третьего коммутатора 19 и подключает выход блока 12 памяти адресов процессов к входу регистра 2 микропрограммной адреса. Кроме того, сигнал Переключение процессов через третий элемент ИЛИ 31 поступает на первый вход четвертого элемента И 27, через первый элемент ИЛИ 29 на первый вход второго элемента И 25 и на первый вход третьего элемента И 26.

На выходе регистра 2 микропрограммного адреса в этот момент уже находится адрес второй микрокоманды (точка 2, диаграмма Г фиг. 6), которая считывается с выхода блока 3 памяти микрокоманд. Выход блока 3 частью разрядов, соответствующих полю управления адресом микрокоманды, подключен к входу данных блока 12 памяти адресов процессов через второй коммутатор 18, По приходу на вход записи блока 12 памяти сигнала записи с второго выхода блока 9 синхросигналов через второй вход элемента И 25 в блок 12 запишется информация из разрядов поля управления адресом микрокоманды, определяющих новый начальный адрес (точку возврата) для старого процесса (диаграммы Б, Д, Ж, И фиг. 6). В

следующий момент времени появляется единичный сигнал на третьем выходе блока 9 синхронизации (диаграмма Б фиг. 6). Он поступает на второй вход элемента И 26, на первом входе которого присутствует сигнал

0 Переключение режима, поэтому с выхода элемента И 26 на счетный вход 38 пересчетной схемы 15 приходит сигнал. Этот сигнал (фиг, 2) поступает на счетный вход счетчика 43 адреса, который по нему увеличивает

5 свое содержимое на единицу. Новый адрес появляется на выходе 36 пересчетной схемы и на первом входе схемы 44 сравнения

На второй вход схемы 44 сравнения подается информация с выхода регистра 45

0 числа процессов. Если новый адрес процесса совпадает с числом процессов, хранящихся в регистре 45, то схема 44 сравнения вырабатывает сигнал. Этот сигнал поступает через пятый элемент ИЛИ 46 на вход

5 установки в ноль счетчика 43 адреса, что означает, что очередь процессов обслужена, и на обслуживание вновь ставится нулевой процесс. В любом случае на выходе 36 адреса пересчетной схемы 15 появляется

0 новый адрес: нулевой или превышающий на единицу адрес старого процесса (диаграмма Л фиг. 6). Этот адрес поступает через первый коммулатор 17 на адресные входы блоков 11 и 12, с которых начинается считы5 вание соответственно значений имени (номера страницы) и начального адреса (точки возврата) нового процесса (диаграммы И и К фиг. 6) Номер страницы нового процесса, считываемый с выхода блока 11 памяти

0 страниц, поступает на информационный вход регистра 13 страниц и запишется в этот регистр 13 по приходу на синхровход регистра 13 очередного синхросигнала с первого выхода блока 9 синхронизации

5 (диаграммы А, К, М фиг. 6).

С выхода регистра 13 страниц информация поступает на вход дешифратора 14 номера страницы. Формирующийся сигнал на одном из выходов дешифратора 14 подается

0 на управляющий вход соответствующей страницы блока 10 регистровой памяти, и данная страница оказывается включенной в работу. Начальный адрес нового процесса, считываемый с выхода блока 12 памяти ад5 ресов процессов, поступает через соответственно подключенный третий коммутатор 19 на информационный вход регистра 2 микропрограммного адреса и запишется в этот регистр 2 по приходу на его синхровход очередного синхросигнала с первого выхода блока 9 синхронизации (диаграмма А и Г фиг. 6). В результате, на адресный вход блока 3 памяти микрокоманд поступит начальный адрес нового процесса, первая микрокоманда которого начнет считываться с выхода блока 3 памяти микрокоманд (диаграммы Г, Д, точка 3 фиг. 6). Следующим синхросигналом с первого выхода блока 9 синхронизации первая микрокоманда нового процесса записывается в регистр 4 микрокоманд (точка 4, диаграмма Е фиг. 6) и начинается ее выполнение. Новый процесс считается поставленным на обслуживание.

Постановка процесса на обслуживание не по опереди, а по адресу записи информации об sffcM процессе в блоках 11 и 12 происходит аналогично постановке на обслуживание по очереди и описывается теми же диаграммами (фиг. 6), считая, что на диаграмме Ж фиг. 6 показан сигнал на выходе Запись адреса в пересчетную схему дешифратора 5 управляющих микроинструкций, и код микроинструкции Запись адреса в пересчетную схему содержится в поле управляющих микроинструкций первой микрокоманды вместо кода микроинструкции Переключение процессов.

Кроме того, в первой микрокоманде в поле кода операции должен содержаться код, обеспечивающий появление на информационном выходе арифметико-логического блока 6 адреса процесса, берущегося на обслуживание, в поле чтения - код чтения информационного выхода арифметико-логического блока 6 на шину 33 памяти. Тогда сигнал Запись адреса в пересчетную схему появляется на одноименном выходе дешифратора 5 и поступает через первый элемент ИЛИ 29 на первый вход второго элемента И 25 и на первый вход пятого элемента И 28 (точка 2, диаграмма Ж фиг. 6). Сигнал с выхода этого элемента И 28 появится и поступит на вход 39 записи адреса пересчетной схемы 15 в момент появления единичного сигнала на третьем выходе блока 9 синхронизации. Этот сигнал поступает на вход записи счетчика 43 адреса (фиг, 2) и осуществляет запись информации с информационного входа 41 пересчетной схемы, подключенного к шине 33 данных, на которой в этот момент находится адрес нового процесса. В остальном процедура постановки нового процесса на обслуживание полностью совпадает с предыдущей.

Операция уничтожения процесса подтягиванием выполняется с помощью операций чтения информации о процессе и порождения нового процесса. При необходимости уничтожить некоторый процесс, находящийся в циклической очереди в микропрограммном процессоре,требуется сначала указанным выше способом установить триггер 16 режима в единичное состояние. Затем выполнить операцию чтения имени и 5 адреса процесса, информация о котором записана в блоках 11 и 12 памяти по адресу, следующему за адресом, по которому в блоках 11 и 12 записана информация об уничтожаемом процессе.

0 Далее производится операция порождения считанного только что процесса по адресу уничтожаемого процесса. После этого адрес чтения увеличивается на единицу относительно адреса, по которому выполня5 лась предыдущая операция чтения, и осуществляется операция порождения процесса, считанного вторым, по адресу процесса, считанного первым. Процедура чтения информации о процессе по последующему ад0 ресу и порождения этого процесса по предыдущему адресу продолжается до перезаписи всех процессов, следовавших в очереди за уничтожаемым процессом. После этого триггер 16 режима переводится в

5 нулевое состояние, а в пересчетную схему 15 записывается новое, уменьшенное на единицу число процессов, существующих в процессоре.

Формула изобретения

0 Процессор с микропрограммным управлением, содержащий блок формирования микропрограммного адреса, регистр микропрограммного адреса, блок памяти микрокоманд, регистр микрокоманды,

5 дешифратор управляющих микроинструкций, арифметико-логический блок, регистр адреса, блок оперативной памяти, блок синхронизации, основной блок регистровой памяти, причем выход регистра микропрог0 раммного адреса соединен с первым входом блока формирования микропрограммного адреса и с входом адреса блока памяти микрокоманд, выход которого соединен с информационным входом регистра

5 микрокоманды, синхровход которого соединен с синхровходом арифметико-логическо- . го блока, с синхровходом регистра микропрограммного адреса и с первым выходом блока синхронизации, выход управ0 ления адресом регистра микрокоманды соединен с вторым входом блока формирования микропрограммного адреса, выход управляющих микроконструкций регистра микрокоманды соединен с третьим входом

5 блока формирования микропрограммного адреса и с входом дешифратора управляющих микроинструкций, выход чтения регистра микрокоманды соединен с входом чтония блока оперативной памяти, вход записи которого соединен с выходом записи данных

дешифратора управляющих микроинструкций, первый выход блока формирования микропрограммного адреса соединен с входом переноса арифметико-логического блока, выход переноса которого соединен с четвертым входом блока формирования микропрограммного адреса, пятый вход которого соединен с выходом блока оперативной памяти и с информационным входом арифметико-логического блока, вход кода операции которого соединен с одноименным выходом регистра микрокоманды, выход адреса арифметико-логического блока соединен с информационным входом регистра адреса, синхровход которого соединен с выходом управления записью арифметико-логического блока, синхровыход которого соединен с синхровходом основного блока регистровой памяти, информационный вход-выход которого соединен с входом-выходом регистровой информации арифметико-логического блока, выход адреса регистра которого соединен с входом адреса основного блока регистровой памяти, отличающийся тем, что, с целью повышения производительности за счет уменьшения времени при переключении с процесса на процесс в мультипрограммном режиме работы, в него введены дополнительные блоки регистровой памяти, блок памяти страниц, блок памяти адресов процессов, регистр страниц, дешифратор страниц, пересчетная схема, триггер режима, первый, второй и третий коммутаторы, первый, второй, третий и четвертый шинные формирователи, первый, второй, третий, четвертый и пятый элементы И, первый, второй, третий и четвертый элементы ИЛИ, причем синхровходы дополнительных блоков регистровой памяти соединены с синхровыходом арифметико-логического блока, выход адресов регистров которого соединен с адресными входами дополнительных блоков регистровой памяти, инфор- мационные входы-выходы которых соединены с входом-выходом регистровой информации арифметико-логического блока, информационный вход которого является одновременно информационным выходом и соединен с информационным входом блока оперативной памяти, который является его информационным выходом, соединенным с шиной данных, с которой соединены информационный вход пересчетиой схемы, выходы соответственно первого, второго, третьего и четвертого шинных формирователей, первый информационный вход второго коммутатора и вход данных блока памяти страниц, выход которого соединен с информационными входами первого блока шинных формирователей и регистра страниц, выход которого соединен с входом дешифратора страниц, выходы которого соединены соответственно с управляющим входами основного и дополнительных блоков регистровой памяти, адресный выход пересчетной схемы соединен с информационным входом третьего шинного формирователя и с первым инфор0 мационным входом первого коммутатора, выход которого соединен с адресными входами блока памяти страниц и блока памяти адресов процессов, выход которого соединен с информационным входом второго

5 шинного формирователя и с первым информационным входом третьего коммутатора, виход которого соединен с информационным входом регистра микропрограммного адреса, второй информационный вход

0 третьего коммутатора соединен с вторым выходом блока формирования микропрограммного адреса, управляющий вход третьего коммутатора соединен с выходом четвертого элемента ИЛИ, первый вход ко5 торого соединен с входом начальной установки процессора, с первым входом третьего элемента ИЛИ, с единичным входом триггера режима, с входом начальной установки регистра адреса, с первым вхо0 дом второго элемента ИЛИ, с входом начальной установки пересчетной схемы и с первым входом первого элемента ИЛИ выход которого соединен с первым входом второго элемента И, выход которого соеди5 нен с входом записи блока памяти адресов процессов, вход данных которого соединен с выходом второго коммутатора, второй информационный вход которого соединен с выходом блока памяти микрокоманд, управ0 ляющий вход второго коммутатора соединен с выходом триггера режима и с управляющим входом первого коммутатора, второй информационный вход которого соединен с шиной адреса, с которой соединен

5 выход регистра адреса и вход адреса блока оперативной памяти, вход чтения которого соединен с входом чтения арифметико-логического блока и с управляющими входами соответственно первого, второго, третьего и

0 четвертого шинных формирователей, информационный вход которого соединен с выходом Число процессов пересчетной схемы, счетный вход которой соединен с выходом третьего элемента И, первый вход

5 которого соединен с вторыми входами соответственно первого, третьего и четвертого элементов ИЛИ и с выходом переключения процессов дешифратора управляющих микроинструкций, выход установки режима которого соединен с вторым единичным

установочным входом триггера режима, нулевой установочный вход которого соединен с выходом снятия режима дешифратора управляющих микроинструкций, выход записи страниц которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выход которого соединен с входом записи блока памяти страниц, второй вход первого элемента И соединен с вторым входом второго элемента И и с вторым выходом блока синхронизации, третий выход которого соединен с вторым входом третьего элемента И и с первым входом пятого элемента И, выход которого соединен с входом записи адреса пересчетной схемы, вход записи числа процессов которой соединен с

одноименным выходом дешифратора управляющих микроинструкций, выход записи адреса пересчетной схемы которого соединен с вторым входом пятого элемента И, с третьим входом третьего элемента ИЛИ, с третьим входом четвертого элемента ИЛИ и с третьим входом первого элемента ИЛИ, четвертый вход которого соединен с выходом записи адреса процесса дешифратора управляющих микроинструкций, выход третьего элемента ИЛИ соединен с первым входом четвертого элемента И, выход которого соединен с синх- ровходом регистра страниц, второй вход четвертого элемента И соединен с первым выходом блока синхронизации и с синх- ровходом триггера режима.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство обработки информации | 1986 |

|

SU1451710A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммный процессор | 1986 |

|

SU1462339A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Процессор | 1984 |

|

SU1246108A1 |

Изобретение относится к цифровой вычислительной технике, а именно к высокопроизводительным микропрограммным процессорам в ЭВМ и вычислительным системам. Целью изобретения является повышение производительности за счет уменьшения времени при переключении с процесса на процесс в мультипрограммном режиме работы. Поставленная цель достигается тем, что процессор с микропрограм- мным управлением содержит блок 1

СТ2

W

л /

46

39

W

«

а

чч

(LG

№

W

37

О

Фие.2

Фиг.З

Фиг.5

,AJ

П

H

XI

Раг в

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Тотье Р | |||

| Руководство по операционной системе | |||

| - М.: Финансы и статистика, 1985, с.232. | |||

Авторы

Даты

1991-12-23—Публикация

1990-02-21—Подача