4

СО

сд

00

о

4

3149

Изобретение относится к вычислительной технике и может быть использовано при построении общей оперативной памяти блочного типа большой информационной ем1сости многомикрома- шинных вычислительных систем.

Целью изобретения является расширение области применения за счет рас пшнения адресного пространства об- щего поля памяти.

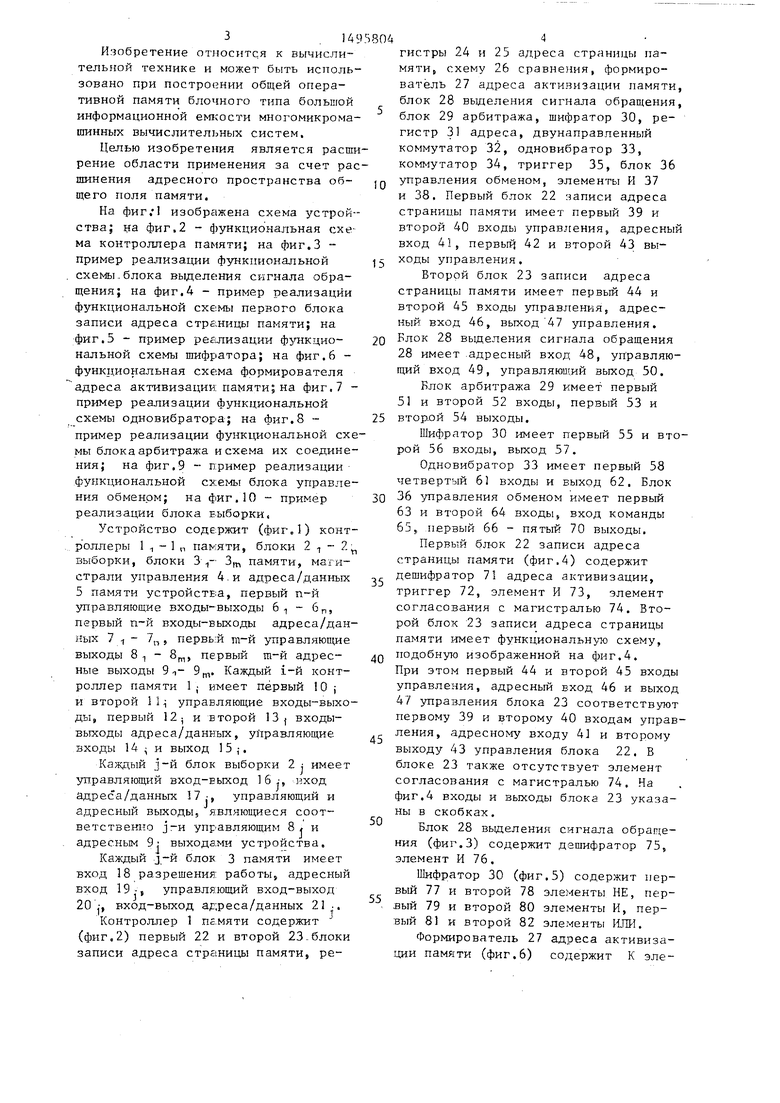

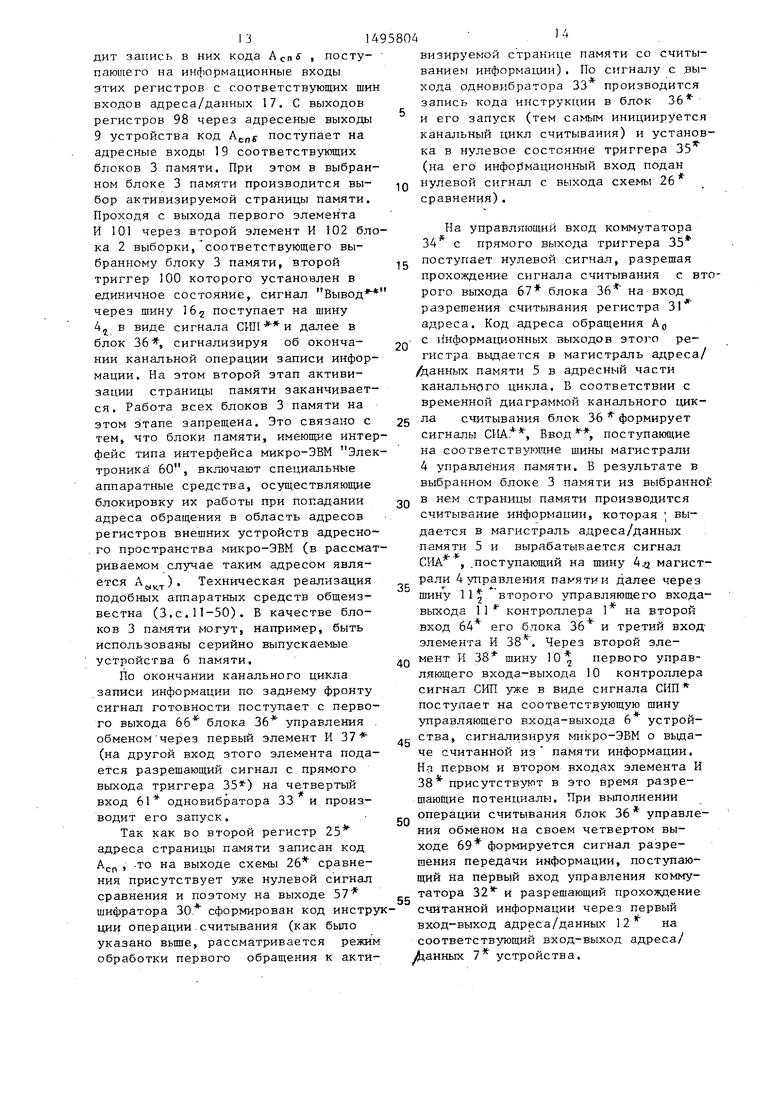

На фиг. 1 изображена схема устройства; фиг.2 - функциональная схема контроллера памяти; на фиг.З - пример реализации функпиор альной схемы-блока выделе ния сигнала обращения; на фиг,4 - пример реализации функциональной схе:мы первого блока записи адреса памяти; на фиг,5 - пример регшизации налъной схемы шифратора; на фиг,6 - функциональная схема формирователя адреса активизации памяти; на фиг,7 - пример реализации функциональной схемы одновибратор1а; на фиг,8 - пример реализации функциональной схемы блока арбитража и схема их соединения; на фиг,9 - пример реализации функциональной схемы блока управления обменом; на фиг,10 - пример реализации блока ЕЪ1борки,

Устройство соде;ржит () контроллеры 1 1 - 1 п , блоки 2 - 2. выборки, блоки 3 памяти, магистрали управления 4. и адреса/данных 5 памяти устройстЕ;а, первый п-й управляющие входы-выходы 6 - бр, первый входы-выходы адреса/данных 7 1 - 7„5 первьй т-й управляющие выходы 8 - 8f, первый т-й адрес- ные выходы 91- 9, Каждый i-й контроллер памяти 1; имеет первый 10 j и второй lii управляющие входы-выходы, первый 12 и второй 13) входы- выходы адреса/данных, управляющие входы 14 и выход 15;,

Каждый j-й блок выборки 2 j имеет управлягощий вход-выход 16;, нход адреса/данных 57;, управляющий и адресный выходы, я;вляющиеся соответственно j-и упр-авляющим 8 / и адресным 9; выходами устройства.

Каждый j.-й блок 3 памяти имеет вход 18 разрешения: работы, адресный вход 19-5 управля:ющий вход-выход 20;, вход-выход адреса/данных 21 .,

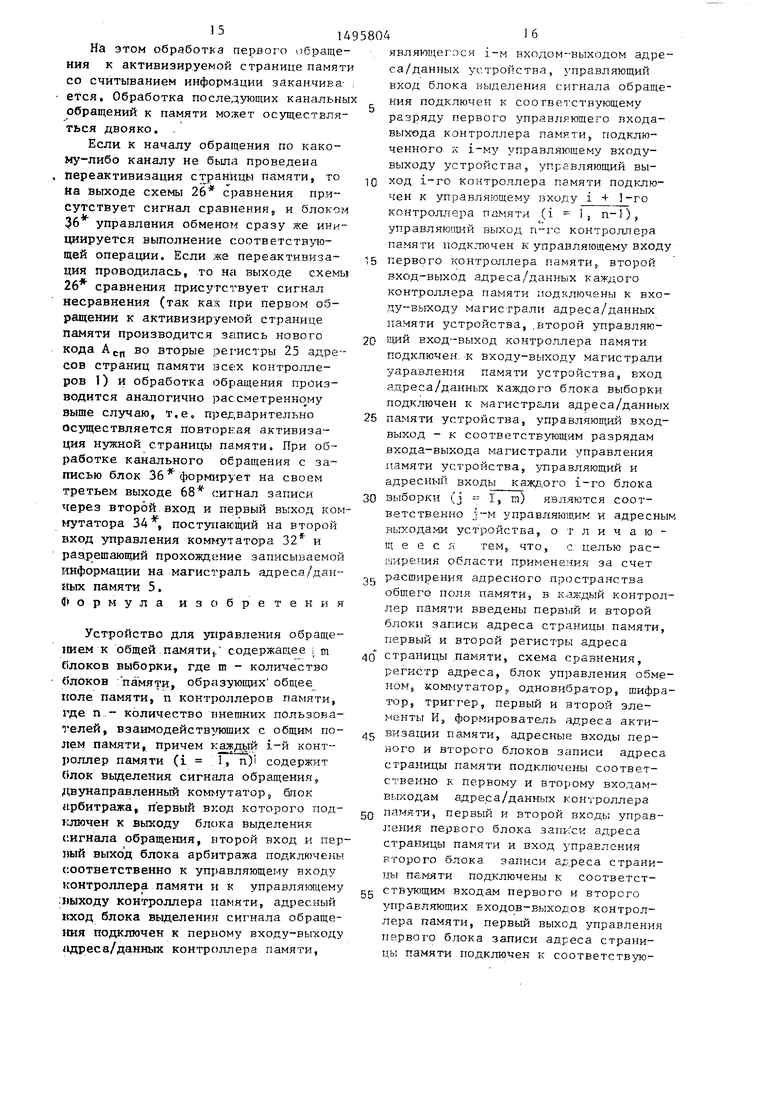

Контроллер 1 ПЕ.мяти содержит (фиг.2) первый 22 и второй 23-блоки записи адреса страницы памяти, ре

Q

з 0 5 0

5 0

5

0

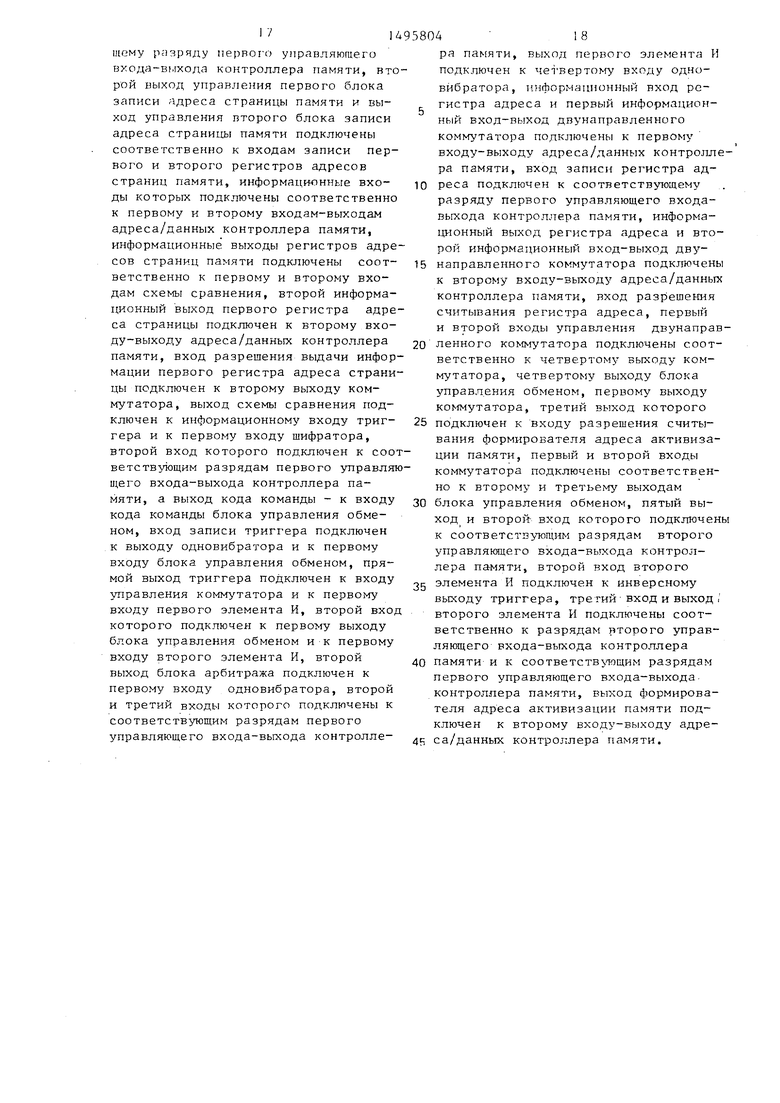

гистры 24 и 25 адреса страницы памяти, схему 26 сравнения, формирователь 27 адреса активизации памяти, блок 28 вьщеления сигнала обращения, блок 29 арбитража, шифратор 30, регистр 31 адреса, двунаправленный коммутатор 32, одновибратор 33, коммутатор 34, триггер 35, блок 36 управления обменом, элементы И 37 и 38, Первый блок 22 записи адреса страницы памяти имеет первый 39 и второй 40 входы управ; ения, адресный вход 41, первый 2 и второй 43 выходы управления.

Второй блок 23 записи адреса страницы памяти имеет первый 44 и второй 45 Входы управления, адресный вход 46, выход 47 управления. Блок 28 выделения сигнала обращения 28 имеет .адресный вход 48, управляющий вход 49, управляющий выход 50,

Блок арбитража 29 имеет первый 51 и второй 52 входы, первый 53 и второй 54 выходы.

Шифратор 30 имеет первый 55 и второй 56 входы, выход 57,

Одновибратор 33 имеет первый 58 четвертый 61 входы и выход 62, Блок 36 управления обменом имеет первый 63 и второй 64 входы, вход команды 65, первый 66 - пятый 70 выходы.

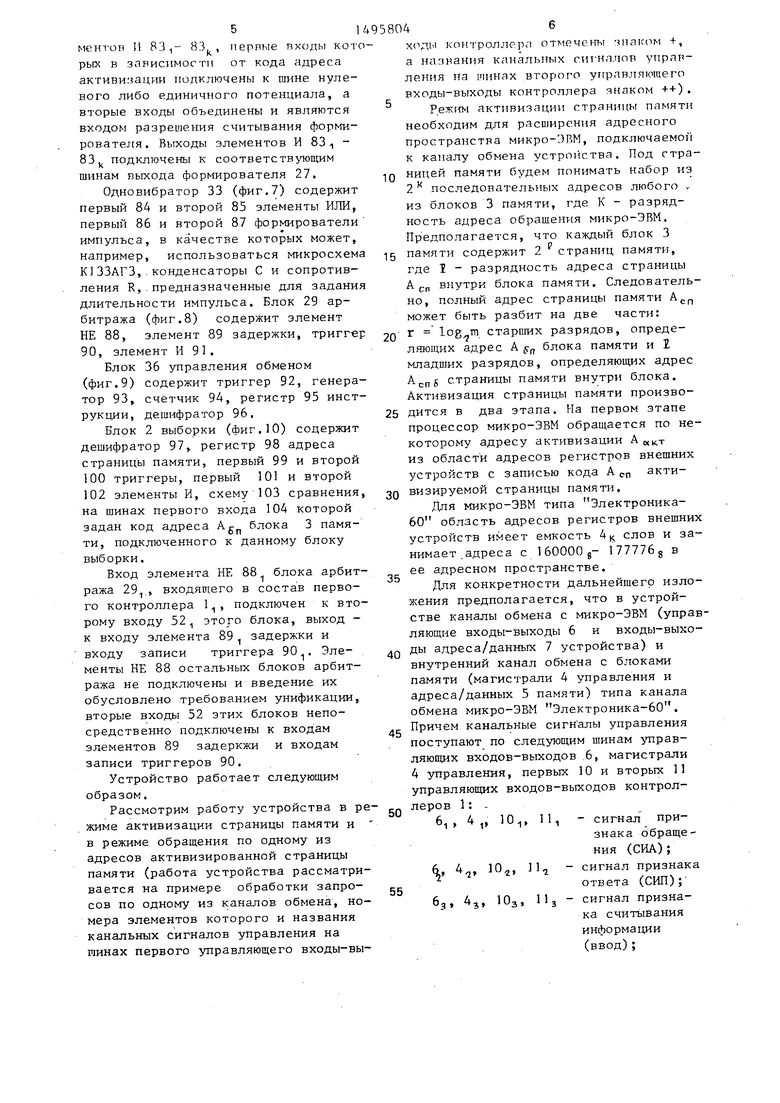

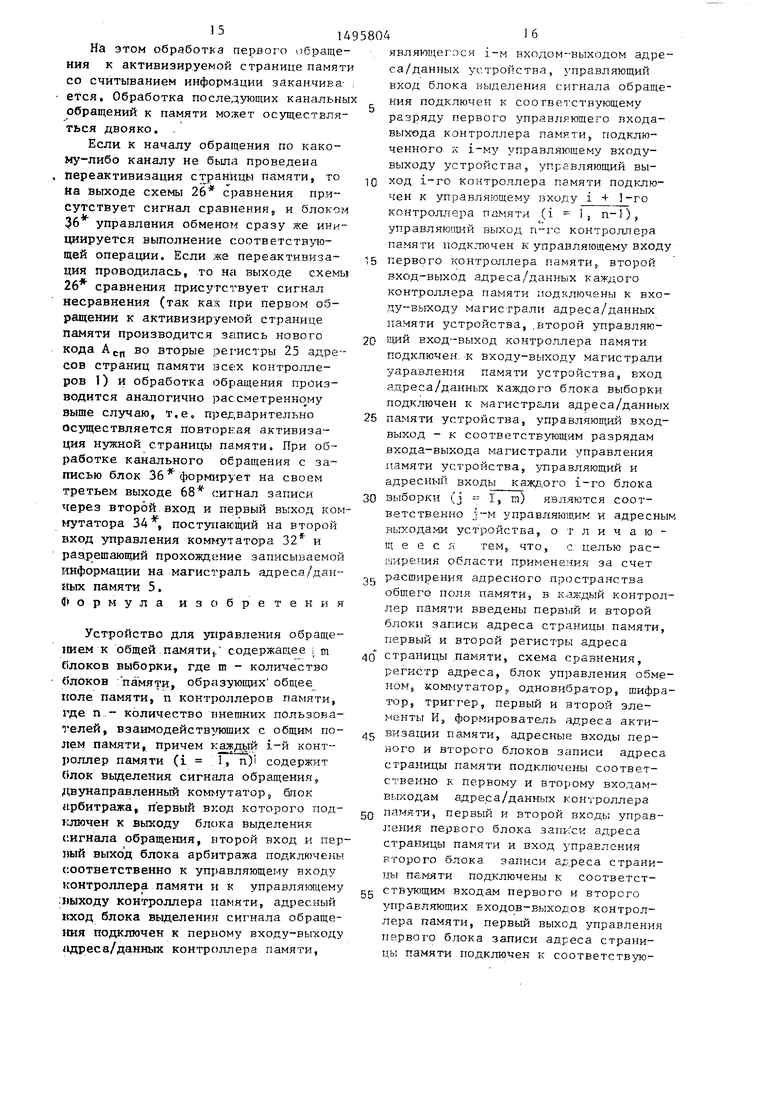

Первый блок 22 записи адреса страницы памяти (фиг,4) содержит дешифратор 71 адреса активизации, триггер 72, элемент И 73, элемент согласования с магистралью 74, Второй блок 23 записи адреса страницы памяти имеет функциональную схему, подобную изображенной на фиг,4, При этом первый 44 и второй 45 входы управления, адресный вход 46 и выход 47 управления блока 23 соответствуют первому 39 и второму 40 входам управления, адресному входу 41 и второму выходу 43 управления блока 22, В блоке 23 также отсутствует элемент согласования с магистралью 74, На фиг,4 входы и выходы блока 23 указаны в скобках.

Блок 28 выделения сигнала обращения (фиг,3) содержит дешифратор 75, элемент И 76,

Шифратор 30 (фиг,5) содержит первый 77 и второй 78 элементы НЕ, первый 79 и второй 80 элементы И, первый 81 и второй 82 элементы ИЛИ,

Формирователь 27 адреса активизации памяти (фиг,6) содержит К элементов И 83,- 83|, первые входы котрых в зависимости от кода адреса активи;зации подключены к шине нулевого либо единичного потенциала, а вторые входы объединены и являются входом разрешения считывания формирователя. Выходы элементов И 83 - 83ц подключены к соответствующим шинам выхода формирователя 27.

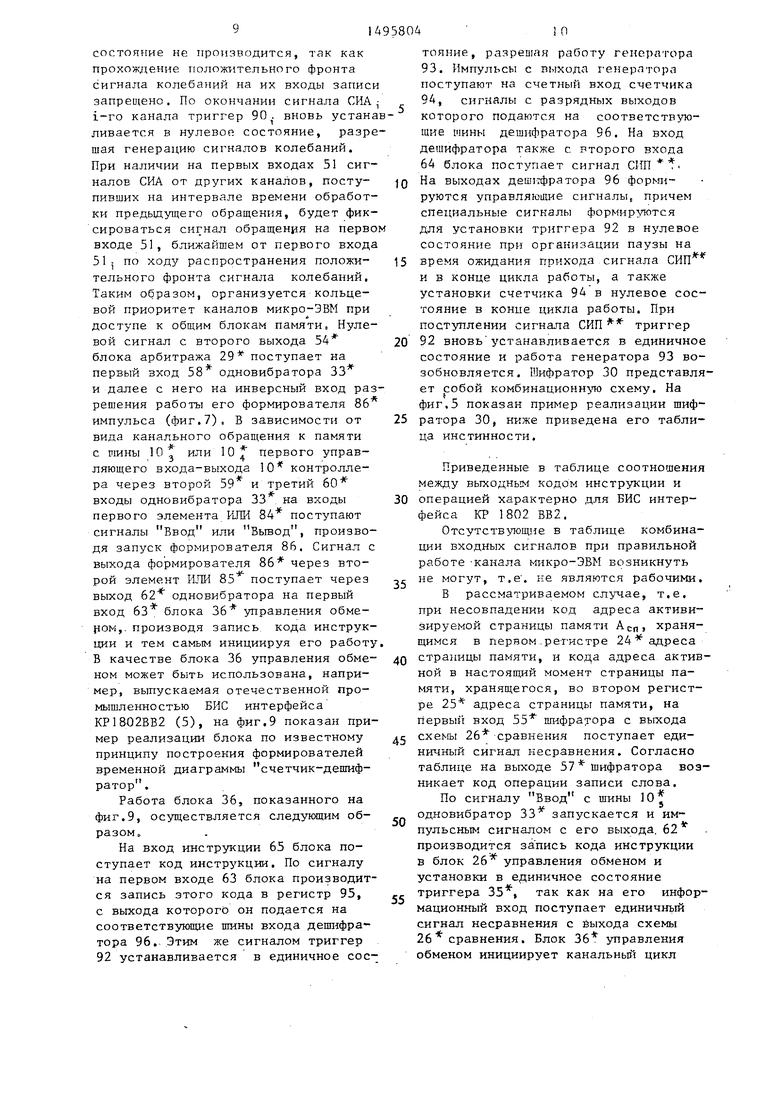

Одновибратор 33 (фиг.7) содержит первый 84 и второй 85 элементы ИЛИ, первый 86 и второй 87 формирователи импульса, в качестве которых может, например, использоваться микросхем К1ЗЗАГЗ,.конденсаторы С и сопротивления R,.предназначенные для задани длительности импульса. Блок 29 арбитража (фиг.8) содержит элемент НЕ 88, элемент 89 задержки, тригге 90, элемент И 91 .

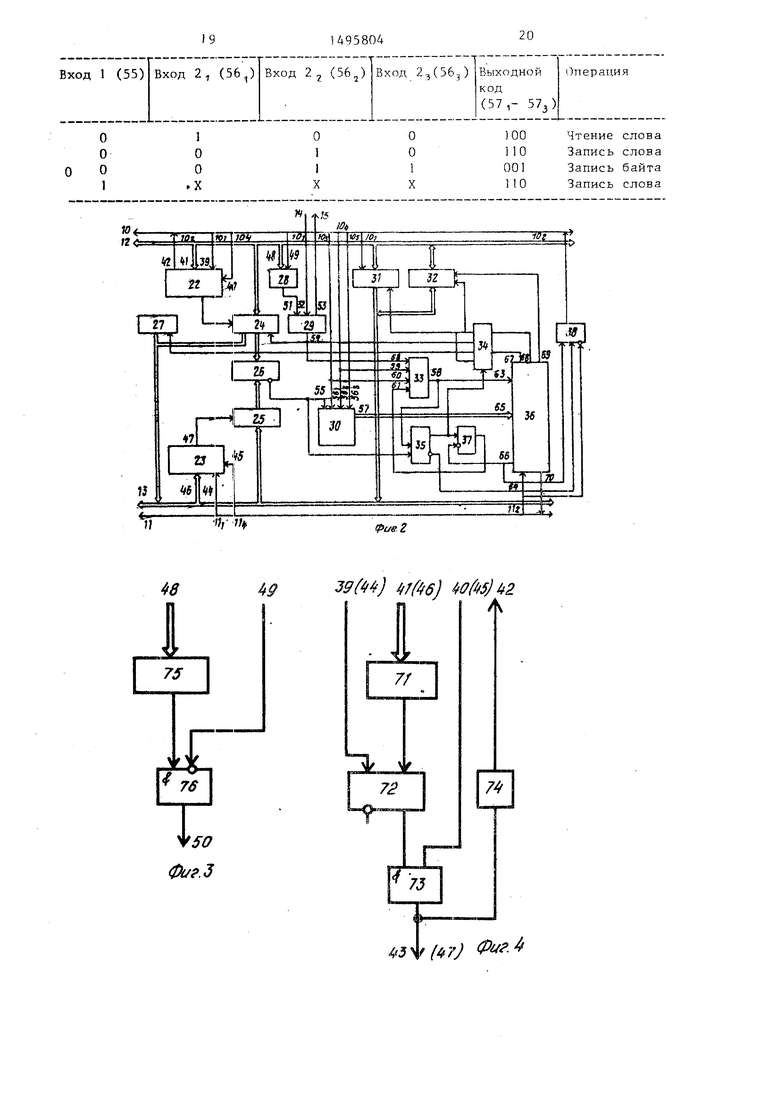

Блок 36 управления обменом (фиг.9) содержит триггер 92, генератор 93, счетчик 9А, регистр 95 инструкции, дешифратор 96,

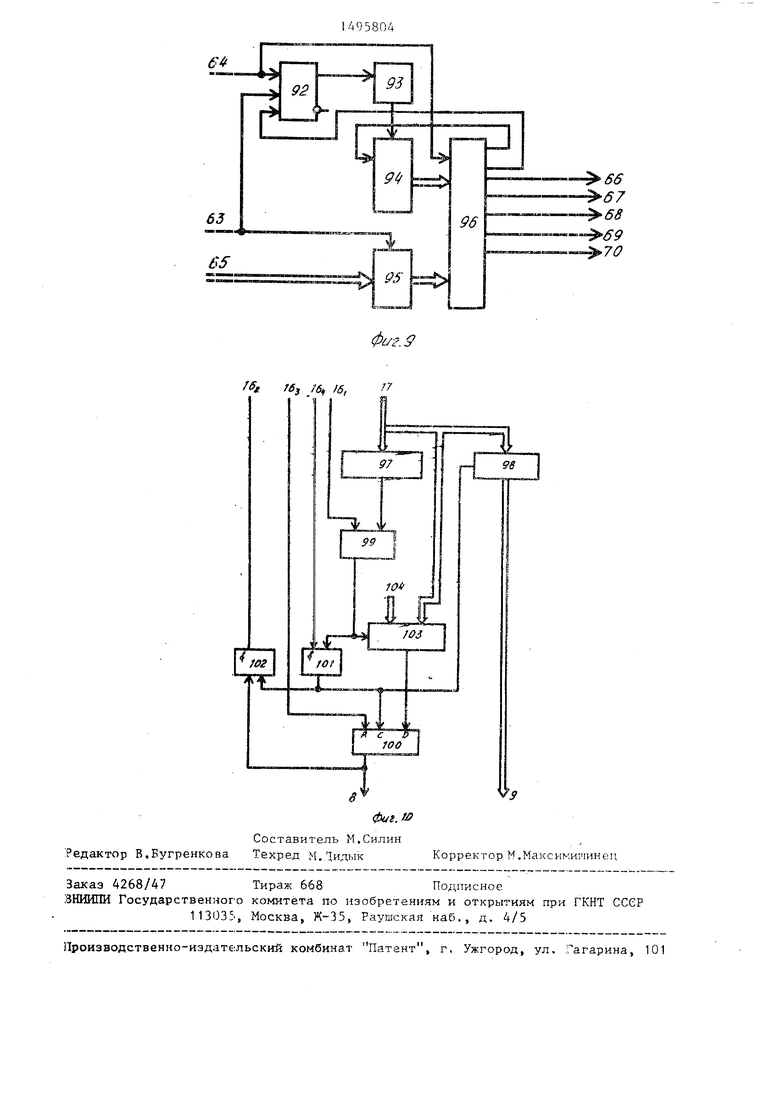

Блок 2 выборки (фиг.10) содержит дешифратор 97, регистр 98 адреса страницы памяти, первый 99 и второй 100 триггеры, первый 101 и второй 102 элементы И, схему 103 сравнения на шинах первого входа 104 которой задан код адреса А блока 3 памяти, подключенного к данному блоку выборки.

Вход элемента НЕ 88 блока арбитража 29., входящего в состав первого контроллера 1, подключен к второму входу 52, этого блока, выход - к входу элемента 89 задержки и входу записи триггера 90,. Элементы НЕ 88 остальных блоков арбитража не подключены и введение их обусловлено требованием унификации, вторые входы 52 этих блоков непосредственно подключены к входам элементов 89 задеркжи и входам записи триггеров 90.

Устройство работает следующим образом.

Рассмотрим работу устройства в режиме активизации страницы памяти и в режиме обращения по одному из адресов активизированной страницы памяти (работа устройства рассматривается на примере обработки запросов по одному из каналов обмена, номера элементов которого и названия канальных сигналов управления на гайках первого управляющего входы-выxciAbi контроллера отмечены зншсом +, а нггзванмя канальных сигналов управления на шинах второго уггравлпющего входы-выходы контроллера знаком ) . Реж(-1м активизации страницы памяти необходим для расширения адресного пространства микро-ЭВМ, подключаемой к каналу обмена устро1 ства. Под страницей памяти будем понимать набор из 2 последовательных адресов любого , из блоков 3 памяти, где К - разрядность адреса обращения микро-ЭВМ. Предполагается, что каждый блок 3

о Р

памяти содержит / страниц памяти, где 1 - разрядность адреса страницы А р„ внутри блока памяти. Следовательно, полный адрес страницы памяти А.

0

может быть разбит на две части:

г log m старших разрядов, опреде0

ляющих адрес А блока памяти и 1 младших разрядов, определяющих адрес А,п5 страницы памяти внутри блока. Активизация страницы памяти произво- 5 дится в два этапа. На первом этапе процессор микро-ЭВМ обращается по некоторому адресу активизации А из области адресов регистров внешних устройств с записью кода А п активизируемой страницы памяти.

Для микро-ЭВМ типа Электроника- 60 область адресов регистров внешних устройств имеет емкость 4 (; слов и занимает .адреса с 160000g- 177776g в ее адресном пространстве.

Для конкретности дальнейшего изложения предполагается, что в устройстве каналы обмена с микро-ЭВМ (управляющие входы-выходы 6 и входы-выходы адреса/данных 7 устройства) и внутренний канал обмена с блоками памяти (магистрали 4 управления и адреса/данных 5 памяти) типа канала обмена микро-ЭВМ Электроника-60. Причем канальные сигн алы управления поступают по следующим шинам управ- ЛЯЮ1ДИХ входов-выходов 6, магистрали 4 управления, первых 10 и вторых 11 управляющих входов-выходов контроллеров 1: .

5

0

5

0

6,, 4„ 10,, 11

5

. .,

10

3

10

г. Ч

п.

3

- сигнал признака обращения (СИА); сигнал признака ответа (СИП); сигнал признака считывания информации (ввод);

5

Ч

7 П.

64 4 ч сигнал признака записи ин1}юрмации (вывод);

10,5-, 11 5 - сигнал признака записи байта (байт) (индекс i онущен).

Код А OIH,. через адресньй вход 4 Г первого блока 22 записи адреса страницы памяти 22 поступает на вкод его дешифратора адреса активизации 7 (фиг.4). При опознавании кода единичный сигнал с выхода дешифратора 71 подается на информационный вход триггера 72., на вход записи которого через первый вход управления ЗЯ в соответствии с временной диаграммой канального цикла ; обмена микро-ЭВМ поступает по шине 10 первого управляющего входа-выхода 10 сигнал СИЛ, По сигналу CI-IA производится установка триггера 72 в единичное состояние, единичный сигнал с прямого выхода которого поступает на первый вход элемента И 73, При поступлении на второй вкод элемента И- 73 через второй вход управления 40 блока 22 по шине 10 ка.нального сигнапа признака записи информации Вывод на его выходе возникает сигнал, который через элемен согласования с магистралью 74, первый выход управления 42 выдается на шину 10 в ваде сигнала ответа СИП и через второй выход управле- - ния 43 - на вход записи первого регистра адреса с:траницы памяти 24 и в него заносится код А ел с первого входы-выходы адреса/данных 12 контроллера. На этом первый этап активиза1;ии страницы памяти заканчивается ,

Необходимость проведения второго этапа определяется в процессе первого обращения микро-ЭВМ по одному из адресов активизируемой страницы памяти.

Pacc ютpим работу устройства во втором релшме при обработке первого обращения со считы занием информации к активизируемой странице памяти, если ее адрес е совпадает с адресом активной в настоящий момент страницы памяти.

В режиме обращ(ния микро-ЭВМ по одному из активизирован495804

ной страшщы памяти код адреса обра- и1ения АО через соответствующие пгины первого входы-выхода адреса/данных 12 контроллера 1 поступает на адресный вход 48 блока 28 выделения сигнала обращения и информационный вход регистра 31 адреса, куда заносится по сигнал СИА с

10

Дешифратор 75 блока

шины 28

5

0

5

0

5

0

5

0

5

(фиг.З) осуществляет декодирование адреса А, и в случае его принадлежности к зоне адресов памяти единичный сигнал с егЬ выхода поступает на первый вход элемента И 76, разрешая прохождение с управляющего входа 49 блока на его управляющий выход 50 и далее на первый вход 51 блока арбитража 29 сигнала СИА Совокупность блоков 29 т - 29 . арбитражей входящих в состав контроллеров 1, - 1 (фиг.8), осуществляет разрешение конфликтных ситуаций при одновременном обращении к блокам 3 памяти нескольких микро-ЭВМ. Работа кх осуществляется следующим образом. При отсутствии сигналов СИА на первых входах 51 присутствует низкий уровень сигнала. При этом триггеры 90 удерживаются в нулевом состоянии, на вторые входы элементов И 9) с инверсных выходов триггеров 90 поступают сздиничные сигналы, и в цепи из элемента НЕ 88,, элементов 89 задержки и элементов И 91 - 91 возникают колебания, продолжающиеся до тех пор, пока на одном из первых входов 51, например 51,. , ке появится единичных сигнал обращения. В этом случае триггер 90-,, на информационный вход которого поступил еди- сигнал обращения, опрокинется ближайщим по времени положительным фронтом сигнала колебаний, поступающим на его вход записи. При этом нулевой сигнал с инверсного выхода триггера 90; блокирует д, 1льнейшее распространение сигналов колебаний. Элемент 89 задержки обеспечивает згщержку распространения этих сигналов на время переключения триггера. Единичный сигнал с прямого выхода триггера 90 поступает на второй выход 54, сигнализируя о фиксации сигнала СИА; i-ro канала. При поступлении сигналов СИА по другим каналам во время обработки сигнала обращения i-ro канала установка соответствующих триггеров 90 в единичное

состояние не производится, так как прохождение положительного фронта сигнала колебаний на их входы записи запрещено. По окончании сигнала CPiA i-ro канала триггер 90. вновь устаналивается в нулевое состояние, разрешая генерацию сигналов колебаний. При наличии на первых входах 51 сигналов СИА от других каналов, посту- пивших на интервале времени обработки предыдущего обращения, будет фиксироваться сигнал обращения на перво входе 51, ближайшем от первого входа 51 по ходу распространения положи- тельного фронта сигнала колебаний. Таким образом, организуется кольцевой приоритет каналов микро-ЭВМ при

а

доступе к общим блокам памяти. Нулевой сигнал с второго выхода 54 блока арбитража 29 поступает на первый вход 58 одновибратора 33 и далее с него на инверсный вход раз рещения работы его формирователя 86 импульса (фиг,7), В зависимости от вида канального обраЕ(ения к памяти с пшны 10 - или 10 первого управляющего входа-выхода 10 контроллера через второй 59 и третий 60 входы одновибратора 33 на входы первого элемента FJTO 84 поступают сигналы Ввод или Вьшод, производя запуск формирователя 86, Сигнал с выхода формирователя 86 через второй элемент ИЛИ 85 поступает через выход 62 одновибратора на первый вход 63 блока 36 управления обмером,, производя запись, кода инструкции и тем самым инициируя его работу В качестве блока 36 управления обме- ном может быть использована, например, выпускаемая отечественной промышленностью БИС интерфейса КР1802ВВ2 (5), на фиг,9 показан пример реализации блока по известному принципу построения формирователей временной диаграммы счетчик-дешифратор ,

Работа блока 36, показанного на фиг,9, осуществляется следующим об- разом„

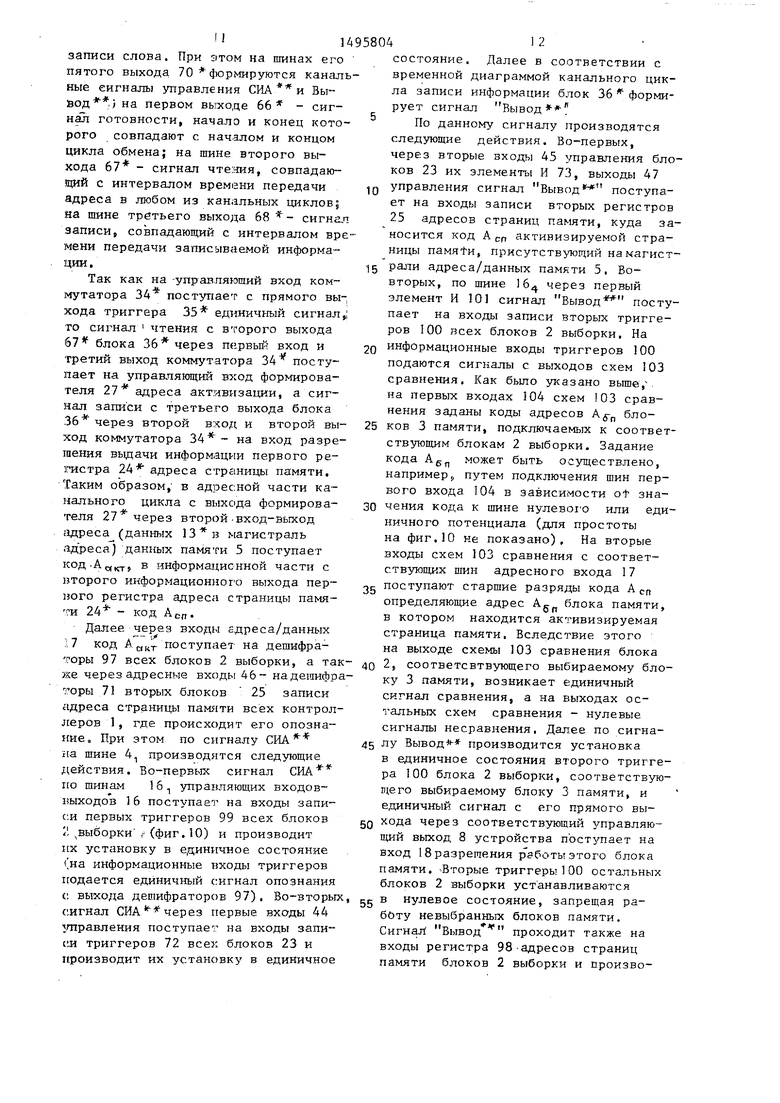

На вход инструкции 65 блока поступает код инструкции. По сигналу на первом входе 63 блока производится запись этого кода в регистр 95, с выхода которого он подается на соответствующие шины входа дешифратора 96, Этим же сигналом триггер 92 устанавливается в единичное соех-а

тояние, разрешая работу генератора

93,Импульсы с выхода генератора поступают на счетный вход счетчика

94,сигналы с разрядных выходов которого подаются на соответствующие шины дешифратора 96, На вход дешифратора также с второго входа 64 блока поступает сигнал Clffl. На выходах дешггфратора 96 формируются управляющие сигналы, причем специальные сигналы формирлтотся для установки триггера 92 в нулевое состояние при организации паузы на время ожидания прихода сигнала СИП и в конце цикла работы, а также установки счетчика 94 в нулевое состояние в конце цикла работы. При поступлении сигнала СИП триггер 92 вновь устанавливается в единичное состояние и работа генератора 93 возобновляется. Шифратор 30 представляет собой комбинационн то схему. На фиг,5 показан пример реализации шифратора 30, ниже приведена его таблица инстинности.

Приведенные в таблице соотношения между выходным кодом инструкции и операцией характерно для БИС интерфейса К 1802 ВВ2,

Отсутствующие в таблице комбинации входных сигналов при правильной работе -канала микро-ЭВМ возникнуть не могут, т,е , ке являются рабочими,

В рассматриваемом случае, т,е, при несовпадении код адреса активизируемой страницы памяти АСП, хранящимся в первом .регистре 24 адреса страницы памяти, и кода адреса активной в настоящий момент страницы памяти, хранящегося, во втором регистре 25 адреса страницы памяти, на Первый вход 55 шифратора с выхода схемы 26 сравнения поступает единичный сигнал несравнения. Согласно таблице на выходе 57 шифратора возникает код операции записи слова.

По сигналу Ввод с щины 10 одновибратор 33 запускается и импульсным сигналом с его выхода. 62 производится за пись кода инструкции в блок 26 управления обменом и установки в единичное состояние триггера 35, так как на его информационный вход поступает единичньгй сигнал несравнения с йыхода схемы 26 сравнения. Блок 36 управления обменом инициирует канальный цикл

записи слова. При этом на шинах его пятого выхода 70 4юрмируются канальные еигналь управления СИЛ и Вы- первом выходе 66 - сигнал готовности, начало и конец которого совпадают с началом и концом цикла обмена; на шине второго выхода 67 - сигнал чте:аия, совпадающий с интервалом времени передачи адреса в любом из канальных цикловj на шине третьего выхода 68 - сигнг.п записи, совпадающий с интервалом времени передачи записываемой информации.

Так как на -упр авпяюший вход коммутатора 34 поступает с прямого выхода триггера 35 единичный сигнал, то сигнал чтения с второго выхода 67 блока 36 через первый вход и третий выход коммутатора 34 поступает на управляющий вход формирователя 27 адреса активизации, а сигнал записи с третьего выхода блока 36 через второй вход и второй выход коммутатора на вход разрешения выдачи информации первого ре- 1Гистра 24 адреса страницы памяти. Таким образом, в адресной части канального цикла с выхода формирователя 27 через второй-вход-выход адреса (данных магистраль адреса) данных памяти 5 поступает код-Ас(5 в информационной части с второго информационного выхода пер- 1ЮГО регистра адреса страницы памяти 24 - код А СП.

Далее через входы адреса/данных 17 код А поступает на дешифра0

5

состояние. Далее в соответствии с временной диаграммой канального цикла записи информации блок 36 формирует сигнал Вывод

По данному сигналу производятся следующие действия. Во-первых, через вторые входы 45 управления блоков 23 их элементь И 73, выходы 47 управления сигнал Вывод поступает на входь записи вторых регистров 25 адресов страниц памяти, куда заносится код А СП активизируемой страницы памяфи, присутствующий на магистрали адреса/данных памяти 5. Во- вторых, по шине 16 через первый элемент И 101 сигнал Вывод поступает на входы записи вторых триггеров 100 всех блоков 2 выборки. На

Q информационные входы триггеров 100 подаются сигналы с выходов схем 103 сравнения. Как бьшо указано вьппе, на первых входах J04 схем 103 сравнения заданы коды адресов А бло5 ков 3 памяти, подключаемых к соответствующим блокам 2 выборки. Задание кода Ag| может быть осуществлено, например,, путем подключения шин первого входа 104 в зависимости ot зна0 чения кода к шине нулевого или единичного потенциала (для простоты на фиг,10 не показано). На вторые входы схем 103 сравнения с соответствующих шин адресного входа 17

5 поступают старшие разряды кода А сп определяющие адрес Ag блока памяти, в котором находится активизируемая страница памяти. Вследствие этого на выходе схемы 103 сравнения блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации оперативной памяти | 1985 |

|

SU1262497A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Устройство адресации оперативной памяти | 1987 |

|

SU1417003A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Станция локальной сети | 1990 |

|

SU1824640A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1259262A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении общей оперативной памяти многомикромашинных вычислительных систем. Целью изобретения является расширение области применения устройства за счет расширения адресного пространства общего поля памяти. Устройство содержит контроллеры 11 - 1N памяти, блоки 21 - 2м выборки, блоки 31 - 3м памяти, магистрали 4 управления и 5 адреса/данных и имеет управляющие выходы 81 - 8м и адресные выходы 91 - 9м. 10 ил., 1 табл.

торы 97 всех блоков 2 выборки, а так- Q 2, соответсвтвующего выбираемому бло- же через адресные входы 46- надешифра- у з памяти, возникает единичный

25

торы 71 вторых блоков 25 записи адреса страницы памяти всех контроллеров 1 , где происходит его опознание. При зтом по сигналу СИА шине 4 производятся следующие

СИА

50

действия. Во-первых сигнал rto шинам 16 управляющих входов- выходов 16 поступает на входы записи первых триггеров 99 всех блоков i. выборки , (фиг, 10) и производит их установку в единичное состояние (на информационные входы триггеров ггодается единичный с:игнал опознания (; выхода дешифраторов 97), Во-вторых, gg сигнал СИА через первые входы 44 «шравления поступает на входы запи- (1И триггеров 72 всех блоков 23 и производит их установку в единичное

сигнал сравнения, а на выходах остальных схем сравнения - нулевые сигналы несравнения. Далее по сигна- 45 лу Вывод - производится установка

в единичное состояния второго триггера 100 блока 2 выборки, соответствующего выбираемому блоку 3 памяти, и единичный сигнал с его прямого выхода через соответствующий управляющий выход 8 устройства поступает на вход 18 разрешения работы этого блока памяти, Вторые триггеры 100 остальных блоков 2 выборки устанавливаются в нулевое состояние, запрещая работу невыбранных блоков памяти. Сигнал Вывод проходит также на входы регистра 98-адресов страниц памяти блоков 2 выборки и произво0

g

сигнал сравнения, а на выходах остальных схем сравнения - нулевые сигналы несравнения. Далее по сигна- 5 лу Вывод - производится установка

в единичное состояния второго триггера 100 блока 2 выборки, соответствующего выбираемому блоку 3 памяти, и единичный сигнал с его прямого выхода через соответствующий управляющий выход 8 устройства поступает на вход 18 разрешения работы этого блока памяти, Вторые триггеры 100 остальных блоков 2 выборки устанавливаются в нулевое состояние, запрещая работу невыбранных блоков памяти. Сигнал Вывод проходит также на входы регистра 98-адресов страниц памяти блоков 2 выборки и произво13кода А СП 6

14

дит запись в них кода АСП посту- narauiero на информационные входы этих регистров с соответствующих шин входов адреса/данных 17. С выходов регистров 98 через адресеные выходы 9 устройства код поступает на адресные входы 19 соответствующих блоков 3 памяти. При этом в выбранном блоке 3 памяти производится выбор активизируемой страницы памяти. Проходя с выхода первого элемента И 101 через второй элемент И 102 блока 2 выборки, соответствующего выбранному блоку 3 памяти, второй триггер 100 которого установлен в единичное состояние, сигнал Вывод через шину le поступает на шину 4j в виде сигнала СИП и далее в блок 36, сигнализируя об окончании канальной операции записи информации. На этом второй этап активизации страницы памяти заканчивается. Работа всех блоков 3 памяти на этом slTane запрещена. Это связано с тем, что блоки памяти, имеющие интерфейс типа интерфейса микро-ЭВМ Электроника 60, включают специальные аппаратные средства, осуществляющие блокировку их работы при попадании адреса обращения в область адресов регистров внешних устройств адресного пространства микро-ЭВМ (в рассматриваемом случае таким адресом является Aj.), Техническая реализация подобных аппаратных средств общеизвестна (3.с.11-50). В качестве блоков 3 памяти могут, например, быть использованы серийно выпускаемые устройства 6 памяти.

По окончании канального цикла записи информации по заднему фронту сигнал готовности поступает с первого выхода 66 блока 36 управления . обменом через первый элемент И 37 (на другой вход этого элемента подается разрешающий сигнал с прямого выхода триггера 35) на четвертый вход 61 одновибратора 33 и производит его запуск.

Так как во второй регистр 25 адреса страницы памяти записан код Apf, , .то на выходе схемы 26 сравнения присутствует уже нулевой сигнал сравнения и поэтому на выходе 57 шифратора 30 сформирован код инструции операции считывания (как было указано вьш1е, рассматривается режим обработки первого обращения к акти1495804

5

визируемой странице памяти со считыванием информации), По сигналу с выхода одновибратора 33 производится запись кода инструкции в блок 36 и его запуск (тем самым инициируется канальный цикл считывания) и установка в нулевое состояние триггера 35 (на его инфор мационный вход подан Q нулевой сигнал с выхода схемы 26 сравнения).

На управляющий вход коммутатора 34 с прямого выхода триггера 35 поступает нулевой сигнал, разрешая прохождение сигнала считывания с второго выхода 67 блока 36 на вход разрешения считывания регистра 3 адреса. Код адреса обращения Ад с 11нформационных выходов регистра вьщается в магистраль адреса/ /ланных памяти 5 в адресный части канального цикла. В соответствии с временной диаграммой канального цикла считывания блок 36 формирует сигналы CI-IA, Ввод, поступающие на соответствующие шины магистрали А управления памяти. В результате в выбранном блоке 3 памяти из выбранной в нем страницы памяти производится считывание информации, которая выдается в магистраль адреса/данных памяти 5 и вырабатывается сигнал

0

5

0

СЯА

-

.поступающий на шину 4 магистрали 4 управления памятии далее через шину 11 второго управляв

на второй

0

S

0

5

шину 1J второго управляющего входа- выхода 1 1 контроллера 1 вход 64 его блока 36 и третий вход элемента И . Через второй элемент И 38 шину 10 первого управляющего входа-выхода 10 контроллера сигнал СИП уже в виде сигнала СИП поступает на соответствующую шину зшравляющего входа-выхода 6 устройства, сигнализируя микро-ЭВМ о вьща- че считанной из памяти информации. На первом и втором входах элемента И 38 присутствуют в это время разре- шаю&;ие потенциалы. При выполнении операции считывания блок 36 управления обменом на своем четвертом выходе 69 формируется сигнал разрешения передачи информации, поступающий на первый вход управления коммутатора 32 и разрешающий прохождение считанной информации через первый вход-выход адреса/данных 12 на соответствующий вход-выход адреса/ у(анных 7 устройства.

Hia этом обработка первого обращения к активизируемой странице памяти со считыванием информации заканчива ется. Обработка последующих канальны обращений к памяти может осуществляться двояко.

Если к началу обращения по какому-либо каналу не была проведена переактивизация страницы памяти, то на выходе схемы 26 сравнения присутствует сигнал сравненияр и блоком 36 управления обменом сразу же инициируется выполнение с;оответствую щей операции. Если же переактивизация проводилась, .то на выходе схеья 26 сравнения присутствует сигнал несравнения (так ка;к при первом обращении к активизируемой странице памяти производится запись нового кода А СП во вторые .регистры 25 адресов страниц памяти асех контроллеров 1) и обработка обращения производится аналогично рассметренно му выше случаю, т,е, предварительно осуществляется повторная активизация нужной страницы памяти. При обработке канального обращения с записью блок 36 формирует на своем третьем выходе 68 сигнал записи через второй-вход и первый выход коммутатора 34, поступающий на второй вход управления коммутатора 32 и раз,р ешающий прохояздение записываемой информации на магистраль адреса/данных памяти 5. в)ормула изобретен1 5я

Устройство для управления обраще- 1шем к общей памяти,, содержащее i m блоков выборки, где m - количество блоков :памяти, образующих общее поле памяти, п контроллеров памяти, где п.. количество внешних пользователей, взаимодействзпощих с общим полем памяти, причем i-й контроллер памяти (i 1, п)1 содержит блок выделения сигнгша обращения, двунаправленный коммутатор, блок арбитража, первый вкод которого под- 1слючен к выходу блока выделения сигнала обращения, лторой вход и пер ВЫХОД блока арбитража подключекь соответственно к управляющему входу контроллера памяти и к управляющему . иыходу контроллера памяти, адресный кход блока выделения сигнала обращения подключен к первому входу-выходу адреса/данных контроллера памяти,

являющегося I-M входом-выходом адреса/данных устройства, управляющий вход блока выделения сигнала обращения подключен к соответствующему разряду первого управляющего входа- выхода контроллера памяти подключенного к i-му управляющему входу- выходу устройства, управляющий выход i-ro контроллера памяти подключен к управляющему входу 1-го

контроллера памяти (i Ij п-S), управляюищй выход п--гс контроллера памяти подключен к управляющему входу

первого контроллера памяти,, второй вход-выход адреса/данных каждого контроллера памяти гюдключены к входу-выходу магистрали адреса/данных памяти устройства,.второй управляющий вход-выход контроллера памяти подключен, к входу-выходу магистрали уаравления памяти устройства, вход адреса/данных каждого блока выборки подключен к магистрали адреса/данных

памяти устройства, управляющий вход- выход - к соответствующим разрядам входа-выхода магистрали управления памяти устройства, управляющий и адресный входы кажр,ого i-ro блока

выборки (J -If m) являются соот- ветствен1-га j-м управх яющим и адресным вькодами устройства, отличающее с я теМ), что, с целью рас- иирения области применения за счет

расширения адресного пространства

общего поля памяти, в к игдый контроллер памяти введены первый и второй блоки записи адреса страницы памяти, первый и второй регистры адреса

страницы памяти, схема сравнения,

регистр адреса, блок управления обме- пом, коммутатор,, одновибратор, шифратор, триггер, первый и второй элементы Hj формирователь ,адреса активизадии памяти, адресные входы первого и второго блоков записи адреса страницы памяти подключены соответственно к первому и второму входам- выходам адреса/данных контроллера

памяти, первый и второй входы управления первого блока адреса страницы памяти и вход управления второго блока записи адреса страницы памяти подключень к соответстствукщим входам первого и второго управляющих ЕХОДОВ-ВЫХОДОВ контроллера памяти, первый выход управления первого блока записи адреса страпи- ць памяти подключен к соответствуютему разряду первого управляющего гзхода-выхода контроллера памяти, второй выход управления первого блока записи адреса страницы памяти и выход управления второго блока записи адреса страницы памяти подключены соответственно к входам записи первого и второго регистров адресов страниц памяти, информационные входы которых подключены соответственно к первому и второму входам-выходам адреса/данных контроллера памяти, информационные выходы регистров адресов страниц памяти подключены соответственно к первому и второму входам схемы сравнения, второй информационный выход первого регистра адреса страницы подключен к второму вхо- ду-вь ходу адреса/данных контроллера памяти, вход разрешения выдачи информации первого регистра адреса страницы подключен к второму выходу коммутатора, выход схемы сравнения подключен к информационному входу триггера и к первому входу шифратора, второй вход которого подключен к соот ветствукзщим разрядам первого управляющего входа-выхода контроллера памяти, а выход кода команды - к входу кода команды блока управления обменом, вход записи триггера подключен к выходу одновибратора и к первому входу блока управления обменом, прямой выход триггера подключен к входу управления коммутатора и к первому входу первого элемента И, второй вход которого подключен к первому выходу блока управления обменом и к первому входу второго элемента И, второй выход блока арбитража подключен к первому входу одновибратора, второй и третий входы которого подключены к соответствующим разрядам первого управляющего входа-выхода контроллера памяти, выход первого элемента И подключен к четвертому входу одно- вибратора, информационный вход регистра адреса и первый информационный вход-выход двунаправленного коммутатора подключены к первому входу-выходу адреса/данных контроллера памяти, вход записи регистра адреса подключен к соответствующему разряду первого управляющего входа- выхода контроллера памяти, информационный выход регистра адреса и второй информационный вход-выход двунаправленного коммутатора подключены к второму входу-выходу адреса/данных контроллера памяти, вход разрешения считывания регистра адреса, первый и второй входы управления двунаправленного коммутатора подключены соответственно к четвертому выходу коммутатора, четвертому выходу блока управления обменом, первому выходу коммутатора, третий выход которого

подключен к входу разрешения считывания формирователя адреса активизации памяти, первый и второй входы коммутатора подключены соответственно к второму и третьему выходам

блока управления обменом, пятый выход и второй- вход которого подключены к соответствующим разрядам второго управляющего входа-выхода контроллера памяти, второй вход второго

элемента И подключен к инверсному вьосоду триггера, трегий вход и выход . второго элемента И подключены соответственно к разрядам второго управляющего входа-выхода контроллера

памяти и к соответствующим разрядам первого управляющего входа-выхода, контроллера памяти, выход формирователя адреса активизации памяти подключен к второму входу-выходу адреса/данных контроллера памяти.

1 о

о

X

X

П

Ч,- Щ

46

39() ) 0{if5)

A

7ff

76

I

Л7 0t/.3

100Чтениеслова

110Записьслова

001Записьбайта

1 1 ОЗаписьслова

Фив2

7/

4 5Ф/«7У (

0i/.S

58

59

60

8

54i

U

S7fl

Tta-

ж

ХЧ

„0 J

Фиэ.б

w

J

62

:

ВЯШ

i /Й

5

.7

54,

Sffr.

8

6

I.

92

63

5

96

9S

| Устройство управления доступом к общей памяти | 1977 |

|

SU750490A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления подключением к магистрали общего блока памяти | 1980 |

|

SU934834A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-11-23—Подача