ел

00

мутатор 1, счетчик 2 информации, регистр 3 состояния, первый 4, второй счетчики адреса, блок 6 управления, буферный регистр 7, мультиплексоры адреса 8 и информации 9. Устройс/гво

обеспеч1шает режим доступа процессора к оперативной памяти и прямого доступа внешнего запоминающего устройства , к оперативной памяти. 1 з,п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании вычислительных систем. Цель изобретения - повышение быстродействия и сокращение объема оборудования устройства. Устройство содержит двунаправленный коммутатор 1, счетчик 2 информации, регистр 3 состояния, первый 4, второй 5 счетчики адреса, блок 6 управления, буферный регистр 7, мультиплексоры адреса 8 и информации 9. Устройство обеспечивает режим доступа процессора к оперативной памяти и прямого доступа внешнего запоминающего устройства к оперативной памяти. 1 з.п.ф-лы, 2 ил.

Изобретение относится к вычислительной технике и может быть использовано при проектировании вычислительных систем.

Целью изобретения является повыше- пне быстродействия.

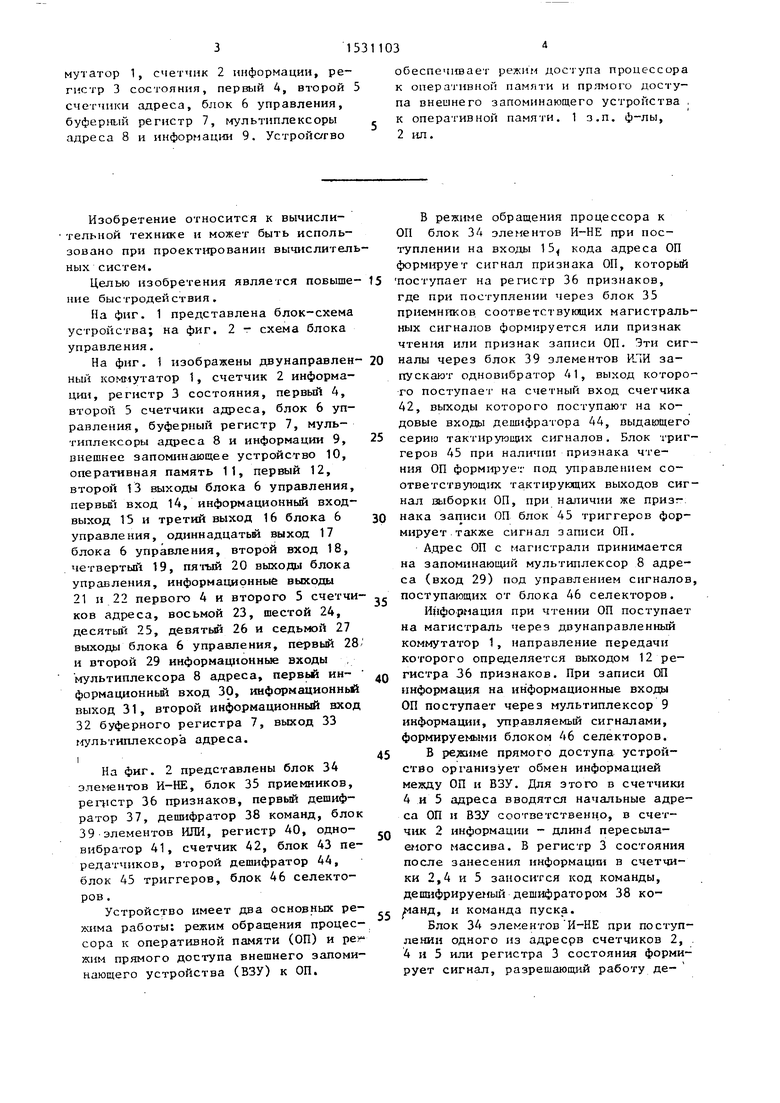

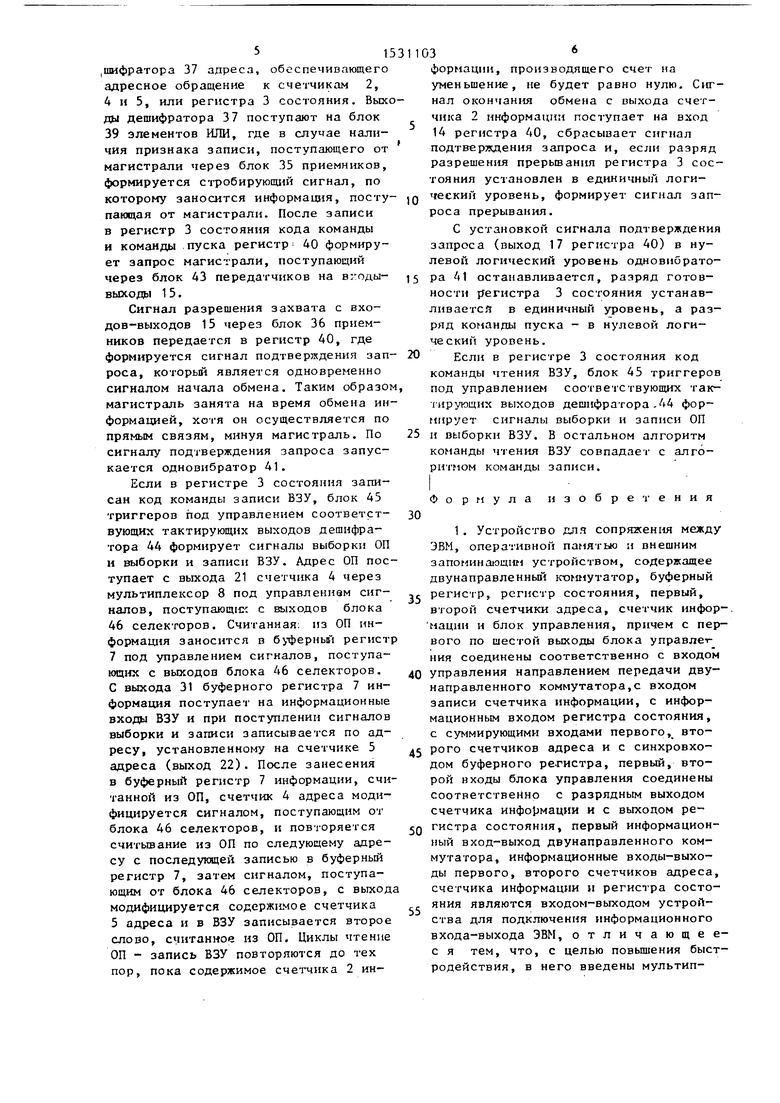

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема блока управления.

На фиг. 1 изображены двунаправлен- ный коммутатор 1, счетчик 2 информации, регистр 3 состояния, первьй 4, второй 5 счетчики адреса, блок 6 управления, буферный регистр 7, мультиплексоры адреса 8 и информации 9, внешнее запом1шающее устройство 10, оперативная память 11, первый 12, второй 13 выходы блока 6 управления, первьй вход 14, информационный вход- выход 15 и третий выход 16 блока 6 управления, одиннадцатьм выход 17 блока 6 управления, второй вход 18, четвертый 19, пятый 20 выходы блока управления, информационные выходы 21 и 22 первого 4 и второго 5 счетчи ков адреса, восьмой 23, шестой 24, десятьп 25, девятый 26 и седьмой 27 выходы блока 6 управления, первый 28 и второй 29 информационные входы мультиплексора 8 адреса, первьй ин- формационньй вход 30, информационньй выход 31, второй информационный вход 32 буферного регистра 7, выход 33 г-1ультнплексора адреса.

:

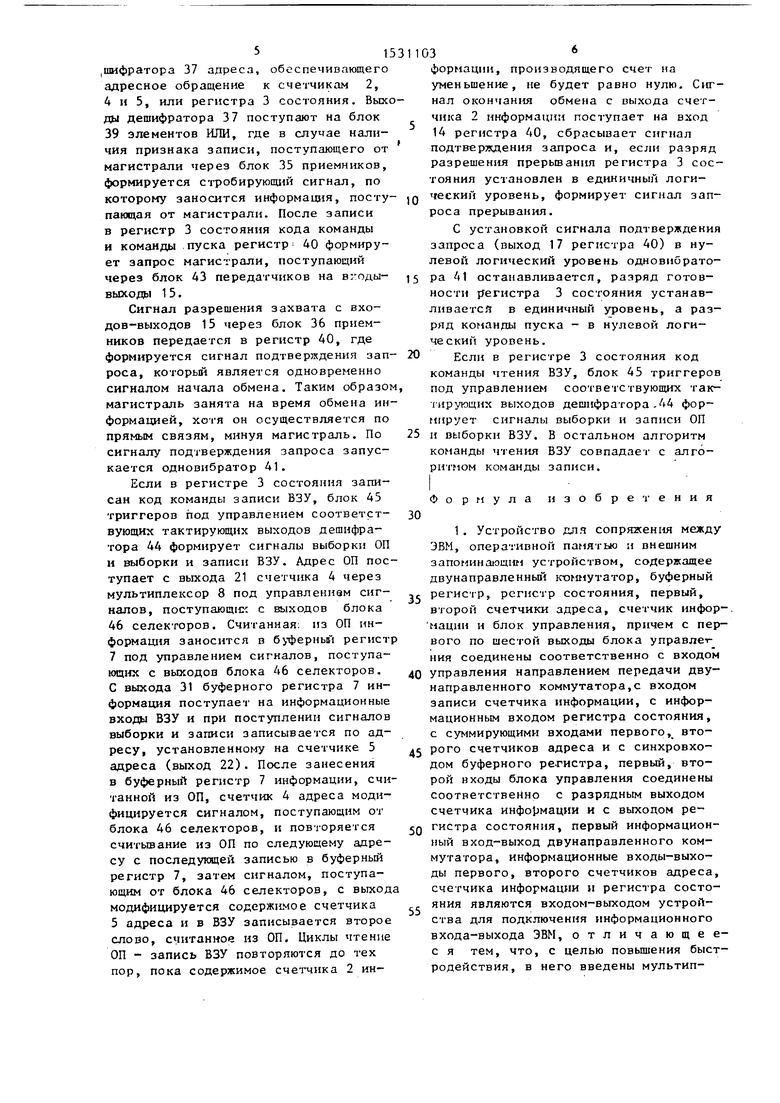

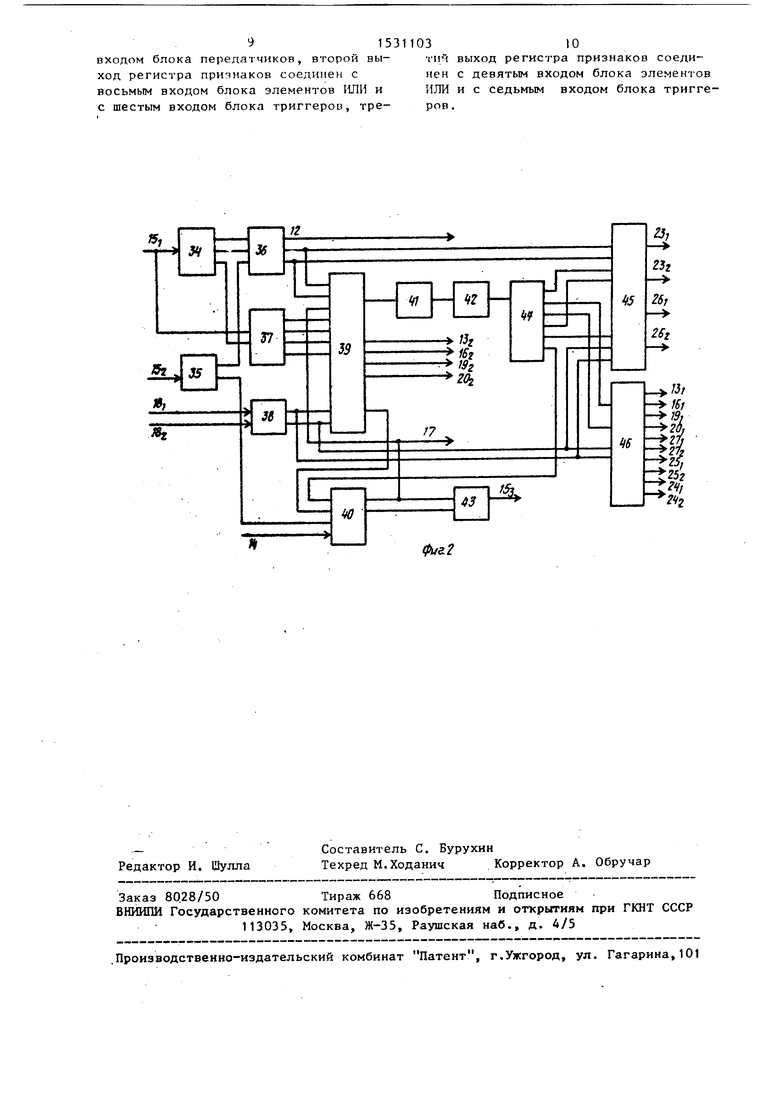

На фиг. 2 представлены блок 34 элементов И-НЕ, блок 35 приемников, perviCTp 36 признаков, первый дешифратор 37, дешифратор 38 команд, блок 39 элементов ИЛИ, регистр 40, одно- вибратор 41, счетчик 42, блок 43 передатчиков, второй дешифратор 44, блок 45 триггеров, блок 46 селекторов .

Устройство имеет два основных режима работы: режим обращения процессора к оперативной памяти (СП) и ре жим прямого доступа внешнего запоминающего устройства (ВЗУ) к ОП.

В режиме обращения процессора к ОП блок ЗА элементов И-НЕ при поступлении на входы 15 кода адреса ОП формирует сигнал признака ОП, который пос 1 упает на регистр 36 признаков, где при поступлении через блок 35 приемников соответствующих магистральных сигналов формируется или признак чтения или признак записи ОП, Эти сигналы через блок 39 элементов ИЛИ запускают одновибратор 41, выход которого поступает на счетный вход счетчика 42, выходы которого поступают на кодовые входы дешифратора 44, выдающего серию тактирующих сигналов. Блок триггеров 45 при наличии признака чтения ОП формирует под управлением соответствующих тактирующих выходов сигнал выборки ОП, при наличии же призт- нака записи ОП блок 45 триггеров формирует также сигнал записи ОП.

Адрес ОП с магистрали принимается на запоминающий мультиплексор 8 адреса (вход 29) под управлением сигналов поступающих от блока 46 селекторов.

Информация при чтении ОП поступает на магистраль через двунаправленный коммутатор 1, направление передачи которого определяется выходом 12 регистра 36 признаков. При записи ОП информация на информационные входы ОП поступает через мультиплексор 9 информации, управляемый сигналами, формируемыми блоком 46 селекторов.

В редиме прямого доступа устройство организует обмен информацией между ОП и ВЗУ. Для этого в счетчики 4 и 5 адреса вводятся начальные адреса ОП и ВЗУ соответственно, в счетчик 2 информации - длинй пересылаемого массива. В регистр 3 состояния после занесения информац1ш в счетчики 2,4 и 5 заносится код команды, депифрируеньш дешифратором 38 ко- анд, и команда пуска.

Блок 34 элементов И-НЕ при поступлении одного из адресрв счетчиков 2, . 4 и 5 или регистра 3 состояния формирует сигнал, разрешающий работу де-

51

шифратора 37 адреса, обеспечивающего адресное обращение к счетчикам 2,

4н 5, или регистра 3 состояния. Выхды дешифратора 37 поступают на блок

39 элементов ИЛИ, где в случае наличия признака записи, поступающего от магистрали через блок 35 приемников, формируется стробирующий сигнал, по которому заносится информащ1я, посту пающая от магистрали. После записи в регистр 3 состояния кода команды и команды пуска регистр 40 формирует запрос магистрали, поступающий через блок 43 передатчиков на вгоды- выхода 1 5.

Сигнал разрешения захвата с входов-выходов 15 через блок 36 приемников передается в регистр 40, где формируется сигнал подтверждения зап роса, которьй является одновременно сигналом начала обмена. Таким образо магистраль занята на время обмена информацией, хоч я он осуществляется по прямым связям, минуя магистраль. По сигналу под 1 верждения запроса запускается одновибратор 41.

Если в регистре 3 состояния записан код команды записи ВЗУ, блок 45 триггеров под управлением соответст- вующих тактирующих выходов дешифратора 44 формирует сигналы выборки ОП и выборки и записи ВЗУ. Адрес ОП поступает с выхода 21 счетчика 4 через мультиплексор 8 под управлением сигналов, поступающих с выходов блока 46 селекторов. Считанная; из ОП ин- формащ1я заносится в б -ферный регист 7 под управлением сигналов, поступающих с выходов блока 46 селекторов. С выхода 31 буферного регистра 7 информация поступае 1 на информационные входы ВЗУ и при поступлении сигналов выборки и записи записывается по адресу, установленному на счетчике 5 адреса (выход 22). После занесения в буферный регистр 7 информации, считанной из ОП, счетчик 4 адреса модифицируется сигналом, поступающим от блока 46 селекторов, и пов 1 оряется считьшание из ОП по следующему адресу с последукяцей записью в буферный регистр 7, затем сигналом, поступающим от блока 46 селекторов, с выход модифицируется содержимое счетчика

5адреса и в ВЗУ записывается второе слово, считанное из ОП. Циклы чтение ОП - запись ВЗУ повторяются до тех пор, пока содержимое счетчика 2 ин

Q 5

0 5

О , д

5

03

формации, производящего счет на уменьшение, не будет равно нулю. Сигнал окончан11я обмена с выхода счетчика 2 информации поступает на вход 14 регистра 40, сбрасывает сигнал подтверждения запроса и, если разряд разрешения прерьшания регистра 3 состояния установлен в единичный логический уровень, формирует сигнал запроса прерывания.

С установкой сигнала подтверждения запроса (выход 17 регистра 40) в нулевой логический уровень одновибрато- ра 41 останавливается, разряд готовности ргегистра 3 состояния устанавливается в единичный уровень, а разряд команды пуска - в нулевой логический уровень.

Если в регистре 3 состояния код команды чтения ВЗУ, блок 45 триггеров под управлением соответствующих тактирующих выходов дешифратора.44 формирует сигналы выборки и записи ОП и выборки ВЗУ. В остальном алгоритм команды чтения ВЗУ совпадает с алгоритмом команды записи.

Формула изобретения

0

5

0

5

0

5

0

5

вход-выход блока соединен с вх;)п;ом блока элементов И-НЕ, с первым информационным входом первого дешифратора, с выходом блока передатчиков и с входом блока приемников, первый, второй выходы которого соединены с первыми информационными входами регистра признаков и регистра соответственно, первый, второй выходы блока элементов И-НЕ соединены соответственно с вторым информационным входом регистра признаков и с вторым информационным входом первого дешифратора, с первого по четвертый выходы которого соединены соответственно с первого по четвертый входами блока элементов ИЛИ, второй информационный вход регистра является первым входом логического условия блока, информационный вх; :; дешифратора команд является вторым входом логического условия блока, первый выход регистра признаков является первым выходом блока, с первого по шестой выходы блока селекторов являются с второго по седьмой выходами блока, первый, второй выходы блока триггеров являются восьмым, девятым выходами блока, седьмой выход блока селекторов является десятым выходом блока, с первого по четвертый выходы блока элементов ИЛИ являются с второго по пятый выходами блока, первый выход регистра соединен с пятым входом блока элементов ИЛИ, с первым входом блока передатчиков и является одиннадцатьЕ выходом блока, пятый выход блока элементов ИЛИ через последовательно соединенные одновибратор и счетчик соединен с информационным входом второго дешифратора, с первого по шестой выходы которого соединены соответственно с первым, вторым, третьим входами блока триггеров, с первым, вторым информационными входами блока селекторов и с третьим информационным входом регистра, четвертый информацион}1ый вход которого соединен с шестым выходом блока элементов ИЛИ, шестой вход которого соединен с первым выходом дешифратора команд, с первым управляющим входом блока селекторов и с четвертым входом блока триггеров, второй выход дешифратора команд соединен с седьмьП входом блока элементов ИЛИ, с вторым управляющим входом блока селекторов и с пятым входом блока триггеров, второй выход регистра соединен с вторым

153110310

входом блока передатчиков, второй вы- тий выход регистра признаков соеди- ход регистра признаков соединен с нен с девятым входом блока элементов восьмым входом блока элементов ИЛИ и ИЛИ и с седьмым входом блока тригге- с шестым входом блока триггеров, тре- ров.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления обменом | 1983 |

|

SU1151976A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-12-23—Публикация

1988-03-28—Подача