Изобретение относится к вычислительной технике и может быть применено в центральных процессорах в качестве управляющего блока.

Цель изобретения - сокращение

объема блока управляюпдей памяти за счет уменьшения адресной части микрокоманды.

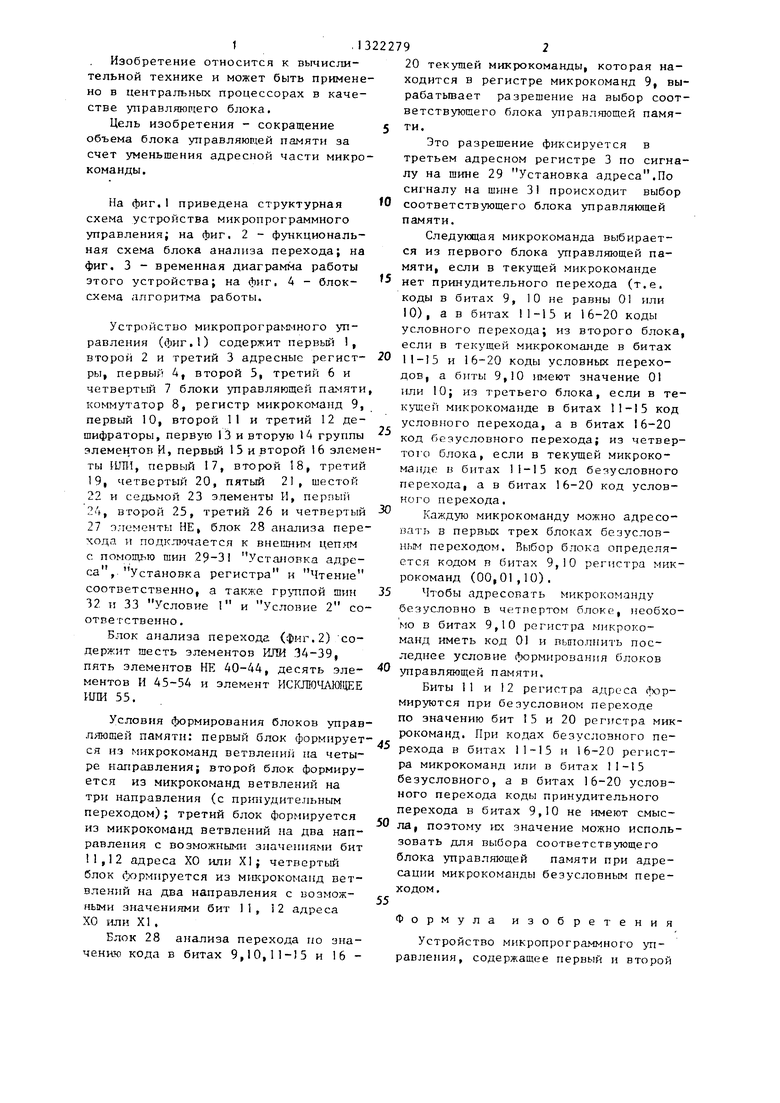

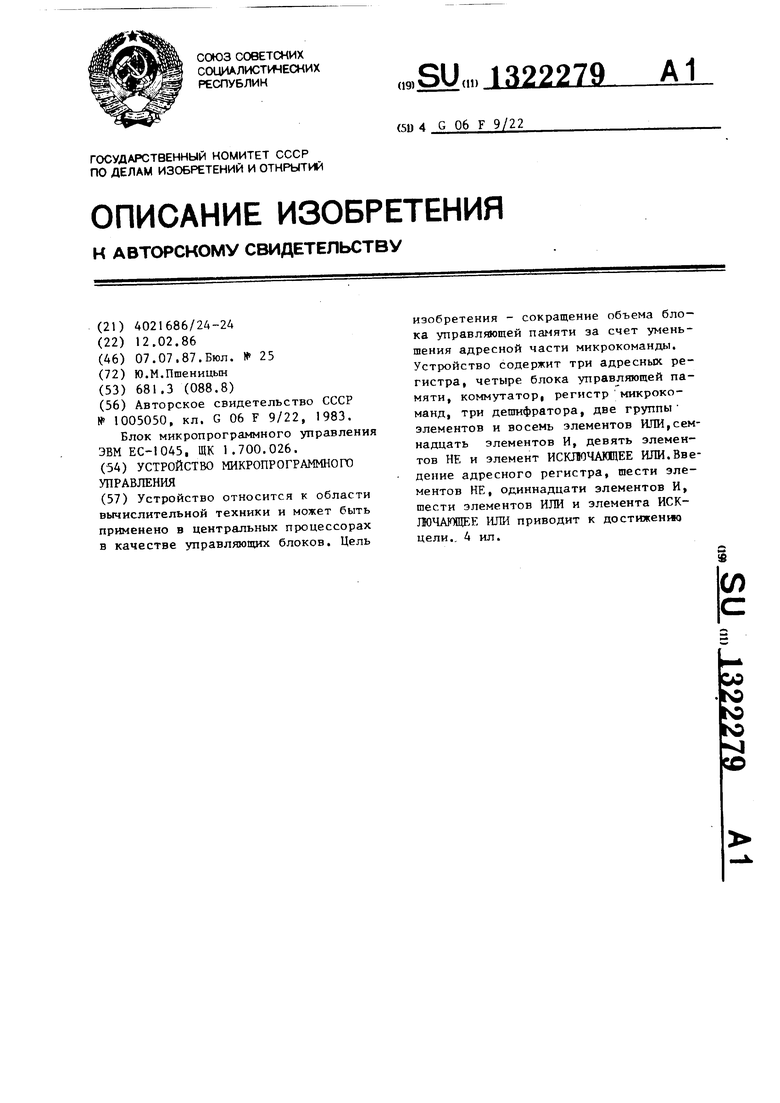

На фиг.I приведена структурная

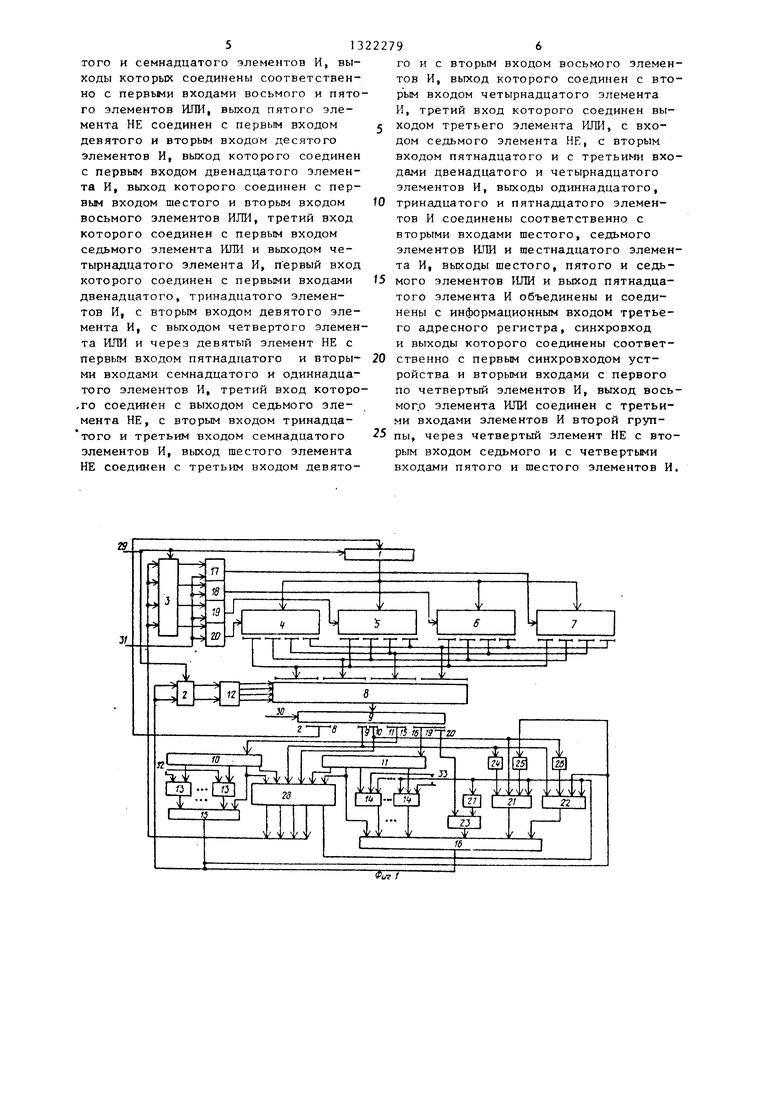

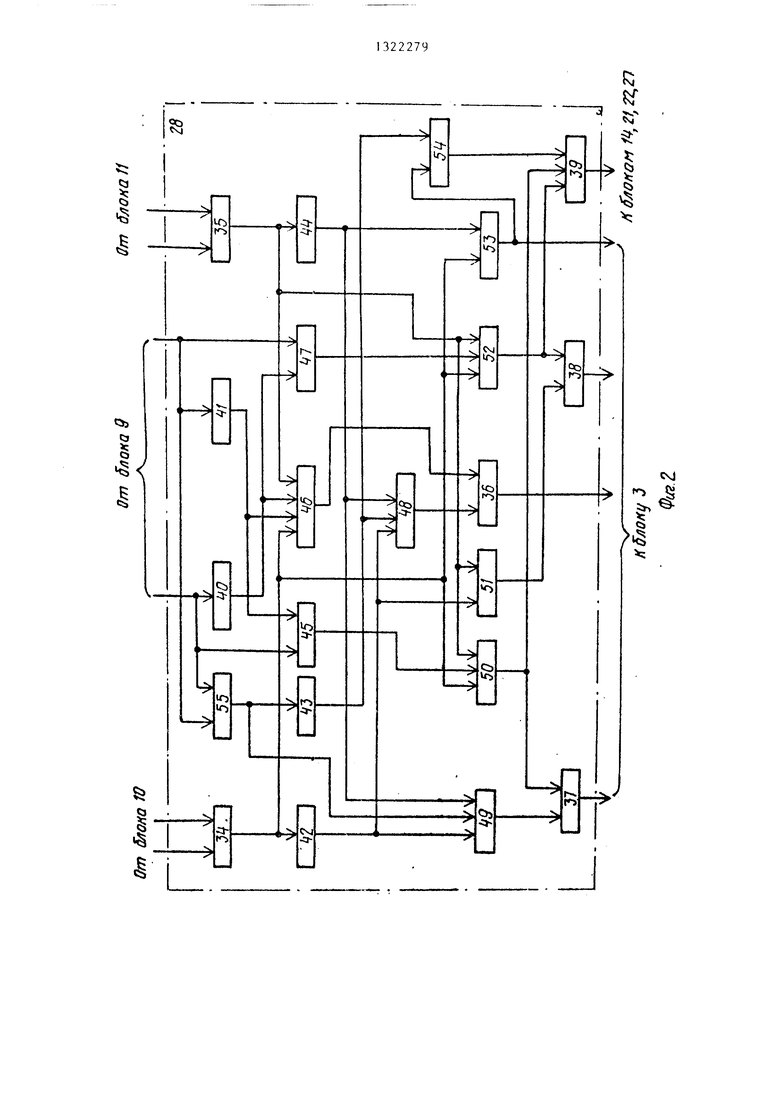

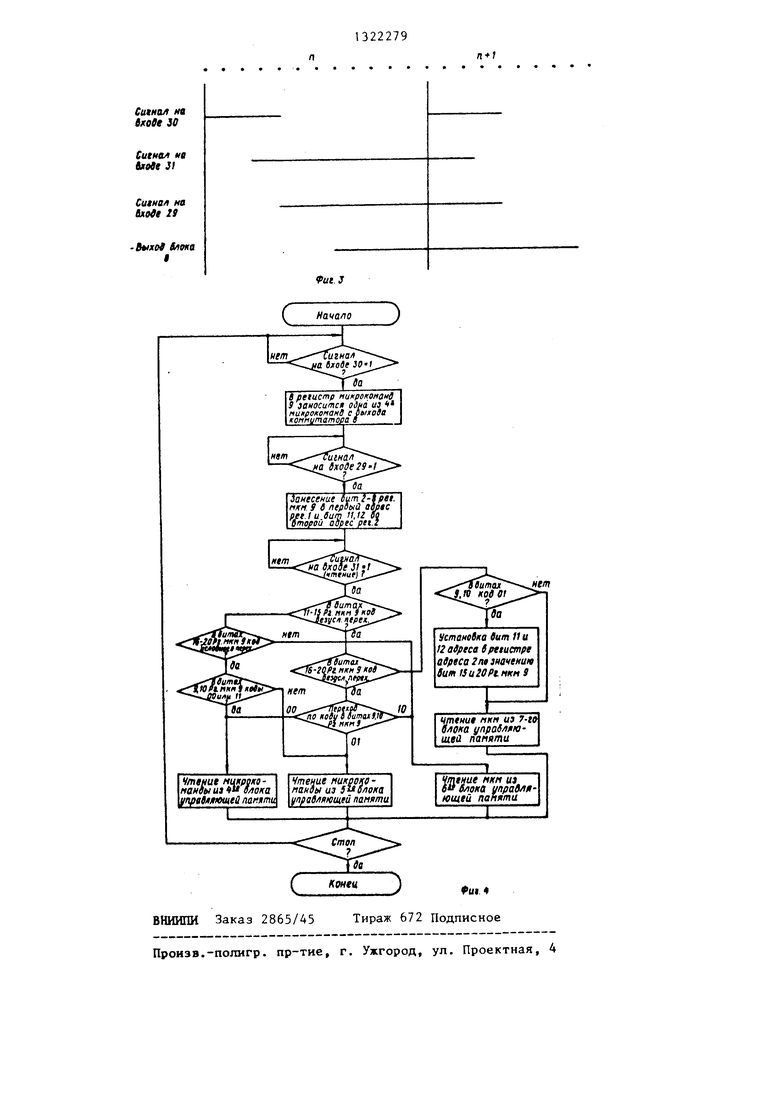

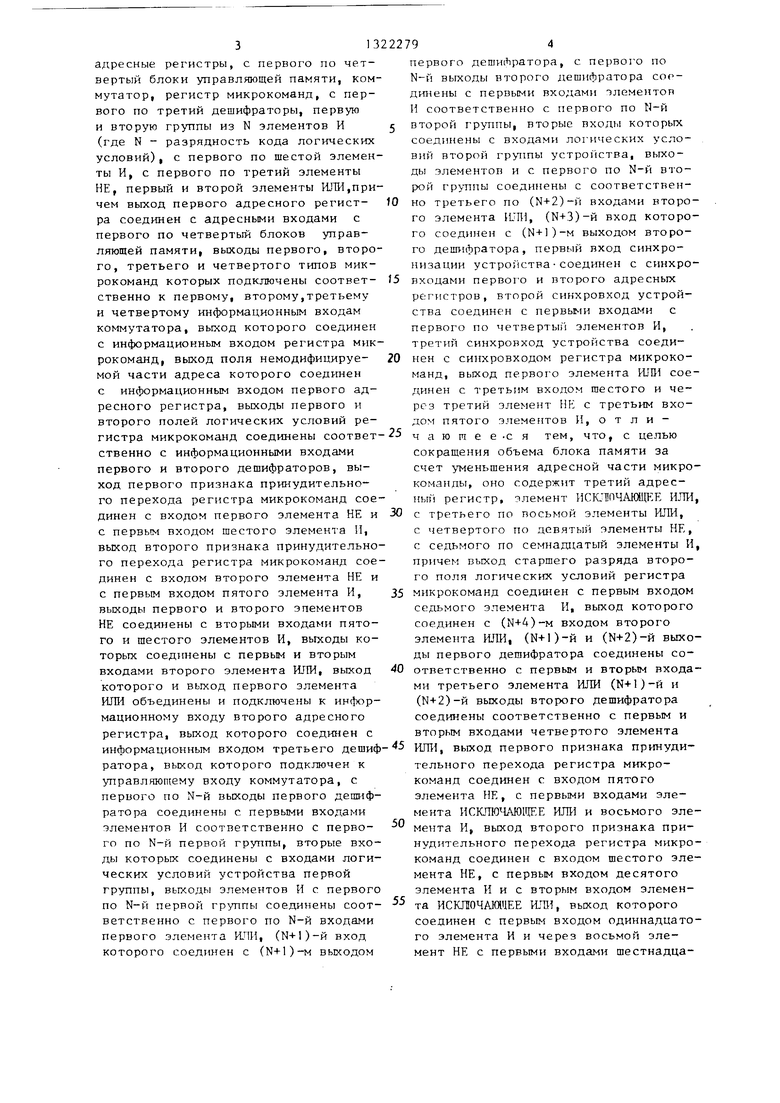

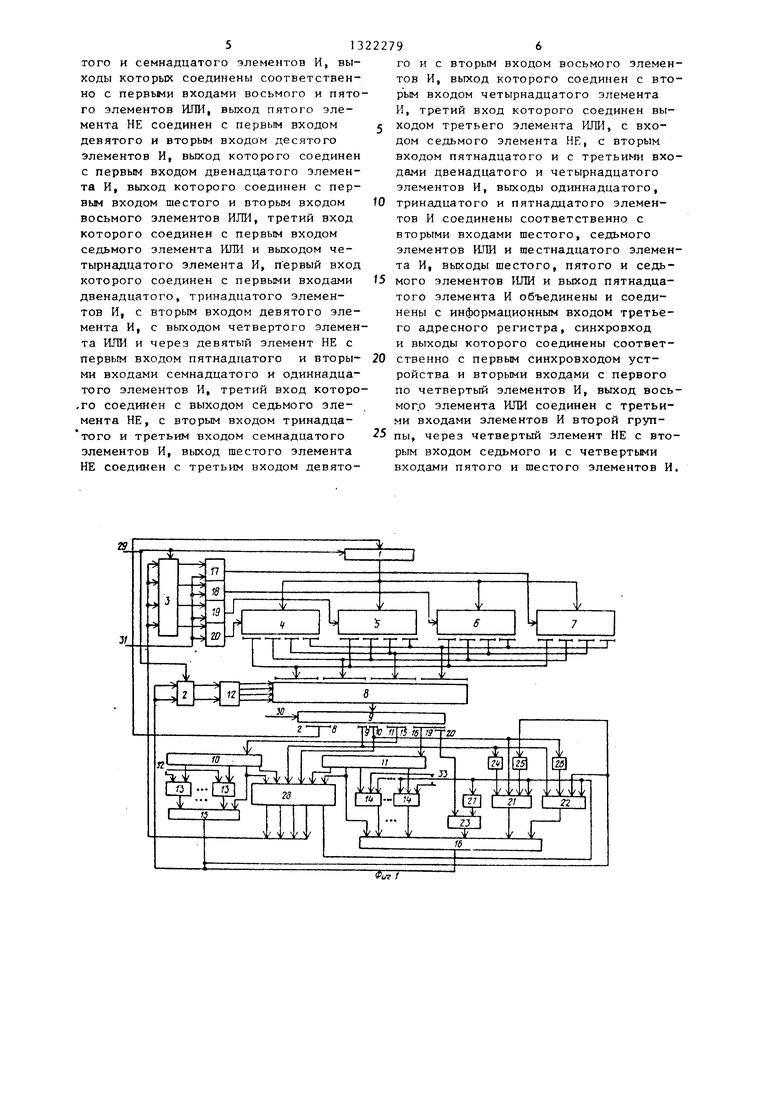

схема устройства микропрограммного управления; на фиг. 2 - функциональная схема блока анализа перехода; на фиг. 3 - временная диаграмма работы этого устройства; на фиг. 4 - блок- схема алгоритма работы.

Устройство микропрограммного управления (фиг.1) содержит первый , второй 2 и третий 3 адресные регист- ры, первый 4, второй 5, третий 6 и четвертый 7 блоки управляющей памяти коммутатор 8, регистр микрокоманд 9, первый 10, второй 11 и третий 12 дешифраторы, первую 13 и вторую 14 группы элементов И, первый 15 и второй 16 элеметы ЯЛИ, первый 17, второй 18, третий 19, четвертый 20, пятый 21, шестой 22 и седьмой 23 элементы И, перпы11 24, второй 25, третий 26 и четвертый 27 элементы НЕ, блок 28 анализа перехода н подключается к внешним цеп.гм с помощью шин 29-31 Установка адреса , Установка регистра и Чтение соответственно, а также гр ттпой шин 32 и 33 Условие 1 и Условие 2 соответственно .

Блок анализа перехода (фиг.2) содержит шесть элементов ИЛИ 34-39, пять элементов НЕ 40-44, десять эле- ментов И 45-54 и элемент ИСКЛЮЧ(}а.ЦЕЕ ИЛИ 55.

Условия формирования блоков управляющей памяти: первый блок формирует ся из микрокоманд ветвлений на четыре направления; второй блок формируется из микрокоманд ветвлений на три направления (с принудительным переходом); третий блок формируется из микрокоманд ветвлений на два направления с возможными значениями бит 11,12 адреса ХО или XI; четвертый блок (У рмируется из микрокоманд ветвлений на два направления с возмож- ными значениями бит 11, 12 адреса ХО 11ли XI .

Блок 28 анализа перехода гю зна- ченшо кода в битах 9,10,11-15 и 16 20 текущей микрокоманды, которая находится в регистре микрокоманд 9, вы- рабатьшает разрешение на выбор соответствующего блока управляющей памяти.

Это разрешение фиксируется в третьем адресном регистре 3 по сигналу на шине 29 Установка адреса.По сих налу на шине 31 происходит выбор соответствующего блока управляющей памяти.

Следующая микрокоманда выбирается из первого блока управляющей памяти, если в текущей микрокоманде нет принудительного перехода (т.е. коды в битах 9, 10 не равны 01 или 10), а в битах 11-15 и 16-20 коды условного перехода; из второго блока, если в текущей микрокоманде в битах 11-15 и 16-20 коды условных переходов, а биты 9,10 имеют значение 01 или 10; из третьего блока, если в текущей микрокоманде в битах 11-15 код условного перехода, а в битах 16-20 код безусловного перехода; из четвер- тот о блока, если в текущей микрокоманде в битах 11-15 код безусловного перехода, а в битах 16-20 код условного перехода.

Каждую микрокоманду можно адресовать в первых трех блоках безусловным переходом. Выбор блока определяется кодом в битах 9,10 регистра микрокоманд (00,01,10).

Чтобы адресовать микрокоманду безусловно в четвертом блоке, необхо- мо в битах 9,10 регистра микрокоманд иметь код 01 и выполнить последнее условие формирования блоков управляющей памяти.

Биты 11 и 12 регистра адреса (х)р- мируются при безусловном переходе по значению бит 15 и 20 регистра микрокоманд. При кодах безусловного перехода в битах 11-15 и 16-20 регистра микрокоманд или в битах 11-15 безусловного, а в битах 16-20 условного перехода коды принудительного перехода в битах 9,10 не имеют смысла, поэтому их значение можно использовать для выбора соответствующего блока управляющей памяти при адресации микрокоманды безусловным переходом .

Формула изобретения

Устройство микропрограммного управления, содержащее первый н второй

адресные регистры, с первого по четвертый блоки управляющей памяти, коммутатор, регистр микрокоманд, с первого по третий дешифраторы, первую и вторую группы из N элементов И (где N - разрядность кода логических условий), с первого по шестой элементы И, с первого по третий элементы НЕ, первый и второй элементы ИЛИ|Приго дешифратора, первый вход синхронизации устройствасоединен с синхрочем выход первого адресного регист- 10 но третьего по (Н+2)-й входами второ- ра соединен с адресными входами с го элемента IL Tli, (К+3)-й вход которо- первого по четвертый блоков управ- го соединен с (N+1)-M выходом второ- ляющей памяти, вьсходы первого, второго, третьего и четвертого типов микрокоманд которых подключены соответ- J5 входами первого и второго адресных ственно к первому, второму,третьему регистров, второй синхровход устрой- и четвертому информационным входам ства соединен с первьми входами с коммутатора, выход которого соединен первого по четвертый элементов И,

третий синхровход устройства соединен с синхровходом регистра микрокоманд, выход nepBoi o элемента ШБ1 соединен с третьим входом шестого и через третий элемент Нр с третьим входом пятого элементов И, о т л и с информационным входом регистра микрокоманд, выход поля немодифицируе- 20 мой части адреса которого соединен с информационным входом первого адресного регистра, выходы первого и второго полей логических условий регистра микрокоманд соединены соответ-25 ственно с информационными входами первого и второго дешифраторов, выход первого признака принудительного перехода регистра микрокоманд соединен с входом первого элемента НЕ и 30 с третьего по восьмой элементы ИШ-i, с первым входом шестого элемента И, с четвертого по девятый элементы НЕ, выход второго признака принудительного перехода регистра микрокоманд соединен с входом второго элемента НЕ и с первым входом пятого элемента И, выходы первого и второго эпементов НЕ соединены с вторыми входами пятого и шестого элементов И, выходы которых соединены с первым и вторым входами второго элемента ИЛИ, выход которого и выход первого элемента ИЛИ объединены и подключены к информационному входу второго адресного регистра, выход которого соединен с информационным входом третьего дешиф- -5 ИЛИ, выход первого признака принуди- ратора, выход которого подключен к тельного перехода регистра микро- управляюп5ему входу коммутатора, с первого по N-й выходы первого дешифчаюгаее-ся тем, что, с целью сокращения объема блока памяти за счет уменьшения адресной части микрокоманды, оно содержит третий адресный регистр, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,

с седьмого по семнадцатый элементы И, причем выход старшего разряда второго поля логических условий регистра

35 микрокоманд соединен с первым входом седьмого элемента И, выход которого соединен с (N+4)-M входом второго элемента ИЛИ, (Н+1)-й и (Ы+2)-й выходы первого дешифратора соединены со40 ответственно с первым и вторым входами третьего элемента ИЛИ ()-й и (К+2)-й вьгходы второго дешифратора соединены соответственно с первым и вторым входами четвертого элемента

команд соединен с входом пятого элемента НЕ, с первыми входами элемента ИСКЛЮЧАЮНЦ-Е ИЛИ и восьмого элемента И, выход второго признака принудительного перехода регистра микрокоманд соединен с входом шестого элемента НЕ, с первым входом десятого элемента И и с вторым входом элеменратора соединены с первыми входами элементов И соответственно с первого по N-й первой группы, вторые входы которых соединены с входами логических условий устройства первой группы, выходы элементов И с первого

50

команд соединен с входом пятого элемента НЕ, с первыми входами элемента ИСКЛЮЧАЮНЦ-Е ИЛИ и восьмого элемента И, выход второго признака принудительного перехода регистра микрокоманд соединен с входом шестого элемента НЕ, с первым входом десятого элемента И и с вторым входом элеменпо N-й первой группы соединены соот- та ИСКЛОЧАЮЩЕЕ ИЛИ, выход которого ветственно с первого по N-й входами соединен с первым входом одиннадцато- первого элемента ИЛИ, (N-l-l)-й вход которого соединен с (N+1)-M выходом

го элемента И и через восьмой элемент НЕ с первыми входами шестнадца522794

первого дешифратора, с первого по N-Й выходы второго дешифратора соединены с первыми входами -элементоп Н соответственно с первого по N-й второй группы, вторые входы которых соединены с входами логических условий второй ycTpoi icTBa, выходы элементов и с первого по N-й второй группы соединены с соответственго дешифратора, первый вход синхронизации устройствасоединен с синхроно третьего по (Н+2)-й входами второ- го элемента IL Tli, (К+3)-й вход которо- го соединен с (N+1)-M выходом второ- входами первого и второго адресных регистров, второй синхровход устрой- ства соединен с первьми входами с первого по четвертый элементов И,

с третьего по восьмой элементы ИШ-i, с четвертого по девятый элементы НЕ, ИЛИ, выход первого признака принуди- тельного перехода регистра микро-

чаюгаее-ся тем, что, с целью сокращения объема блока памяти за счет уменьшения адресной части микрокоманды, оно содержит третий адресный регистр, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,

с третьего по восьмой элементы ИШ-i, с четвертого по девятый элементы НЕ, ИЛИ, выход первого признака принуди- тельного перехода регистра микро-

с седьмого по семнадцатый элементы И, причем выход старшего разряда второго поля логических условий регистра

микрокоманд соединен с первым входом седьмого элемента И, выход которого соединен с (N+4)-M входом второго элемента ИЛИ, (Н+1)-й и (Ы+2)-й выходы первого дешифратора соединены соответственно с первым и вторым входами третьего элемента ИЛИ ()-й и (К+2)-й вьгходы второго дешифратора соединены соответственно с первым и вторым входами четвертого элемента

с третьего по восьмой элементы ИШ-i, с четвертого по девятый элементы НЕ, ИЛИ, выход первого признака принуди- тельного перехода регистра микро-

команд соединен с входом пятого элемента НЕ, с первыми входами элемента ИСКЛЮЧАЮНЦ-Е ИЛИ и восьмого элемента И, выход второго признака принудительного перехода регистра микрокоманд соединен с входом шестого элемента НЕ, с первым входом десятого элемента И и с вторым входом элемента ИСКЛОЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом одиннадцато-

та ИСКЛОЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом одиннадцато-

го элемента И и через восьмой элемент НЕ с первыми входами шестнадцатого и семнадцатого элементов И, выходы которых соединены соответственно с первыми входами восьмого и пятого элементов ИЛИ, выход пятого элемента НЕ соединен с первым входом девятого и вторым входом десятого элементов И, выход которого соединен с первым входом двенадцатого элемента И, выход которого соединен с первым входом шестого и вторым входом восьмого элементов ИЛИ, третий вход которого соединен с первым входом седьмого элемента ИЛИ и выходом четырнадцатого элемента И, п ервый вход которого соединен с первыми входами двенадцатого, тринадцатого элементов И, с вторым входом девятого элемента И, с выходом четвертого элемента ИЛИ и через девятый элемент НЕ с первым входом пятнадцатого и вторыми входами семнадцатого и одиннадцатого элементов И, третий вход которо- ,го соединен с выходом седьмого зле- мента НЕ, с вторым входом тринадца- того и третьим входом семнадцатого элементов И, выход шестого элемента НЕ соединен с третьим входом девятого и с вторым входом восьмого элементов И, выход которого соединен с вторым входом четырнадцатого элемента И, третий вход которого соединен выходом третьего элемента ИЛИ, с входом седьмого элемента НЕ, с вторым входом пятнадцатого и с третьими входами двенадцатого и четырнадцатого элементов И, выходы одиннадцатого,

тринадцатого и пятнадцатого элементов И соединены соответственно с вторыми входами шестого, седьмого элементов ИЛИ и шестнадцатого элемента И, выходы шестого, пятого и седьмого элементов ИЛИ и выход пятнадцатого элемента И объединены и соединены с информационным входом третьего адресного регистра, синхровход и выходы которого соединены соответственно с первым синхровходом устройства и вторыми входами с первого по четвертый элементов И, выход восьмого элемента ИЛИ соединен с третьими входами элементов И второй группы, через четвертый элемент НЕ с вторым входом седьмого и с четвертыми входами пятого и шестого элементов И.

§

«55

сз

§

Ri

55

Cvj r J

.t

V

Сынол на вхоОв 30

CutHO W Лиове 31

Сигнал на txoSt 19

-Выяов 8лта I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1986 |

|

SU1322280A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Микропроцессор | 1985 |

|

SU1290340A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2049347C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046396C1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для сжатия и развертывания данных | 1985 |

|

SU1359791A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1283761A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

Устройство относится к области вычислительной техники и может быть применено в центральных процессорах в качестве управляющих блоков. Цель изобретения - сокращение объема блока управляющей памяти за счет уменьшения адресной части микрокоманды. Устройство содержит три адресньк регистра, четыре блока управляющей памяти, коммутатор, регистр микрокоманд, три дешифратора, две группы элементов и восемь элементов ИЛИ,семнадцать элементов И, девять элементов НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.Введение адресного регистра, шести элементов НЕ, одиннадцати элементов И, шести элементов ИЛИ и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ приводит к достижение цели., 4 ил. 1 (Л

I petucfip никроконанв у заносится aijfu w HUKpOKOfiaHo с obinoStt коппитатора I

занесение cuml-tfet. пкп 9 6 первый eiotc pet. I и Sum t, IZ fo fmofou аорес pn.Z

Htm

Установка вит t1 и Падрпа tpttumft atpica 2nt значению Sum ISu2ePtHKnS

Чтпшв HKH из 7-to блока упра9/Н1Ю- шей паняти

Чтение нанеыизЧКоней

ВНИИПИ Заказ 2865/45 Тираж 672 Подписное Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

f UI 4

| Микропрограммное устройство управления | 1981 |

|

SU1005050A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ПРИБОР ДЛЯ ИНТЕГРИРОВАНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ И ДЛЯ НАХОЖДЕНИЯ КОРНЕЙ ЧИСЛЕННЫХ УРАВНЕНИЙ | 1924 |

|

SU1045A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-12—Подача