Изобретение относится к вычислительной технике и может быть применено в центральных процессорах в качестве управляющего блока или в других устройствах, управляемых микропрограммно.

Цель изобретения - сокращение объема используемого оборудования путем обеспечения одновременного считывани из управляющей памяти микрокоманд ветвлений и условий для их выбора.

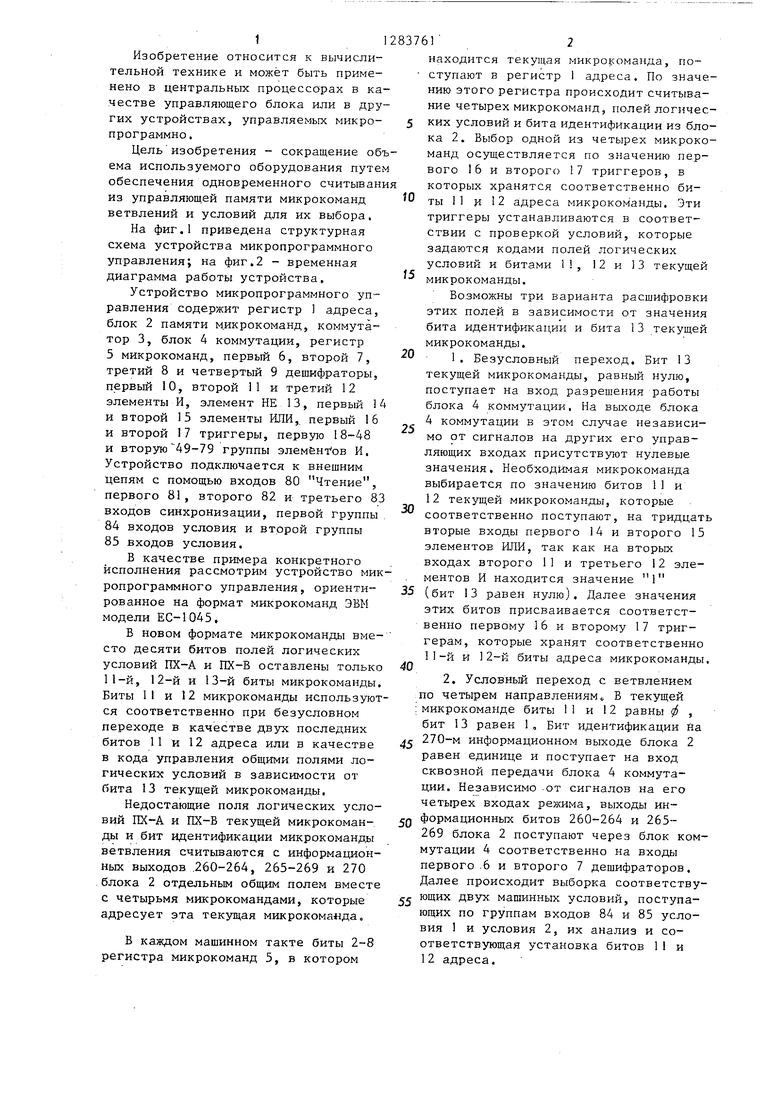

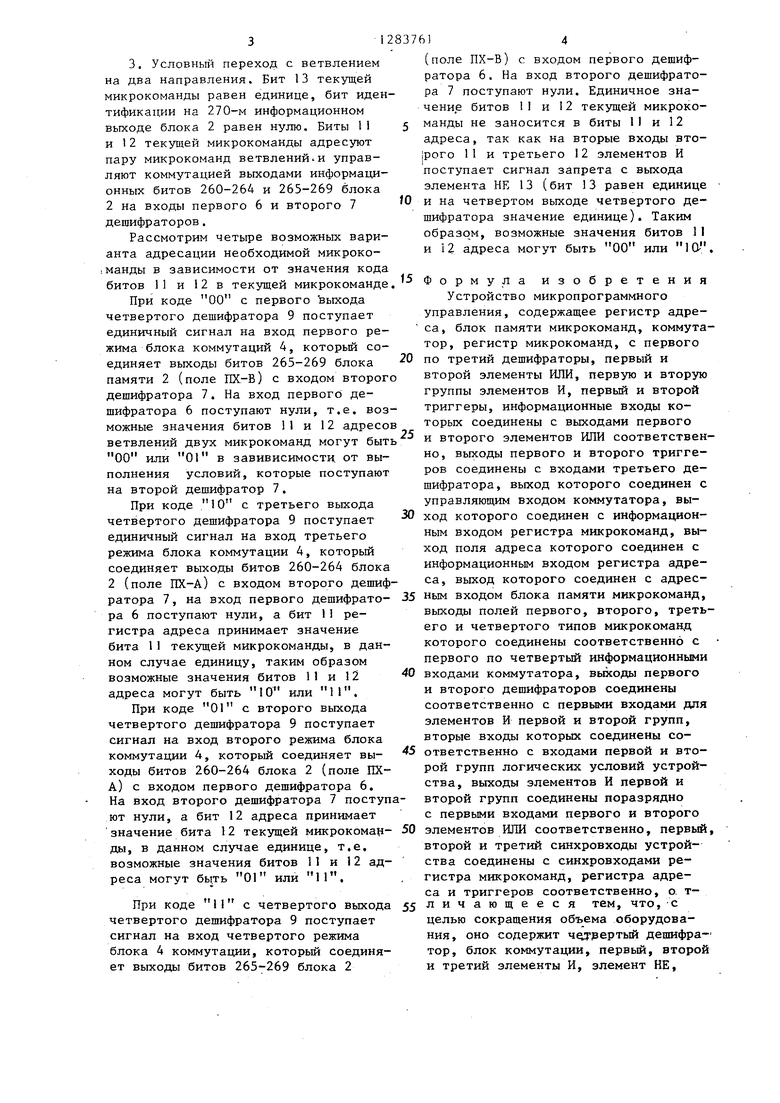

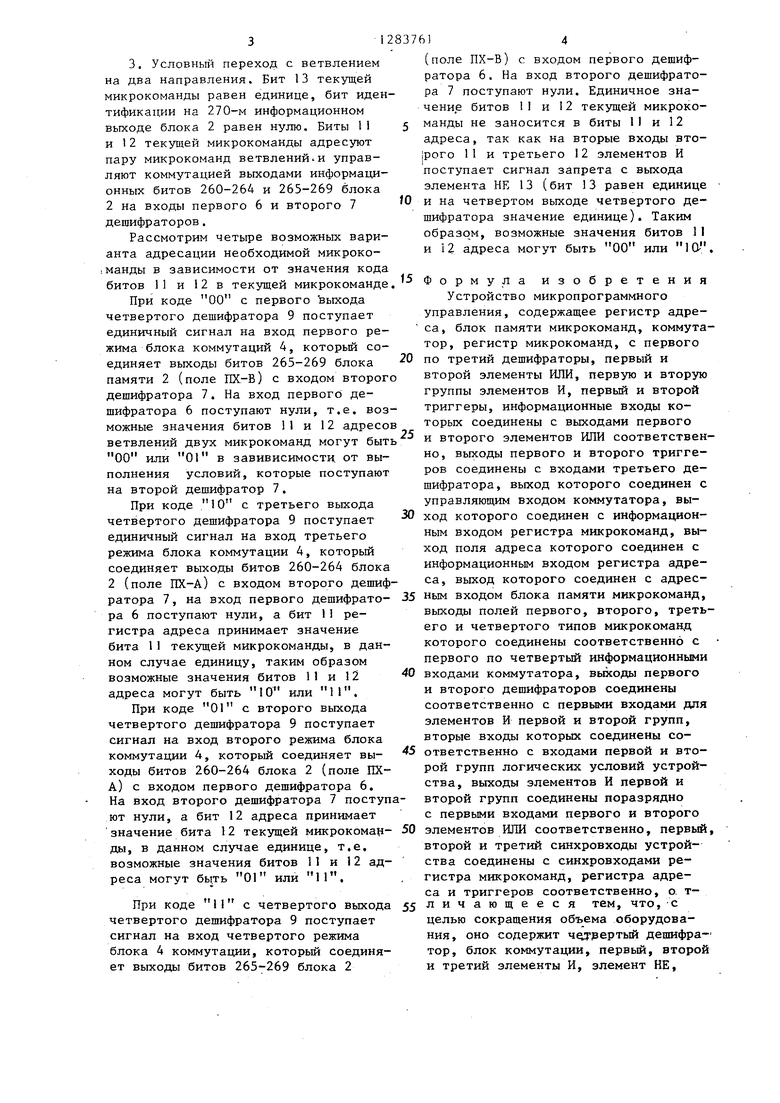

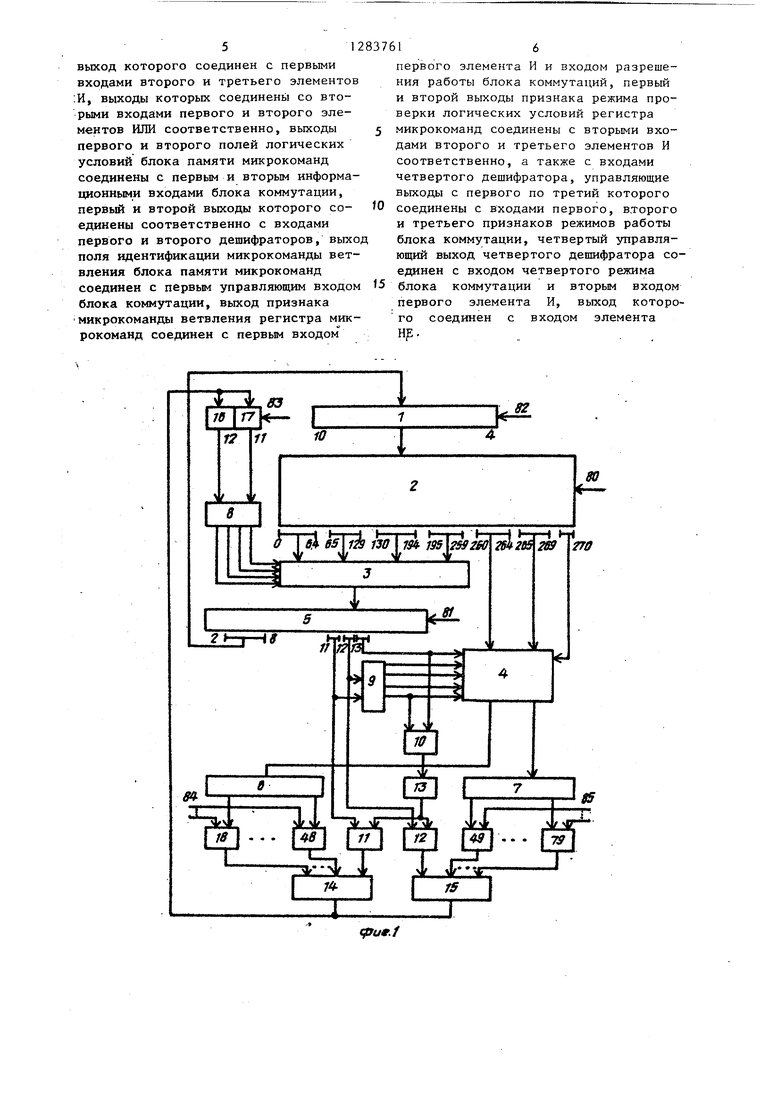

На фиг.1 приведена структурная схема устройства микропрограммного управления; на фиг.2 - временная диаграмма работы устройства.

Устройство микропрограммного управления содержит регистр 1 адреса, блок 2 памяти микрокоманд, коммутатор 3, блок 4 коммутации, регистр 5 микрокоманд, первый 6, второй 7, третий 8 и четвертьш 9 дешифраторы, первый 10, второй 11 и третий 12 элементы И, элемент НЕ 13, первый 14 и второй 15 элементы ИЛИ, первый 16 и второй 17 триггеры, первую 18-48 и вторую 49-79 группы элембн1 ов И. Устройство подключается к внешним цепям с помощью входов 80 Чтение, первого 81, второго 82 и третьего 83 входов синхронизации, первой группы

84входов условия и второй группы

85входов условия.

В качестве примера конкретного исполнения рассмотрим устройство микропрограммного управления, ориентированное на формат микрокоманд ЭВМ модели ЕС-1045,

В новом формате микрокоманды вме- сто десяти битов полей логических условий ПХ-А и ПХ-В оставлены только 11-й, 12-й и 13-й биты микрокоманды. Биты II и 12 микрокоманды используются соответственно при безусловном переходе в качестве двух последних битов 11 и 12 адреса или в качестве в кода управления общими полями логических условий в зависимости от бита 13 текущей микрокоманды.

Недостающие поля логических условий ПХ-А и ПХ-В текущей микрокоманды и бит идентификации микрокоманды ветвления считываются с информационных выходов .260-264, 265-269 и 270 блока 2 отдельным общим полем вместе с четырьмя микрокомандами, которые адресует эта текущая микрокоманда.

В каждом машинном такте биты 2-8 регистра микрокоманд 5, в котором

5

0

5

0

5

0

5

0

5

находится текущая микрокоманда, поступают в регистр 1 адреса. По значению этого регистра происходит считывание четырех микрокоманд, полей логических условий и бита идентификации из блока 2. Выбор одной из четырех микрокоманд осуществляется по значению первого 16 и второго 17 триггеров, в которых хранятся соответственно биты 11 и 12 адреса микрокоманды. Эти триггеры устанавливаются в соответствии с проверкой условий, которые задаются кодами полей логических условий и битами П, 12 и 13 текущей микрокоманды.

Возможны три варианта расшифровки этих полей в зависимости от значения бита идентификации и бита 13 текущей микрокоманды,

1, Безусловный переход. Бит 13 текущей микрокоманды, равный нулю, поступает на вход разрешения работы блока 4 коммутации. На выходе блока 4 коммутации в этом случае независимо от сигналов на других его управляющих входах присутствуют нулевые значения. Необходимая микрокоманда выбирается по значению битов 11 и 12 текущей микрокоманды, которые соответственно поступают, на тридцать вторые входы первого 14 и второго 15 элементов ИЛИ, так как на вторых входах второго 11 и третьего 12 элементов И находится значение 1 (бит 13 равен нулю). Далее значения этих битов присваивается соответственно первому 16 и второму 17 триггерам, которые хранят соответственно 11-и и 12-й биты адреса микрокоманды.

2. Условный переход с ветвлением по четырем направлениям,, Б текущей : микрокоманде биты 11 и 12 равны , бит 13 равен „ Бит идентификации йа 270-м информационном вьгкоде блока 2 равен единице и поступает на вход сквозной передачи блока 4 коммутации. Независимо -от сигналов на его четырех входах режима, выходы информационных битов 260-264 и 265- 269 блока 2 поступают через блок коммутации 4 соответственно на входы первого-6 и второго 7 дешифраторов. Далее происходит выборка соответствующих двух, машинных условий, поступающих по группам входов 84 и 85 условия 1 и условия 2, их анализ и соответствующая установка битов 11 и 12 адреса.

3. Условный переход с ветвлением на два направления. Бит 13 текущей микрокоманды равен единице, бит идентификации на 270-м информационном выходе блока 2 равен нулю. Биты 11 и 12 текущей микрокоманды адресуют пару микрокоманд ветвлений и управляют коммутацией выходами информационных битов 260-264 и 265-269 блока 2 на входы первого 6 и второго 7 дешифраторов.

Рассмотрим четыре возможных варианта адресации необходимой микроко- ;манды в зависимости от значения кода битов 11 и 12 в текущей микрокоманде

При коде 00 с первого выхода четвертого дещифратора 9 поступает единичный сигнал на вход первого режима блока коммутаций 4, которьм соединяет выходы битов 265-269 блока памяти 2 (поле ПХ-В) с входом второг дешифратора 7. На вход первого дешифратора 6 поступают нули, т.е. возможные значения битов 11 и 12 адресо ветвлений двух микрокоманд могут быт 00 или 01 в завивисимости, от выполнения условий, которые поступают на второй дешифратор 7.

При коде 10 с третьего выхода четвертого дешифратора 9 поступает единичный сигнал на вход третьего режима блока коммутации 4, который соединяет выходы битов 260-264 блока 2 (поле ПХ-А) с входом второго дешифратора 7, на вход первого дешифратора 6 поступают нули, а бит 1 1 регистра адреса принимает значение бита 11 текущей микрокоманды, в данном случае единицу, таким образом возможные значения битов 11 и 12 адреса могут быть 10 или 11.

При коде О с второго выхода четвертого дешифратора 9 поступает сигнал на вход второго режима блока коммутации 4, который соединяет выходы битов 260-264 блока 2 (поле ПХ- А) с входом первого дешифратора 6. На вход второго дешифратора 7 поступют нули, а бит 12 адреса принимает значение бита 12 текущей микрокоманды, в данном случае единице, т.е. возможные значения битов 11 и 12 адреса могут быть 01 или 11.

При коде 11 с четвертого выхода четвертого дешифратора 9 поступает сигнал на вход четвертого режима блока 4 коммутации, который соединяет выходы битов 265-269 блока 2

(поле ПХ-В) с входом первого дещифратора 6. На вход второго дешифратора 7 поступают нули. Единичное значение битов 11 и 12 текущей микрокоманды не заносится в биты 11 и 12 адреса, так как на вторые входы вто- jporo 11 и третьего 12 элементов И поступает сигнал запрета с выхода элемента НЕ 13 (бит 13 равен единице и на четвертом выходе четвертого дешифратора значение единице). Таким образом, возможные значения битов 11 и 12 адреса могут быть 00 или 10.

ф

ормула изобретения

Устройство микропрограммного управления, содержащее регистр адре- са, блок памяти микрокоманд, коммутатор, регистр микрокоманд, с первого

по третий дешифраторы, первый и

второй элементы ИЛИ, первую и вторую группы элементов И, первый и второй триггеры, информационные входы которых соединены с выходами первого

и второго элементов ИЛИ соответственно, выходы первого и второго триггеров соединены с входами третьего дешифратора, выход которого соединен с управляющим входом коммутатора, выход которого соединен с информационным входом регистра микрокоманд, выход поля адреса которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, выходы полей первого, второго, третьего и четвертого типов микрокоманд которого соединены соответственно с первого по четвертый информационными

входами коммутатора, выходы первого и второго дешифраторов соединены соответственно с первыми входами для элементов И первой и второй групп, вторые входы которых соединены соответственно с входами первой и второй групп логических условий устройства, выходы элементов И первой и второй групп соединены поразрядно с первыми входами первого и второго

элементов ИЛИ соответственно, первый, второй и третий синхровходы устройства соединены с синхровходами регистра микрокоманд, регистра адреса и триггеров соответственно, о тличающееся тем, что,-с

целью сокращения объема оборудования, оно содержит ч урертый дешифратор, блок коммутации, первый, второй и третий элементы И, элемент НЕ,

выход которого соединен с первыми входами второго и третьего элементов :И, выходы которых соединены со вторыми входами первого и второго элементов ИЛИ соответственно, выходы первого и второго полей логических условий блока памяти микрокоманд соединены с первым и вторым информа- 1Ц1ОННЫМИ входами блока коммутации, первый и второй выходы которого соединены соответственно с входами первого и второго дешифраторов, выхо поля идентификации микрокоманды ветвления блока памяти микрокоманд соединен с первым управляющим входом блока коммутации, выход признака микрокоманды ветвления регистра микрокоманд соединен с первым входом

. , (ЭД I

83

Ю

первого элемента И и входом разрешения работы блока коммутаций, первый и второй выходы признака режима проверки логических условий регистра микрокоманд соединены с вторыми входами второго и третьего элементов И соответственно, а также с входами четвертого дешифратора, управляющие выходы с первого по третий которого соединены с входами первого, в.торого и третьего признаков режимов работы блока коммутации, четвертый управляющий выход четвертого дешифратора соединен с входом четвертого режима блока коммутации и вторым входом первого элемента И, выход которого соединен с входом элемента . .

82

I

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1986 |

|

SU1381505A1 |

| Устройство микропрограммного управления | 1986 |

|

SU1322280A1 |

| Устройство микропрограммного управления | 1986 |

|

SU1322279A1 |

| Устройство для сбора диагностической информации о формировании адресов переходов микропрограмм | 1983 |

|

SU1290328A1 |

| Устройство для отладки программ | 1986 |

|

SU1410038A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммное устройство управления и отладки микропрограмм процессора | 1984 |

|

SU1168937A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Микропрограммное устройство управления | 1980 |

|

SU881748A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU842815A1 |

Устройство относится к области вычислительной техники и может быть применено в центральных процессорах в качестве управляющего блока или в других устройствах, управляемых микропрограммно. Цель изобретения - сокращение объема используемого оборудования. Устройство содержит регистр адреса, блок памяти микрокоманд, коммутатор, блок коммутации, регистр микрокоманд, четьфе дешифратора, три элемента И, элемент НЕ, два элемента ИЛИ, два триггера, две группы элементов И. Введение дешифратора, блока коммутации, трех элементов И и элемента НЕ обеспечивает достижение цели. 2 ил.

8

J I «i ffSlf fJO

I н-г-Н ь-гн

fTff

(ffur.t

I.

ШN

Составитель А.Афанасьев Редактор Л. -Пчелинская Техред Л. Сердюкова Корректор В. Бутяга

7442Г47

Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная,4

| Микропрограммное устройство управления | 1981 |

|

SU1005050A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное управляющее устройство | 1981 |

|

SU1005051A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-11—Подача