1

Изобретение относится к вычислительной технике и может быть применно в центральных процессорах в качестве управляющего блока или в других устройствах, управляемых микропрограммно .

Цель изобретения - сокращения обема используемого оборудования за счет уменьшения разрядности адресно части микрокоманды.

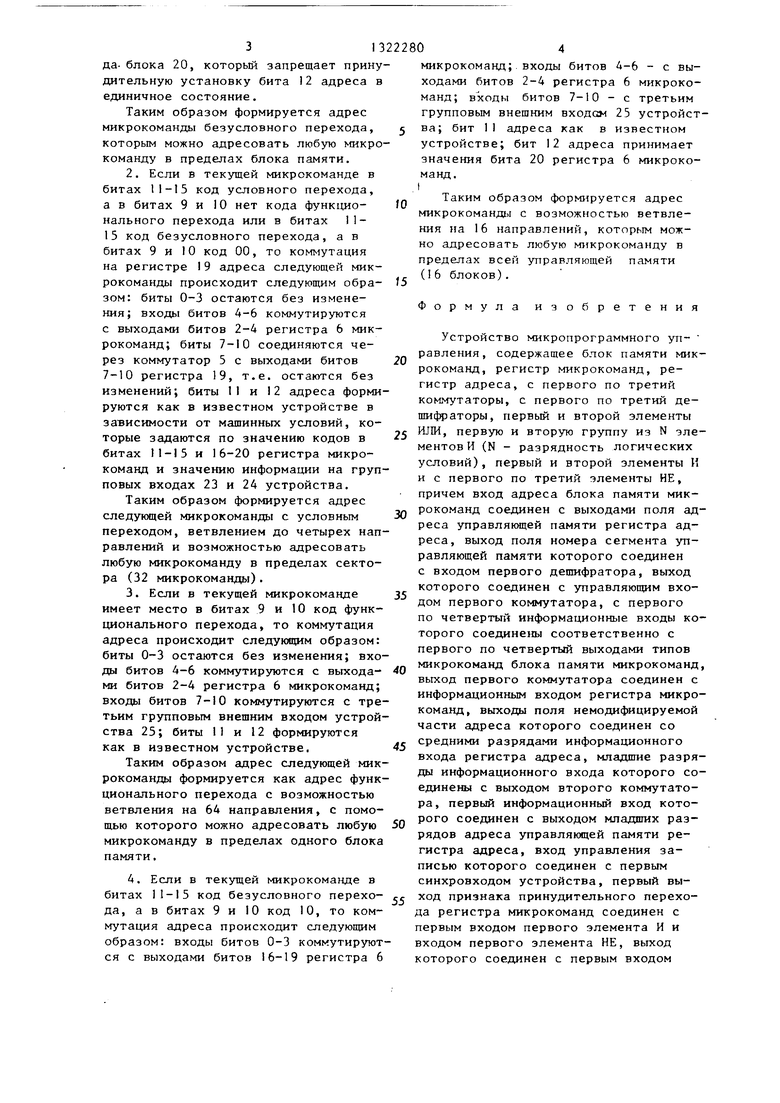

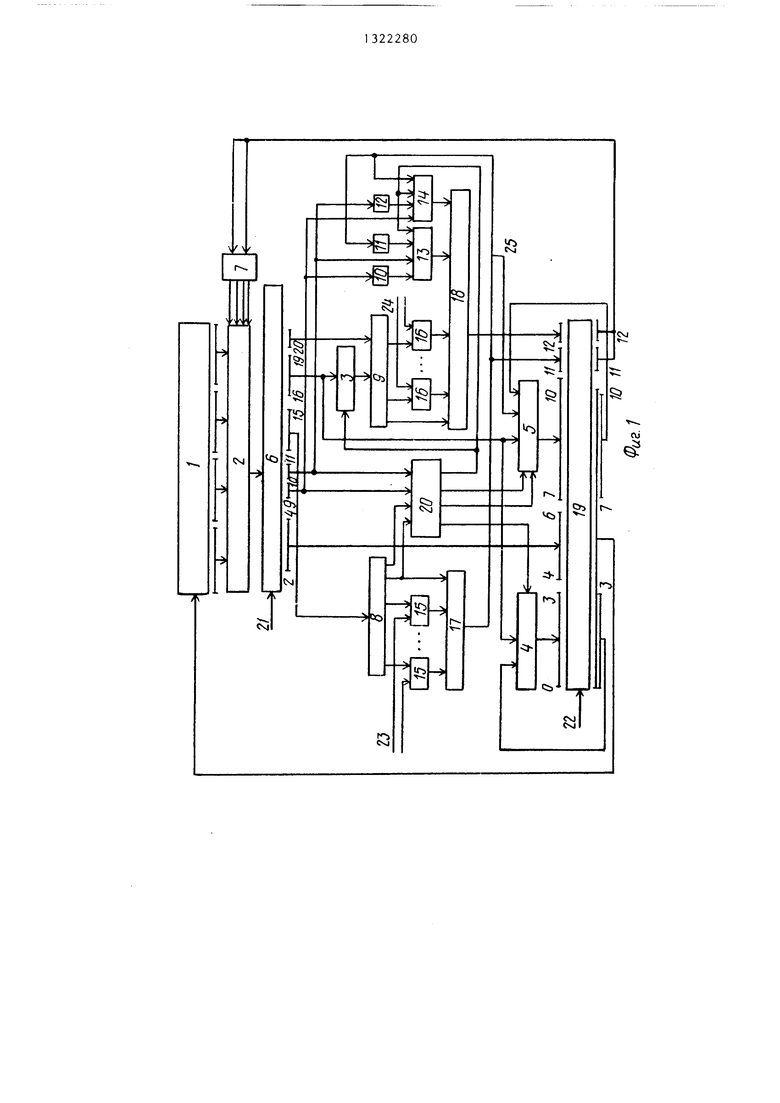

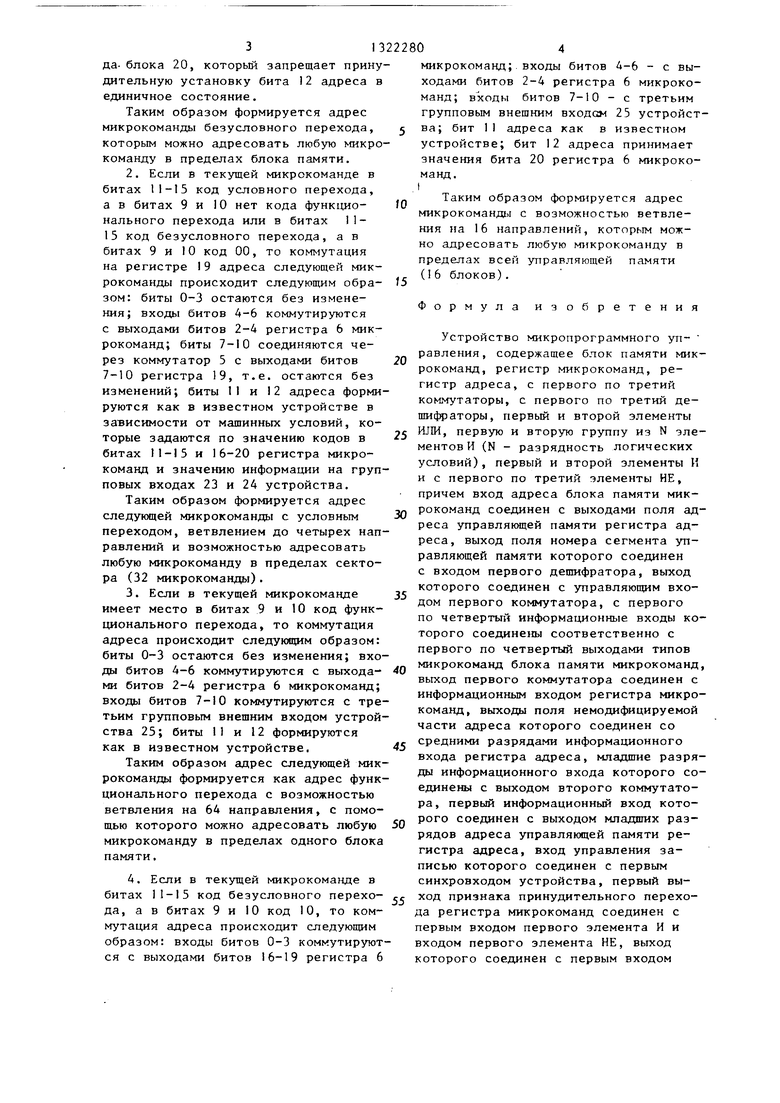

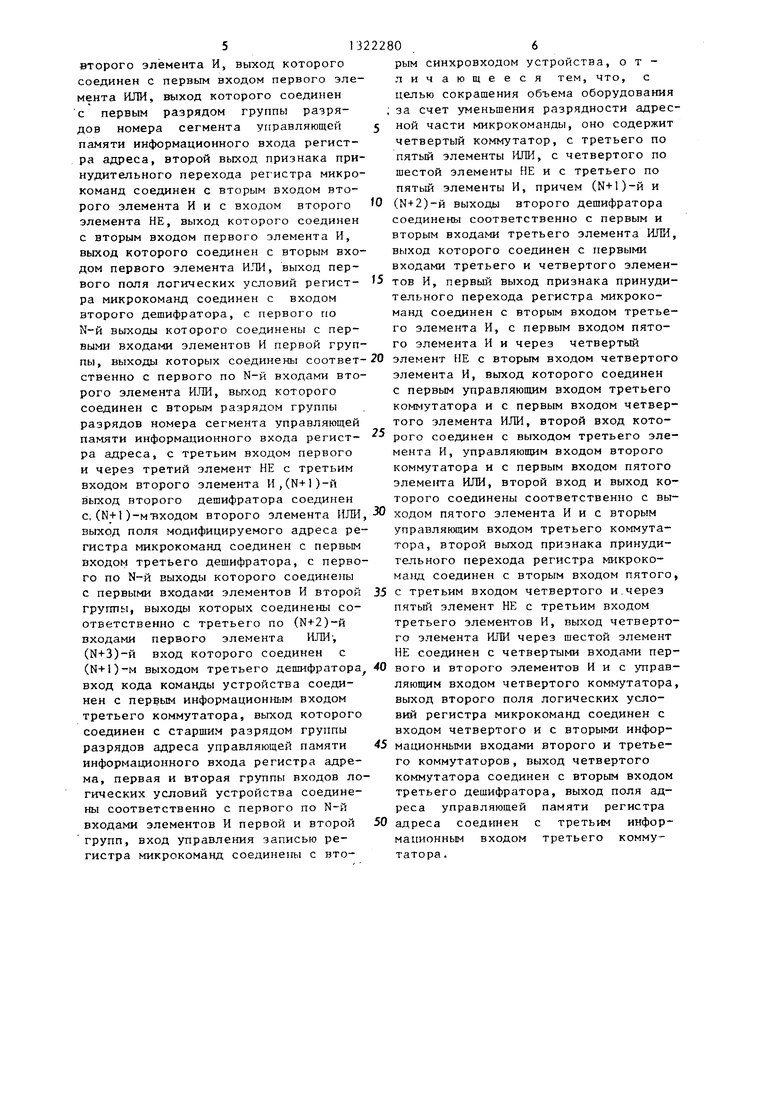

Fia фиг.1 приведена структурная схема устройства микропрограммного управления; на фиг.2 - функциональная схема блока анализа перехода.

Устройство микропрограммного управления (фиг.1) содержит блок 1 памяти микрокоманд, коммутаторы 2-5, регистр 6 микрокоманд, дешифраторы 7-9, элементы НЕ 10-12, элементы И 13 и 14, группы 15 и 16 элементов И элемент 1 ИЛИ 17 и 18, регистр 19 адреса, блок 20 анализа перехода и поключается к внешним цепям 21 и 22 синхронизирующи п1 входами, а также входами 23 и 24 логических условий и входом 25 кода операции.

Блок анализа перехода (фиг.2) содержит три элемента H.Tli 26-28, три элемента НЕ 29-31 и три элемента К 32--34.

15 ycTpoiicTBe используется п1М- нуди- тельная адресация, т.е. адрес следующей :икpoкoмaнды задается битами текущей микрокоманды в пределах одного Олока угфавляющей памяти.

Блок памяти микрокоманд конструк-- тивпо выполняется из 16 одинаковых независимых блоков. Поэтому для удобства рассмотрим адресацию одно- го из этих блоков.Каждый такой блок адресуется битами 4-10 регистра адреса. Два последних бита адреса микро1 . Если в текущей микрокоманде в битах 11-15 код безусловного перехода, а в битах 9 и 10 код равен 01, то коммутация на регистре 19 адреса следующей микрокоманды происходит

команды 11 и 12 связаны с реализацией условных переходов в шкpoпpoгpaм-45 с еДУющим образом: биты 0-3 соединя ;ax. По дешифрации битов 4-10 адреса

ются через коммутатор 4 с выходами битов 0-3 регистра 19, т.е. остаются без изменения; входы битов 4-6 соединяются с выходами битов 2-4 регистра 6 микpoкo aнд; входы битов 7-10 коммутируются через коммутатор 5 с выходами битов 16-19 регистра 6 микрокоманд; бит 11 адреса формируется по значению кодов в битах 11-15 регистра 6 микрокоманд (00000 или 00001); бит 12 адреса формируется по значению бита 20 регистра 6 микрокоманд; на четвертые входы блоков 3 и 14 постуггает сигнал с первого выхосчитывается сначала четыре микрокоманды иэ блока памяти, а далее по поступлении битов 11 и 12 выбирается одна из них.

Если в битах 11-15 код безусловного кода 00000 или 00001, а в битах 16-20 коды условного nepexo:i;a, то коды принудительного перехода в битах 9-10 регистра 6 ьшкрокоманд не имеют смысла и их значение можно использовать для г каза.ния способа фор1 Я рова- гия .дреса следующей микрокоманды.

Устройство работает следующим образом.

O

5

0

5

0

5

0

По значению битов 0-10 регистра 19 происходит считывание четьфех микрокоманд из блока 1. По значению битов 11 и 12 регистра 19 дешифратор 7 вырабатывает соответствуюшл1й сигнал на управляющий вход коммутатора 2. По синхросигналу на входе 21 устройства происходит занесение информации с выхода коммутатора 2 на регистр 6. По синхросигналу на входе 22 устройства происходит занесение информации в регистр 19 с выходов коммутаторов 4 и 5, битов 2-4 регистра 6 и элементов 17 и 18. Блоки 8, 15 и 17 используются для модификации бита 11 адреса, значение которого зависит от кодов в битах 11-15 регистра 6 и сигналов на групповом входе 23. Аналогично блоки 9, 16, 18 служат для модификации бита 12 адреса в зависимости от кодов в битах 16-20 регистра 6 и сигналов на групповом входе 24. Блоки 10-14 слркат для принудительной установки бита 12 адреса в единичное состояние, если в битах 9 и 10 регистра 6 значение кодов 01 или 10, л бит 11 адреса равен соответственно О или 1. Блок 20 анализа перехода в зависимости от КОДОБ в битах 9-10 и 11-15 регистра 6 микрокоманд вырабатывает упрлвлжтпис сиг- :ча:1Ы на коммутаторы 3-5. В -inriiicH- мости от сочетания . кодов Б этих битах адрес следую1ией г- икроко- формируется одним из следующих способов.

1 . Если в текущей микрокоманде в битах 11-15 код безусловного перехода, а в битах 9 и 10 код равен 01, то коммутация на регистре 19 адреса следующей микрокоманды происходит

5 с еДУющим образом: биты 0-3 соединяс еДУющим образом: биты 0-3 соединя

ются через коммутатор 4 с выходами битов 0-3 регистра 19, т.е. остаются без изменения; входы битов 4-6 соединяются с выходами битов 2-4 регистра 6 микpoкo aнд; входы битов 7-10 коммутируются через коммутатор 5 с выходами битов 16-19 регистра 6 микрокоманд; бит 11 адреса формируется по значению кодов в битах 11-15 регистра 6 микрокоманд (00000 или 00001); бит 12 адреса формируется по значению бита 20 регистра 6 микроко. манд; на четвертые входы блоков 3 и 14 постуггает сигнал с первого выхода- блока 20, который запрещает принудительную установку бита 12 адреса в единичное состояние.

Таким образом формируется адрес микрокоманды безусловного перехода, которым можно адресовать любую микрокоманду в пределах блока памяти.

2.Если в текущей микрокоманде в битах 11-15 код условного перехода, а в битах 9 и 10 нет кода функ1Ц1о- нального перехода или в битах 11- 15 код безусловного перехода, а в битах 9 и 10 код 00, то коммутация на регистре I9 адреса следующей микрокоманды происходит следующим образом: биты 0-3 остаются без изменения; входы битов 4-6 коммутируются

с выходами битов 2-4 регистра 6 микрокоманд; биты 7-10 соединяются через коммутатор 5 с выходами битов 7-10 регистра 19, т.е. остаются без изменений; биты II и 12 адреса формируются как в известном устройстве в зависимости от мащинных условий, которые задаются по значению кодов в битах 11-15 и 16-20 регистра микрокоманд и значению информации на групповых входах 23 и 24 устройства.

Таким образом формируется адрес следующей микрокоманды с условным переходом, ветвлением до четырех направлений и возможностью адресовать любую микрокоманду в пределах сектора (32 микрокоманды).

3.Если в текущей микрокоманде имеет место в битах 9 и 10 код функционального перехода, то коммутация адреса происходит следующим образом: биты 0-3 остаются без изменения; входы битов 4-6 коммутируются с выходами битов 2-4 регистра 6 микрокоманд; входы битов 7-10 коммутируются с третьим групповым внешним входом устройства 25; биты 11 и 12 формируются как в известном устройстве.

Таким образом адрес следующей микрокоманды формируется как адрес функционального перехода с возможностью ветвления на 64 направления, с помощью которого можно адресовать любую микрокоманду в пределах одного блока памяти.

4.Если в текущей микрокоманде в битах 11-15 код безусловного перехода, а в битах 9 и 10 код 10, то коммутация адреса происходит следующим образом: входы битов 0-3 коммутируются с выходами битов 16-19 регистра 6

микрокоманд; входы битов 4-6 - с выходами битов 2-4 регистра 6 микрокоманд; входы битов 7-10 - с третьим групповым внешним входом 25 устройст- ва; бит 11 адреса как в известном устройстве; бит 12 адреса принимает значения бита 20 регистра 6 fикpoкo- манд.

Таким образом формируется адрес микрокоманды с возможностью ветвления на 16 направлений, которым можно адресовать любую микрокоманду в пределах всей управляющей памяти (I6 блоков).

Формула изобретения

Устройство микропрограммного уп- равления, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса, с первого по третий коммутаторы, с первого по третий де- щифраторы, первый и второй элементы

И1Ш, первую и вторую группу из N элементов И (N - разрядность логических условий), первый и второй элементы И и с первого по третий элементы НЕ, причем вход адреса блока памяти 1чикрокоманд соединен с выходами поля адреса управляющей памяти регистра адреса, выход поля номера сегмента управляющей памяти которого соединен с входом первого дешифратора, выход которого соединен с управляющим входом первого коммутатора, с первого по четвертый информационные входы которого соединены соответственно с первого по четвертый выходами типов

микрокоманд блока памяти микрокоманд, выход первого коммутатора соединен с информационным входом регистра микрокоманд, выходы поля немодифицируемой части адреса которого соединен со

средними разрядами информационного входа регистра адреса, младщие разряды информационного входа которого соединены с выходом второго коммутатора, первый информационный вход которого соединен с выходом младших разрядов адреса управляющей памяти регистра адреса, вход управления записью которого соединен с первым синхровходом устройства, первый выход признака принудительного перехода регистра микрокоманд соединен с первым входом первого элемента И и входом первого элемента НЕ, выход которого соединен с первым входом

второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым разрядом группы разрядов номера сегмента управляющор памяти информационного входа регистра адреса, второй выход признака принудительного перехода регистра микрокоманд соединен с вторым входом второго элемента И и с входом второго элемента НЕ, выход которого соединен с вторым входом первого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход первого поля логических условий регистра микрокоманд соединен с входом второго дешифратора, с первого по N-й выходы которого соединены с перрым синхровходом устройства, о т - лич ающееся тем, что, с целью сокращения объема оборудования ; за счет уменьшения разрядности адрес- 5 ной части микрокоманды, оно содержит четвертый коммутатор, с третьего по пятый элементы ИЛИ, с четвертого по шестой элементы НЕ и с третьего по пятый элементы И, причем (Ы+1)-й и 10 (Ы+2)-й выходы второго дешифратора соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элемен- 5 тов И, первый выход признака принудительного перехода регистра микрокоманд соединен с вторым входом третьего элемента И, с первым входом пятого элемента И и через четвертый

выми входами элементов И первой группы, выходы которых соединены соответ-20 элемент НЕ с вторым входом четвертого ственно с первого по N-й входами вто- элемента И, выход которого соединен рого элемента ИЛИ, выход которого

с первым управляющим входом третьего коммутатора и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, управляюш 1М входом второго коммутатора и с первым входом пятого элемента ИЛИ, второй вход и выход которого соединены соответственно с высоединен с вторым разрядом группы разрядов номера сегмента управляющей памяти информационного входа регистра адреса, с третьим входом первого и через третий элемент НЕ с третьим входом второго элемента И,(М+1)-й выход второго дешифратора соединен

25

с первым управляющим входом третьего коммутатора и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего эле мента И, управляюш 1М входом второго коммутатора и с первым входом пятого элемента ИЛИ, второй вход и выход которого соединены соответственно с вы

с, ( )-м ВХОДОМ второго элемента ИШ, ходом пятого элемента И и с вторым выход поля модифицируемого адреса ре- управляющим входом третьего коммута- гистра микрокоманд соединен с первым входом третьего дешифратора, с первого по N-й выходы которого соединены

35

с первыми входами элементов И второй группы, выходы которых Соединены соответственно с третьего по (Ы+2)-й входами первого элемента ИЛИ; (N+3)-й вход которого соединен с

тора, второй выход признака принудительного перехода регистра микроко- ма1щ соединен с вторым входом пятого с третьим входом четвертого и.через пятьп элемент НЕ с третьим входом третьего элементов И, выход четвертого элемента ИЛИ через шестой элемент НЕ соединен с четвертыми входами пер(Н+1)-м выходом третьего дешифратора 40 вого и второго элементов И и с управвход кода команды устройства соединен с первым информационным входом третьего коммутатора, выход которого соединен с старшим разрядом группы разрядов адреса управляющей памяти информационного входа регистра адре- ма, первая и вторая группы входов логических условий устройства соединены соответственно с первого по N-й входами элементов И первой и второй групп, вход управления записью регистра микрокоманд соединены с вторым синхровходом устройства, о т - лич ающееся тем, что, с целью сокращения объема оборудования за счет уменьшения разрядности адрес- ной части микрокоманды, оно содержит четвертый коммутатор, с третьего по пятый элементы ИЛИ, с четвертого по шестой элементы НЕ и с третьего по пятый элементы И, причем (Ы+1)-й и (Ы+2)-й выходы второго дешифратора соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элемен- тов И, первый выход признака принудительного перехода регистра микрокоманд соединен с вторым входом третьего элемента И, с первым входом пятого элемента И и через четвертый

элемент НЕ с вторым входом четвертого элемента И, выход которого соединен

элемент НЕ с вторым входом четвертого элемента И, выход которого соединен

с первым управляющим входом третьего коммутатора и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, управляюш 1М входом второго коммутатора и с первым входом пятого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом пятого элемента И и с вторым управляющим входом третьего коммута-

тора, второй выход признака принудительного перехода регистра микроко- ма1щ соединен с вторым входом пятого с третьим входом четвертого и.через пятьп элемент НЕ с третьим входом третьего элементов И, выход четвертого элемента ИЛИ через шестой элемент НЕ соединен с четвертыми входами перляющим входом четвертого коммутатора выход второго поля логических условий регистра микрокоманд соединен с входом четвертого и с вторыми инфор45 мационными входами второго и третьего коммутаторов, выход четвертого коммутатора соединен с вторым входом третьего дешифратора, выход поля адреса управляющей памяти регистра

50 адреса соед1-шен с третьим информационным входом третьего коммутатора .

От ff/юка 8

1322280 От блока 6

Н блоку

Редактор Н.Тупица

Составитель А.Афанасьев

Техред Л.Олейник Корректор Н.Король

Заказ 2865/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

К блоку 5

Фиг.г

К блокам J, / J,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1986 |

|

SU1322279A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1283761A1 |

| Устройство микропрограммного управления | 1986 |

|

SU1381505A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Устройство для отладки программ | 1986 |

|

SU1410038A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Устройство для сбора диагностической информации о формировании адресов переходов микропрограмм | 1983 |

|

SU1290328A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

Изобретение относится к вычислительной технике и может быть применено в процессорах в качестве управляющего блока. Цель изобретения - сок-ращение используемого оборудования за счет уменьшения разрядности адресной части микрокоманд. Устройство содержит блок памяти микропрограмм, первый, второй, третий и четвертый кoм fyтaтopы,регистр микрокоманд, три дешифратора, три элемента НЕ, два элемента И, две группы элементов И, два элемента ИЛИ, регистр адреса и блок анализа перехода. Введение четвертого коммутатора и блока анализа перехода приводит к достижению цели. 2 ил.

| ПРИБОР ДЛЯ ИНТЕГРИРОВАНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ И ДЛЯ НАХОЖДЕНИЯ КОРНЕЙ ЧИСЛЕННЫХ УРАВНЕНИЙ | 1924 |

|

SU1045A1 |

| Техническое описание. | |||

Авторы

Даты

1987-07-07—Публикация

1986-02-12—Подача