(Л

ел

ND

Ю

ю

(pus.1

ИЖ 15, RS-триггер 16 прохождения прерывания, RS-триггер 17 прерывания , RS-триггер 1 8 прерывания, RS-триггер 19 конца прерывания, RS-триггер 20 начальной установки, RS-Tpnrrep 21 запрета, со второго по десятый элег- менты ИЛИ 22-30, с третьего по девятый элементы И 31-37, элемент ЙЕ 38, Возможность работы в реальном масшта- бе времени обеспечивается запоминанием сигналов запроса на внешнее прерывание проверкой сигнала запрета. прерывания, многократным запоминанием

текущего адреса основной микропрограммы, в котором-происходят прерывания, формированием аппаратными средствами микрокоманды безусловного перехода в начальный адрес микропрограммы внешнего прерывания или программными средствами - в адрес произ- вопьной микроподпрограммы прерывания и формированием после ее выполнения микрокоманды безусловного перехода в адрес, на котором прервалось выполнение основной микропрограммы. 1 3.п.ф-лы, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для микропрограммного управления | 1983 |

|

SU1188742A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1019450A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для отладки программ | 1990 |

|

SU1709320A1 |

| Микропрограммный процессор | 1980 |

|

SU947868A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1354192A1 |

| Устройство для отладки программ | 1979 |

|

SU849218A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - расширение области применения устройства путем обеспечения возможности работы в реальном масштабе времени при многоуровневых прерываниях. Устройство содержит коммутатор 1 адреса, счетчик 2 адреса, блок 3 памяти микропрограмм, блок 4 дешифраторов микрокоманд, регистр 6 адреса, коммутатор 7 условий, первый кольцевой сдвиговый регистр 8, второй кольцевой сдвиговый регистр 9, первый 10 и второй 11 элементы И, стековую память 12, группу 13 RS - триггеров аппаратных прерываний, блок 14 отладки программы, первый элемент ИЛИ 15, RS - триггер 16 прохождения пребывания, RS - триггер 17 прерывания, D - триггер 18 прерывания, RS - триггер 19 конца прерывания, RS - триггер 20 начальной установки, D - триггер 21 запрета, со второго по десятый элементы ИЛИ 22-30, с третьего по девятый элементы И 31-37 элемент НЕ 38. Возможность работы в реальном масштабе времени обеспечивается запоминанием сигналов запроса на внешнее прерывание, проверкой сигнала запрета прерывания, многократным запоминанием текущего адреса основной микропрограммы, в котором происходят прерывания, формированием аппаратными средствами микрокоманды безусловного перехода в начальный адрес микропрограммы внешнего прерывания или программными средствами - в адрес произвольной микроподпрограммы прерывания и формированием после ее выполнения микрокоманды безусловного перехода в адрес, на котором прервалось выполнение основной микропрограммы. 1 з.п. ф-лы, 5 ил.

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных процессорах.

Цель изобретения - расширение области применения устройства путем обеспечения возможности работы в реальном масштабе времени при многоуровневых прерываниях.

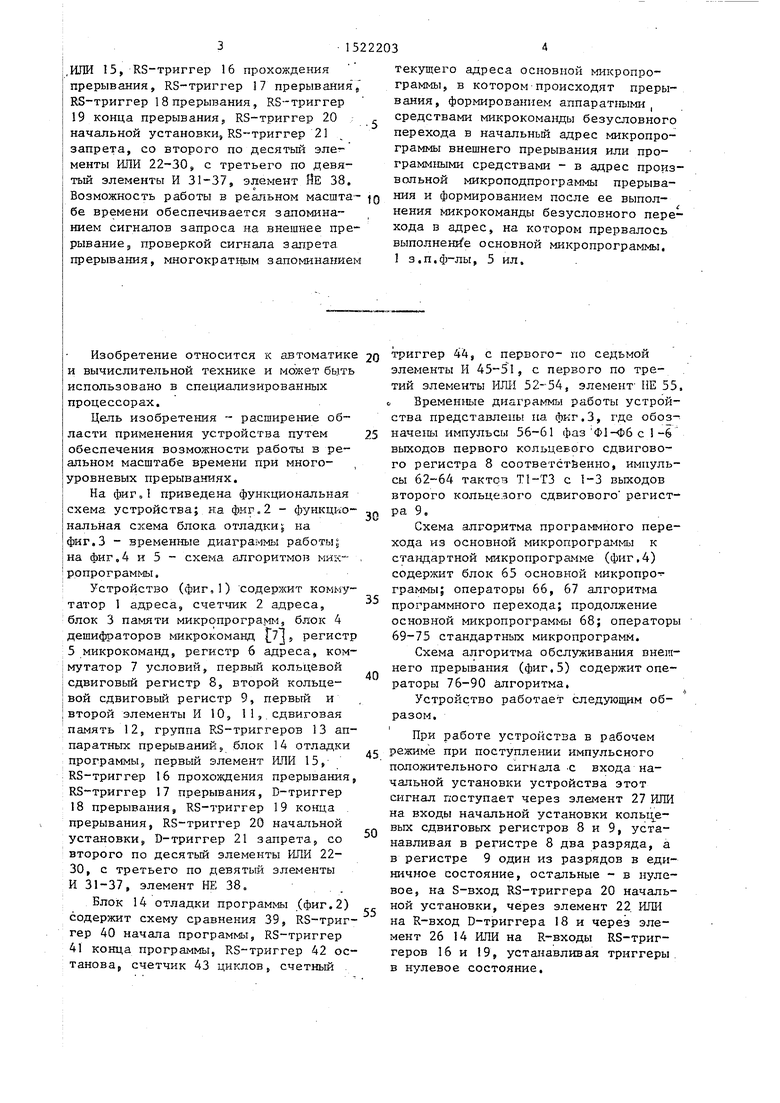

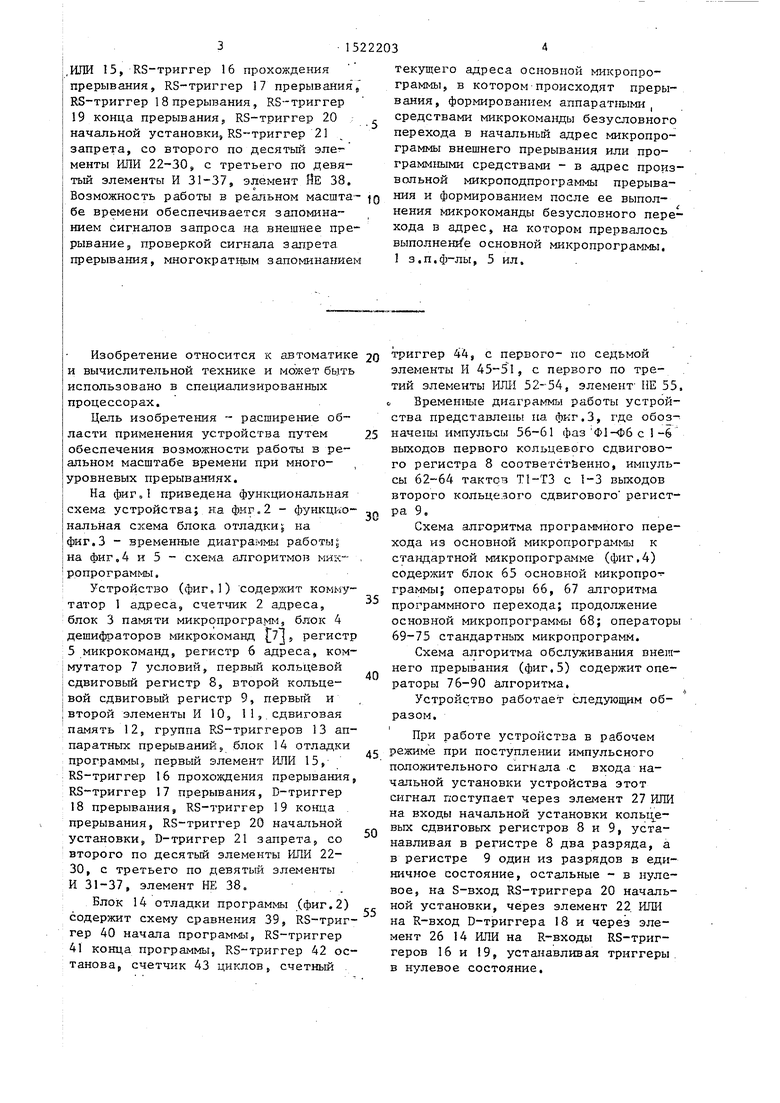

На фиг,1 приведена функциональная схема устройства; на фиг.2 - функциональная схема блока отладки; на фиг.З - временные диаграммы работы,$ на фиг,4 и 5 - схема алгоритмов мяк- ропрограммы.

Устройство (фиг,1) содержит коммутатор 1 адреса, счетчик 2 адреса, блок 3 памяти микропрограмм, блок 4 дешифраторов микрокоманд , регистр 5 микрокоманд, регистр 6 адреса, коммутатор 7 условий, первый кольцевой сдвиговый регистр 8, второй кольцевой сдвиговый регистр 9, первый и второй элементы И 10, И,.сдвиговая память 12, группа RS-триггеров 13 аппаратных прерываний, блок 14 отладки программы, первый элемент ИЛИ 15, RS-триггер 16 прохождения прерывания RS-триггер 17 прерывания, D-триггер 18 прерывания, RS-триггер 19 конца прерывания, RS-триггер 20 начальной установки, D-триггЕф 21 запрета, со второго по десятый элементы ИЛИ 22- 30, с третьего по девятый элементы И 31-37, элемент НЕ 38.

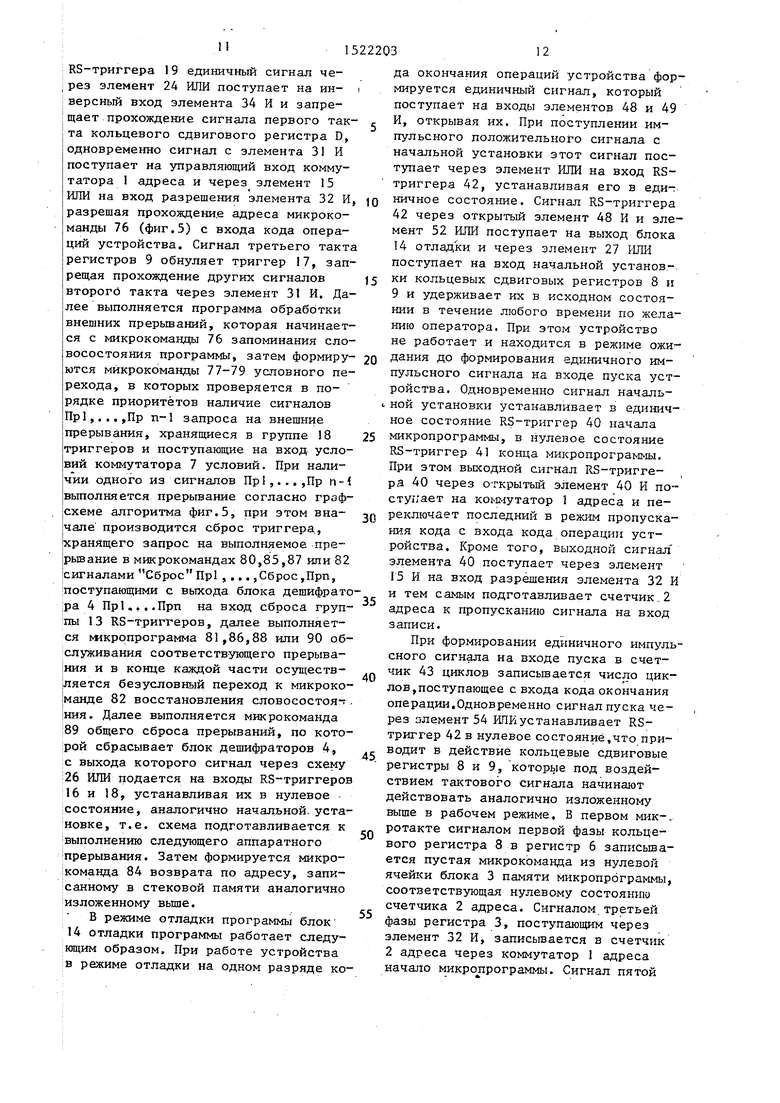

Блок 14 отладки программы (фиг.2) содержит схему сравнения 39, RS-триггер 40 начала программы, RS-триггер 41 конца программы, RS-триггер 42 ос- танова, счетчик 43 циклов, счетный .

триггер 44, с первого- по седьмой

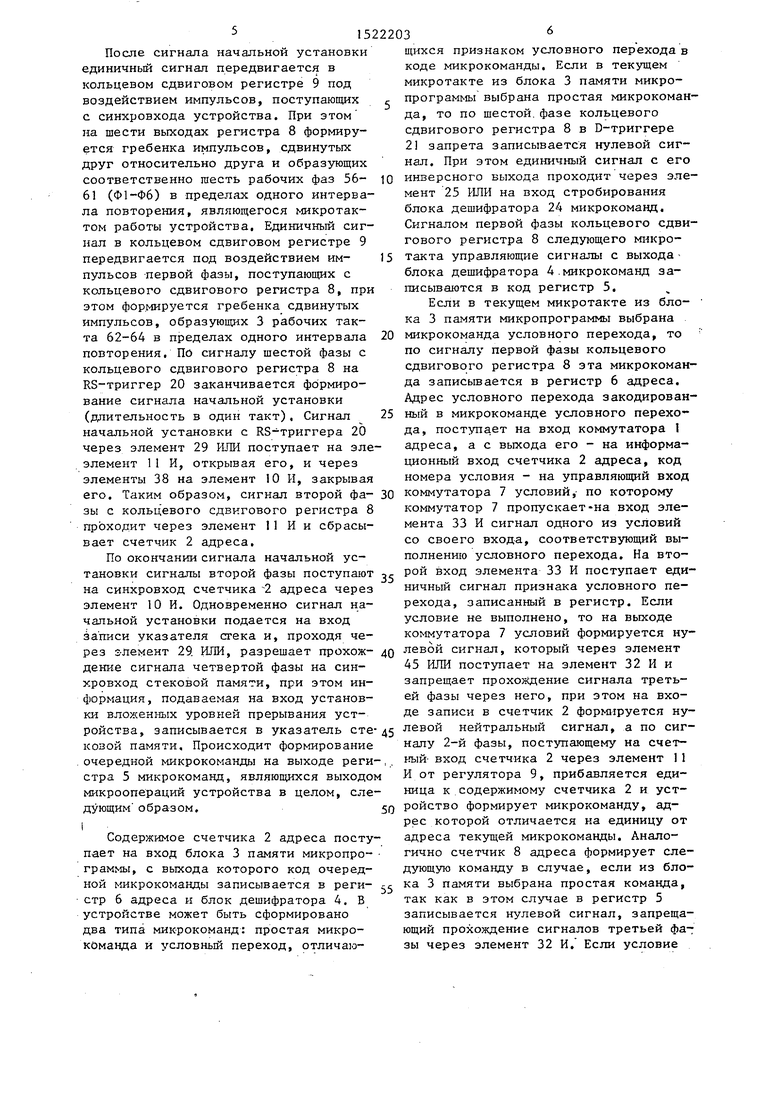

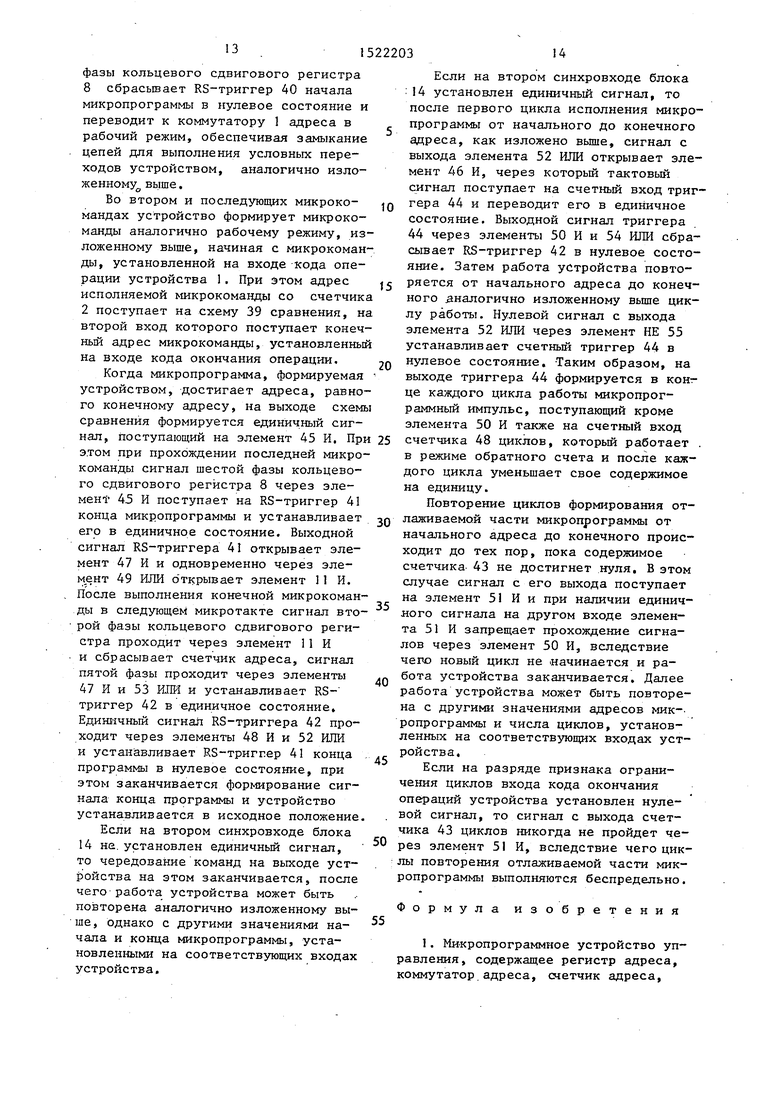

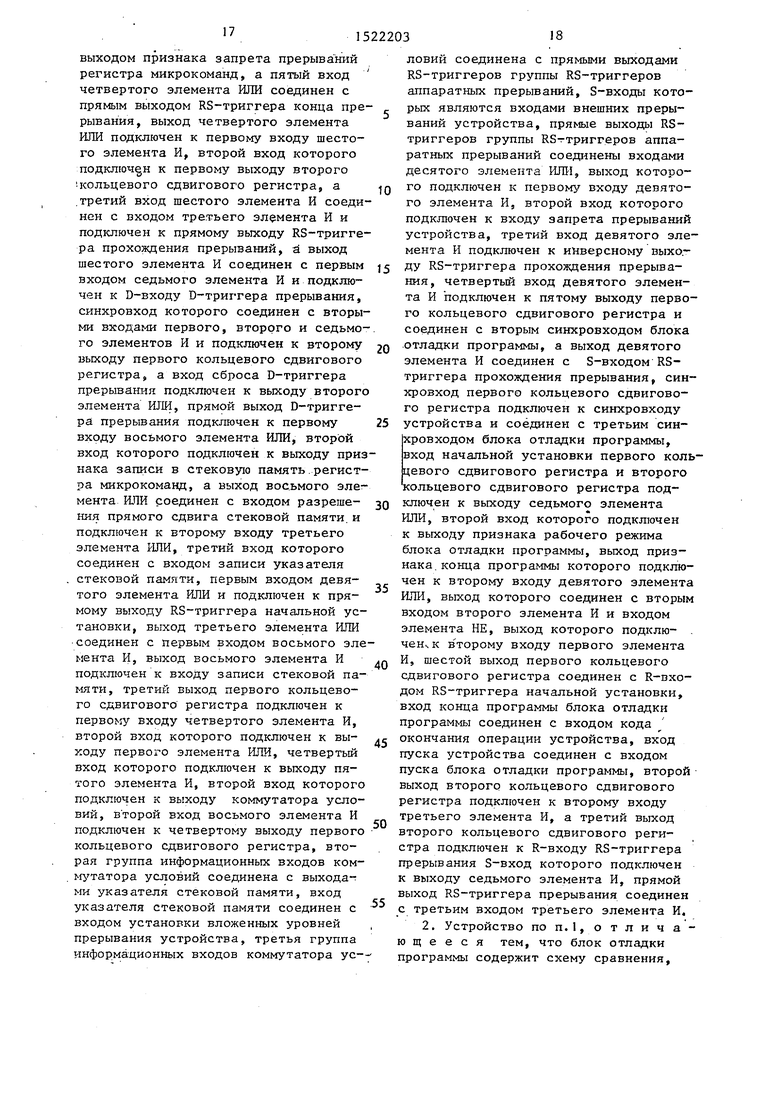

элементы И 45-51, с первого по тре- , тий элементы ИШ1 52-54, элемент НЕ 55, о Времен1ые диаграммг работы устройства представлепь па фкг.З, где обозначены импульсы 56-61 фаз Ф1-Ф6 с 1-6 выходов первого кольцевого сдвигового регистра 8 соответственно, импульсы 62-64 тактов Т1-ТЗ с 1-3 выходов второго кольцезого сдвигового регистРа 9..

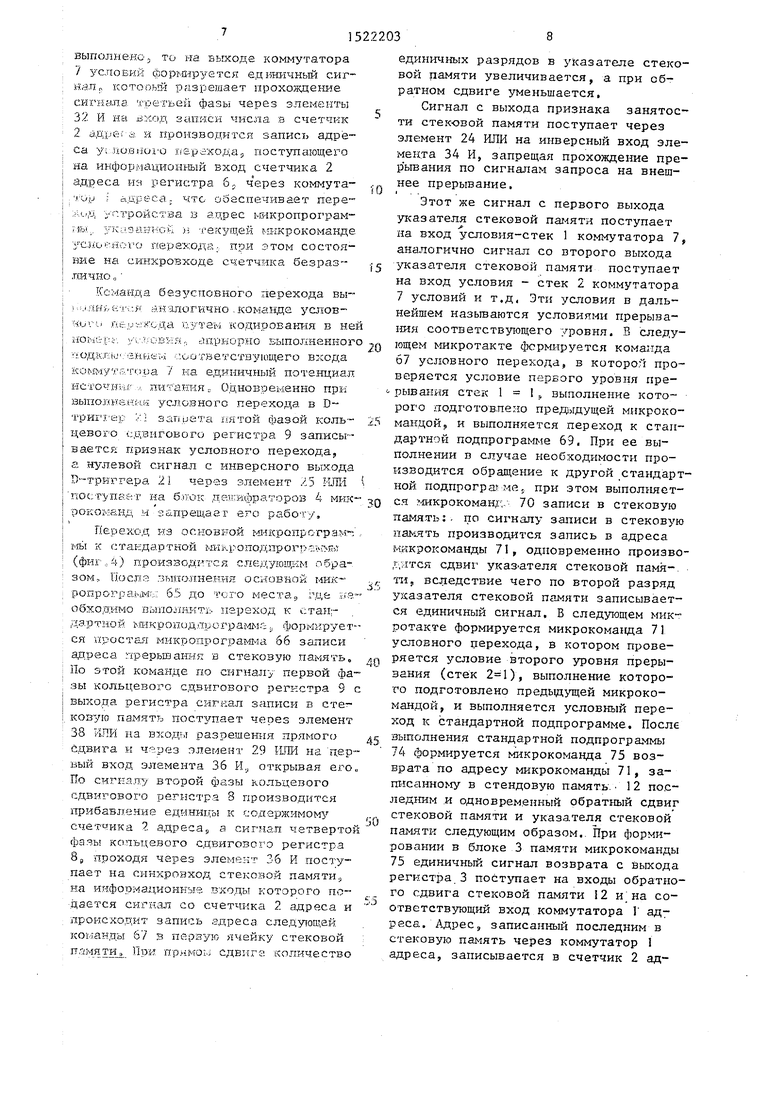

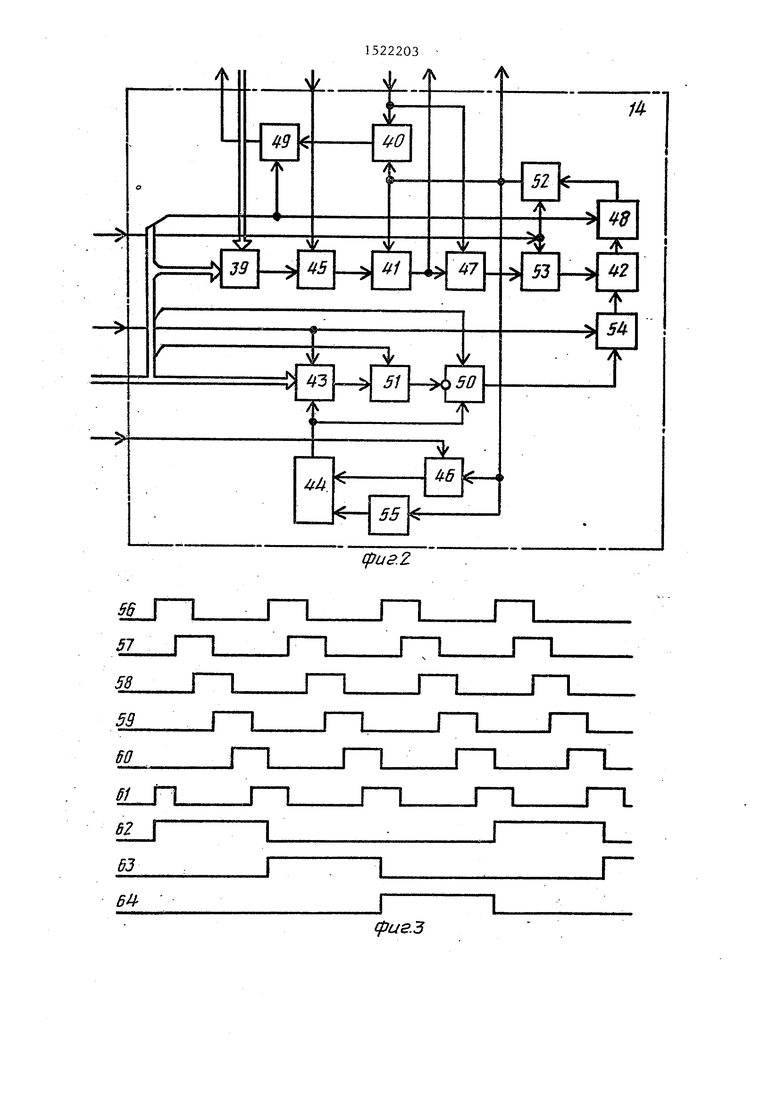

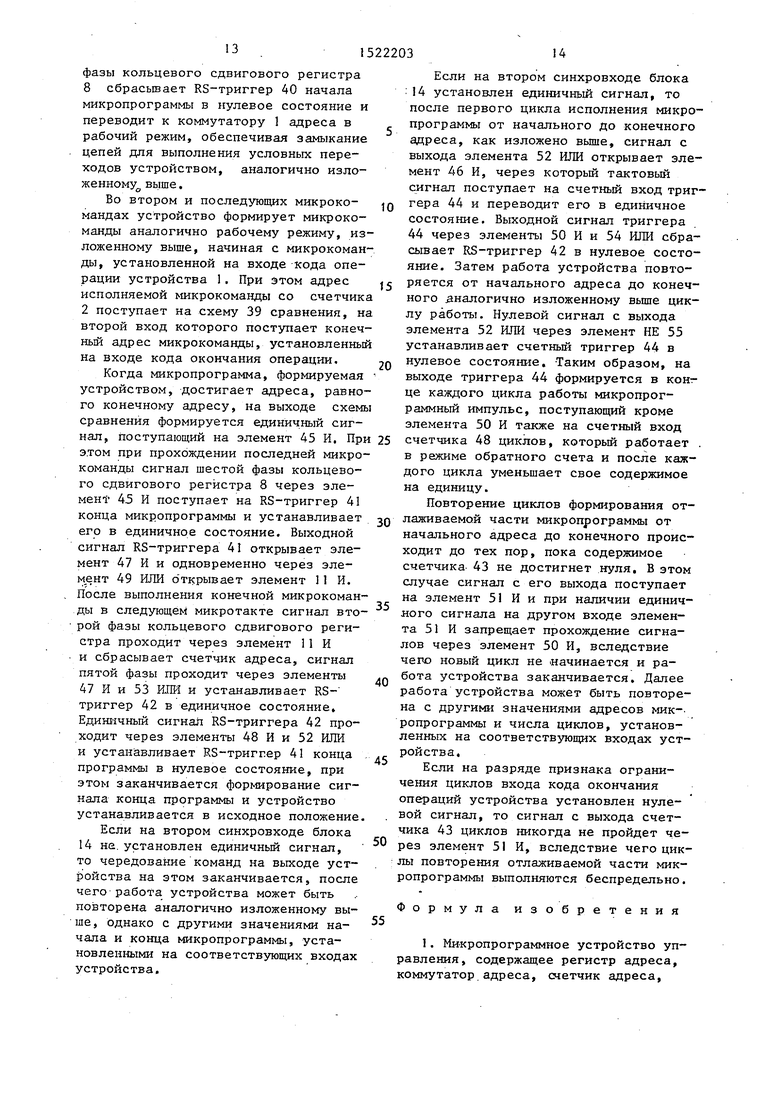

Схема алгоритма программного перехода из основной микропрогра1-1мы к стандартной микропрограмме (фиг,4) содержит блок 65 основной микропрограммы; операторы 66, 67 алгоритма программного перехода; продолжение основной микропрограммы 68; операторы 69-75 стандартных микропрограмм.

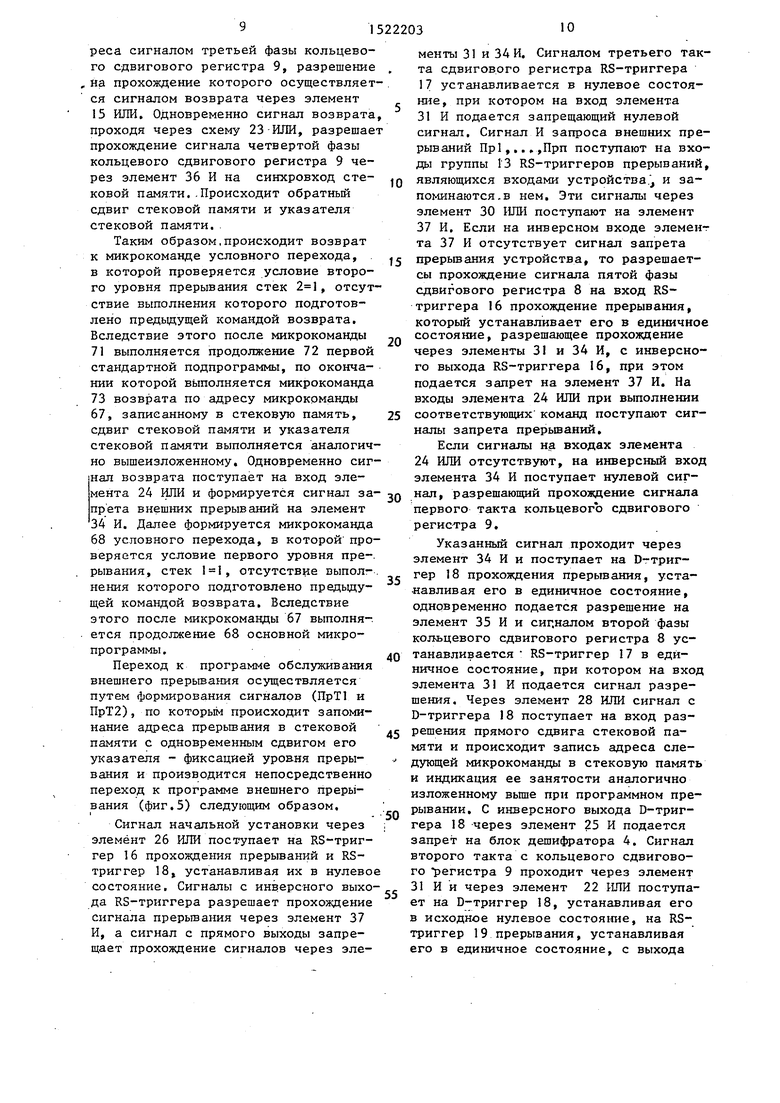

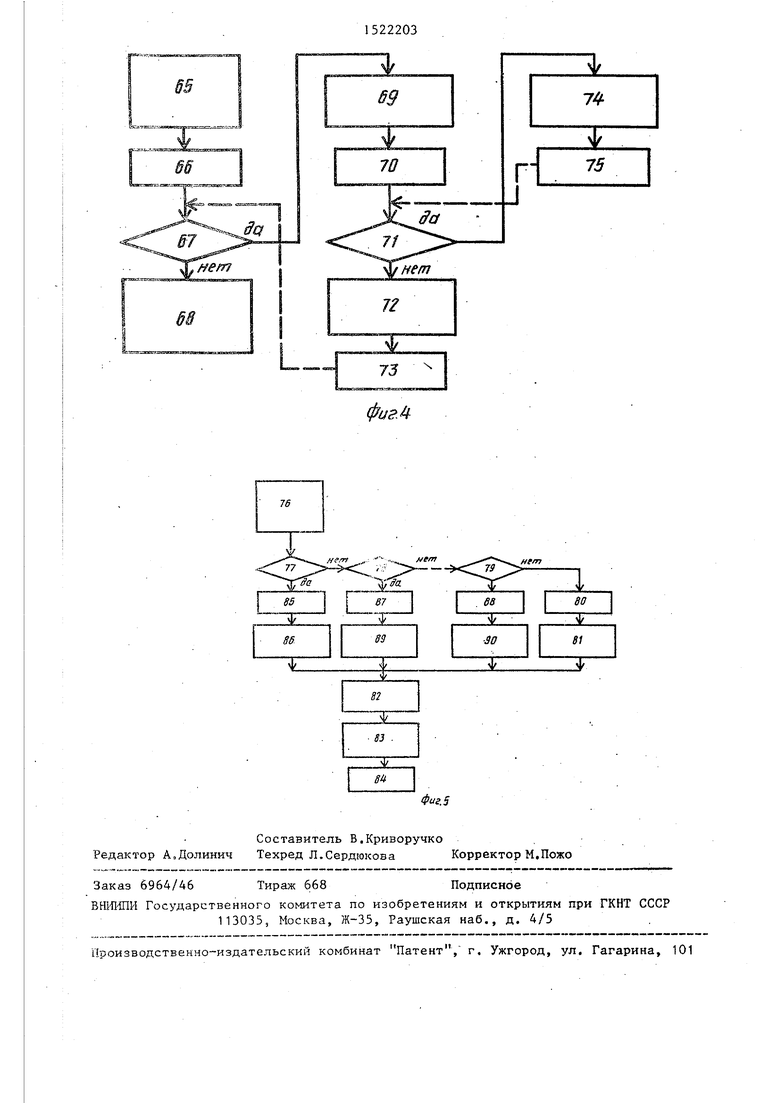

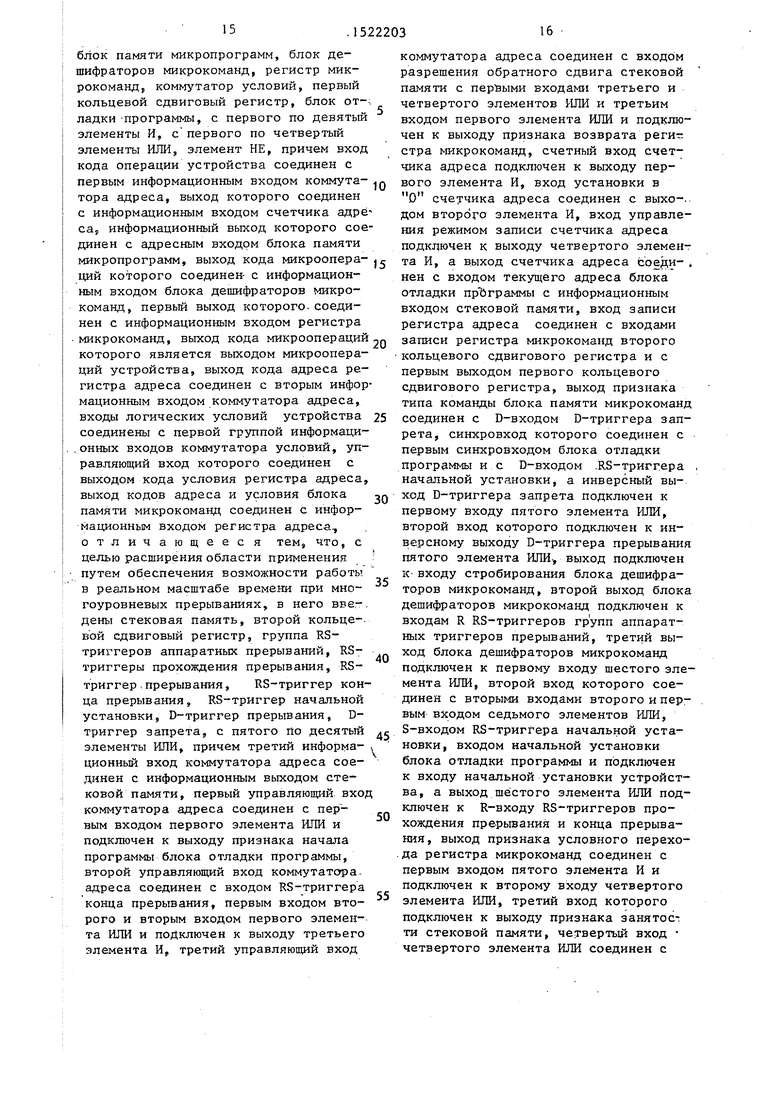

Схема алгоритма обслуживания внешнего прерывания (фиг,5) содержит операторы 76-90 алгоритма.

Устройство работает следующим образом.

При работе устройства в рабочем режиме при поступлении импульсного положительного сигнала С входа начальной установки устройства этот сигнал поступает через элемент 27 ИЛИ на входы начальной установки вьгх сдвиговых регистров 8 и 9, устанавливая в регистре 8 два разряда, а в регистре 9 один из разрядов в единичное состояние, остальные - в нулевое, на S-вход RS-триггера 20 началь- ной установки, через элемент 22. ИШi на R-вход D-триггера 18 и через элемент 26 14 ИЛИ на R-входы RS-триггеров 16 и 19, устанавливая триггеры в нулевое состояние.

После сигнала начальной установки единичный сигнал передвигается в кольцевом сдвиговом регистре 9 под воздействием импульсов, поступающих с с синхровхода устройства. При этом на шести выходах регистра 8 формируется гребенка импульсов, сдвинутых друг относительно друга и образующих соответственно шесть рабочих фаз 56- ю 61 (Ф1-Ф6) в пределах одного интервала повторения, являющегося микротактом работы устройства. Единичный сигнал в кольцевом сдвиговом регистре 9 передвигается под воздействием им- 15 пульсов первой фазы, поступающих с кольцевого сдвигового регистра 8, при этом фор.мируется гребенка сдвинутых импульсов, образующих 3 рабочих такта 62-64 в пределах одного интервала 20 повторения. По сигналу шестой фазы с кольцевого сдвигового регистра 8 на RS-триггер 20 заканчивается формирование сигнала начальной установки (длительность в один такт). Сигнал 25 начальной установки с RS-триггера 20 через элемент 29 1-ШИ поступает на эле- элемент 11 И, открывая его, и через элементы 38 на элемент 10 И, закрывая

щихся признаком условного перехода коде микрокоманды. Если в текущем микротакте из блока 3 памяти микропрограммы выбрана простая микрокома да, то по шестой, фазе кольцевого сдвигового регистра 8 в D-триггере 2 запрета записывается нулевой сиг нал. При этом единичный сигнал с ег инверсного выхода проходит через эл мент 25 1-ШИ на вход стробирования блока дешифратора 24 микрокоманд, Сигналом первой фазы кольцевого сдв гового регистра 8 следующего микротакта управляющие сигналы с выхода блока дешифратора 4.микрокоманд записываются Б код регистр 5,

Если в текущем микротакте из бло ка 3 памяти микропрограммы выбрана микрокоманда условного перехода, то по сигналу первой фазы кольцевого сдвигового регистра 8 эта микрокома да записывается в регистр 6 адреса. Адрес условного перехода закодирова ный в микрокоманде условного перехо да, поступает на вход коммутатора 1 адреса, а с выхода его - на информа ционный вход счетчика 2 адреса, код номера условия - на управляющий вхо

его. Таким образом, сигнал второй фа- 30 коммутатора 7 условий,- по которому

зы с кольцевого сдвигового регистра 8 проходит через элемент 11 И и сбрасывает счетчик 2 адреса.

По окончании сигнала начальной ускоммутатор 7 пропускает-на вход элемента 33 И сигнал одного из условий со своего входа, соответствующий выполнению условного перехода. На вто-

чальной установки подается на вход записи указателя стека и, проходя четановки сигналы второй фазы поступают ,r Рой вход элемента 33 И поступает едина синхровход счетчика 2 адреса через ничный сигнал признака условного пе- элемент 10 И, Одновременно сигнал на- рехода, записанный в регистр. Если

условие не выполнено, то на выходе коммутатора 7 условий формируется ну- рез з-лемент 29. ИЛИ, разрешает прохож- дО левой сигнал, который через элемент дение сигнала четвертой фазы на син- 45 1-ШИ поступает на элемент 32 И и хровход стековой памяти, при этом информация, подаваемая на вход установки вложенных уровней прерывания устройства, записывается в указатель сте-45 левой нейтральный сигнал, а по сиг- козой памяти. Происходит формирование налу 2-й фазы, поступающему на счет- очередной микрокоманды на выходе реги-,. ный- вход счетчика 2 через элемент 11 стра 5 микрокоманд, являющихся выходом И от регулятора 9, прибавляется еди- микроопераций устройства в целом, еле- ница к содержимому счетчика 2 и уст- дующнм образом,50 ройство формирует микрокоманду, адIрее которой отличается на единицу от

Содержимое счетчика 2 адреса поступает на вход блока 3 памяти микропро-

запрещает прохождение сигнала третьей фазы через него, при этом на входе записи в счетчик 2 формируется нуадреса текущей микрокоманды. Аналогично счетчик 8 адреса формирует следующую команду в случае, если из блока 3 памяти выбрана простая команда, так как в этом случае в регистр 5 записывается нулевой сигнал, запрещающий прохождение сигналов третьей фа-; зы через элемент 32 И, Если условие

граммы, с выхода которого код очередной микрокоманды записывается в реги- стр 6 адреса и блок дешифратора 4. В устройстве может быть сформировано два типа микрокоманд: простая микрокоманда и условный переход, отличающихся признаком условного перехода в коде микрокоманды. Если в текущем микротакте из блока 3 памяти микропрограммы выбрана простая микрокоманда, то по шестой, фазе кольцевого сдвигового регистра 8 в D-триггере 2 запрета записывается нулевой сигнал. При этом единичный сигнал с его инверсного выхода проходит через элемент 25 1-ШИ на вход стробирования блока дешифратора 24 микрокоманд, Сигналом первой фазы кольцевого сдвигового регистра 8 следующего микротакта управляющие сигналы с выхода блока дешифратора 4.микрокоманд записываются Б код регистр 5,

Если в текущем микротакте из бло- ка 3 памяти микропрограммы выбрана микрокоманда условного перехода, то по сигналу первой фазы кольцевого сдвигового регистра 8 эта микрокоманда записывается в регистр 6 адреса. Адрес условного перехода закодированный в микрокоманде условного перехода, поступает на вход коммутатора 1 адреса, а с выхода его - на информационный вход счетчика 2 адреса, код номера условия - на управляющий вход

коммутатор 7 пропускает-на вход элемента 33 И сигнал одного из условий со своего входа, соответствующий выполнению условного перехода. На вто-

условие не выполнено, то на выходе коммутатора 7 условий формируется ну- левой сигнал, который через элемент 45 1-ШИ поступает на элемент 32 И и левой нейтральный сигнал, а по сиг- налу 2-й фазы, поступающему на счет- ный- вход счетчика 2 через элемент 11 И от регулятора 9, прибавляется еди- ница к содержимому счетчика 2 и уст- ройство формирует микрокоманду, адзапрещает прохождение сигнала третьей фазы через него, при этом на входе записи в счетчик 2 формируется нуадреса текущей микрокоманды. Аналогично счетчик 8 адреса формирует следующую команду в случае, если из блока 3 памяти выбрана простая команда, так как в этом случае в регистр 5 записывается нулевой сигнал, запрещающий прохождение сигналов третьей фа-; зы через элемент 32 И, Если условие

выполнено 3 то на выходе коммутатора 7 услоЕий форг-шруетск единичный сигнал,, котооьй разрешает прохояодение сигнала третьей фазы через элементы 32 И на вход записн числа Б счетчик 2 aflp fjf а н производится запись адреса у; noBHoi O пер ахода, поступающего : на информационный вход счетчика 2 j адреса ия регистра б,, ч ерез коммута- том ; адреса, что обеспечивает пере- I .д уптройства з адрес ьмкропрограмI ifbL. уК;л34ШНОй ; ТвКуЩвЙ МККрОКОМаНДв

I ycjiopi-jov o ггерехода; при этом состояI вне на синхровходе счетчихса безраз-

: лично о

Команда безз сповного перекода вы- .манх.е-.1ч;я ан алогично комавде услов- I МОП. п. путем кодировакия в ней I номйр . y-i.-j;oBHH, априорно выполненного юдкл10 .еныи;-:; соответствующего входа йоммут&тора 7 на единичный потенциал источннг л нитакия Одновременно при выполне - .-.- условного перехода в D трип ер /: запрета пятой фазой коль- I цевого сдвигового регистра 9 записьг- вается признак условного перехода,

а нулевой сигнал с инверсного выхода I 1 -триггера 21 через элемент Z3 FJIIi j пос;тупа& на блок деп;ифраторов 4 мик-

I рокоманд и запреш,аег его работу,

1

I Переход из осиовной м- кропрогра.м-.

I мы к стандартной микроподпрогр-г сж (фиг а 4) произзодг тся следующим образом. Посла выполнения основной мик- ропрограьахгь; 65 до того места9 HS обходимо выполнить переход к стан;- дартной -шкропод.арох рагФ.-;,, формируется простая MHKponporpaf avia 56 залиси адреса прерьшаник в стековую память, По з гой команде по снгна.1г первой фа зы кольцевого сдвигового регистра 9 I выхода регистра сигнал записи в стег- i козую память поступает через элемент 38 ИЛИ на входгл разрешешш прямого Сдвига и через элемент 29 ИПИ на цер вый вход элемента 36 И,, открывая его По сигналу второй фазы кольдевого сдвигового peri-iCTpa 8 производится прибавление единиць к содержимом счетчика 2 адреса а скгпап четверто фаяь кольдевого сдвигового регистра 8д проходя через элемент 36 И поступает на синхровход стековой памяти на информационные входы которого подается сигнал со счетчика 2 адреса и происходит запись адреса следующей команды 57 з первую х чейку стековой памяти,, При np iMo;:.j сдвига количество

«

( 5

Q

,,.

единичных разрядов в указателе стековой памяти увеличивается, а при обратном сдвиге уменьшается.

Сигнал с выхода признака занятости стековой памяти поступает через элемент 24 Ш1И. на инверсный вход элемента 34 И, запрещая прохожде11ие пре- р ьгеания по сигналам запроса на внешнее прерывание.

Этот же сигнал с первого выхода указателя стековой па1-1яти поступает на вход условия-стек 1 коммутатора 7, аналогично сигнал со второго вькода указателя стековой памяти поступает на вход условия - стек 2 коммутатора 7 условий и т.д. Эти условия в дальнейшем называются условиями прерывания соответствующего уровня. В следующем микротакте формируется команда 67 условного перехода, в которой проверяется условие первого уровня пре- рываьшя стек 1 1,, выполнение которого подготовлено пред адущей микрокомандой,, и выполшгется переход к стандартной подпрограмме 69, При ее выполнении в случае необходимости производится обращение к другой стандартной подпрогра мв;, при этом выполняется г-шкрокомащ ;- 70 записи в стековую память:- по сигналу записи в стековую память производится запись в адреса №5крокоманды 71, одновременно произво- ,г,ится сдвиг указ втеля стековой памя-. т, вследствие чего по второй разряд указателя стековой памяти записывается единичный сигнал, В следующем мик ротакте формируется микрокома1ща 71 условного перехода, в котором проверяется условие второго уровня прерывания (стёк ), выполнение которого подготовлено предыдущей микрокомандой, и выполняется условный переход к стандартной подпрограмме. После выполнения стандартной подпрограммы

74формируется микрокоманда 75 возврата по адресу микрокоманды 71, записанному в стендовую память. 12 последним .и одновременный обратный сдвиг стековой памяти и указателя стековой памяти следующим образом,. При формировании в блоке 3 памяти микрокоманды

75единичный сигнал возврата с выхода регистра 3 поступает на входы обратрю- го сдвига стековой памяти 12 и;на соответствующий вход коммутатора Г адреса. Адрес, записанный последним в стековую память через коммутатор I адреса, записывается в счетчик 2 ад

У

реса сигналом третьей фазы кольцевого сдвигового регистра 9, разрешени на прохождение которого осуществляеся сигналом возврата через элемент 15 ИЛИ, Одновременно сигнал возврат проходя через схему 23 ИЛИ, разреша прохождение сигнала четвертой фазы кольцевого сдвигового регистра 9 через элемент 36 И на синхровход стековой памяти..Происходит обратный сдвиг стековой памяти и указателя стековой памяти..

Таким образом,происходит возврат к микрокоманде условного перехода, в которой проверяется условие второго уровня прерывания стек , отсуствие выполнения которого подготовлено предыдущей командой возврата. Вследствие этого после микрокоманды 71 выполняется продолжение 72 перво стандартной подпрограммы, по окончании которой выполняется микрокоманд 73 возврата по адресу микрокоманды 67, записанному в стековую память, сдвиг стековой памяти и указателя стековой памяти выполняется аналогино вышеизложенному. Одновременно синал возврата поступает на вход элемента 24 РШИ и формируется сигнал зпрета внешних прерываний на элемент 34 И. Далее формируется микрокоманд 68 условного перехода, в которой прверяется условие первого уровня пре-

рывания, стек , отсутствие выполнения которого подготовлено предыдущей командой возврата. Вследствие этого после микрокоманды 67 выполня-. ется продолжение 68 основной микропрограммы.

Переход к программе обслуживания внешнего прерьгоания осуществляется путем формирования сигналов (ПрТ1 и ПрТ2), по которым происходит запоминание адреса прерьшания в стековой памяти с одновременным сдвигом его указателя - фиксацией уровня прерывания и производится непосредственно переход к программе внешнего прерывания (фиг.5) следующим образом.

Сигнал начальной установки через элемент 26 ИЛИ поступает на RS-триг- гер 16 прохожде шя прерываний и RS- триггер 18, устанавливая их в нулево состояние. Сигналы с инверсного выхода RS-триггера разрешает прохождение сигнала прерьшания через элемент 37 И, а сигнал с прямого выходы запрещает прохождение сигналов через эле10

0

5

0

5

0

5

0

5

0

5

менты 31 и 34 И. Сигналом третьего такта сдвигового регистра RS-триггера 17 устанавливается в нулевое состояние, при котором на вход элемента 31 И подается запрещающий нулевой сигнал. Сигнал И запроса внешних прерываний Пр1,,.,,Прп поступают на входы группы 13 RS-триггеров прерываний, являющихся входами устройства., и запоминаются, в нем. Эти сигналы через элемент 30 UTtti поступают на элемент 37 И. Если на инверсном входе элемента 37 И отсутствует сигнал запрета прерьшания устройства, то разрешает- сы прохождение сигнала пятой фазы сдвигового регистра В на вход RS- триггера 16 прохождение прерывания,

который устанавливает его в единичное состояние, разрешающее прохояадение

через элементы 31 и 34 И, с инверсного выхода RS-триггера 16, при этом подается запрет на элемент 37 И, На входы элемента 24 ИЛИ при выполнении соответствующих команд поступают сигналы запрета прерьшаний.

Если сигналы на входах элемента 24 ИЛИ отсутствуют, на инверсный вход элемента 34 И поступает нулевой сигнал, разрешающий прохождение сигнала первого такта кольцевого сдвигового регистра 9.

Указанный сигнал проходит через элемент 34 И и поступает на D-триггер 18 прохождения прерывания, устанавливая его в единичное состояние, одновременно подается разрешение на элемент 35 И и сигналом второй фазы кольцевого сдвигового регистра 8 устанавливается RS-триггер 17 в единичное состояние, при котором иа вход элемента 31 И подается сигнал разрешения. Через элемент 28 ИЛИ сигнал с Dтриггера 18 поступает на вход разрешения прямого сдвига стековой памяти и происходит запись адреса следующей микрокоманды в стековую память и индикация ее занятости аналогично изложенному вьщ1е при программном прерывании, С инверсного выхода D-триггера 18 через элемент 25 И подается запрет на блок дешифратора 4, Сигнал второго такта с кольцевого сдвигового регистра 9 проходит через элемент 31 И и через элемент 22 ИЛИ поступает на D-триггер 18, устанавливая его в исходное нулевое состояние, на RS- триггер 19 прерывания, устанавливая его в единичное состояние, с выхода

RS-триггера 19 единичный сигнал че- рез элемент 24 ИЛИ поступает на ин- версный вход элемента 34 И и запре- iщает прохождение сигнала первого так- 1 та кольцевого сдвигового регистра D, одновременно сигнал с элемента 31 И поступает на управляющий вход коммутатора 1 адреса и через элемент 15 ИЛИ на вход разрешения элемента 32 И, разрешая прохождение адреса микрокоманды 76 (фиг.5) с входа кода операций устройства. Сигнал третьего такта регистров 9 обнуляет триггер 17, зап рещая прохождение других сигналов второгсэ такта через элемент 31 И. Далее выполняется программа обработки внешних прерьшаний, которая начинается с микрокоманды 76 запоминания сло- восостояния программы, затем формируются микрокоманды 77-79 условного перехода, в которых проверяется в порядке приоритетов наличие сигналов Пр1,..,,Пр п-1 запроса на внешние 1прерывания, хранящиеся в группе 18 триггеров и поступающие на вход условий коммутатора 7 условий. При нали- |чии одного из сигналов Пр1,... ,Пр ti-1 выполняется прерывание согласно граф- схеме алгоритма фиг,5, при этом вначале производится сброс триггера., |хранящего запрос на выполняемое пре- |рьшанйе в микрокомандах 80,85,87 или 82 {сигналами Сброс Пр1 , ...,Сброс,Прп, {поступающими с выхода блока дешифрато ;ра 4 Пр1.,.,Прп на вход сброса груп- пы 13 RS-триггеров, далее выполняется микропрограмма 81,86,88 или 90 обслуживания соответствующего прерыва- ния и в конце каждой части осуществ- |Ляется безусловный переход к микроко- 1манде 82 восстановления словосостоя|ния. Далее выполняется микрокоманда 89 общего сброса прерываний, по кото- ;рой сбрасывает блок дешифраторов 4, :с выхода которого сигнал через схему :26 ИЛИ подается на входы RS-триггеров 16 и 18, устанавливая их в нулевое состояние, аналогично начальной, установке, т.е. схема подготавливается к выполнению следующего аппаратного Прерывания. Затем формируется микро- :команда 84 возврата по адресу, запи- санному в стековой памяти аналогично изложенному вьш1е.

В режиме отладки программы блок 14 отладки программы работает следующим образом. При работе устройства в режиме отладки на одном разряде ко

5

0

5

0

5

0

0

5

да окончания операций устройства формируется единичный сигнал, который поступает на входы элементов 48 и 49 И, открывая их. При поступлении импульсного положительного сигнала с начальной установки этот сигнал поступает через элемент ИЛИ на вход RS- триггера 42, устанавливая его в единичное состояние. Сигнал RS-триггера 42 через открытый элемент 48 И и элемент 52 ИЛИ поступает на выход блока

14отладки и через элемент 27 I-UIIi поступает на вход начальной установки кольцевых сдвиговых регистров 8 и 9 и удерживает их в исходном состоянии в течение любого времени по желанию оператора. Бри этом устройство

не работает и находится в режиме ожидания до формирования единичного импульсного сигнала на входе пуска устройства. Одновременно сигнал начальной установки устанавливает в единичное состояние RS-триггер 40 начала микропрограммы, в нулевое состояние RS-триггер 41 конца микропрограммы. При этом выходной сигнал RS-триггера 40 через открытый элемент 40 И по- стуь ает на коммутатор 1 адреса и переключает последний в режим пропуска- ршя кода с входа кода операции устройства. Кроме того, выходной сигнал элемента 40 поступает через элемент

15И на вход разрешения элемента 32 И и тем самым подготавливает счетчик.2 адреса к пропусканию сигнала на вход записи.

При формировании единичного импульсного сигнала на входе пуска в счетчик 43 циклов записывается число циклов, поступающее с входа кода окончания операции,Одновременно сигнал пуска через элемент 54 ИЛИ устанавливает RS- триггер 42 в нулевое состояние,что приводит в действие кольцевые сдвиговые регистры 8 и 9, которые под воздействием тактового сигнала начинают действовать аналогично изложенному выше в рабочем режиме, В первом мик-. ротакте сигналом первой фазы кольцевого регистра 8 в регистр 6 записьша- ется пустая микрокоманда из нулевой ячейки блока 3 памяти микропрограммы, соответствующая нулевому состоянию счетчика 2 адреса. Сигналом третьей фазы регистра 3, поступающим через элемент 32 И, записьгоается в счетчик 2 адреса через коммутатор I адреса начало микропрограммы. Сигнал пятой

фазы кольцевого сдвигового регистра 8 сбрасьшает RS-триггер 40 начала микропрограммы в кулевое состояние и переводит к коммутатору 1 адреса в рабочий режим, обеспечивая замыкание цепей для выполнения условных переходов устройством, аналогично изло- женномУд выше,

Во втором и последующих микрокомандах устройство формирует микрокоманды аналогично рабочему режиму, изложенному выше, начиная с микрокоманды, установленной на входе кода операции устройства 1. При этом адрес исполняемой шкpoкoмaнды со счетчика 2 поступает на схему 39 сравнения, на второй вход которого поступает конечный адрес микрокоманды, установленный на входе кода окончания операции.

Когда микропрограмма, формируемая устройством, достигает адреса, равного конечному адресу, на выходе схемы сравнения формируется единичный сигнал, поступающий на элемент 45 И. При Э.ТОМ при прохождении последней микрокоманды сигнал шестой фазы кольцевого сдвигового регистра 8 через элемент 45 И поступает на RS-триггер 41 конца микропрограммы и устанавливает его в единичное состояние. Выходной сигнал RS-триггера 4I открывает элемент 47 И и одновременно через эле- 49 ИЛИ о ткрывает элемент 11 И. После выполнения конечной микрокоманды в следующем микротакте сигнал второй фазы кольцевого сдвигового регистра проходит через элемент 11 И и сбрасывает счетчик адреса, сигнал пятой фазы проходит через элементы 47 И и 53 ИЛИ и устанавливает RS- триггер 42 в единичное состояние, Едишшный сигнал RS-триггера 42 проходит через элементы 48 И и 52 ИЛИ и устанавливает RS-тригг.ер 41 конца программы в нулевое состояние, при этом заканчивается формирование сигнала конца программы и устройство устанавливается в исходное положение.

Если на втором синхровходе блока 14 на. установлен единичный сигнал, то чередование команд на выходе устройства на этом заканчивается, после чего работа устройства может быть повторена аналогично изложенному вы- ше, однако с другими значениями начала и конца микропрограммы, установленными на соответствующих входах устройства.

0

5

0

5

0

5

0

5

0

5

Если на втором синхровходе блока : 14 установлен единичнь1Й сигнал, то после первого цикла исполнения микропрограммы от начального до конечного адреса, как изложено вьше, сигнал с выхода элемента 52 ИЛИ открывает элемент 46 И, через который тактовый сигнал поступает на счетный вход триггера 44 и переводит его в единичное состояние. Выходной сигнал триггера 44 через элементы 50 И и 54 ИЛИ сбрасывает RS-триггер 42 в нулевое состояние. Затем работа устройства повторяется от начального адреса до конечного диалогично изложенному выше циклу работы. Нулевой сигнал с выхода элемента 52 ИЛИ через элемент НЕ 55 устанавливает счетный триггер 44 в нулевое состояние. Таким образом, на выходе триггера 44 формируется в конце каждого цикла работы микропрограммный импульс, поступающий кроме элемента 50 И также на счетный вход счетчика 48 циклов, который работает . в режиме обратного счета и после каждого цикла уменьшает свое содержимое на единицу.

Повторение циклов формирования отлаживаемой части микропрограммы от начального адреса до конечного происходит до тех пор, пока содержимое счетчика 43 не достигнет нуля, В этом случае сигнал с его выхода поступает на элемент 51 И и при наличии единичного сигнала на другом входе элемента 51 И запрещает прохождение сигналов через элемент 50 PI, вследствие чего новый цикл не .начинается и работа устройства заканчивается. Далее работа устройства может быть повторена с другими значениями адресов мик-. ропрограммы и числа циклов, установленных на соответствующих входах устройства.

Если на разряде признака ограничения циклов входа кода окончания операций устройства установлен нулевой сигнал, то сигнал с выхода счетчика 43 циклов никогда не пройдет через элемент 51 И, вследствие чего циклы повторения отлаживаемой части микропрограммы выполняются беспредельно.

Формула изобретения

лок памяти микропрограмм, блок деифраторов микрокоманд, регистр микокоманд, коммутатор условий, первый ольцевой сдвиговый регистр, блок от--. адки -программы, с первого по девятый элементы И, с первого по четвертый элементы ИЛИ, элемент НЕ, причем вход ода операции устройства соединен с ервым информационным входом коммута- Q тора адреса, выход которого соединен с информационным входом счетчика адрё са, информационный выход которого соеинен с адресным входом блока памяти микропрограмм, выход кода микроопера-j ций которого соединен- с информационным входом блока дешифраторов микрокоманд, первый выход которого.соединен с информационным входом регистра микрокоманд, выход кода микроопераций-- которого является выходом микроопераций устройства, выход кода адреса регистра адреса соединен с вторым информационным входом коммутатора адреса, входы логических условий устройства 25 соединены с первой группой информаци- онных входов коммутатора условий, управляющий вход которого соединен с выходом кода условия регистра адреса, выход кодов адреса и условия блока о памяти микрокоманд соединен с информационным входом регистра адреса, отличающееся тем, что, с целью расширения области применения путем обеспечения возможности работы в реальном масштабе времени при мне гоуровневых прерываниях, в него введены стековая память, второй кольцевой сдвиговый регистр, группа RS- три1 геров аппаратных прерываний, RS- триггеры прохождения прерывания, RS- триггер.прерывания, RS-триггер конца прерывания, RS-триггер начальной установки, D-триггер прерывания, D- триггер запрета, с пятого По десятый элементы ИЛИ, причем третий информа- ционньй вход коммутатора адреса соединен с информационным выходом стековой памяти, первый управляющий вход коммутатора адреса соединен с первым входом первого элемента ИЛИ и подключен к выходу признака начала программы блока отладки программы, второй управляющий вход коммутатора- адреса соединен с входом RS-триггера конца прерывания, первым входом второго и вторым входом первого элемента ИЛИ и подключен к выходу третьего элемента И, третий управляющий вход

.- 35

40

50

55

-. Q j -- 25 о

35

40

50

55

коммутатора адреса соединен с входом разрешения обратного сдвига стековой памяти с первыми входами третьего и четвертого элементов ИЛИ и третьим входом первого элемента ИЛИ и подключен к выходу признака возврата региг. стра микрокоманд, счетный вход счетчика адреса подключен к выходу первого элемента И, вход установки в D счетчика адреса соединен с выхо-. дом второго элемента И, вход управления режимом записи счетчика адреса подключен к выходу четвертого элемент та И, а выход счетчика адреса соеди- иен с входом текущего адреса блока отладки программы с информационным входом стековой памяти, вход записи регистра адреса соединен с входами записи регистра микрокоманд второго кольцевого сдвигового регистра и с первым выходом первого кольцевого сдвигового регистра, выход признака типа команды блока памяти микрокоманд соединен с D-входом D-триггера запрета, синхровход которого соединен с первым синхровходом блока отладки программы и с D-входом .RS-триггера , начальной установки, а инверсный выход D-триггера запрета подключен к первому входу пятого элемента ИЛИ, второй вход которого подключен к инверсному выходу D-триггера прерывания пятого элемента ИЛИ-, выход подключен к входу стробирования блока дешифраторов микрокоманд, второй выход блока дешифраторов микрокоманд подключен к входам R RS-триггеров групп аппаратных триггеров прерываний, третий выход блока дешифраторов микрокоманд подключен к первому входу шестого элемента ИЛИ, второй вход которого соединен с вторыми входами второго и первым входом седьмого элементов ИЛИ, В-входом RS-триггера начальной установки, входом начальной установки блока отладки программы и подключен к входу начальной установки устройства, а выход шестого элемента ИЛИ подключен к R-входу RS-триггеров прохождения прерывания и конца прерывания, выход признака условного перехода регистра микрокоманд соединен с первым входом пятого элемента И и подключен к второму входу четвертого элемента ИЛИ, третий вход которого подключен к выходу признака занятое-: ти стековой памяти, четвертый вход четвертого элемента ИЛИ соединен с

выходом признака запрета прерываний регистра микрокоманд, а пятый вход четвертого элемента ИЛИ соединен с прямым выходом RS-триггера конца прерывания, выход четвертого элемента ИЛИ подключен к первому входу шестого элемента И, второй вход которого подключен к первому выходу второго кольцевого сдвигового регистра, а .третий вход шестого элемента И соединен с входом третьего элемента И и подключен к прямому выходу RS-тригге- ра прохождения прерываний, и выход шестого элемента И соединен с первым входом седьмого элемента И и подключен к D-входу D-триггера прерывания, синхровход которого соединен с вторыми входами первого, второго и седьмого элементов И и подключен к второму выходу первого кольцевого сдвигового регистра, а вход сброса D-триггера прерывания подключен к выходу второго элемента ИЛИ, прямой выход D-триггера прерывания подключен к первому входу восьмого элемента ИЛИ, второй вход которого подключен к выходу признака записи в стековую память.регистра микрокоманд, а выход восьмого элемента ИЛИ соединен с входом разрешения прямого сдвига стековой памяти, и подключен к второму входу третьего элемента РШИ, третий вход которого соединен с входом записи указателя стековой памяти, первым входом девятого элемента ИЛИ и подключен к прямому выходу RS-триггера начальной установки, выход третьего элемента ИЛИ соединен с первым входом восьмого элемента И, выход восьмого элемента И подключен к вхоДу записи стековой памяти, третий выход первого кольцевого сдвигового регистра подключен к первому входу четвертого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, четвертый вход которого подключен к выходу пятого элемента И, второй вход которого подключен к выходу коммутатора условий, второй вход восьмого элемента И подключен к четвертому выходу первого кольцевого сдвигового регистра, вторая группа информационных входов ком- м татора условий соединена с выхода-; ми указателя стековой памяти, вход указателя стековой памяти соединен с входом установки вложенных уровней прерывания устройства, третья группа информационных входов коммутатора ус0

5

0

5

0

5

0

5

0

5

ловий соединена с прямыми выходами RS-триггеров группы RS-триггеров аппаратных прерываний, S-входы которых являются входами внешних прерываний устройства, прямые выходы RS- триггеров группы RS-триггеров аппаратных прерываний соединены входами десятого элемента ИЛИ, выход которого подключен к первому входу девятого элемента И, второй вход которого подключен к входу запрета прерываний устройства, третий вход девятого элемента И подключен к инверсному выхо.- ду RS-триггера прохождения прерывания, четвертый вход девятого элемента И подключен к пятому выходу первого кольцевого сдвигового регистра и соединен с вторым синхровходом блока отладки программы, а выход девятого элемента И соединен с S-входом RS- триггера прохождения прерывания, синхровход первого кольцевого сдвигового регистра подключен к синхровходу устройства и соединен с третьим синхровходом блока отладки программы, вход начальной установки первого кольцевого сдвигового регистра и второго кольцевого сдвигового регистра подключен к выходу седьмого элемента ИЛИ, второй вход которого подключен к выходу признака рабочего режима блока отладки программы, выход признака, конца программы которого подключен к второму входу девятого элемента ИЛИ, выход которого соединен с вторым входом второго элемента И и входом элемента НЕ, выход которого подклю- . ченчк в торому входу первого элемента И, шестой выход первого кольцевого сдвигового регистра соединен с R-BXO- дом RS-триггера начальной установки, вход конца программы блока отладки программы соединен с входом кода окончаршя операции устройства, вход пуска устройства соединен с входом пуска блока отладки программы, второй выход второго кольцевого сдвигового регистра подключен к второму входу третьего элемента И, а третий выход второго кольцевого сдвигового регистра подключен к R-входу RS-триггера прерывания S-вход которого подключен к выходу седьмого элемента И, прямой выход RS-триггера прерывания соединен с третьим входом третьего элемента И.

счетчик циклов, счетный триггер, RS- триггер начала и RS-триггер конца программь, RS-триггер останова, с первого по седьмой элементы И, с пер- - вого по третий элементы ИЛИ, элемент НЕ, причем первый и второй входы схе- мы сравнения подключены соответст- венно к младшим разрядам входа конца программы и входу текущего адреса - программы, блока отладки программы, выход схемы сравнения подключен к первому входу первого элемента И, второй вход которого подключен к первому син- хровходу.блока отладки программы, а ,г выход яервого элемента И подключен к S-входу RS-триггера конца программы, R-вход которого соединен с S-входом RS-триггера начала программы, с перовым входом второго элемента И, вхот jn дом элемента НЕ и выходом признака рабочего режима блока отладки программы и подключен к выходу первого элемента ИЛИ, а прямой выход RS-триггера конца программы с выхо- 25 дом признака конца программы блока отладки программы и подключен к первому входу третьего элемента И, второй вход которого соединен с R-входом

RS-триггера.начала программы и под

ганочен к второму синхровходу блока отладки, программы, а выход третьего элемента И подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с вторым входом первого элемента ИЛИ и подключен к входу начальной установки блока отладки программ., а выход второго элемента ИЛИ подключен к З-входу RS-триггера останова, прямой выход которого подключен к первому входу четвертого элемента И, второй вход которого сое

г 5

0

0

динен с первым входом пятого элемента И и подключен к первому старшему разряду входа конца программы блока отладки программ,, а выход четвертого элемента И подключен к первому входу первого элемента ИЛИ, R-вход RS-триггера останова подключен к выходу третьего элемента ИЛИ, первьш вход которого соединен с входом записи счетчика циклов и подключен к входу пуска блок.а отладки программ, а второй вход элемента ИЛИ подключен к выходу элемента И, первый вход которого подключен к второму старшему разряду входа конца программы блока отладки nporfJ af-iM, второй вход элемента И соединен с входом -1 счетчика циклов и подключен к прямому выходу счетного, триггера, а третий вход шестого элемента И подключен к выходу седьмого элемента И, первый вход которого подключен к третьему старшему разряду входа конца программы блока отладки nporpaNjM, а второй вход седьмого элемента И подключен к вых9 ду счетчика циклов, вход сброса и счетный вход счетного триггера подключены соответственно к выходам зле- мента НЕ блока и второго элемента И, второй вход которого подключен к третьему синхровходу блока отладки программ, прямой выход RS-триггера начала программы подключен к второму входу пятого элемента И, а выход пятого элемента И соединен с выходом признака начала программы блока отладки программ, с четвертого по последний старшие разряды входа конца программы соединены с информа - ционными входами счетчика цик ЛОВ .

58

59

SO

61 П

J

дз

БИcpus.Z

гп

J

J

сригЗ

фигМ

Фчг.5

| Микропрограммное устройство управления | 1982 |

|

SU1019450A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1188742A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-15—Публикация

1987-06-15—Подача