Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и системах автоматического управления.

Цель изобретения - расширение функционал ьньгх; возможностей устройства за счет увеличения числа каналов прямогср доступа.

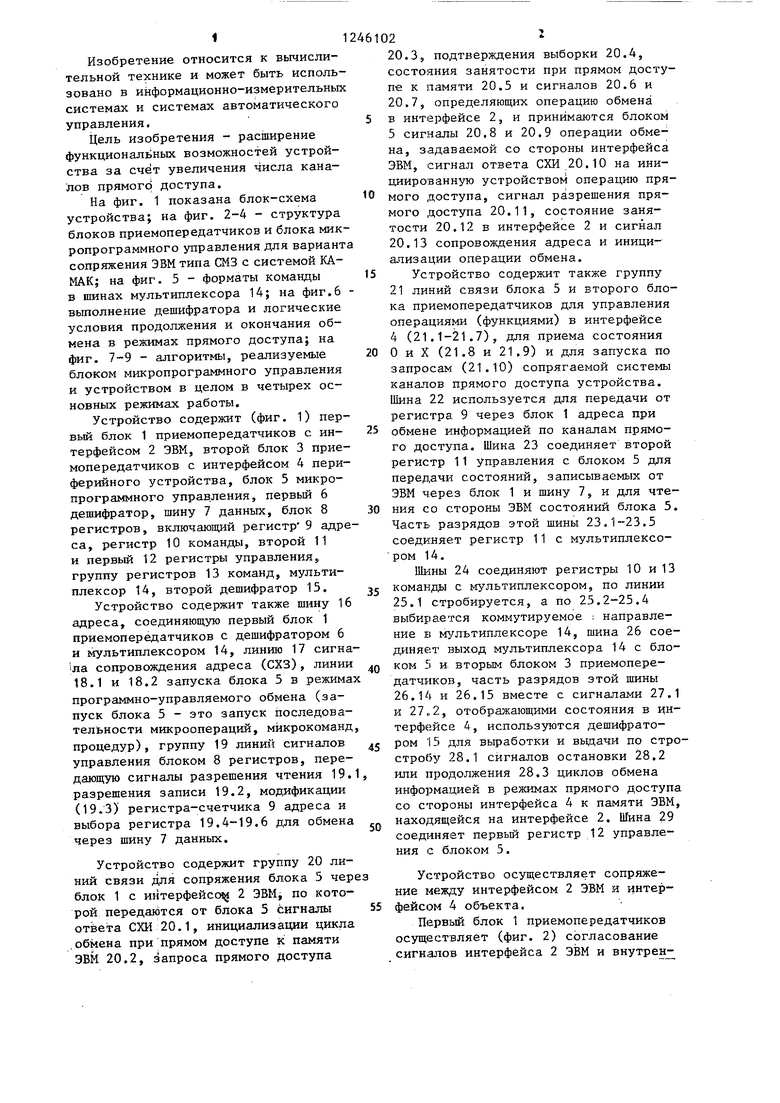

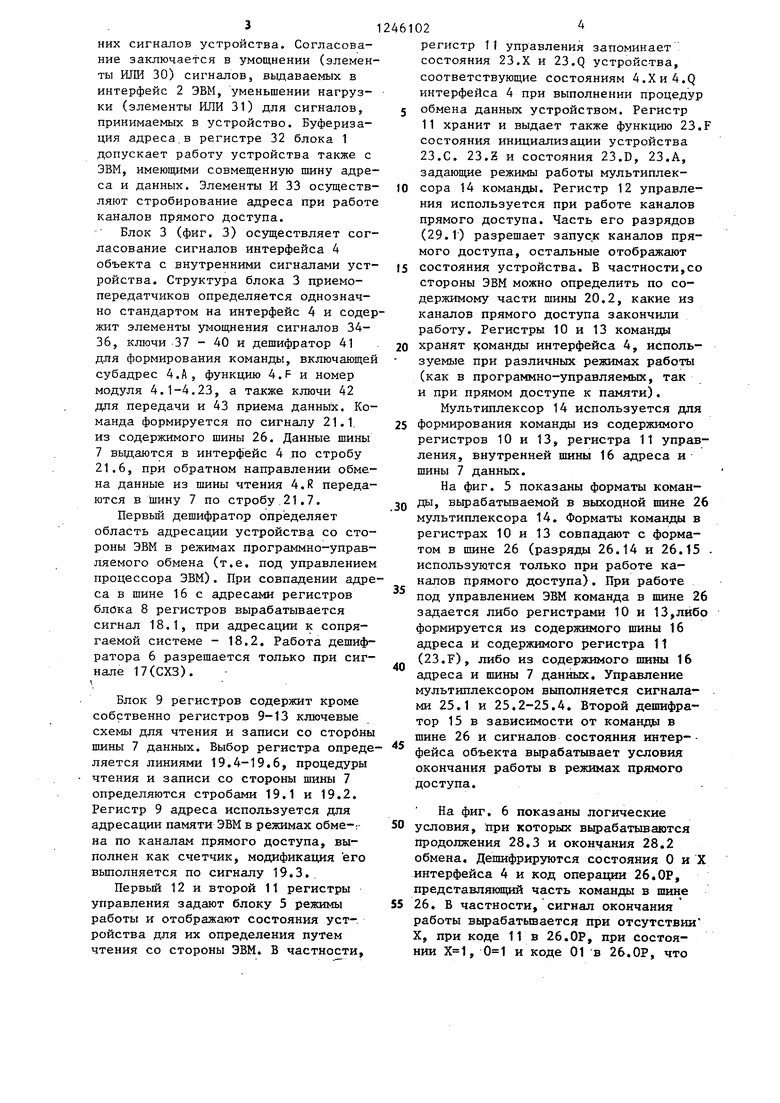

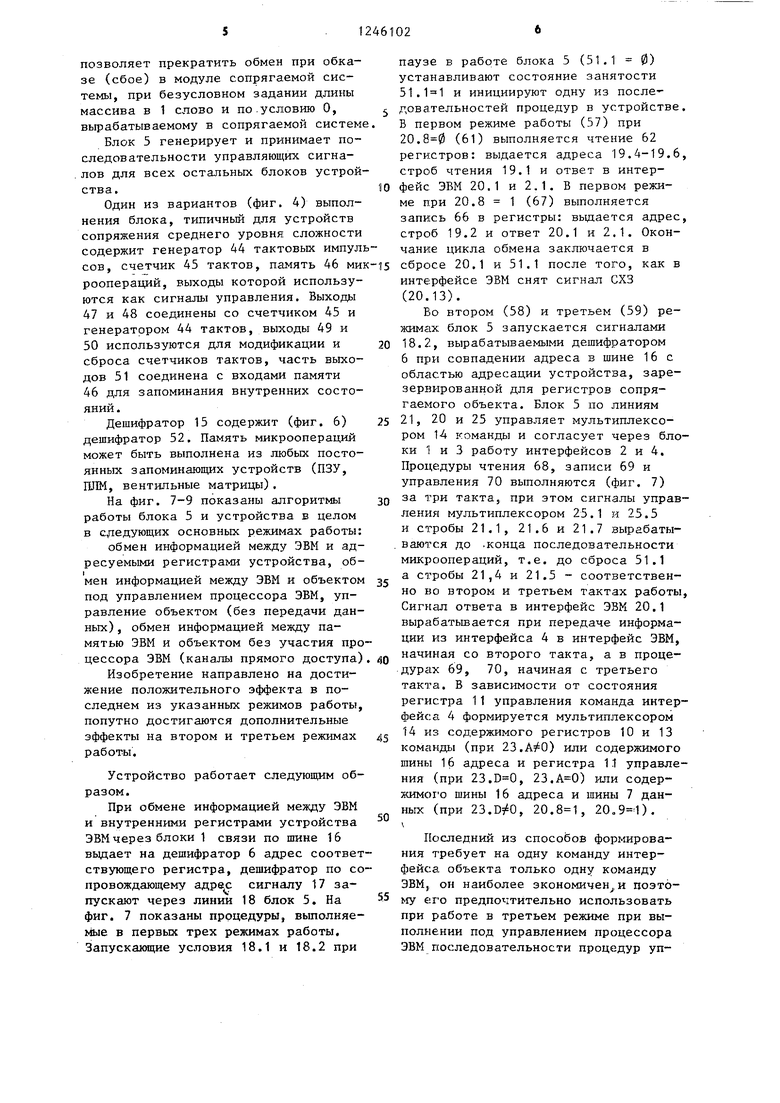

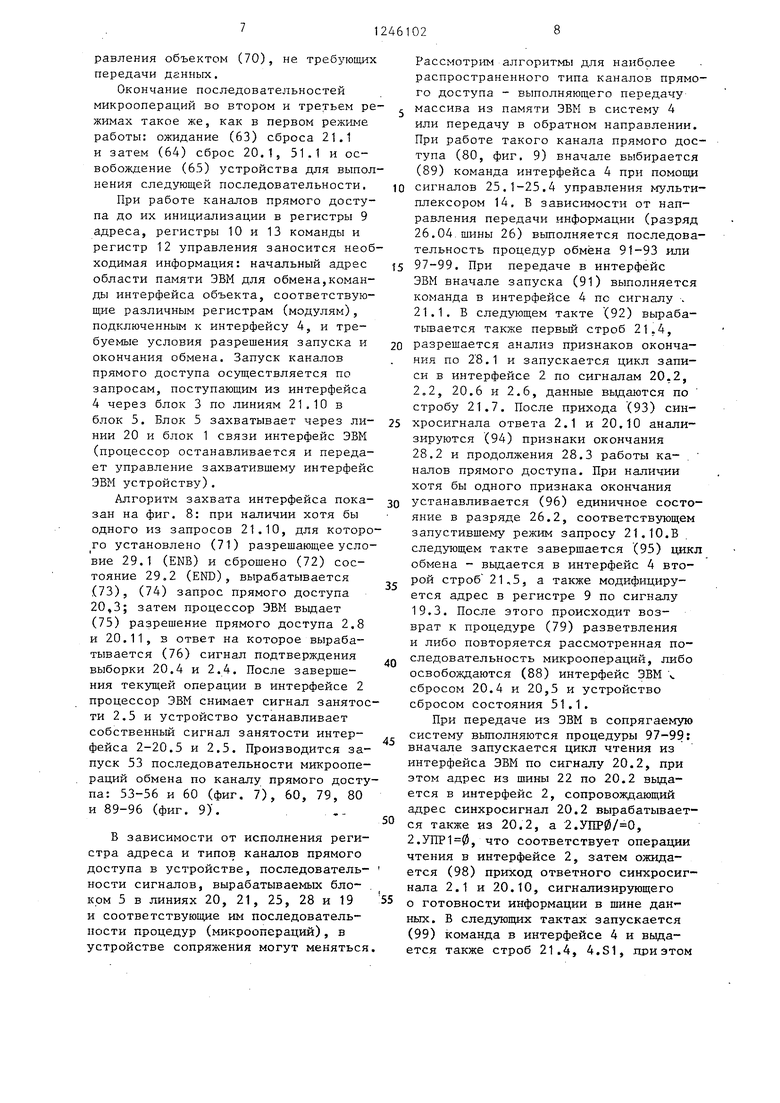

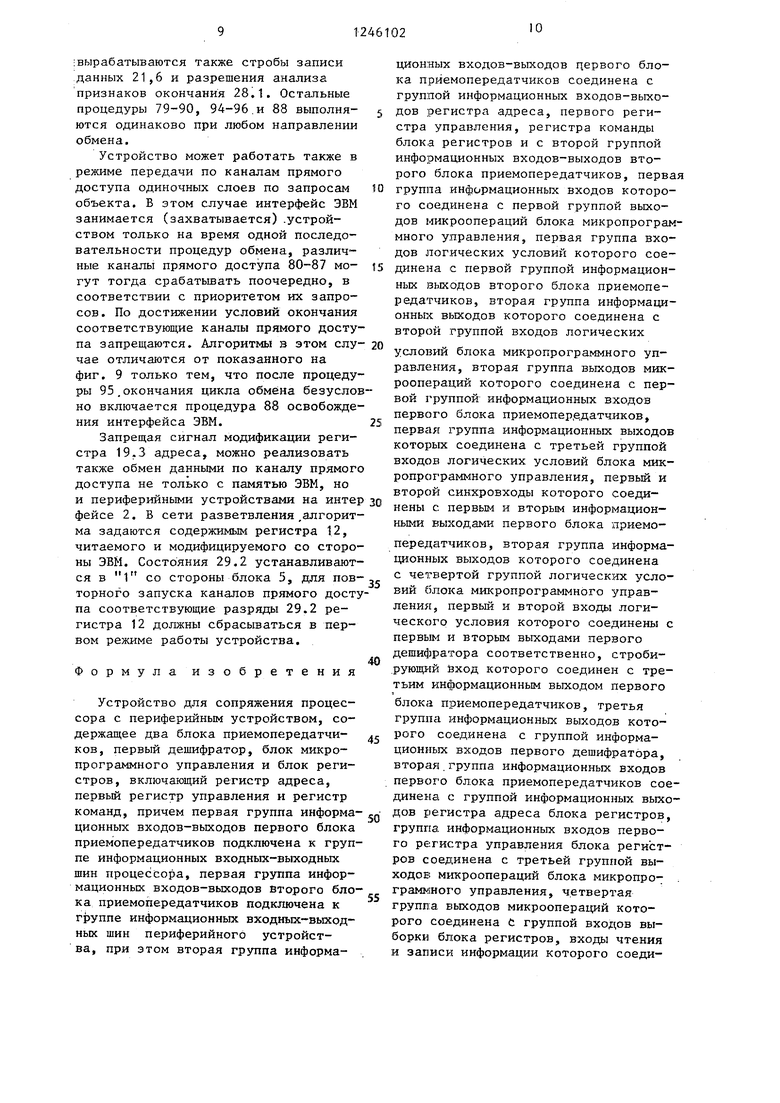

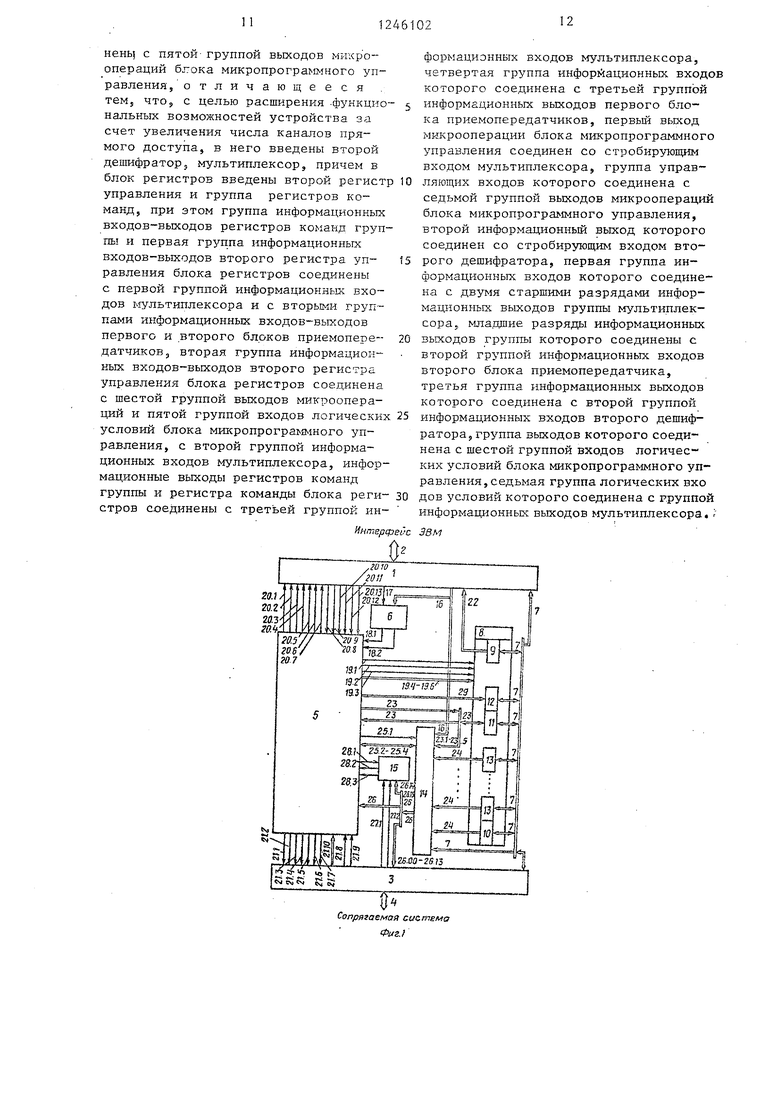

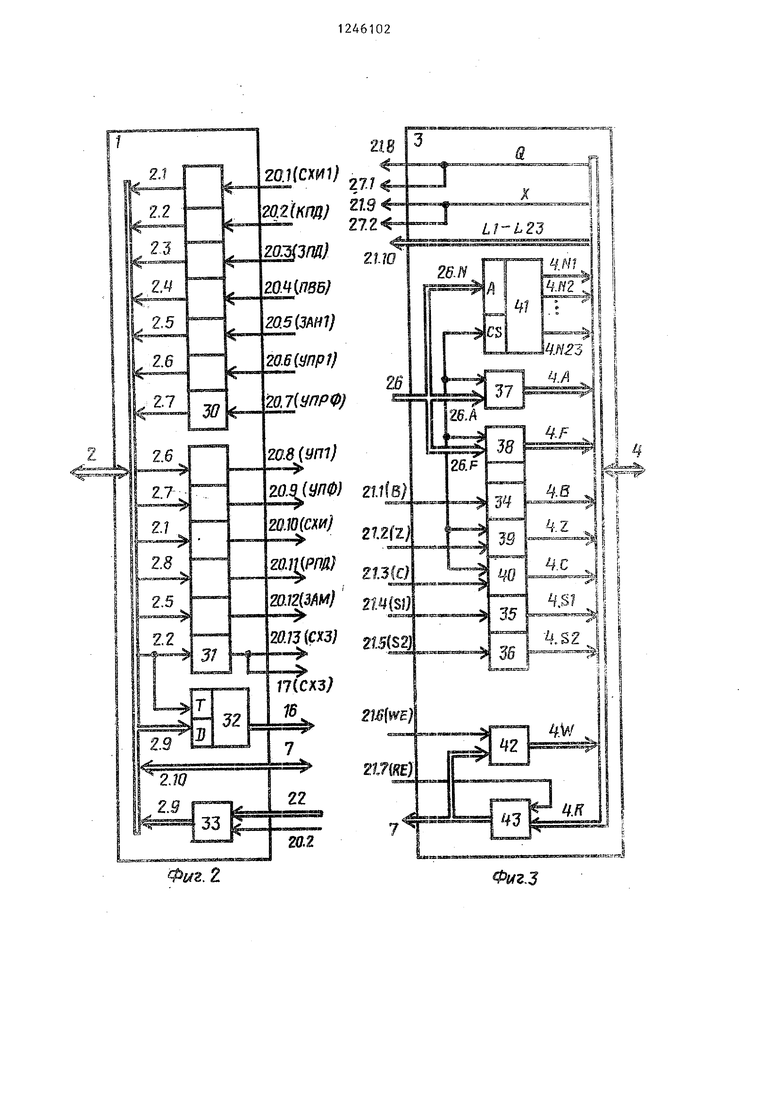

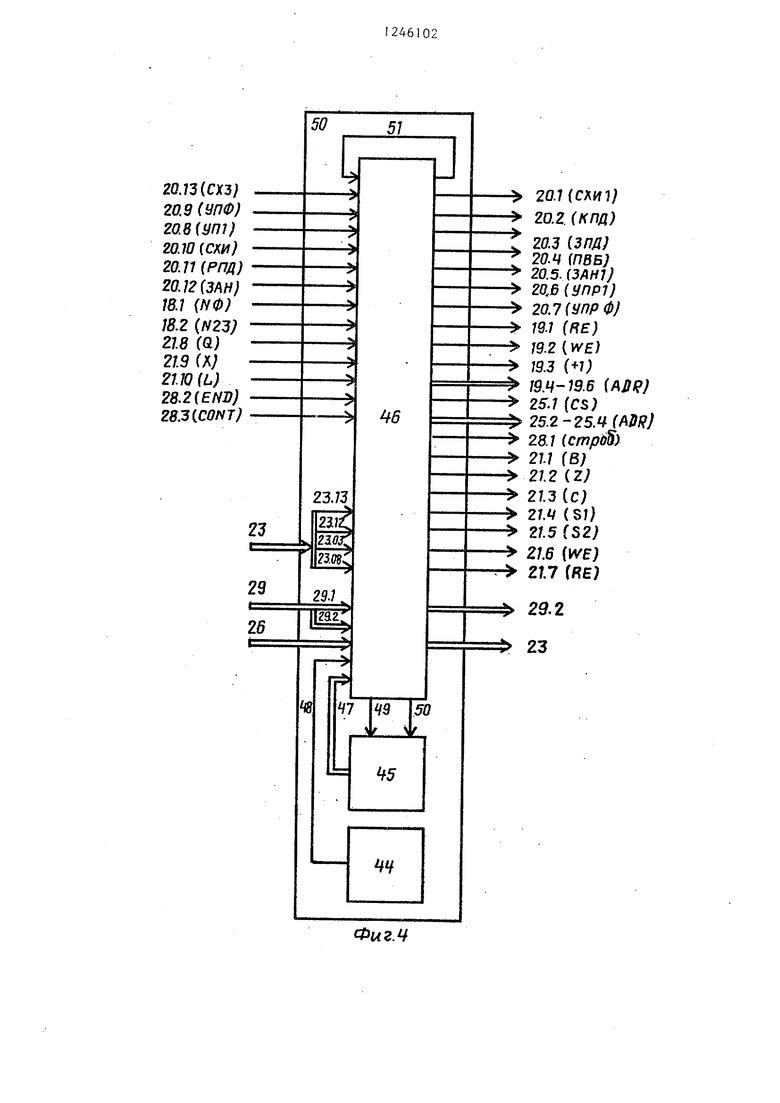

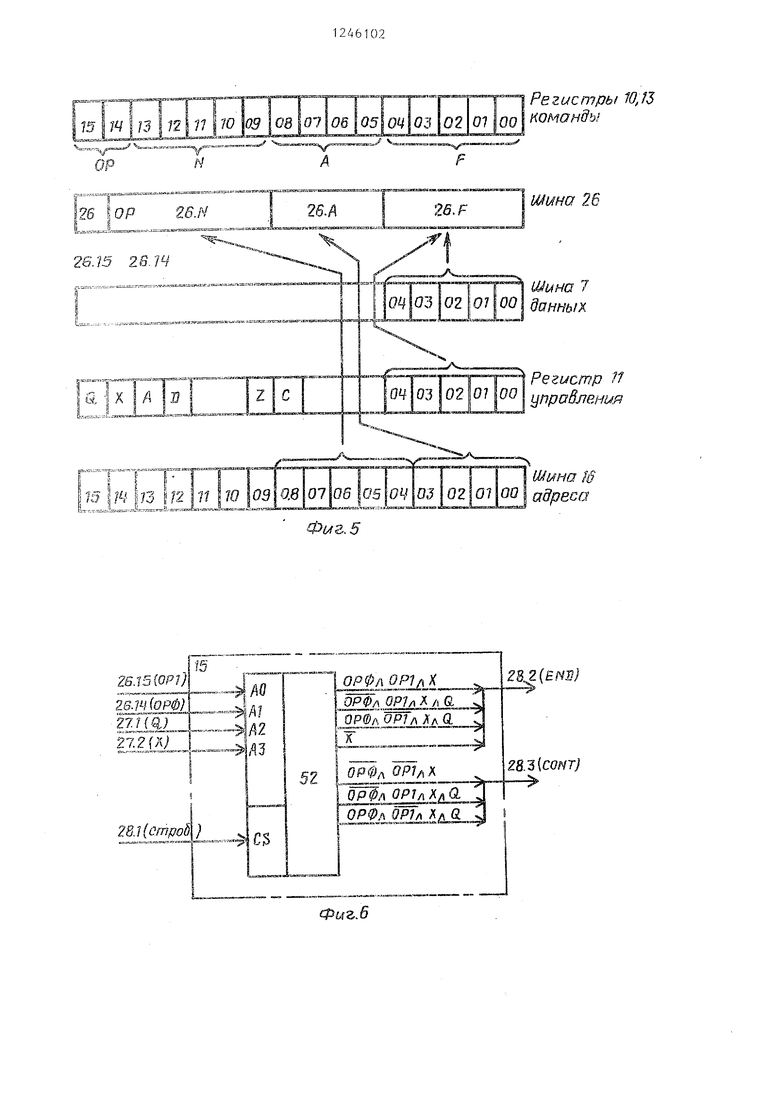

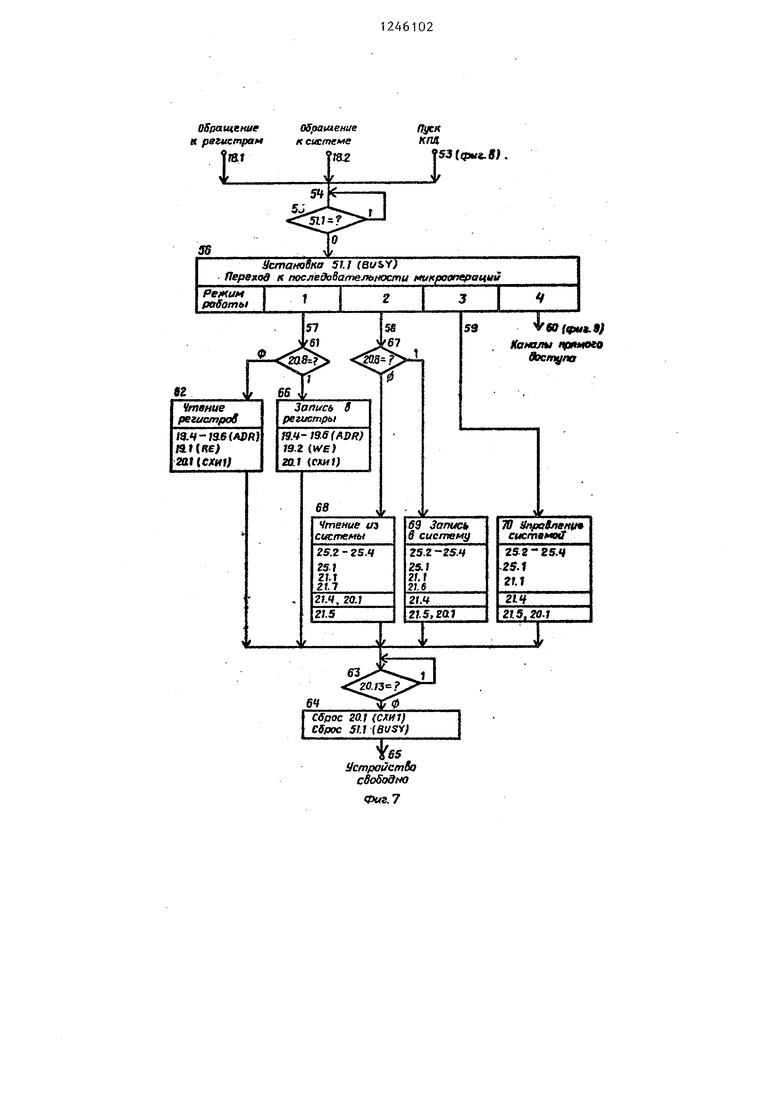

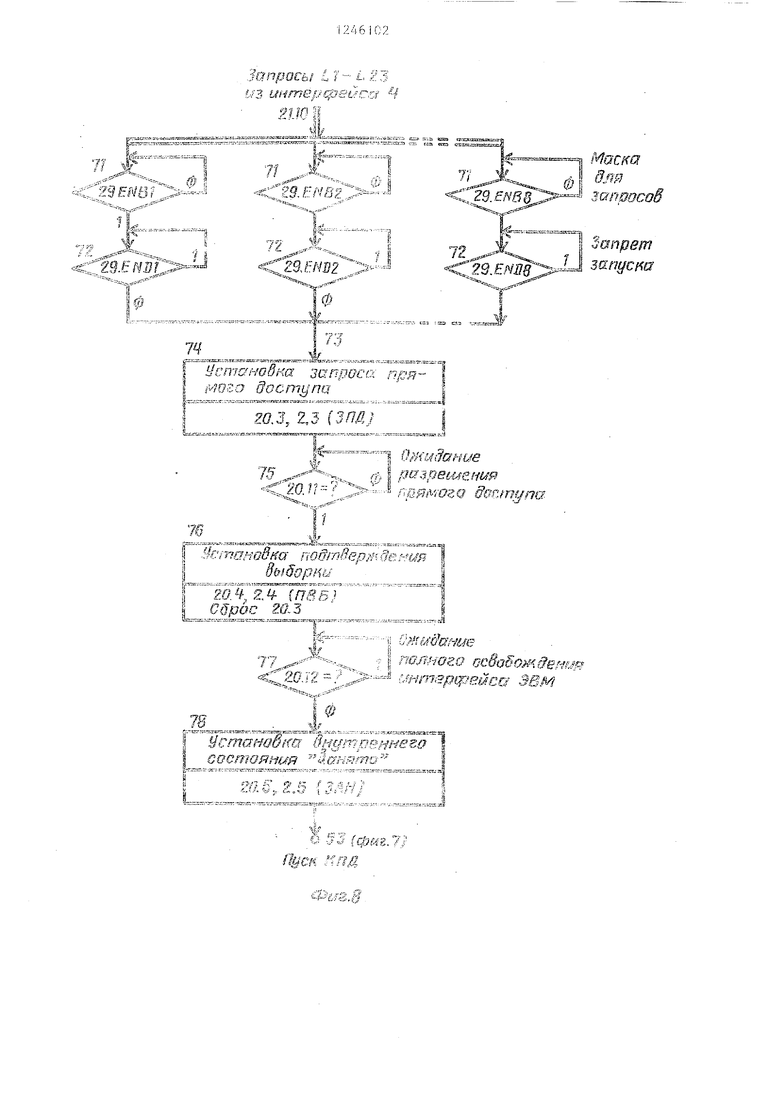

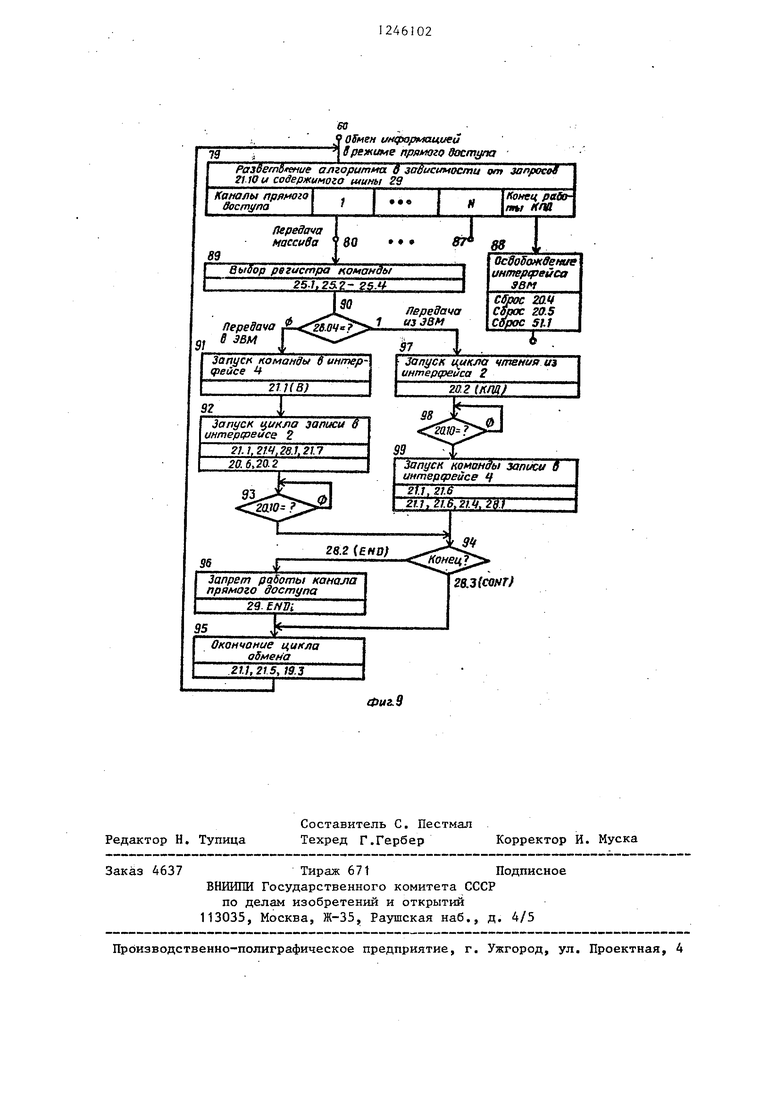

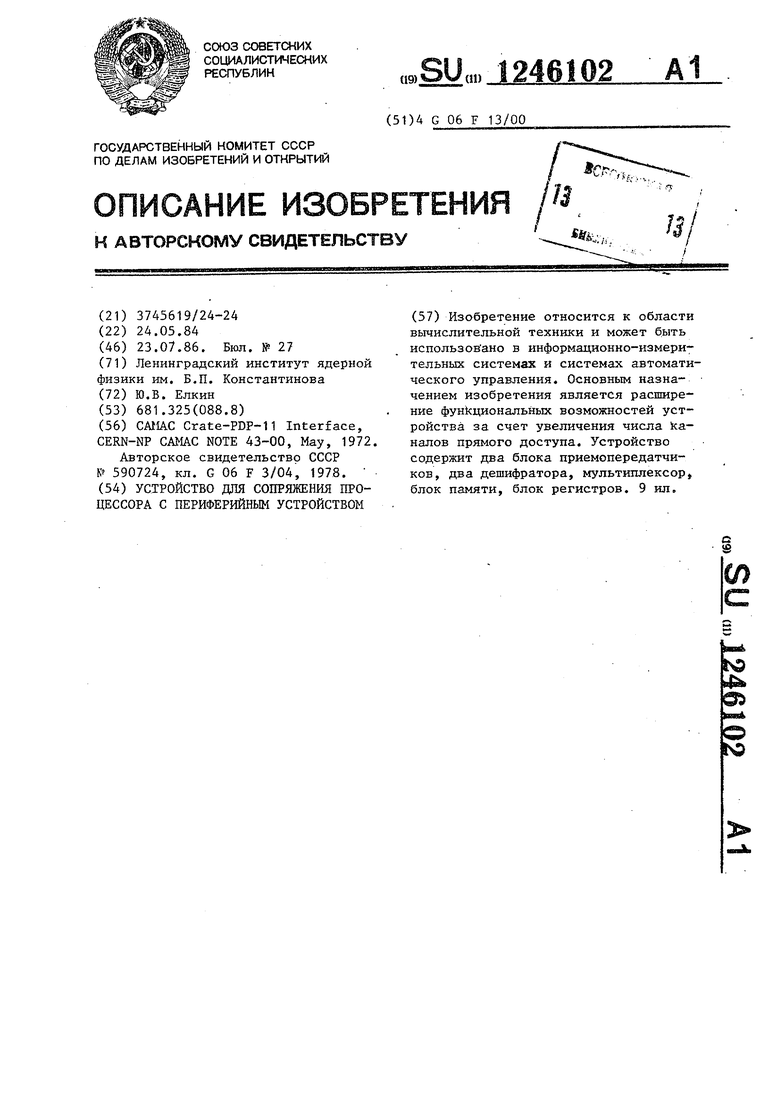

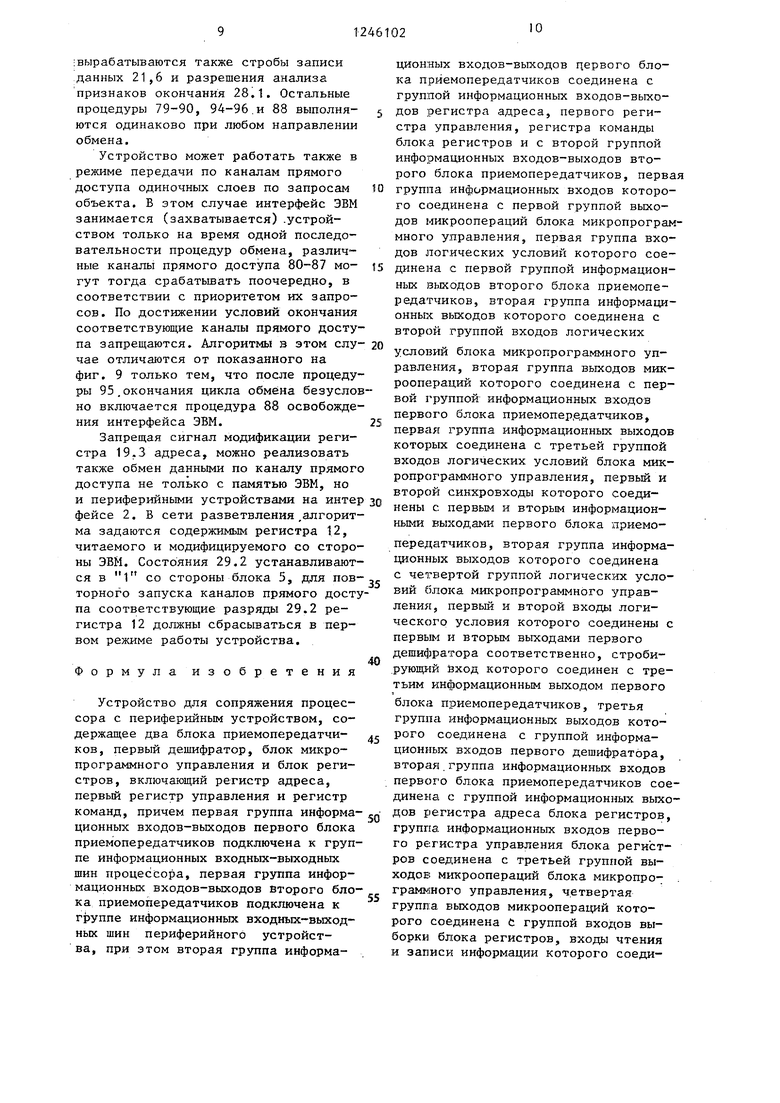

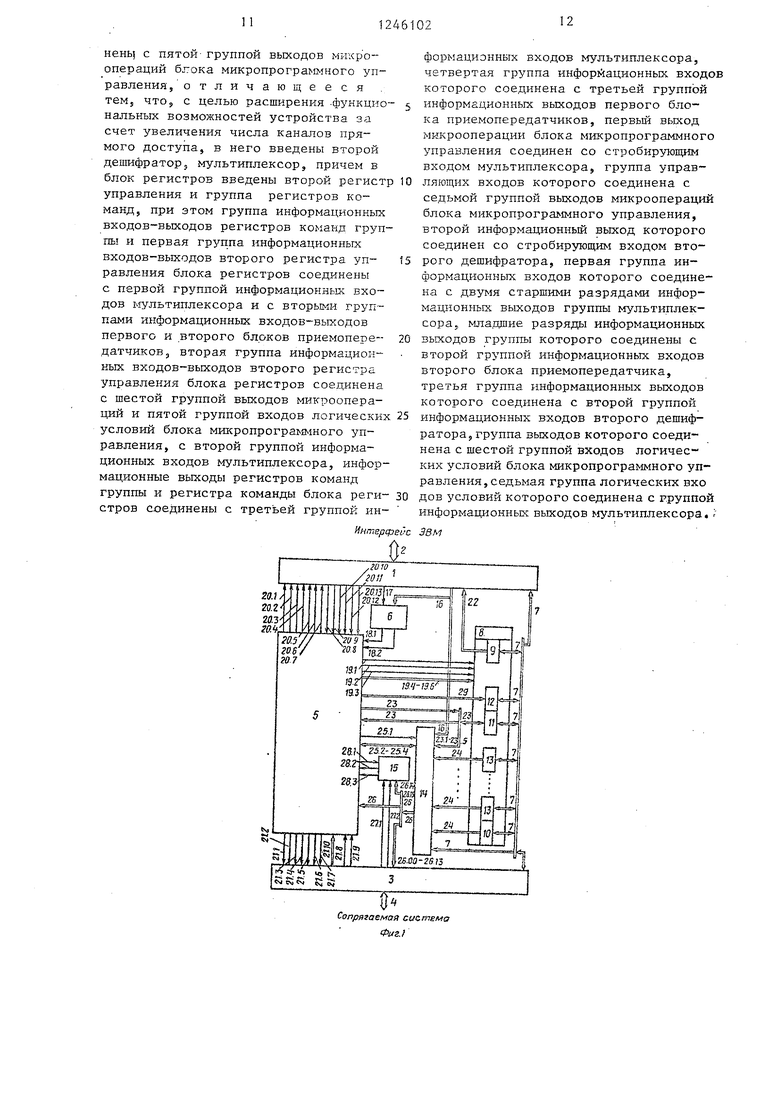

На фиг. 1 показана блок-схема устройства; на фиг. 2-4 - структура блоков приемопередатчиков и блока микропрограммного управления для вариант сопряжения ЭВМ типа СМЗ с системой КА- МАК; на фиг. 5 - форматы команды в шинах мультиплексора 14; на фиг.6 выполнение дешифратора и логические условия продолжения и окончания обмена в режимах прямого доступа; на фиг. 7-9 - алгоритмы, реализуемые блоком микропрограммного управления и устройством в делом в четырех основных режимах работы.

Устройство содержит (фиг. 1) первый блок 1 приемопередатчиков с ин- терфейсом 2 ЭВМ, второй блок 3 приемопередатчиков с интерфейсом 4 периферийного устройства, блок 5 микропрограммного управления, первый 6 дешифратор, шину 7 данных, блок 8 регистров, включающий регистр 9 адреса, регистр 10 команды, второй 11 и первый 12 регистры управления, группу регистров 13 команд, мультиплексор 14, второй дешифратор 15.

Устройство содержит также шину 16 адреса, соединяющую первый блок 1 приемопередатчиков с дешифратором 6 и г ультиплексором 14, линию 17 сигна сопровождения адреса (СХЗ), линии 18.1 и 18.2 запуска блока 5 в режима программно-управляемого обмена (запуск блока 5 - это запуск последовательности микроопераций, микрокоманд процедур), группу 19 линий сигналов управления блоком 8 регистров, передающую сигналы разрешения чтения 19. разрешения записи 19.2, модификации (19.3) регистра-счетчика 9 адреса и выбора регистра 19.4-19.6 для обмена через шину 7 данных.

Устройство содержит группу 20 линий связи для сопряжения блока 5 чер блок 1 с интерфейсов 2 ЭВМ по которой передаются от блока 5 сигналы ответа СХИ 20.1, инициализации цикла .обмена при прямом доступе к памяти ЭВМ 20.2, запроса прямого доступа

20.3, подтверждения выборки 20.4, состояния занятости при прямом доступе к памяти 20.5 и сигналов 20.6 и 20.7, определяющих операцию обмена в интерфейсе 2, и принимаются блоком 5 сигналы 20.8 и 20.9 операции обмена, задаваемой со стороны интерфейса ЭВМ, сигнал ответа СХИ 20.10 на инициированную устройством операцию прямого доступа, сигнал разрешения прямого доступа 20.11, состояние занятости 20.12 в интерфейсе 2 и сигнал

20.13сопровождения адреса и инициализации операции обмена.

Устройство содержит также группу 21 линий связи блока 5 и второго блока приемопередатчиков для управления операциями (функциями) в интерфейсе 4 (21.1-21.7), для приема состояния О и X (21.8 и 21.9) и для запуска по запросам (21.10) сопрягаемой системы каналов прямого доступа устройства. Шина 22 используется для передачи от регистра 9 через блок 1 адреса при обмене информацией по каналам прямого доступа. Шина 23 соединяет второй регистр 11 управления с блоком 5 для передачи состояний, записываемых от ЭВМ через блок 1 и шину 7, и для чтения со стороны ЭВМ состояний блока 5 Часть разрядов этой шины 23.1-23.5 соединяет регистр 11 с мультиплексором 14.

Шины 24 соединяют регистры 10 и 13 команды с мультиплексором, по линии 25.1 стробируется, а по 25.2-25.4 выбирается коммутируемое : направление в м шьтиплeкcope 14, шина 26 сое- выход мультиплексора 14 с блоком 5 и вторым блоком 3 приемопередатчиков, часть разрядов этой шины

26.14и 26.15 вместе с сигналами 27.1 и 27„2, отображающими состояния в интерфейсе 4, используются дешифратором 15 для выработки и выдачи по стро стробу 28.1 сигналов остановки 28.2 или продолжения 28.3 циклов обмена информацией в режимах прямого доступа со стороны интерфейса 4 к памяти ЭВМ, находящейся на интерфейсе 2. 29 соединяет первый регистр 12 управления с блоком 5.

Устройство осуществляет сопряжение меж;с;у интерфейсом 2 ЭВМ и интерфейсом 4 объекта.

Первьй блок 1 приемопередатчиков осуществляет (фиг. 2) согласование сигнштов интерфейса 2 ЭВМ и внутренних сигналов устройства. Согласование заключается в умощнении (элементы ШШ 30) сигналов, выдаваемых в интерфейс 2 ЭВМ, уменьшении нагрузки (элементы ИЛИ 31) для сигналов, принимаемых в устройство. Буферизация адреса,в регистре 32 блока 1 допускает работу устройства также с ЭВМ, имеющими совмещенную шину адреса и данных. Элементы И 33 осуществляют стробирование адреса при работе каналов прямого доступа.

Блок 3 (фиг, 3) осуществляет согласование сигналов интерфейса 4 объекта с внутренними сигналами устройства. Структура блока 3 приемопередатчиков определяется однозначно стандартом на интерфейс 4 и содержит элементы умощнения сигналов 34- 36, ключи 37 - 40 и дешифратор 41 для формирования команды, включающей субадрес 4.А, функцию 4.F и номер модуля 4.1-4.23, а также ключи 42 для передачи и 43 приема данных. Команда формируется по сигналу 21.1. из содержимого шины 26. Данные шины 7 выдаются в интерфейс 4 по стробу 21.6, при обратном направлении обмена данные из шины чтения 4.R передаются в шину 7 по стробу.21.7.

Первый дешифратор определяет область адресации устройства со стороны ЭВМ в режимах программно-управляемого обмена (т.е. под управлением процессора ЭВМ). При совпадении адреса в шине 16 с адресами регистров блока 8 регистров вырабатывается сигнал 18.1, при адресации к сопрягаемой системе - 18.2, Работа дешифратора 6 разрешается только при сигнале 17(СХЗ).

Блок 9 регистров содержит кроме собственно регистров 9-13 ключевые схемы для чтения и записи со сторбны шины 7 данных. Выбор регистра опреде ляется линиями 19.4-19.6, процедуры чтения и записи со стороны шины 7 определяются стробами 19.1 и 19.2. Регистр 9 адреса используется для адресации памяти ЭВМ в режимах обме-- на по каналам прямого доступа, выполнен как счетчик, модификация его вьшолняется по сигналу 19.3,.

Первый 12 и второй 11 регистры управления задают блоку 5 режимы работы и отображают состояния устройства для их определения путем чтения со стороны ЭВМ, В частности.

o

S

0

5

0

5

0

5

регистр 11 управления запоминает состояния 23.x и 23.Q устройства, соответствующие состояниям 4.Хи4.р интерфейса 4 при выполнении процедур обмена данных устройством. Регистр 11 хранит и выдает также функцию 23.F состояния инициализации устройства 23.С. 23.Z и состояния 23.D, 23.А, задающие режимы работы мультиплексора 14 команды. Регистр 12 управления используется при работе каналов прямого доступа. Часть его разрядов (29.1) разрешает за:пуск каналов прямого доступа, остальные отображают состояния устройства. В частности,со стороны ЭВМ можно определить по содержимому части шины 20.2, какие из каналов прямого доступа закончили работу. Регистры 10 и 13 команды хранят команды интерфейса 4, используемые при различных режимах работы (как в программно-управляемых, так и при прямом доступе к памяти).

Мультиплексор 14 используется для формирования команды из содержимого регистров 10 и 13, регистра 11 управления, внутренней шины 16 адреса и шины 7 данных.

На фиг. 5 показаны форматы команды, вырабатываемой в выходной шине 26 мультиплексора 14. Форматы команда в регистрах 10 и 13 совпадают с форматом в шине 26 (разряды 26.14 и 26.15 . используются только при работе каналов прямого доступа). При работе под управлением ЭВМ команда в шине 26 задается либо регистрами 10 и 13,либо формируется из содержимого шины 16 адреса и содержимого регистра 11 (23.F), либо из содержимого шины 16 адреса и шины 7 данных. Управление мультиплексором выполняется сигналами 25,1 и 25.2-25.4, Второй дешифратор 15 в зависимости от команды в шине 26 и сигналов состояния интер- фейса объекта вырабатывает условия окончания работы в режимах прямого доступа.

На фиг. 6 показаны логические условия. При которых вырабатываются продолжения 28,3 и окончания 28,2 обмена, Дешифрирзтотся состояния О и X интерфейса 4 и код операции 26.ОР, представляющий часть команды в шине 26. В частности, сигнал окончания работы вырабатьшается при отсутствии X, при коде 11 в 26.ОР, при состоянии , и коде 01 в 26,ОР, что

позволяет прекратить обмен при обка- 36 (сбое) в модуле сопрягаемой системы, при безусловном задании длины массива в 1 слово и по.условию О, вырабатываемому в сопрягаемой систем

Блок 5 генерирует и принимает последовательности управляющих сигналов для всех остальных блоков устройства.

Один из вариантов (фиг. 4) выполнения блока, типичный для устройств сопряжения среднего уровня сложности содержит генератор 44 тактовых импулсов, счетчик 45 тактов, память 46 ми роопераций, выходы которой используются как сигналы управления. Выходы 47 и 48 соединены со счетчиком 45 и генератором 44 тактов, выходы 49 и 50 используются для модификации и сброса счетчиков тактов, часть выходов 51 соединена с входами памяти 46 для запоминания внутренних состояний .

Дешифратор 15 содержит (фиг. 6) дешифратор 52. Память микроопераций может быть выполнена из любых постоянных запоминающих устройств (ПЗУ, ПЛМ, вентильные матрицы).

На фиг. 7-9 показаны алгоритмы работы блока 5 и устройства в целом в следующих основных режимах работы:

обмен информацией между ЭВМ и адресуемыми регистрами устройства, обмен информацией между ЭВМ и объектом под управлением процессора ЭВМ, управление объектом (без передачи данных) , обмен информацией между памятью ЭВМ и объектом без участия процессора ЭВМ (каналы прямого доступа)

Изобретение направлено на достижение положительного эффекта в последнем из указанных режимов работы, попутно достигаются дополнительные эффекты на втором и третьем режимах работы.

Устройство работает следующим образом.

При обмене информацией между ЭВМ и внутренними регистрами устройства ЭВМ через блоки 1 связи по шине 16 выдает на дешифратор 6 адрес соответствующего регистра, дешифратор по сопровождающему адрех; сигналу 17 запускают через линии 18 блок 5. На фиг. 7 показаны процедуры, вьшолняе- мые в первых трех режимах работы, Запускахщие условия 18.1 и 18.2 при

0

5 0

5

о

5 0

5

5

0

паузе в работе блока 5 (51.1 0) устанавливают состояние занятости 51. и инициируют одну из последовательностей процедур в устройстве. Б первом режиме работы (57) при 20. (61) выполняется чтение 62 регистров: выдается адреса 19.4-19.6, строб чтения 19.1 и ответ в интерфейс ЭВМ 20.1 и 2.1. В первом режиме при 20.8 1 (67) выполняется запись 66 в регистры: выдается адрес, строб 19.2 и ответ 20.1 и 2.1. Окончание цикла обмена заключается в сбросе 20.1 и 51.1 после того, как в интерфейсе ЭВМ снят сигнал СХЗ (20.13).

Во втором (58) и третьем (59) режимах блок 5 запускается сигналами 18.2, вырабатываемыми дешифратором 6 при совпадении адреса в шине 16 с областью адресации устройства, зарезервированной для регистров сопрягаемого объекта. Блок 5 по линиям 21, 20 и 25 управляет мультиплексором 14 команды и согласует через блоки 1 и 3 работу интерфейсов 2 и 4. Процедуры чтения 68, записи 69 и управления 70 выполняются (фиг. 7) за три такта, при этом сигналы управления мультиплексором 25.1 и 25.5 и стробы 21,1, 21.6 и 21.7 вырабаты- . ваются до .конца последовательности микроопераций, т.е. до сброса 51.1 а стробы 21,4 и 21.5 - соответственно во втором и третьем тактах работы, Сигнал ответа в интерфейс ЭВМ 20.1 вырабатьшается при передаче информации из интерфейса 4 в интерфейс ЭВМ, начиная со второго такта, а в процедурах 69, 70, начиная с третьего такта. В зависимости от состояния регистра 11 управления команда интерфейса 4 формируется мультиплексором 14 из содержимого регистров 10 и 13 командь, (при 23.) или содержимого шины 1 (э адреса и регистра 11 управления (при 23., 23,) или содержимого шины 16 адреса и шины 7 данных (при 23., 20., 20,).

Последний из способов формирования тр€2бует на одну команду интерфейса объекта только одну команду ЭВМ, он наиболее экономичен, и поэтому его предпочтительно использовать при работе в третьем режиме при выполнении под управлением процессора ЭВМ последовательности процедур управления объектом (70), не требующих передачи данных.

Окончание последовательностей микроопераций во втором и третьем режимах такое же, как в первом режиме работы: ожидание (63) сброса 21.1 и затем (64) сброс 20.1, 51.1 и освобождение (65) устройства для выполнения следующей последовательности.

При работе каналов прямого доступа до их инициализации в регистры 9 адреса, регистры 10 и 13 команды и регистр 12 управления заносится необходимая информация: начальный адрес области памяти ЭВМ для обмена,команды интерфейса объекта, соответствующие различным регистрам (модулям), подключенным к интерфейсу 4, и требуемые условия разрешения запуска и окончания обмена. Запуск каналов прямого доступа осуществляется по запросам, поступающим из интерфейса 4 через блок 3 по линиям 21.10 в блок 5, Блок 5 захватывает через линии 20 и блок 1 связи интерфейс ЭВМ (процессор останавливается и передает управление захватившему интерфейс ЭВМ устройству).

Алгоритм захвата интерфейса показан на фиг. 8: при наличии хотя бы одного из запросов 21.10, для которого установлено (71) разрешающее условие 29.1 (ENB) и сброшено (72) состояние 29.2 (END), вырабатывается (73), (74) запрос прямого доступа 20,3; затем процессор ЭВМ вьщает (75) разрешение прямого доступа 2.8 и 20.11, в ответ на которое вырабатывается (76) сигнал подтверждения выборки 20.4 и 2.4. После завершения текущей операции в интерфейсе 2 процессор ЭВМ снимает сигнал занятости 2.5 и устройство устанавливает собственный сигнал занятости интерфейса 2-20.5 и 2.5. Производится запуск 53 последовательности микроопераций обмена по каналу прямого доступа: 53-56 и 60 (фиг. 7), 60, 79, 80 и 89-96 (фиг. 9).

В зависимости от исполнения регистра адреса и типов каналов прямого доступа в устройстве, последовательности сигналов, вырабатываемых бло- ком 5 в линиях 20, 21, 25, 28 и 19 и соответствующие им последовательности процедур (микроопераций), в устройстве сопряжения могут меняться

Рассмотрим алгоритмы для наиболее распространенного типа каналов прямого доступа - выполняющего передачу с массива из памяти ЭВМ в систему 4 или передачу в обратном направлении. При работе такого канала прямого доступа (80, фиг. 9) вначале выбирается (89) команда интерфейса 4 при помошд

10 сигналов 25.1-25.4 управления мультиплексором 14. В завис1-1мости от направления передачи информации (разряд 26.04 шины 26) выполняется последовательность процедур обмена 91-93 или

t5 97-99. При передаче в интерфейс

ЭВМ вначале запуска (91) выполняется команда в интерфейсе 4 по сигналу . 21.1. В следующем такте (92) выраба- тьшается также первый строб 21.4,

20 разрешается анализ признаков окончания по 28.1 и запускается цикл записи в интерфейсе 2 по сигналам 20.2, 2.2, 20.6 и 2.6, данные выдаются по стробу 21.7. После прихода (93) син5 хросигнала ответа 2.1 и 20.10 анализируются (94) признаки окончания 28.2 и продолжения 28.3 работы ка- . налов прямого доступа. При наличии хотя бы одного признака окончания

0 устанавливается (96) единичное состояние в разряде 26.2, соответствующем запустившему режим запросу 21.10.В следующем такте завершается (95) цикл обмена - вьщается в интерфейс 4 второй строб 21,5, а также модифицируется адрес в регистре 9 по сигналу 19.3. После этого происходит возврат к процедуре (79) разветвления и либо повторяется рассмотренная поQ следовательность микроопераций, либо освобождаются (88) интерфейс ЭВМ v сбросом 20.4 и 20,5 и устройство сбросом состояния 51.1.

При передаче из ЭВМ в сопрягаемую систему вьтолняются процедуры 97-99: вначале запускается цикл чтения из интерфейса ЭВМ по сигналу 20.2, при этом адрес из шины 22 по 20.2 вьщается в интерфейс 2, сопровождающий адрес синхросигнал 20.2 вырабатывает- 0 ся также из 20.2, а 2.У11Р0/ 0,

2.УТГР1 0, что соответствует операции чтения в интерфейсе 2, затем ожидается (98) приход ответного синхросигнала 2.1 и 20.10, сигнализирующего 5 о готовности информации в шине данных. В следующих тактах запускается (99) команда в интерфейсе 4 и выдается также строб 21.4, 4.S1, при этом

5

iвырабатываются также стробы записи данных 21,6 и разрешения анализа признаков окончания 28,1. Остальные процедуры 79-90, 94-96.и 88 выполни- ются одинаково при любом направлении обмена.

Устройство может работать также в режиме передачи по каналам прямого доступа одиночных слоев по запросам объекта, В этом случае интерфейс ЭВМ занимается (захватывается) .устройством только на время одной последовательности процедур обмена, различные каналы прямого доступа 80-87 мо- гут тогда срабатьшать поочередно, в соответствии с приоритетом их запросов. По достижении условий окончания соответствующие каналы прямого доступа запрещаются. Алгоритмы в этом слу- чае отличаются от показанного на фиг, 9 только тем, что после процедуры 95.окончания цикла обмена безусловно включается процедура 88 освобождения интерфейса ЭВМ,

Запрещая сигнал модификации регистра 19.3 адреса, можно реализовать также обмен данными по каналу прямого доступа не только с памятью ЭВМ, но и периферийными устройствами на интер фейсе 2, Б сети разветвления .алгоритма задаются содержимым регистра 12, читаемого и модифицируемого со стороны ЭВМ, Состояния 29,2 устанавливаются в 1 со стороны блока 5, для повторного запуска каналов прямого доступа соответствующие разряды 29,2 регистра 12 должны сбрасываться в первом режиме работы устройства,

Формула изобретения

Устройство для сопряжения процессора с периферийным устройством, содержащее два блока приемопередатчи- ков, первый дешифратор, блок микропрограммного управления и блок регистров, включающий регистр адреса, первый регистр управления и регистр команд, причем первая группа информа- ционных входов-выходов первого блока приемопередатчиков подключена к группе информационных входных-выходных шин процессора, первая группа информационных входов-выходов второго блока приемопередатчиков подключена к группе информационных входных-выходных шин периферийного устройства, при этом вторая группа информационных входов-выходов первого блока приемопередатчиков соединена с группой информационных входов-выходов регистра адреса, первого регистра управления, регистра команды блока регистров и с второй группой информационных входов-выходов второго блока приемопередатчиков, перва группа информационных входов которого соединена с первой группой выходов микроопераций блока микропрограммного управления, первая группа входов логических условий которого соединена с первой группой информационных выходов второго блока приемопередатчиков, вторая группа информационных выходов которого соединена с второй группой входов логических

условий блока микропрограммного управления, вторая группа выходов микроопераций которого соединена с первой группой информационных входов первого блока приемопередатчиков, первая группа информационных выходов которых соединена с третьей группой входов логических условий блока мик- ропрограм шого управления, первый и второй синхровходы которого соединены с первым и вторым информационными выходами первого блока приемопередатчиков, вторая группа информационных выходов которого соединена с четвертой группой логических условий блока микропрограммного управления, первый и второй входы логического условия которого соединены с первым и вторым выходами первого дешифратора соответственно, строби- .рующий йход которого соединен с третьим информационным выходом первого блока п;риемопередатчиков, третья группа информационных выходов которого соединена с группой информационных входов первого дешифратора, вторая.группа информационных входов первого блока приемопередатчиков соединена с группой информационных выходов регистра адреса блока регистров, группа информационных входов первого регистра управления блока регистров соединена с третьей группой вы- ХОДОЕ1 микроопераций блока микропрограммного управления, четвертая группа выходов микроопераций которого соединена С группой входов выборки блока регистров, входы чтения и записи информации которого соединень; с пятой- группой выходов микро-операций блока микропрограммного управления, отличающееся TBMj что, с целью расширения .функцио- нальных возможностей устройства за счет увеличения числа каналов прямого доступа, в него введены второй дешифраторэ мультиплексор, причем в

блок регистров введены второй регистр 10 ляющих входов которого соединена с

управления и группа регистров команд, при этом группа информационных входов-выходов регистров команд группы и первая группа информационных входов-выходов второго регистра управления блока регистров соединены с первой группой информационных входов мультиплексора и с вторыми группами информационных входов-выходов первого и второго блоков приемопередатчиков, вторая группа информационных входов-выходов второго регистра управления блока регистров соединена с шестой группой выходов микроопераций и пятой группой входов логических условий блока микропрограммного управления, с второй группой информационных входов мультиплексора, информационные выходы регистров команд группы и регистра команды блока реги- стров соединены с третьей группой ин(t«

Сопрягаемой система Фиг.

форыационных входов мультиплексора, четвертая группа информационных входов которого соединена с третьей группой информационных выходов первого блока приемопередатчиков, первый выход микрооперации блока микропрограммного управления соединен со стробирующим входом мультиплексора, группа управ15

20

25ЗОседьмой группой выходов микроопераций блока микропрограммного управления, второй информационный выход которого соединен со стробирующим входом второго дешифратора, первая группа информационных входов которого соединена с двумя старшими разрядами информационных выходов группы мультиплексора, младшие разряды информационных выходов группы которого соединены с второй группой информационных входов второго блока приемопередатчика, третья группа информационных выходов которого соединена с второй группой информационных входов второго дешифратора, группа выходов которого соединена с шестой группой входов логичес ких условий блока микропрограммного управления, седьмая группа логических вхо дов условий которого соединена с группой информационных выходов мультиплексор а 4

реС с ЭВМ 2

О

0l/2.Z

ФигЗ

20.73(СХЗ;

20.9(УПФ) 20.8 (Ут)

20.10(СХИ)

20.11(РПД)

20.12(ЗАН)

18.1(N0)

18.2(N23} 218 (d)

21.9 (л;

21.10 (L)

28.2(EHD)

28.3(CONT)

(R)

Фиг.Ч

N

„„«« и

Регистры lOJZ команды

. v,

т IOP 26.Н

Шина 26

Шина 7 001 донных

Регистр 11 управления

Ш1АНО /1 адреса

, 5

Фигб

5J

SS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1224805A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для сопряжения эвм с периферийной системой | 1984 |

|

SU1246104A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1332326A1 |

| Устройство для обмена информацией с общей шиной | 1984 |

|

SU1322301A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

Изобретение относится к области вычислительной техники и может быть использов ано в информационно-измерительных системах и системах автоматического управления. Основным назначением изобретения является расширение фyнkциoнaльныx возможностей устройства за счет увеличения числа ka- налов прямого доступа. Устройство содержит два блока приемопередатчиков, два дешифратора, мультиплексор блок памяти, блок регистров. 9 ил.

64

CSfjoc 20. t (СХИ1)

csmc su (BUSY}

6S

Устройство свободно

Фиг.7

fJcmcfHodKa запроса п/зя- I мого ffocmi/nif I

IZ0.3, 2,3 (ЗПД}I

&.«....,™,„.......-.:.:...

,.,..1 o/ffiff/GHue 7-5 .... fi-i I разрви е:н1 я

, g,n ,), „ у -; I „

Mir-: f.

-.L.:.,:,,:.Ji ,,,,,,,.,,,,.

г h-irifj/ioBKa noijm8epff-.9ef- im 1

j выдорки I

1,,.„..„,. ..„„ ,...„..

C(Jp6c 20.3 I

...,.:т,.,.,.« ,..Ч„.т,„-...,:„:а„:,..,,„й1|

-у (1ание

., / j / «лД с гс QcBoS 2(7. й-/,- f.Hm pspeucG

I сп1ано ч{а вмс/тпеннеко I с о с/по я 1-1 f.fя -u.aHpmcf - - .5

ОУмгн uf«fxy «U4ueu

Редактор Н. Тупица

Составитель С, Пестмал

Техред Г.Гербер Корректор И. Муска

Заказ 4637Тираж 671Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство управления периферийной системой | 1975 |

|

SU590724A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-23—Публикация

1984-05-24—Подача