экстремумов при произвольных начальных точках для функции вида f(x)

ГЛ (У п/

ZlC;x , где с, О - заданТ 11

яые коэффициенты,oi; R - показатели степени, Устрор ство содержит блок 1 задания параметров функции, генератор 2 тактовых импульсов, элементы 3, А, 5, 15, 20, 57 сравнения, блоки 6, 7, 16 памяти, логарифмический преобразователь 8, счетчики 9, 11 адреса, группу 10 элементов ИЛИ, умИзобретение относится к вычислительной технике и может быть использовано в автоматизированных системах управления.

Цель изобретения - расширение клас са решаемых задач геометрического программирования,

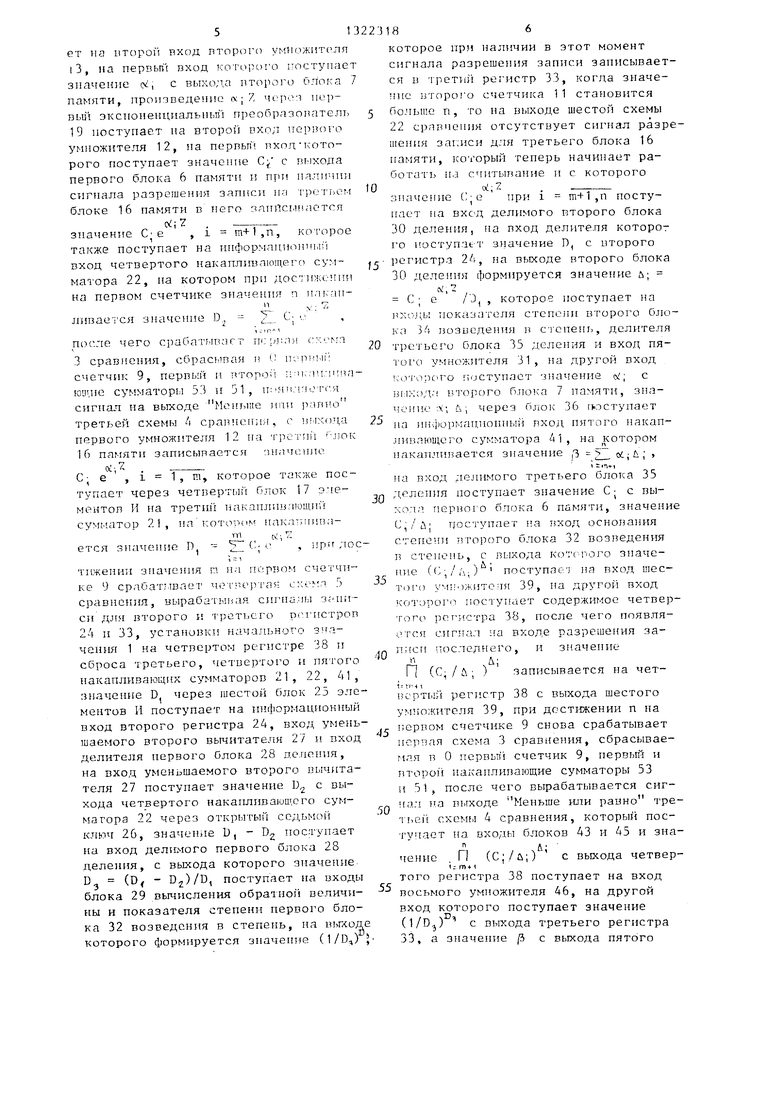

На чертеже представлена структурная схема устройства.

Устройство содержит блок 1 задания параметров функции, генератор 2 тактовых импульсов, элементы 3-5 сравнения, блоки 6 и 7 памяти, логарифмический преобразователь 8, первый счетчик 9 адреса, группу 10 элементов ИЛИ, второй счетчик 11 адреса, первый умножитель 12, второй умножи- гель 13, nepBbiii регистр 14, элемент 15 сравнения, третий блок 16 памяти, четвертьш блок 17 элементов И, пятый блок 18 элементов И, первый экспоненциальный преобразователь 19, элемент 20 сравнения, третий накапливающий сумматор 21, четвертый накапливающий сумматор 22, первый элемент 23 задержки, второй регистр 24, шестой блок 25 элементов И, седьмой блок 26 элементов И, второй вычитатель 27, первый блок 28 деления, блок 29 вычисления обратной величины, второй блок 30 деления, пятый умножитель 31, первый блок 32 возведения в степень, третий регистр 33, второй блок 34 возведения в степень, третий блок 35 деления восьмой блок 36 элементов И, второй элемент 37 задержки, четвертый регистр 38, шестой умножитель 39, третий элемент 40 задержки, пятый накапножители 12, П, 31, 39, А4, 6, А7, регистры 14, 24, 33, 38, блоки 17, 18, 25, 26, 36, 43, 45, 54, 56, 58, 60 элементов И; экспоненциальные преобразователи 19, 48, накапливающие- сумматоры 21, 22, 41, 51, 53, элементы 23, 37, 40 задержки, вычитатели 27, 42, 59, блоки 28, 30, 35, 50, 55 деления, блок 29 вычисления обратной величины, блоки 32, 34 возведения в степень, обэатный логарифмический преобразователь 61. 1 ил.

ливающий сумматор 41, третий вычитатель 42, девятый блок 43 элементов И седьмой умножитель 44, десятый блок 45 элементов И, восьмой ум11ожитель 46, девятый умножитель 47, второй экспонециальный преобразователь 48, четвертый умножитель 49, четвертый блок 50 деления, второй накапливающий сумматор 51, третий умножитель 52, первый накапливающий сумматор 53 второй е5лок 54 элементов И, пятый блок 55 деления, первый блок 56 элементов И, элемент 57 сравнения, одиннадцатый блок 58 элементов И, первый вычислитель 59, третий блок 60 элементов И, и обратный логарифмический преобразователь 61,

В устройстве реализуется метод наискорейшего спуска, учитывающий специфику рассматриваемой задачи, которая относится к классу геометрического программирования.

Минимизируемая функция задается в виде:

oi;

С.

1, X ,

(1)

11С;Х

oi; е R , i 1 , п объем выборки;

объем выборки с положительными коэффициентамиi весовой коэффициент; коэффициент показателя степени;

аргумент функции, е преобразования Z 1пх

П}

oi;

i:C;e - С,е

с.:, Z

(2)

313223184

Итераци -нный поиск экстремума cot- В силу монотонности функции t тоит из трех этапов. На первом этапе решение задачи (5) равносильно решев текущей точке Z ° функция (2) ап- проксимируетсяг позиноминальной, т.е. функцией аналогичного вида, но с по- 5 ложительными коэффициентами С;. Ззда- ча минимизации функции (2) эквивалентна следующей оптимизационной задаче: найти

нию задачи: найти

у m

МИН t

1 ei, С.е

которая имеет то же решение, что и задача: найти

мин

of-. Z

(6)

v 2 е 6 t

(3)

с - вспомогательная переменная, причем имеет строго положительное значение, этого можно добиться прибавив к f(k) достаточно большую константу. окрестности точки правая

/5

fi.(Z ° )

Заключ определен i вдоль пользован

ь ограничения (3) аппроксимирует- 20 мации (6) Для этого вычисляются веса Dj,

i m+1,п по формулам

/

Л; С;е

г

°)

/D,, i m+1,n

(D, - D,)/D, ; D,

к 1

(V 2

и заменяется правая часть ограничения (3) выражением

У./

(4)

л;

М (I/Dp . П (С; /Д,)

И

( ,11 ос; й-,;

Данная аппроксимация равносильна разложению в ряд Тейлора функции

. X (О) ln(t + 2 С е ) в точке (t ,

по степеням Int, Z с оставлением ли- . нейной части.

Поделив обе части аппроксимированного ограничения (3) на выражение

М е

ftZ

В начальном состоянии на первом счетчике 9 адреса установленного значения М, на третьем и четвертом накап ливающих сумматорах 21 и 22 и на втором счетчике 11 адреса установлено значение О. С выхода значений весового коэффициента, коэффициента показателя степени блока 1 задания параметров функции, значения С; и заносят ся соответственно в первый и второй блоки 6 и 7 памяти. С выхода аргумента функции блока 1 значение х через логарифмический преобразователь 8 и группу 10 элементов ИЛИ поступает на

получается следующая оптимиза-vi 1 ./

- первый регистр 14. ционная задача: найти

Устройство начинает работу при

-- (3)

нератора 2 тактовых импульсов, тактиei;

МИН t, Ц С;е

| 1

где С| С;/Mi

ос| о(;-р ;

i 1,m.

t

55

появлении сигнала на входе Пуск генератора 2 тактовых импульсов, тактирующие импульсы с выхода которого пос тупают на счетные входы первого и второго счетчиков 9 и 15 адреса, увеличивая их значение на 1, значение Z с выхода первого регистра 14 поступанию задачи: найти

у m

МИН t

1 ei, С.е

которая имеет то же решение, что и задача: найти

мин

of-. Z

(6)

7(0

Ha втором этапе в текущей точке

Z определяется направление спуска (антиградиент) функции (6)

. |°1

fi.(Z ° ) - 51

.(«li S

(7)

Заключительным этапом является определение оптимальной величины шага i вдоль выбранного направления с использованием квадратичной аппрокси

oi;

06;2

()

(8)

to)

25

и получение очередной точки итерации по формуле

А. 5; (

(9)

Итерационный процесс продолжается до получения решения, критерием останова является условие

- .6

ьна и

40

}

ли- .

оване

где - заданная точность вычислений.

Устройство работает следующим об- 35 разом.

В начальном состоянии на первом счетчике 9 адреса установленного значения М, на третьем и четвертом накапливающих сумматорах 21 и 22 и на втором счетчике 11 адреса установлено значение О. С выхода значений весового коэффициента, коэффициента показателя степени блока 1 задания параметров функции, значения С; и заносятся соответственно в первый и второй блоки 6 и 7 памяти. С выхода аргумента функции блока 1 значение х через логарифмический преобразователь 8 и группу 10 элементов ИЛИ поступает на

иза-vi 1 ./

нератора 2 тактовых импульсов, такти

появлении сигнала на входе Пуск генератора 2 тактовых импульсов, тактирующие импульсы с выхода которого поступают на счетные входы первого и второго счетчиков 9 и 15 адреса, увеличивая их значение на 1, значение Z с выхода первого регистра 14 поступа51

ет на пторой вход пторсп о ум южитсля |3, на первьп вход К отор ого поступае значение (У, с выхо;1а лтороги блока памяти, произведение к; Z чороп иер- Bbiii экспоненциальный преобразователь 19 поступает на BTOPOI I вход iiepnovo умножителя 12, на перпьп яход кото- рого поступает значение С/ с выхода первого блока 6 памяти и при наличии снгнада разрешения записи н-п Г1),ем блоке 16 памяти в него запПсыпается

cei7 .

значение С е , L m+1,n, которое

также поступает на 1П1формап,1 он11ы:1 вход четвертого накапливающего сум- мач ора 22, па котором при достили/ипи на первом счетчике п илк-ан11 Ч : г дивае1 ся значение D, - С; е

пос.ле чего срабатывает не .л:,ч я с Х . мп 3 сравнения, сбрас1,шая п (- п-.чи-п. счетч1пс 9, первый и пторо i n,-;iu:ii Ra юи пе сумматоры 53 и 31, п; И11; Г).г1т.я сигнал па выходе MoHj,riie ипи равно третьей схемы А сравнении, с выхода первого умноясителя 12 на третпГ 16 памяти записывается значение

Qi;

С- е ,, т, которое также поступает через четвертый блок 17 элементов И на трети накаплиБа ош,и; сумматор 21, на котог1(1м нак.-гплипается значение D.

при ;тос Ю

тпжении зна чения гл на пгфвом счетчике 9 срабатывает чеч и р1 ая 5 35 сравнения, вырабатывая сигналы з; пиСИ для второго I TpCTljCrO рРТ ИСТрОВ

24 и 33, установки начального значения 1 на четвертом регистре 38 и сброса третьего, четвертого и пятого накапливающих сумматоров 21, 22, А1, :значе1И е D через шестой блок 25 элементов II поступает на информационный вход второго регистра 24, вход уменьшаемого второго вычитателя 27 и вход - делителя первого блока 28 деления, иа вход уменьшаемого второго вычитателя 27 поступает значение 1) с выхода чет вертого накапливающего сум- Nsaropa 22 через открытый седьмо клич 26, значение D, - Dg иос.т упает на вход делимого первого блока 28 деления, с выхода которого значение DJ (DI - D2)/D, поступает па входы блока 29 вычислепия o6painoii величи ны и показателя степени первого блока 32 возведения в степень, на выходе

й

.- 55

ние ((. ,/() поступает на вход ше того )житeли 39, на другой вход KOTupoi o поступает содержимое четв того регистра 38, после чего появл ется на входе разрешения за писи последнего, и значение

п Л;

П (с, /U ; ) записывается на чет

1- 1 Ч

верты; регистр 38 с выхода шестого умножителя 39, при достижении п на первом счетчике 9 снова срабатывае первая схема 3 сравне1И1я, сбрасыва мая в О первьп счетчик 9, первьй и второй накапливающие сумматоры 53 и 51, после чего вырабатывается си нал на выходе Меньше или равно т I iiBii схемы 4 сравнения, который по тупает на входы блоков 43 и 45 и з

пЛ

чение , П (С;/й;) с выхода четв

1:: т+ 1

ТОГО регистра 38 поступает на вход восьмого умножителя 46, на другой вход которого поступает значение (1/D) с выхода третьего регистр

которого формируется значение (1/D,) 33, а значение /3 с выхода пятого

223

5 О

jj- .,„ 25

30

Ю

35

-

55

186

которое при наличии в этот момент сигнала разрешения записи записывается в TpeTiiii регистр 33, когда значение второго счетчика 11 становится больше п, то на выходе шестой схемы 22 сравнения отсутствует сигнал разрешения заг:иси для третьего блока 16 памяти, который теперь начинает работать н,;1 считывание и с которого

cY; 4.

значение ( е при i m+1,n поступает на вход делимого второго блока 30 деления, на вход делителя которого HocTynatT з ачение П, с второго регистра 24, на выходе второго блока 30 деления формируется значение &

tv;, С; е / J, , которое поступает на .цы показателя степени второго блока 34 возведения в стеиен ;, дел1-ггеля третьего блока 35 деления и вход пятого умножителя 31, на другой вход Tavi-opciro г;иступает значение о,;; с выхода второго блока 7 памяти, зна- т-.:еиие л; Ь; через блок 36 г эступает на )орГ .ап,попиый вход пятого накап- .пивающего сумматора 41, на котором накапливается значение С(;

на вход де:и1мого третьего блока 35 деления поступает значение С; с вы- кола. первого блока 6 памяти, значение С, / поступает на вход основа)1ия степени тггорого блока 32 воз едения Б степень, с выхода KoTC i oro значе

ние ((. ,/() поступает на вход шестого )житeли 39, на другой вход KOTupoi o поступает содержимое четвертого регистра 38, после чего появляется на входе разрешения записи последнего, и значение

п Л;

П (с, /U ; ) записывается на чет1- 1 Ч

верты; регистр 38 с выхода шестого умножителя 39, при достижении п на первом счетчике 9 снова срабатывает первая схема 3 сравне1И1я, сбрасываемая в О первьп счетчик 9, первьй и второй накапливающие сумматоры 53 и 51, после чего вырабатывается сигнал на выходе Меньше или равно тре- I iiBii схемы 4 сравнения, который поступает на входы блоков 43 и 45 и знапЛ

чение , П (С;/й;) с выхода четвер1:: т+ 1

ТОГО регистра 38 поступает на вход восьмого умножителя 46, на другой вход которого поступает значение (1/D) с выхода третьего регистра

33, а значение /3 с выхода пятого

)0

накапливающего сумматора 41 череа девятый ключ ДЗ,поступает на вход вычитаемого третьего вычитателя 42 и вход седьмого умножителя 44, на другой вход которого поступает знача- с, ние Z с вьгхода первого регистра 14, значение ftZ поступает через второй экспоненциальный преобразователь 48 па вход девятого умножителя 47, на

другой вход которого поступает знап fi д; чение М (1/Д,) П /С; / Л; ) , на

i-ni+ i

вход уменьшаемого третьего В 1читате- ля 42 поступает значение с выхода в торого блока, 7 памяти, значение (yf I 0;; -р с выхода третьего умножителя 42 поступает на вход делимого четвертого блока 50 деления, на вход делителя которого поступает значение Me с выхода девятого умножителя 47, на выходе четвертого умножителя

ние оптимальной точки поступает пя вход обратного лoгapифм гчecкoгo преобразователя 61 и через него на выход устройства, иначе появляется сигнал па выходе Меньше или равно второй схемы 57 сравнения, и значение при- рашения аргумента постуг ает на вход вычитаемого первого вычитателя 59 и через него при нал1гчии сигнала записи с выхода второй схемы 57 сравнения записывается в первый регистр 14, и итерационньп пропесс повторяется .

(5

Формула изобретения Устройство для нахождения зкстре20

49 формируется значение С ./М х

о

X е , которое поступает на второй накапливающий сумматор 51, где накапf о

Ic.:.(у

(где

, содержащее задания параметров функции, генератор тактовьк импульсов, первый счетчик адреса, первый и второй блоки памяти, два элемента сравнения, первый вычитатель, перш,и регистр, логарифмический пре- г1Г разователь, группу элементов ИЛИ, 25 с псрпог о по третий блоки элементов И, с первого по пятый тиножители, первьп и второй накапливающие сумматоры, блок вычисления обратной величины, первый экспоненпиальный преобразователь, обратньпТ логарифмический преобразователь, вход запуска 1 енератора тактовых импульсов является входом запуска устройства, выходы значений весового коэффициента, коэф,., фициент показателя степени, объема

пает значение 2п. при достижении это- 35 ,.

выборки, точности вычисленш и аргуливается значение

/

С С;/М, ос, oi; - /3 ) и через третий умножитель 52 на первый накапливающий сумматор 53, где накапливается

: I ai ; tJ , ; 30 значение е (где С

С /М, -к; -р), с выхода значения количества циклов вычислений блока 1 на вход пятой схемы сравнения постуго значения на втором счетчике 11 срабатывает пятая схема 15 сравнения, сбрасывая второй счетчик 11 в О, накопленное на первом накапливающем

1 , ,2 Od ; 2

51 С, fi е

сумматоре 53 значение

мента функции блока задания параметров функции подключены соответственно к информационным входам первого

лп и второго блоков памяти к первым входам первого и второго элементов сравнения и к входу логарифмического преобразователя, выход генератора тактовых импульсов подключен к счетному

поступает на вход делителя пятого блока 55 деления, на вход делимого

которого

С Od ;

поступает 2

значение

через второй

54с выхода второго накапливающего сумматора 51, на вьсходе пятого блока

55деления формируется приращение аргумента, которое поступает на вход второй схемы 57 сравнения, на другой вход которой поступает значение Е с выхода точности вычислений блока 1, при выполнении условия / Z - Z /,c появляется сигнал на выходе Больше схемы 57 сравнения, вырабатывая сигнал останова для генератора 2 тактовых импульсов и через блок 60 эначе)0

с,

223188

ние оптимальной точки поступает пя вход обратного лoгapифм гчecкoгo преобразователя 61 и через него на выход устройства, иначе появляется сигнал па выходе Меньше или равно второй схемы 57 сравнения, и значение при- рашения аргумента постуг ает на вход вычитаемого первого вычитателя 59 и через него при нал1гчии сигнала записи с выхода второй схемы 57 сравнения записывается в первый регистр 14, и итерационньп пропесс повторяется .

(5

Формула изобретения Устройство для нахождения зкстре20

25

(где

мента функции блока задания параметров функции подключены соответственно к информационным входам первого

и второго блоков памяти к первым входам первого и второго элементов сравнения и к входу логарифмического преобразователя, выход генератора тактовых импульсов подключен к счетному

ВХОДУ первого счетчика адреса, выход которого подключен к адресным входам первого и второго блоков памяти и к второму входу первого элемента сравнения, выход первого блока памяти подключен к первому входу первого умножителя, второй вход которого подключен через первьш экспоненциальный преобразователь к выходу второго умножителя, выход второго блока памяти

подключен к первому входу второго умножителя, выход третьего умножителя соединен с информационным входом первого накапливающего сумматора, выход которого подключен к первому вхо91

ду псфнот о блока Э темсп |-г:п И, перного пьгч11тателя поакчк юп к перпьтм входам элементоп ИЛИ rpvriiir., BTopj ie входы которых подключены к пь:ходу логарифмического преобразонателя, выхо- ды элементов 1ШИ группы подключены к информационному тзходу первого регистра, Бькод которого подключен к второму входу второго умполштеля, первому входу трет1 его блока тов И и к входу уг еиьшаемого первого вычитателя, выход четвертог о умножителя подключен к пнформ;1циоиному входу второго накап1пшаюп ;е1 о су 1мато1 а, выход которого гюдключон i: пг;шому

входу второго блока элег- ентов И, выход Ьолыне второго элемеи ivi cpaiJHC- нпя подключен к втор ;-- У вхоп.у третьего блока элемена ов И, (:)д которого по.цключен к входу обратного логариф- мического преобразователя, ныход ко- тор(1го Я1зляется выхолом ycTixiiicTBa , о т л и ч а К) 1Ц е е с я чем, что, с .целг.ю расшпренпя класса рс ;1а ;м1лх задач геометрического програ 1мирсл а- ПИЯ, в пего введены тре л И1 блик па- r-fHTii, BTopoi i счетчик адреса, с тре- по usecTof i элементь.т сравнения, г; шестого по умнплпгголп, с второго по четверть регистры, с i-icT- вертого по о/динпалда. блоки элемен- i Qii 1, Fri opofT ;,M;ci;ni;cH; ,Ti:i;iT)Hb:;i п)е- обра иимтель, с третье по пя гы накап.1 нп ающие суьг-иггорь, второй и тре в1 1читатели, пл1л/ бл(мсов леле пия, лна блока г.озвед1--пия в степень, три )j;eMeirra заде)жки, причем В л:;о71, эна- ч евия обт,ема 1Л,:бор1Си блок а : адания парамет ров :|) 1и-л;ии подкл пчен к первому входу lu ecToro о.чемснта сравнения выхо;1 1значени.я ко.пичсства пп:.:Л(В вы- числени блока за/дапия парамеч ров 1)ункдии подключеп к первому B/Lony пя- Toi o элемента сравнения, выход лначе- ния объема ыборки с положи гелтлсыми Tco3(ji l innienTa;-ni блока зад.аш И 1- етров функдии подкл)очен к перв.ь;м входа.м третьего и четвертоп олемен- срапне шя, 1 1;1Х1)д Равно Tijro элемента сравверщя подк. почен к вхолу первог о элемента задержки, пер- BixM го:од, шестого и сед,мого элемент(1в И, входам раз 1е1чени-я записи второго и третьего регистгиг и через т1)етиГ: элеметгг задержки к вхо- дам установки в ноль пятого накагип - вающего сумматора TI начади,nofi установки четвертого реги.с7 г;а, вылол, ге- шфатора такт(1вых имчулт-гоп 11: - ключен

18 10

1C счетному входу второго счетчика адреса, выход первого счетчика адреса под.ключен к вторым входам третьего и четвертого элементов сравнения и адресному входу третьего блока памяти, вход разрешения записи которого подключен к выходу Меньше или равно шестого элемента сравнения, выход авно первого элемента сравнения подключен к входам установки в ноль первого, второго накапливающих сумматоров и первого счетчика адреса, . выход второго счетчика адреса подключен к вторым входам шестого и пятого элементов сравнения, выход Равно пятого элемента сравнения подключен к вторым входам первого и второго блоков элементов И и к входу установки в }1оль второго счетчика адреса, выход первого умножителя подключен к инфopмaпиo rным входам третьего блока памяти, первым входам, пятого и четвертого блоков элементов И, вто- poii вход четвертого блока элементов И, первые входы девятого и десятого блоков элементов И подключены к выходу Меньше или равно третьего элемента сравнения, выход Больше которого подключен к второму входу пятого блока элементов И и первому входу восьмого блока элементов И и через второй элемент задержки к входу разрешения заппси четвертого регистра, выхо.д которого подключен к первому входу десятого блока элементов И и первому входу шестого умножителя, выход которого подключен к информационному входу четвертого регистра, а второй вход - к выходу второго блока возведения в степень, вход основания степени которого подключен к выходу третьего блока деления, вход де.чпмого которого подключен, к выходу первого блока памяти, выходы четвертого и пятого блоков элементов И подключены соответственно к информационным входам третьего и четвертого накапливающих сумматоров, входы уста- повки в ноль которых подключены к выходу первого элемента задержки, выходу третьего и четвертого накапливаю- 1ЦПХ сумматоров подключены соответственно к вторым входам шестого и седьмого блоков элементов И, выход шестого блока элементов И подключен к ин- формадиопному входу второго регистра входу уменьшаемого второго вычитателя и входу делителя первого блока деления , вход делимого которого подключен

1113223

к выходу второго вычитателя, вход вычитаемого которого подключен к выходу седьмого блока элементов И, выход первого блока деления подключен к входу, показателя степени и через блок вычи- сления обратной величины к входу основания степени первого блока возведения в степень, выход которого подключен к информадионному входу третьего регистра, выход которого подключен к пер- tO вому входу восьмого умножителя, второй вход которого подключен к выходу десятого блока элементов И, выход третьего блока памяти подключен к первому входу четвертого умножителя и 15 входу делимого второго блока деления, вход делителя которого подключен к выходу второго регистра, выход второго блока деления подключен к входу показателя степени второго блока воз- 20 ведения в степень, входу делителя третьего блока деления и первому входу пятого умножителя, выход которого подключен к второму входу восьмого блока элементов И, выход которого под- ключен к информационному входу пятого накапливающего сумматора, виход которого подключен к второму входу девятого блока элементов И, выход которого подключен к входу вычитаемого 30 третьего вычитателя и первому входу седьмого умножителя, второй вход котоРедактор Н.Рогулич

Заказ 2867/47Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

1812

рого подключен к выходу первого регистра, а выход через второй экспонен циальный преобразователь - к первому входу девятого умножителя, второй вход которого подключен к выходу восьмого умножителя, а выход - к входу делителя четвертого блока деления, выход которого подключен к второму входу четвертого умножителя, выход которого подключен к первому входу третьего умножителя, выход второго блока памяти подключен к второму входу пятого умножителя и входу уменьшаемого третьего вычитателя, выход которого подключен к входу делимого четвертого блока деления и второму входу третьего умножителя, выход второго ключа подключен к входу делимого пятого блока деления, вход делителя которого подключен к выходу первого блока элементов И, а выход - к первому входу одиннадцатого блока элементов И и второму входу второго элемента сравнения, выход Меньше или ра-вно которого подключен к входу разрешения записи первого регистра и второму входу одиннадцатого блока элементов Н, выход которого подключен к входу вычитаемого первого вычитателя, выход Больше второго элемента сравнения подключен к входу останова генерато- . ра тактовых импульсов.

Составитель В.Орлов Техред Л.Олийиык

Корректор А.Тяско

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для нахождения координаты экстремума функции | 1988 |

|

SU1603399A1 |

| Устройство для нахождения экстремумов | 1985 |

|

SU1287180A1 |

| Устройство для нахождения экстремума функции | 1985 |

|

SU1287182A1 |

| Устройство для нахождения экстремума аддитивной функции многих переменных | 1990 |

|

SU1765830A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ПОТЕРЬ В ТРАНСФОРМАТОРЕ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2014 |

|

RU2563331C1 |

| Устройство для нахождения экстремумов функции | 1984 |

|

SU1205156A1 |

| СЧЕТЧИК ПОТЕРЬ АКТИВНОЙ ЭЛЕКТРОЭНЕРГИИ В ТРАНСФОРМАТОРЕ | 2015 |

|

RU2589498C1 |

| СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 1992 |

|

RU2022356C1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1986 |

|

SU1325508A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах управления. Цель изобретения - расширение класса решаемых задач геометрического программирования. Устройство обеспечивает нахождение (Л оо го Ю 00 00 баноЗ

| Устройство для определения экстремумов | 1977 |

|

SU736111A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1982 |

|

SU1205136A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-27—Подача