Изобретение относится к импульсной технике и может быть использовано в технике генерирования и использования сложных сигналов.

Целью изобретения является повышение стабильности формирования псевдослучайной последовательности.

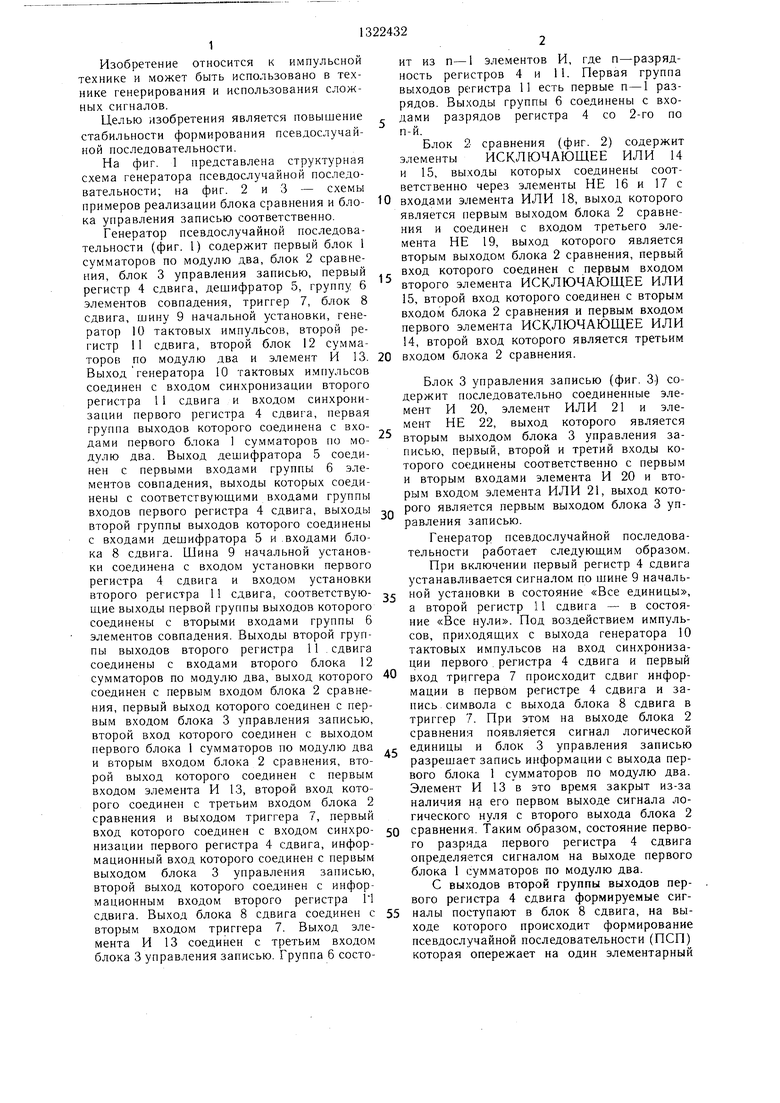

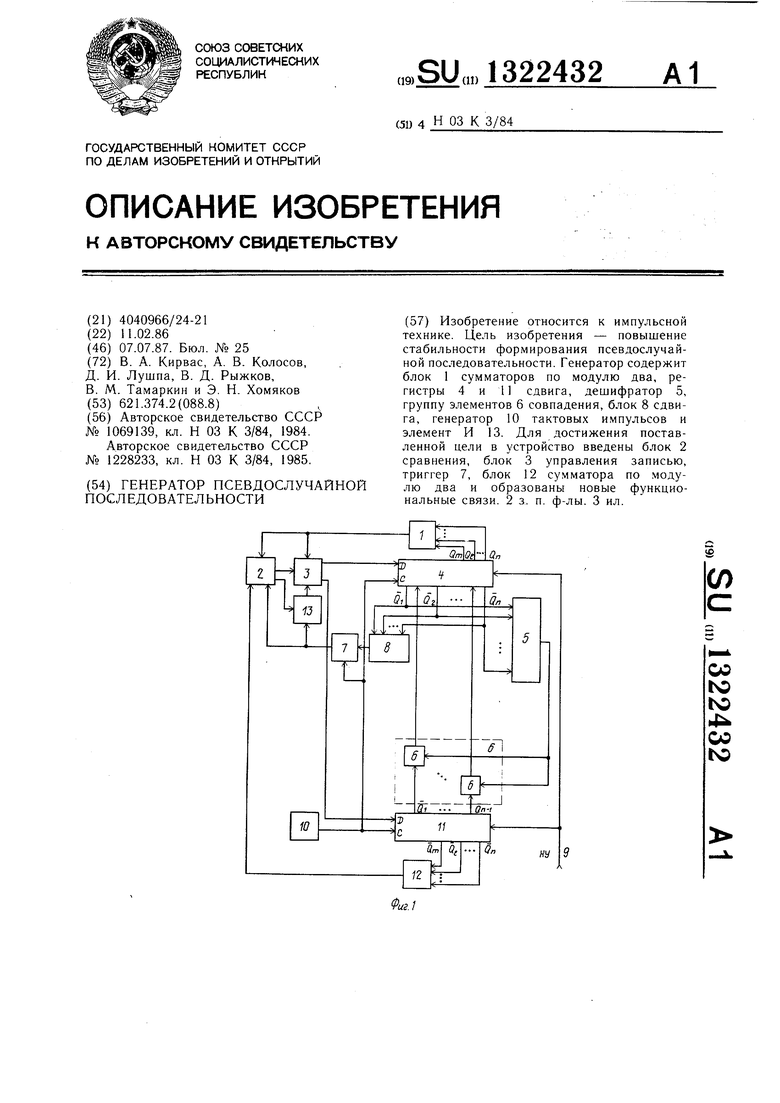

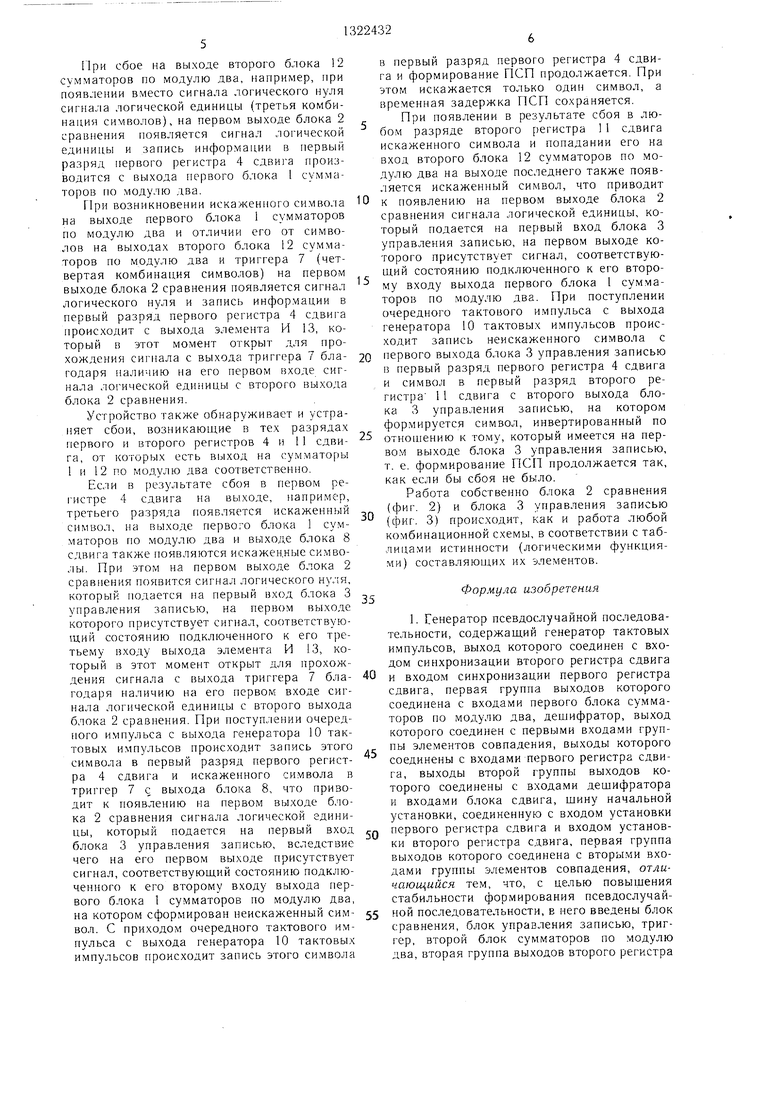

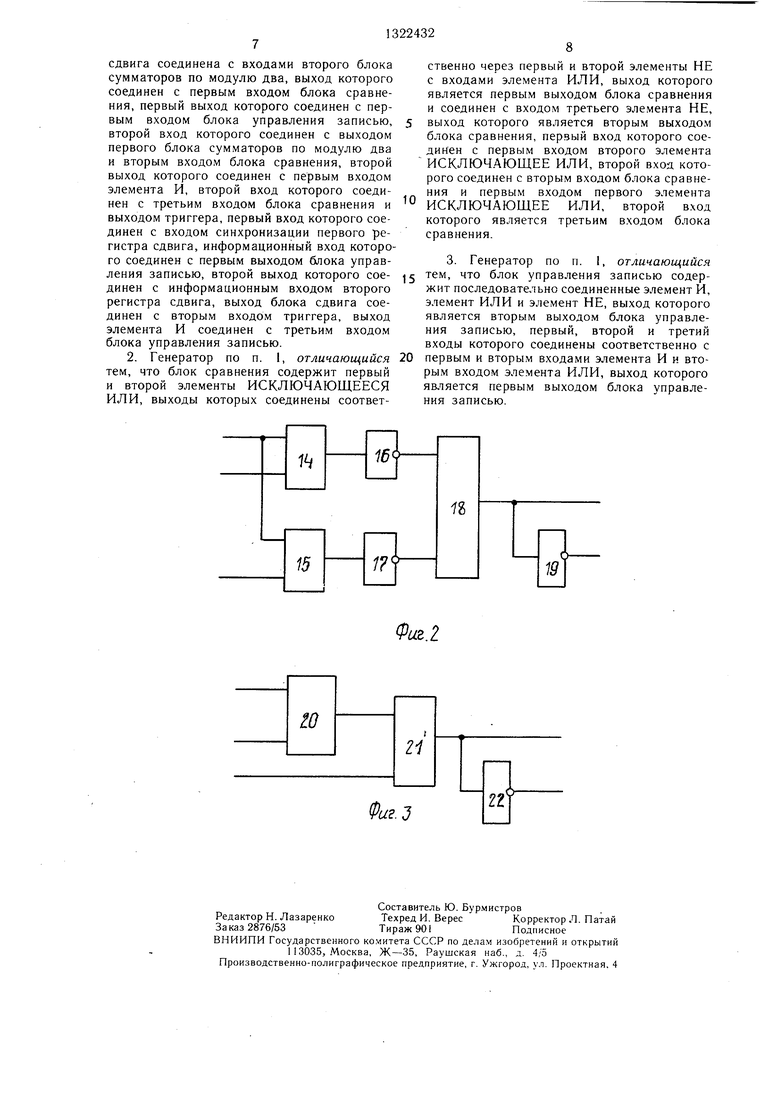

На фиг, 1 представлена структурная схема генератора псевдослучайной последовательности; на фиг. 2 и 3 - схемы

ит из п-1 элементов И, где п-разрядность регистров 4 и 11. Первая группа выходов регистра 11 есть первые п-1 разрядов. Выходы группы 6 соединены с входами разрядов регистра 4 со 2-го по п-й.

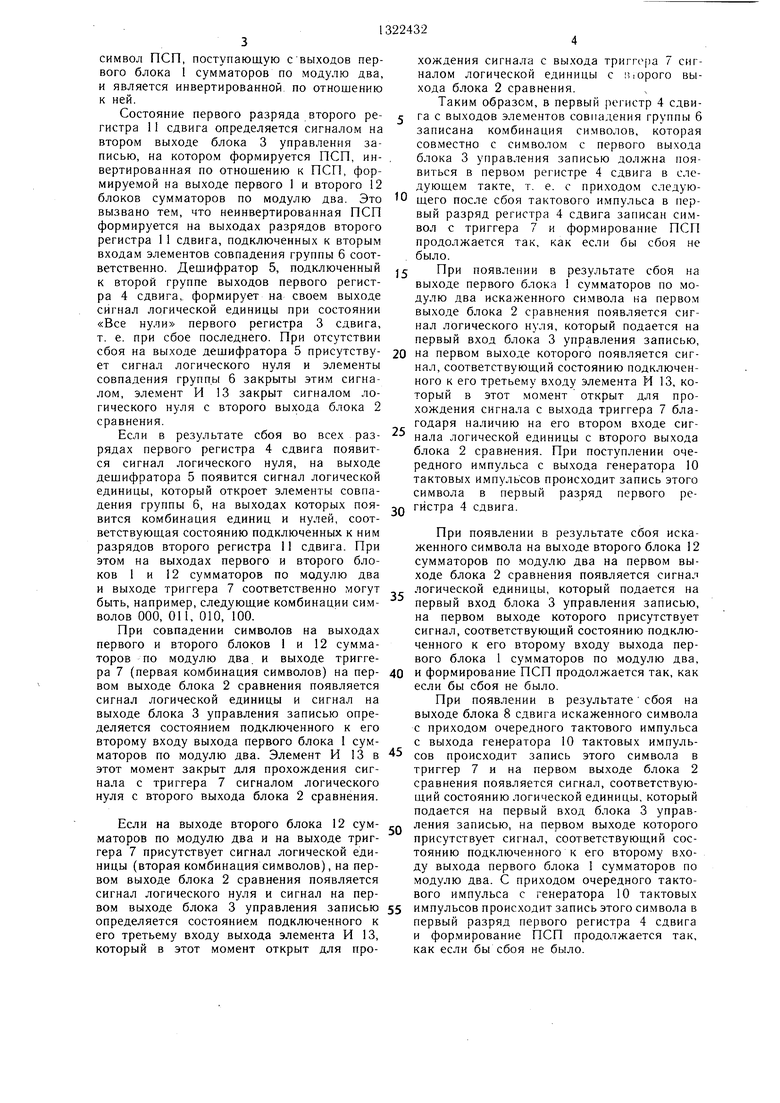

Блок 2 сравнения (фиг. 2) содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и 15, выходы которых соединены соответственно через элементы НЕ 16 и 17 с

примеров реализации блока сравнения и бло- Ю входами элемента ИЛИ 18, выход которого ка управления записью соответственно.является первым выходом блока 2 сравнения и соединен с входом третьего элемента НЕ 19, выход которого является

Генератор псевдослучайной последовательности (фиг. 1) содержит первый блок 1 сумматоров по модулю два, блок 2 сравневторым выходом блока 2 сравнения, первый

ния, блок 3 управления записью, первый . вход которого соединен с первым входом регистр 4 сдвига, дешифратор 5, группу 6 второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ элементов совпадения, триггер 7, блок 8 15, второй вход которого соединен с вторым сдвига, шину 9 начальной установки, гене- входом блока 2 сравнения и первым входом ратор 10 тактовых импульсов, второй ре- первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ гистр 11 сдвига, второй блок 12 сумма-14, второй вход которого является третьим

торов по модулю два и элемент И 13. 20 входом блока 2 сравнения. Выход генератора 10 тактовых импульсов

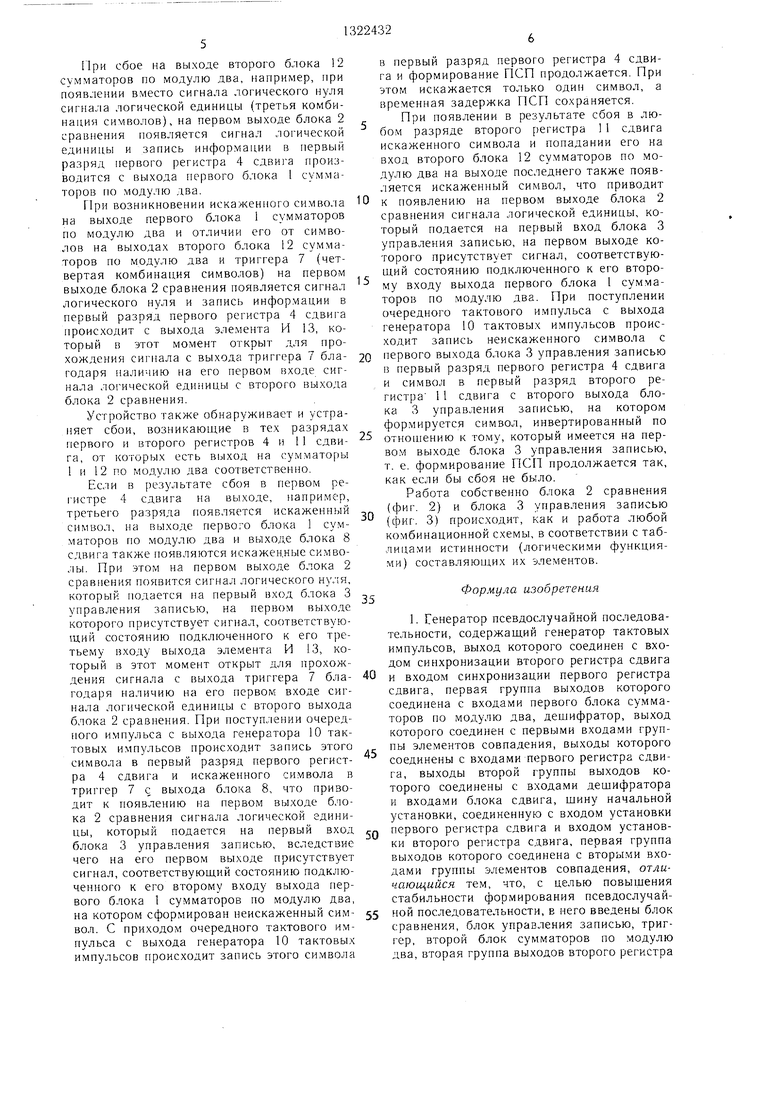

соединен с входом синхронизации второгоБлок 3 управления записью (фиг. 3) сорегистра 1 1 сдвига и входом синхрони- держит последовательно соединенные эле- зации первого регистра 4 сдвига, первая мент И 20, элемент ИЛИ 21 и эле- групна выходов которого соединена с вхо- мент НЕ 22, выход которого является дами первого блока 1 сумматоров по мо- вторым выходом блока 3 управления за- дулю два. Выход дешифратора 5 соеди- писью, первый, второй и третий входы коней с первыми входами группы 6 эле- торого соединены соответственно с первым ментов совпадения, выходы которых соеди- и вторым входами элемента И 20 и вто- нены с соответствуюшими входами группы рым входом элемента ИЛИ 21, выход кото- входов первого регистра 4 сдвига, выходы рого является первым выходом блока 3 уп- второй группы выходов которого соединены равления записью.

с входами дешифратора 5 и .входами бло-Генератор псевдослучайной последовака 8 сдвига. Щина 9 начальной установ-тельности работает следующим образом,

ки соединена с входом установки первогоПри включении первый регистр 4 сдвига

регистра 4 сдвига и входом установкиустанавливается сигналом по шине 9 начальвторого регистра 11 сдвига, соответствую- 5 ной установки в состояние «Все единицы, ш,ие выходы первой группы выходов которогоа второй регистр 11 сдвига в состояние «Все нули. Под воздействием импульсов, приходяш,их с выхода генератора 10 тактовых импульсов на вход синхронизации первого регистра 4 сдвига и первый вход триггера 7 происходит сдвиг информации в первом регистре 4 сдвига и запись символа с выхода блока 8 сдвига в триггер 7. При этом на выходе блока 2 сравнения появляется сигнал логической единицы и блок 3 управления записью разрешает запись информации с выхода первого блока 1 сумматоров по модулю два. Элемент И 13 в это время закрыт из-за наличия на его первом выходе сигнала логического нуля с второго выхода блока 2 вход которого соединен с входом синхро- 50 сравнения. Таким образом, состояние перво- низации первого регистра 4 сдвига, инфор-го разряда первого регистра 4 сдвига

определяется сигналом на выходе первого блока 1 сумматоров по модулю два.

С выходов второй группы выходов первого регистра 4 сдвига формируемые сиг- сдвига. Выход блока 8 сдвига соединен с 55 налы поступают в блок 8 сдвига, на вы- вторым входом триггера 7. Выход эле-ходе которого происходит формирование

мента И 13 соединен с третьим входомпсевдослучайной последовательности (ПСП)

блока 3 управления записью. Группа 6 состо-которая опережает на один элементарный

соединены с вторыми входами группы 6 элементов совпадения. Выходы второй группы выходов второго регистра 11 ,сдвига соединены с входами второго блока 12 сумматоров по модулю два, выход которого 40 соединен с первым входом блока 2 сравнения, первый выход которого соединен с первым входом блока 3 управления записью, второй вход которого соединен с выходом первого блока 1 сумматоров по модулю два и вторым входом блока 2 сравнения, второй выход которого соединен с первым входом элемента И 13, второй вход которого соединен с третьим входом блока 2 сравнения и выходом триггера 7, первый

мационныи вход которого соединен с первым выходом блока 3 управления записью, второй выход которого соединен с информационным входом второго регистра 11

45

ит из п-1 элементов И, где п-разрядность регистров 4 и 11. Первая группа выходов регистра 11 есть первые п-1 разрядов. Выходы группы 6 соединены с входами разрядов регистра 4 со 2-го по п-й.

Блок 2 сравнения (фиг. 2) содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и 15, выходы которых соединены соответственно через элементы НЕ 16 и 17 с

входами элемента ИЛИ 18, выход которого является первым выходом блока 2 сравневторым выходом блока 2 сравнения, первый

символ ПСП, поступающую с выходов первого блока 1 сумматоров по модулю два, и является инвертированной по отношению к ней.

Состояние первого разряда второго регистра 11 сдвига определяется сигналом на втором выходе блока 3 управления записью, на котором формируется ПСП, инвертированная по отношению к ПСП, формируемой на выходе первого 1 и второго 12 блоков сумматоров по модулю два. Это вызвано те.м, что неинвертированная ПСП формируется на выходах разрядов второго регистра 1 1 сдвига, подключенных к вторым входам элементов совпадения группы 6 соответственно. Дешифратор 5, подключенный к второй группе выходов первого регистра 4 сдвига, формирует на своем выходе сигнал логической единицы при состоянии «Все нули первого регистра 3 сдвига, т. е. при сбое последнего. При отсутствии сбоя на выходе дешифратора 5 присутствует сигнал логического нуля и элементы совпадения группы 6 закрыты этим сигналом, элемент И 13 закрыт сигналом логического нуля с второго выхода блока 2 сравнения.

Если в результате сбоя во всех разрядах первого регистра 4 сдвига появится сигнал логического нуля, на выходе дешифратора 5 появится сигнал логической единицы, который откроет элементы совпадения группы 6, на выходах которых появится комбинация единиц и нулей, соответствующая состоянию подключенных к ним разрядов второго регистра 11 сдвига. При этом на выходах первого и второго блоков 1 и 12 сумматоров по модулю два и выходе триггера 7 соответственно могут быть, например, следующие комбинации символов 000, 011, 010, 100.

При совпадении символов на выходах первого и второго блоков 1 и 12 сумматоров по модулю два. и выходе триггера 7 (первая комбинация символов) на первом выходе блока 2 сравнения появляется сигнал логической единицы и сигнал на выходе блока 3 управления записью определяется состоянием подключенного к его второму входу выхода первого блока 1 сумматоров по модулю два. Элемент И 13 в этот момент закрыт для прохождения сигнала с триггера 7 сигналом логического нуля с второго выхода блока 2 сравнения.

Если на выходе второго блока 12 сумматоров по модулю два и на выходе триггера 7 присутствует сигнал логической единицы (вторая комбинация символов), на первом выходе блока 2 сравнения появляется сигнал логического нуля и сигнал на первом выходе блока 3 управления записью определяется состоянием подключенного к его третьему входу выхода элемента И 13, который в этот момент открыт для про5

хождения сигнала с выхода тригго)а 7 сигналом логической единицы с liioporo выхода блока 2 сравнения.

Таким образом, в первый регистр 4 сдви5 га с выходов элементов совпадения группы 6 записана комбинация символов, которая совместно с символом с первого выхода блока 3 управления записью должна появиться в первом регистре 4 сдвига в следующем такте, т. е. с приходом следую 0 щего после сбоя тактового импульса в первый разряд регистра 4 сдвига записан символ с триггера 7 и формирование ПСП продолжается так, как если бы сбоя не было.

J5 При появлении в результате сбой на выходе первого блока 1 сумматоров по модулю два искаженного символа на первом выходе блока 2 сравнения появляется сигнал логического нуля, который подается на первый вход блока 3 управления записью,

0 на первом выходе которого появляется сигнал, соответствующий состоянию подключенного к его третьему входу элемента И 13, который в этот момент открыт для прохождения сигнала с выхода триггера 7 благодаря наличию на его втором входе сигнала логической единицы с второго выхода блока 2 сравнения. При поступлении очередного импульса с выхода генератора 10 тактовых импульсов происходит запись этого символа в первый разряд первого реп гйстра 4 сдвига.

При появлении в результате сбоя искаженного символа на выходе второго блока 12 сумматоров по модулю два на первом выходе блока 2 сравнения появляется сигнал логической единицы, который подается на первый вход блока 3 управления записью, на первом выходе которого присутствует сигнал, соответствующий состоянию подключенного к его второму входу выхода первого блока 1 сумматоров по модулю два,

0 и формирование ПСП продолжается так, как если бы сбоя не было.

При появлении в результате сбоя на выходе блока 8 сдвига искаженного символа с приходом очередного тактового импульса с выхода генератора 10 тактовых импуль5 сов происходит запись этого символа в триггер 7 и на первом выходе блока 2 сравнения появляется сигнал, соответствующий состоянию логической единицы, который подается на первый вход блока 3 управQ ления записью, на первом выходе которого присутствует сигнал, соответствующий состоянию подключенного к его второму входу выхода первого блока 1 сумматоров по модулю два. С приходом очередного тактового импульса с генератора 10 тактовых

5 импульсов происходит запись этого символа в первый разряд первого регистра 4 сдвига и формирование ПСП продолжается так, как если бы сбоя не было.

При сбое на выходе второго блока 2 сумматоров по модулю два, например, при появ:1епии вместо сигнала логического нуля сигнала логической единицы (третья комбинация символов), на первом выходе блока 2 сравнения появляется сигнал логической единицы и запись информации в первый разряд первого регистра 4 сдви1 а производится с выхода первого блока I сумматоров по модулю два.

При возникновении искаженного символа на выходе первого блока 1 сумматоров по модулю два и отличии его от символов на выходах второго блока 12 сумматоров по модулю два и триггера 7 (четвертая комбинация символов) иа первом выходе блока 2 сравнения появляется сигнал логического нуля и запись информации в первый разряд первого регистра 4 сдвига происходит с выхода элемента И 13, который в этот момент открыт для прохождения сигнала с выхода триггера 7 бла- годаря наличию на его первом входе сигнала логической единицы с второго выхода блока 2 сравнения.

Устройство также обнаруживает и устраняет сбои, возникающие в тех разрядах первого и второго регистров 4 и 11 сдвига, от которых есть на сумматоры 1 и 12 по модулю два соответственно.

Если в результате сбоя в нервом регистре 4 сдвига на выходе, например, третьего разряда появляется искаженный символ, на выходе первО;-о блока 1 сумматоров но модулю два и выходе блока 8 сдвига также появляются искаженные символы. При этом па первом выходе блока 2 сравнения появится сигнал логического ну.,, который подается на первый вход блока 3 управления записью, на первом выходе которого присутствует сигнал, соответствующий состоянию подключенного к его третьему входу выхода элемента И 13, который в этот момент открыт для прохождения сигнала с выхода триггера 7 благодаря наличию на его первом входе сигнала логической единицы с второго выхода блока 2 сравнения. При поступлении очередного импульса с вь1хода генератора 10 тактовых импульсов происходит запись этого символа в первый разряд первого регистра 4 сдвига и искаженного символа в триггер 7 с выхода блока 8, что приводит к появлению на первом выходе блока 2 сравнения сигнала логической единицы, который подается на первый вход блока 3 управления записью, вследствие чего на его первом выходе присутствует сигнал, соответствуюш,ий состоянию подключенного к его второму входу выхода первого блока 1 сумматоров по модулю два, на котором сформирован неискаженный сим- вол. С приходом очередного тактового импульса с выхода генератора 10 тактовых импульсов происходит запись этого символа

5

0 0

5

0

5

0

5

0

в первый разряд первого регистра 4 сдвига и формирование ПСП продолжается. При этом искажается только один символ, а временная задержка ПСП сохраняется.

При появлении в результате сбоя в любом разряде второго регистра 1 1 сдвига искаженного символа и попадании его на вход второго блока 12 сумматоров по модулю два на выходе последнего также появляется искаженный символ, что приводит к появлению на первом выходе блока 2 сравнения сигнала логической единицы, который подается на первый вход блока 3 управления записью, на первом выходе которого присутствует сигнал, соответствующий состоянию подключенного к его второму входу выхода первого блока 1 сумматоров по модулю два. При поступлении очередного тактового импульса с выхода генератора 10 тактовых импульсов происходит запись неискаженного символа с первого выхода блока 3 управления записью в первый разряд первого регистра 4 сдвига и символ в первый разряд второго регистра 11 сдвига с второго выхода блока 3 управления записью, на котором формируется символ, инвертированный по отно нению к тому, который имеется на первом выходе блока 3 управления записью, т. е. формирование ПСП продолжается так, как если бы сбоя не .

Работа собственно блока 2 сравнения (фиг. 2) и блока 3 управления записью (фиг. 3) происходит, как и работа любой комбинационной схемы, в соответствии с таблицами истинности (логическими функциями) составляюп их их элементов.

Формула изобретения

I. Генератор псевдослучайной последовательности, содержащий генератор тактовых импульсов, выход которого соединен с входом синхронизации второго регистра сдвига и входом синхронизации первого регистра сдвига, первая группа выходов которого соединена с входами первого блока сумматоров но модулю два, дегпифратор, выход которого соединен с первыми входами группы элементов совпадения, выходы которого соединены с входами первого регистра сдвига, выходы второй группы выходов которого соединены с входами дешифратора и входами блока сдвига, шину начальной установки, соединенную с входом установки первого регистра сдвига и входом установки второго регистра сдвига, первая группа выходов которого соединена с вторыми входами группы элементов совпадения, отличающийся тем, что, с целью повышения стабильности формирования псевдослучайной последовательности, в пего введены блок сравнения, блок управления записью, триггер, второй блок сумматоров по модулю два, вторая группа выходов второго регистра

сдвига соединена с входами второго блока сумматоров по модулю два, выход которого соединен с первым входом блока сравнения, первый выход которого соединен с первым входом блока управления записью, второй вход которого соединен с выходом первого блока сумматоров по модулю два и вторым входом блока сравнения, второй выход которого соединен с первым входом элемента И, второй вход которого соединен с третьим входом блока сравнения и выходом триггера, первый вход которого соединен с входом синхронизации первого регистра сдвига, информационный вход которого соединен с первым выходом блока управления записью, второй выход которого соединен с информационным входом второго регистра сдвига, выход блока сдвига соединен с вторым входом триггера, выход элемента И соединен с третьим входом блока управления записью.

10

ственно через первый и второй элементы НЕ с входами элемента ИЛИ, выход которого является первым выходом блока сравнения и соединен с входом третьего элемента НЕ, выход которого является вторым выходом блока сравнения, первый вход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с вторым входом блока сравнения и первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является третьим входом блока сравнения.

3. Генератор по п. I, отличающийся 5 тем, что блок управления записью содержит последовательно соединенные элемент И, элемент ИЛИ и элемент НЕ, выход которого является вторым выходом блока управления записью, первый, второй и третий

входы которого соединены соответственно с

2. Генератор по п. 1, отличающийся 20 первым и вторым входами элемента И и вто- тем, что блок сравнения содержит первый рым входом элемента ИЛИ, выход которого и второй элементы ИСКЛЮЧАЮЩЕЕСЯ является первым выходом блока управле- ИЛИ, выходы которых соединены соответ- ния записью.

ственно через первый и второй элементы НЕ с входами элемента ИЛИ, выход которого является первым выходом блока сравнения и соединен с входом третьего элемента НЕ, выход которого является вторым выходом блока сравнения, первый вход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с вторым входом блока сравнения и первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является третьим входом блока сравнения.

3. Генератор по п. I, отличающийся тем, что блок управления записью содержит последовательно соединенные элемент И, элемент ИЛИ и элемент НЕ, выход которого является вторым выходом блока управления записью, первый, второй и третий

19

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2276835C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство синхронизации с М-последовательностью | 1985 |

|

SU1312750A2 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2020766C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФАЗОВОГО СДВИГА ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1991 |

|

RU2013016C1 |

| Устройство для контроля ошибок воспроизведения информации с носителя магнитной записи | 1988 |

|

SU1527666A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2284668C1 |

| Дискретный согласованный фильтр | 1978 |

|

SU771891A2 |

Изобретение относится к импульсной технике. Цель изобретения - повышение стабильности формирования псевдослучайной последовательности. Генератор содержит блок 1 сумматоров по модулю два, регистры 4 и 11 сдвига, дешифратор 5, группу элементов 6 совпадения, блок 8 сдвига, генератор 10 тактовых импульсов и элемент И 13. Для достижения поставленной цели в устройство введены блок 2 сравнения, блок 3 управления записью, триггер 7, блок 12 сумматора по модулю два и образованы новые функциональные связи. 2 3. п. ф-лы. 3 ил. о: го ю . со ьо

| Генератор псевдослучайной последовательности импульсов | 1982 |

|

SU1069139A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Генератор псевдослучайной последовательности | 1984 |

|

SU1228233A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-11—Подача