Изобретение относится к радиоизмерительной технике и может использоваться в анализаторах ошибок (устройствах измерения верности передачи информации в цифровых трактах) при контроле каналов связи.

Детектор ошибок решает задачи:

а) формирования внутренней тест-последовательности;

б) синхронизации внутренней тест-последовательности с входной внешней тест-последовательностью;

в) выделения ошибок из входной тест-последовательности путем сравнения входной внешней и внутренней тест-последовательностей;

г) подсчета количества ошибок счетчиком ошибок.

Тест-последовательность подается на объект контроля, с которого поступает на анализатор ошибок, для проверки качества работы объекта контроля. В качестве тест-последовательности наиболее часто используется псевдослучайная последовательность (ПСП) максимальной длины (М-последовательность).

Известны устройства для детектирования ошибок [1], в которых используются систематические свойства М-последовательностей, которые позволяют достаточно точно проводить измерение количества ошибок. Всю работу таких устройств при каждой попытке входа в режим синхронизации можно разбить на три этапа: установка начального состояния, запись информации и проверка отсутствия ложной синхронизации. При успешной попытке входа в режим синхронизации устройство начинает свою основную работу - детектирования и анализа потока ошибок. За счет определения факта ложной синхронизации устройства и запрещения его работы (запрещения счета ошибок) на время, необходимое для повторной синхронизации, повышается точность измерений, так как при этом запрещается регистрация ошибок, в число которых могут входить ошибки, появившиеся на входе счетчика ошибок в результате ложной синхронизации устройства и отсутствующие во входной последовательности. Затраты времени на проверку отсутствия ложной синхронизации и (в случае необходимости) повторную синхронизацию устройства составляют 3n тактовых интервалов, где n - число разрядов (длина) регистра сдвига, в который производится запись входной информации.

Недостатком таких устройств является недостаточная помехоустойчивость - невозможность синхронизации при приеме входной внешней М-последовательности с максимальным средним по времени коэффициентом ошибок  , так как если на этапах записи информации или проверки отсутствия ложной синхронизации во входной внешней М-последовательности будет присутствовать хотя бы одна ошибка (в каком-либо из n битов информации), то такие устройства (детекторы ошибок) будут возвращаться в исходное начальное состояние, при этом подсчет ошибок производиться не будет.

, так как если на этапах записи информации или проверки отсутствия ложной синхронизации во входной внешней М-последовательности будет присутствовать хотя бы одна ошибка (в каком-либо из n битов информации), то такие устройства (детекторы ошибок) будут возвращаться в исходное начальное состояние, при этом подсчет ошибок производиться не будет.

В качестве прототипа принята более помехоустойчивая и точная схема устройства для детектирования ошибок, описанная в [2].

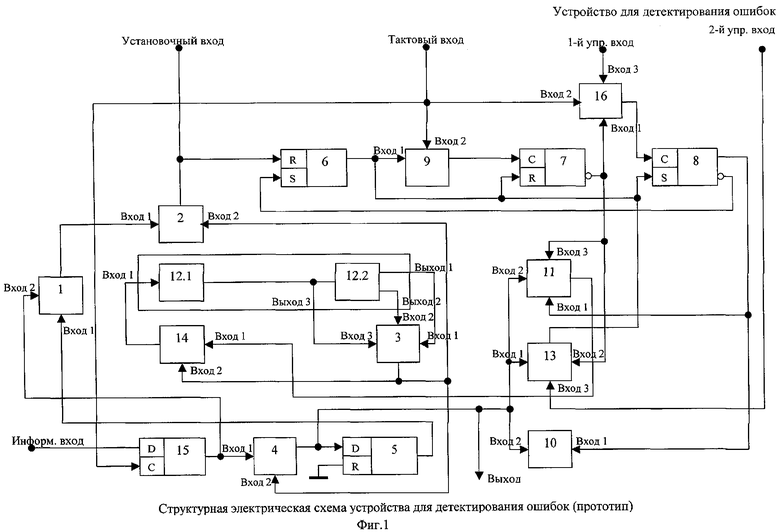

Данная схема содержит первый 1, второй 2, третий 3, четвертый 14 сумматоры по модулю два (СМД), компаратор 4, первый 5, второй 6, третий 7, четвертый 8, пятый 15 триггеры, первый 9, второй 10, третий 13, четвертый 16 счетчики, элемент "И" 11, регистр сдвига (PC) 12.

После включения устройства импульс синхронизации (начальной установки) устанавливает триггеры 6, 7 и 8, счетчики 9, 13, 16 в исходное состояние, при котором на выходе счетчиков 9, 16, прямом выходе триггера 7 устанавливается уровень лог. "0", а на прямом выходе триггера 8 уровень лог."1". При этом на выходе триггера 6 и счетчика 13 установится уровень лог."0", который разрешает счетчику 9 счет тактов. Модуль счета счетчика 16, равный числу (m), и модуль счета счетчика 13, равный числу (1+α), устанавливаются предварительно сигналами управления на соответствующих входах устройства. Компаратор 4 начинает сравнение входной внешней ПСП и формируемой на выходе СМД3 внутренней ПСП. При этом импульсы ошибок с выхода компаратора 4 проходят на счетчик ошибок 13 и на схему "И" 11. Схема "И" 11 открыта уровнями "лог.1" с инверсного выхода триггера 7 и прямого выхода триггера 8. Поэтому импульсы ошибок будут воздействовать на PC12 через СМД14 до тех пор, пока счетчик 9 не досчитает число тактовых импульсов до n. Если при этом в PC12 будет записана безошибочная информация, т.е. PC детектора ошибок войдет в синхронизм с PC "передатчика", то на следующем этапе, когда на инверсном выходе триггера 7 установится "лог.0" и будет разрешен счет тактов С16, и счет ошибок С13, а схема "И" 11 будет закрыта, счетчик 13 за число тактовых периодов m, при правильном выборе m и (1+α), не досчитает до своего модуля счета (1+α) (при ожидаемом распределении ошибок во входной ПСП). На выходе счетчика 16 появится импульс, который установит "лог.0" на прямом выходе триггера 8, который закроет схему "И" 11 и разрешит счет ошибок С10, т.е. третий этап синхронизации благополучно закончится.

Если на втором этапе синхронизации в PC12 будет записана хотя бы одна ошибка, которая принята во входной ПСП, то на третьем этапе синхронизации С13 за число тактовых периодов m успеет досчитать до своего модуля счета (1+α) и положительный импульс на его выходе установит схему устройства в исходное состояние.

Такой процесс повторяется до тех пор, пока PC12 детектора ошибок не войдет в синхронизм с регистром сдвига "передатчика". После этого устройство начинает работать как детектор ошибок входной внешней ПСП.

Если в процессе нормального функционирования устройства произойдет сбой в регистре сдвига 12, на выходе СМД2 появятся импульсы, которые, воздействуя на вход "установки логического нуля" второго триггера, установят "лог.0" на его выходе, начнет работать первый счетчик и устройство вновь перейдет ко второму этапу работы при синхронизации - записи информации, затем к третьему этапу и т.д. до тех пор, пока автоматически не произойдет пересинхронизация устройства.

Большая помехоустойчивость данного устройства позволяет использовать его при анализе входной внешней ПСП, прошедшей объект контроля, и в тех случаях, когда вместо устройства [1] требуются другие методы анализа тестовой ПСП, например, измерение времени задержки сигнала в объекте контроля. Но данная схема устройства детектирования ошибок [2] является сложной за счет аппаратного обеспечения этапов проверки на отсутствие ложной синхронизации и отключения цепи обратной связи (воздействия сигнала ошибки на генератор внутренней ПСП), что снижает ее надежность, сужает диапазон рабочих частот вследствие большого времени прохождения и обработки сигнала в устройстве.

Технической задачей, на решение которой направлено данное изобретение, является упрощение схемы, повышение надежности, быстродействия, расширение диапазона рабочих частот устройства для детектирования ошибок.

Сущность изобретения заключается в том, что в устройстве, содержащем последовательно соединенные компаратор, первый триггер, первый сумматор по модулю два, второй сумматор по модулю два, выход которого является установочным входом устройства, второй триггер R-входом, первый счетчик, второй вход которого является входом тактовых импульсов устройства, и третий триггер С-входом, R-вход которого подключен к выходу второго триггера, второй вход первого счетчика подключен к С-входу четвертого триггера, D-вход которого является информационным входом устройства, а выход соединен со вторым входом первого сумматора по модулю два и первым входом компаратора, другой вход которого подключен ко второму входу второго сумматора по модулю два и к выходу третьего сумматора по модулю два, первый, второй и третий входы которого соединены соответственно с первым, вторым, и третьим выходом регистра сдвига, второй счетчик, первый вход которого соединен с выходом компаратора и является выходом устройства, выход четвертого триггера подключен ко входу регистра сдвига, второй вход второго счетчика соединен с инверсным выходом третьего триггера, прямой выход которого соединен с S-входом второго триггера, а выход второго счетчика является информационным выходом устройства.

На фиг.1 представлена структурная схема прототипа, где обозначено:

1 - первый сумматор по модулю два (СМД);

2 - второй СМД;

3 - третий СМД;

4 - компаратор;

5 - первый триггер;

6 - второй триггер;

7 - третий триггер;

8 - четвертый триггер;

9 - первый счетчик;

10 - второй счетчик;

11 - элемент "И";

12 - регистр сдвига (PC);

13 - третий счетчик;

14 - четвертый СМД;

15 - пятый триггер;

16 - четвертый триггер.

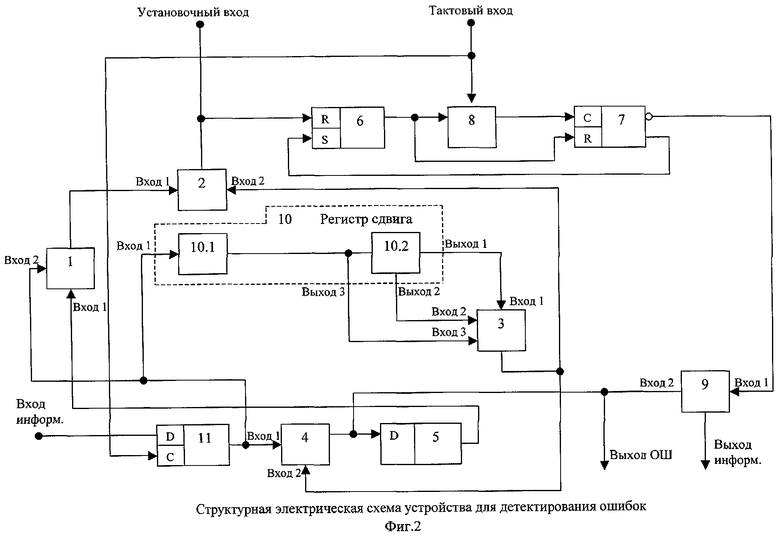

На фиг.2 представлена структурная схема заявляемого устройства, где обозначено:

1 - первый сумматор по модулю два (СМД);

2 - второй СМД;

3 - третий СМД;

4 - компаратор;

5 - первый триггер;

6 - второй триггер;

7 - третий триггер;

8 - первый счетчик (тактов по модулю п+1);

9 - второй счетчик (ошибок);

10 - регистр сдвига (PC);

11 - четвертый триггер.

Обозначение входов триггеров:

R - вход установки логического нуля;

С - счетный (тактовый) вход;

D - информационный вход;

S - вход установки логической единицы.

Устройство (фиг.2) содержит последовательно соединенные СМД1, СМД2, выход которого является установочным входом устройства, а второй вход СМД2 соединен с выходом СМД3 и с одним из входов компаратора 4, выход которого через триггер 5 соединен с первым входом СМД1, последовательно соединенный триггер 6, R-вход которого подключен к установочному входу устройства, счетчик 8, второй вход которого является входом тактовых импульсов устройства, и триггер 7 С-входом, R-вход которого подключен к выходу триггера 6; счетчик 9, первый вход которого соединен с выходом компаратора 4 и является выходом ошибок устройства, второй вход - с инверсным выходом триггера 7, неинверсный выход которого соединен с S-входом триггера 6, а выход счетчика 9 является информационным выходом устройства; регистр сдвига (PC) 10, вход которого соединен с выходом триггера 11, другим входом компаратора 4 и вторым входом СМД1, первый, второй и третий выходы PC10 соединены соответственно с первым, вторым и третьим входами СМД3; D-вход триггера 11 является информационным входом устройства, а С-вход соединен с тактовым входом устройства.

Работа детектора ошибок происходит следующим образом. После включения устройства импульс синхронизации (начальной установки) устанавливает триггеры 6 и 7, счетчик 8 в исходное состояние, при котором на выходе счетчика 8, прямом выходе триггера 7 устанавливается уровень "лог.0", а на инверсном выходе триггера 7 уровень "лог.1". При этом на выходе триггера 6 установится уровень "лог.0", который разрешает счетчику 8 счет тактов. Компаратор 4 начинает сравнение входной внешней ПСП и формируемой на выходе СМД3 внутренней ПСП. При этом импульсы ошибок с выхода компаратора 4 проходят на счетчик ошибок 9, счет которому запрещен уровнем "лог.1" с инверсного выхода триггера 7 до тех пор, пока счетчик тактов 8 не досчитает до своего модуля счета (n+1). После этого сигналом с выхода счетчика тактов 8 триггер 7 устанавливается в состояние "лог.1". При этом уровень "лог.0" с инверсного выхода триггера 7 разрешает счет ошибок счетчику 9. Как отмечается ниже, для правильного определения количества ошибок в принимаемой последовательности с одиночными ошибками (интервал между ошибками ≥n·Тт) и коэффициентом ошибок  , необходимо количество ошибок, подсчитанное счетчиком ошибок, поделить на увеличенное на единицу число точек подключения СМД3 к PC10, что может быть выполнено автоматически в блоке 9 или внешней аппаратурой. Таким образом, устройство начинает работать как детектор ошибок входной внешней ПСП после этапов начальной установки и записи входной информации в PC10.

, необходимо количество ошибок, подсчитанное счетчиком ошибок, поделить на увеличенное на единицу число точек подключения СМД3 к PC10, что может быть выполнено автоматически в блоке 9 или внешней аппаратурой. Таким образом, устройство начинает работать как детектор ошибок входной внешней ПСП после этапов начальной установки и записи входной информации в PC10.

Функции и работа СМД2, компаратора 4 и триггера 5 аналогичны функциям и работе в прототипе.

Заявляемая структура детектора ошибок позволяет отказаться от управления фазовым сдвигом внутренней ПСП, формируемой на выходе СМД3 выделенными импульсами ошибок. Сравнение формируемой внутренней и принимаемой внешней ПСП и выделение импульсов ошибок осуществляется компаратором. При этом формирование внутренней ПСП производится фильтром на регистре сдвига 10 и СМД3, точки подключения которого к PC10 такие же, что и в генераторе передающей части системы контроля, формирующей испытательный сигнал в виде ПСП.

Очевидно, что вести подсчет количества ошибок во входной ПСП, прошедшей объект контроля, необходимо через интервал времени, равный n·Тт, где n - длина (число разрядов) PC10; Тт - период тактовой частоты, после включения устройства и прихода установочного импульса, так как PC10 должен быть заполнен входной информацией. При этом очевидно, что, если PC10 заполнен правильной информацией, то на выходе СМД3 появляется правильный бит внутренней ПСП. Если же в PC10 в составе входной информации записывается ошибка, то на выходе СМД3 появляется ошибочный бит внутренней ПСП в момент, когда "ошибка" попадает в триггер PC10, к которому подключен СМД3. Таким образом, для правильного определения количества ошибок во входной внешней ПСП за некоторый интервал времени в случае, когда коэффициент ошибок этой последовательности Кош.≤1/n и ошибки одиночные (с интервалом между ошибками большим или равным n·Тт), что выполняется в большинстве современных каналов связи, достаточно полное количество ошибок, подсчитанное счетчиком ошибок 9 поделить на увеличенное на единицу количество точек подключения СМД3 к PC10. Увеличение на единицу числа, на которое делится количество ошибок, подсчитанное счетчиком ошибок, вызвано тем, что на выходе компаратора 4 появляется еще ошибка в момент ее записи в четвертый триггер (фиг.2) (после прихода ошибки на информационный вход устройства). В тактовых интервалах, где внутренняя и внешняя ПСП совпадают на выходе компаратора, присутствует "лог.0". При несовпадении битов внутренней и внешней ПСП на выход компаратора выдается "лог.1" в течение периода тактовых импульсов.

Практическая реализация блоков предлагаемого устройства может быть выполнена на следующих серийно выпускаемых микросхемах:

- блоки 1, 2, 3, 4 - на двухвходовых элементах "ИСКЛЮЧАЮЩЕЕ ИЛИ", входящих в состав микросхем, например, К555ЛП5, КМ555ЛП5, где выводы 1 и 2, 4 и 5, 9 и 10, 12 и 13 являются входами, а 3, 6, 8, 11 выходами соответственно (для тактовых частот ПСП, меньших 10 МГц) [3], 100ЛП107, 500ЛП107 (для тактовых частот ПСП, меньших 100 МГц) [4]. Наличие соединений выходов разрядов PC12 с группой входов СМД3 определяется видом характеристического многочлена конкретной принимаемой М-последовательности;

- блоки 5, 10, 11 - на D-триггерах микросхемы КМ555ТМ2 (два D-триггера в одном корпусе). При этом задействованные по схеме устройства входы D - вывод 2 (12), R - вывод 1 (13); С - вывод 3 (11), прямой выход - вывод 5 (9) микросхемы. [3] На D-триггерах микросхемы К500ТМ131 (два D-триггера в одном корпусе). При этом задействованные по схеме устройства входы D - вывод 7 (10), R - вывод 4 (13); С - вывод 9, прямой выход - вывод 2 (15). При этом на вход  - вывод 6 (11) должен быть подан уровень "лог.0" [4];

- вывод 6 (11) должен быть подан уровень "лог.0" [4];

- блоки 6, 7 - на j-триггерах микросхемы К555ТВ9 (два j-k триггера в одном корпусе);

- блоки 8, 9 - на микросхемах К155ИЕ2 (двоично-десятичный 4-разрядный счетчик). Задействованные по схеме устройства счетный вход тактов или импульсов ошибок (вход 1) - вход С1 (вывод 14 микросхемы), вход общего сброса с остановкой счета (вход 2) - входы & R0 (выводы 2 и 3 микросхемы), соединенные вместе. При этом выход Q0 (вывод 12) соединяется с входом С2 (вывод 1) микросхемы. Для наращивания емкости счетчика до необходимого числа микросхемы К155ИЕ2 соединяются последовательно, при этом выход Q3 (вывод 11) предыдущей микросхемы соединяется с входом С1 (вывод 14) последующей [3, 4].

Питание устройства осуществляется от источника +5 В для микросхем К155 и К555 серии и от источника - 5,2 В для микросхем 100, К500 серий. При этом выводы 7 микросхем К555ЛП5, КМ555ЛП5, КМ555ТМ2, вывод 8 микросхем К555ТВ9, вывод 10 микросхемы К155ИЕ2 соединяются с корпусом устройства, а выводы 14 микросхем К555ЛП5, КМ555ЛП5, КМ555ТМ2, вывод 16 микросхем К555ТВ9, вывод 5 микросхемы К155ИЕ2 соединяются с шиной +5 В.

Выводы 1, 16 микросхем 100ЛП107, 500ЛП107, К500ЛС118, К500ЛС119, К500ТМ131 соединяются с корпусом устройства, а вывод 8 этих микросхем соединяются с шиной - 5,2 В.

Источники информации

1. Авторское свидетельство СССР №1251335 кл. Н 04 В 3/46, 1985 г. В.С.Балан, М.С.Гроссман. Устройство для детектирования ошибок.

2. Заявка на изобретение СССР №4832472/09 (059243) от 29.05.90 г., МК. 5 Н 04 В 3/46. Устройство для детектирования ошибок. К.Г.Кирьянов, В.В.Акулов, А.С.Меднов, АС №1709542 - прототип.

3. Интегральные микросхемы. Справочник. Под ред. В.В.Тарабрина. М.: Энергоатомиздат, 1985 г.

4. Аналоговые и цифровые интегральные микросхемы. Справочное пособие. Под ред. С.В.Якубовского. М.: "Радио и связь", 1985 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2279184C2 |

| Устройство для детектирования ошибок | 1985 |

|

SU1251335A1 |

| Устройство для детектирования ошибок | 1988 |

|

SU1573545A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Устройство для детектирования ошибок | 1990 |

|

SU1709542A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2270527C1 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| Устройство для детектирования ошибок | 1989 |

|

SU1663771A1 |

| Устройство для синхронизации @ -последовательности | 1984 |

|

SU1225002A1 |

Изобретение относится к радиоизмерительной технике и может использоваться для выделения ошибочных символов из информационной последовательности. Достигаемым техническим результатом является упрощение устройства для детектирования ошибок с одновременным повышением его надежности, быстродействия и расширением диапазона частот. Для этого устройство содержит первый сумматор по модулю два (СМД1), второй (СМД2), третий (СМД3), первый компаратор (4), первый триггер (5), второй триггер (6), третий триггер (7), первый счетчик (8), второй счетчик (9), регистр сдвига (10), четвертый триггер (11). 2 ил.

Устройство для детектирования ошибок, содержащее последовательно соединенные компаратор, первый триггер, первый сумматор по модулю два, второй сумматор по модулю два, выход которого является установочным входом устройства, второй триггер R-входом, первый счетчик, второй вход которого является входом тактовых импульсов устройства, и третий триггер С-входом, R-вход которого подключен к выходу второго триггера, второй вход первого счетчика подключен к С-входу четвертого триггера, D-вход которого является информационным входом устройства, выход соединен со вторым входом первого сумматора по модулю два и первым входом компаратора, другой вход которого подключен ко второму входу второго сумматора по модулю два и к выходу третьего сумматора по модулю два, первый, второй и третий входы которого соединены соответственно с первым, вторым и третьим выходами регистра сдвига, второй счетчик, первый вход которого соединен с выходом компаратора и является выходом ошибок устройства, отличающееся тем, что выход четвертого триггера подключен ко входу регистра сдвига, второй вход второго счетчика соединен с инверсным выходом третьего триггера, прямой выход которого соединен с S-входом второго триггера, а выход второго счетчика является информационным выходом устройства.

| Устройство для детектирования ошибок | 1990 |

|

SU1709542A1 |

| Устройство для детектирования ошибок | 1989 |

|

SU1663771A1 |

| Устройство для детектирования ошибок | 1988 |

|

SU1573545A1 |

| Устройство для детектирования ошибок | 1985 |

|

SU1251335A1 |

| US 3895349 A1, 15.07.1975 | |||

| US 2004123199 A1, 24.06.2004. | |||

Авторы

Даты

2006-05-20—Публикация

2004-09-27—Подача