1

Изобретение относится к радиотехнике и может использоваться в устройствах частотной и фазовой авто- подйтройки.

Цель изобретения - повышение быс родействия.

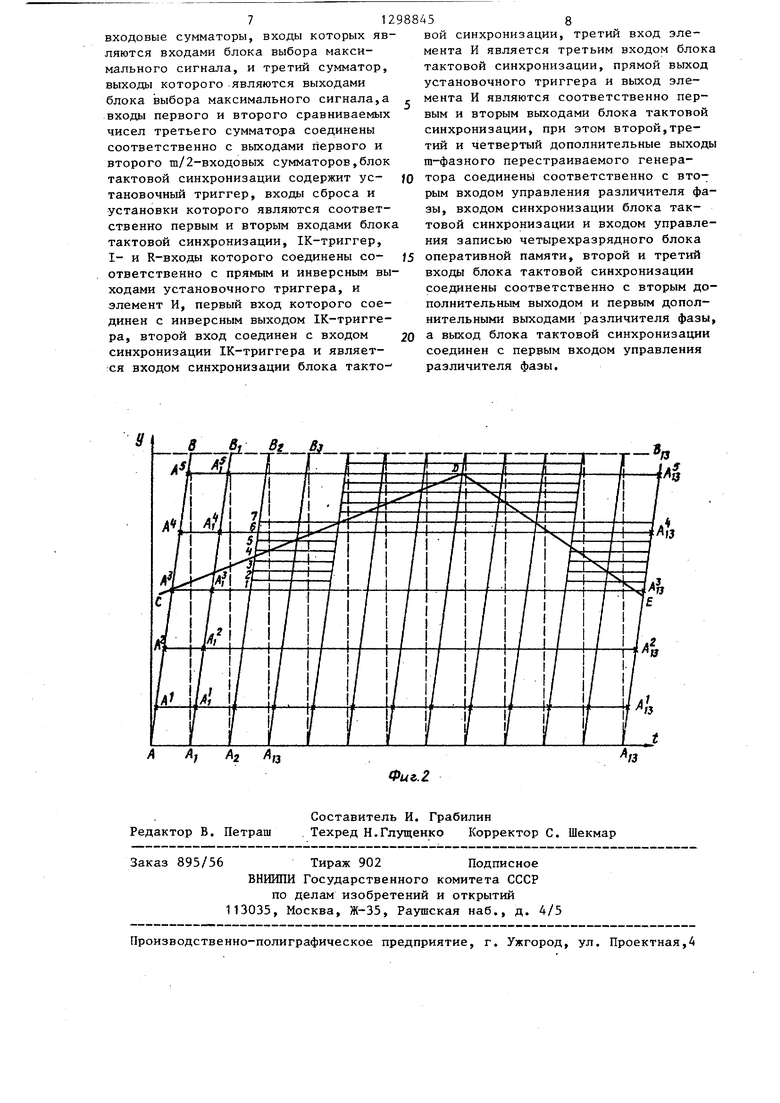

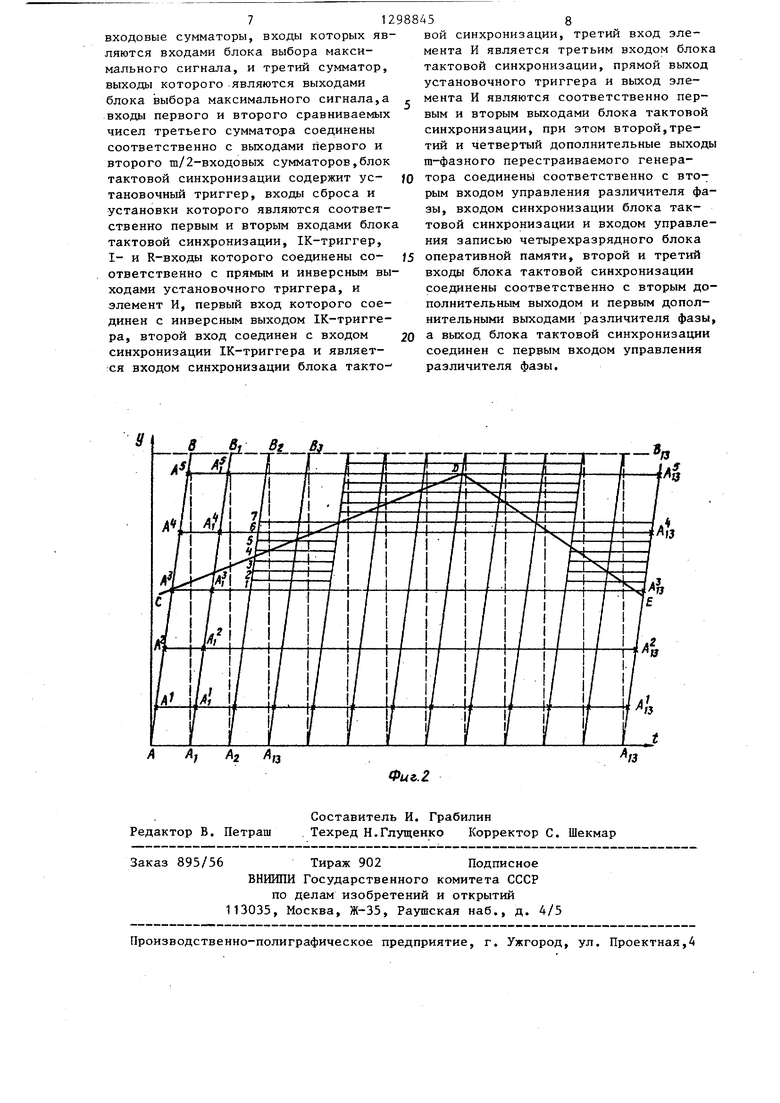

На фиг.1 представлена электрическая функциональная схема цифрового частотного демодулятора; на фиг.2 - график изменения фаз т-фазного перестраиваемого генератора и входного сигнала.

Цифровой частотный демодулятор сдержит т-фазный перестраиваемый генератор 1, га-фазовых детекторов 2 , 2 ,...,2, блок 3 выбора максимального сигнала, четырехразрядный блок

4оперативной памяти, различитель

5фазы, блок 6 тактовой синхронизации. Генератор 1 содержит задающий генератор 7, п-разрядный регистр 8 сдвига, п-входовый элемент И-НЕ 9, инверторы 10 и 11, первый 12, второй 13 элементы И-НЕ, третий 14,четвертый 15, пятый 16 и шестой 17 инверторы, т отводную линию 18 задержк

Блок 3 выбора максимального сигнала содержит первый 19 и второй 20 m/2-входовые сумматоры и третий сумматор 21 .

Различитель 5 фазы содержит четыре инвертора 22-25, D-триггер 26,певый 27 и второй 28 формирователи импульсов знака разности, элемент ИЛИ 29, элеме нт И 30, четырехразрядный цифровой компаратор 31.

Блок 6 тактовой синхронизации содержит установочный триггер 32, IK-- триггер 33, элемент И 34.

Цифровой частотный демодулятор ра- 40 ла f

ботает следзпощим образом.

Период частоты задающего генератора 7 выбирается из следующего соотношения:

0.1).

ном

(1)

где

задающего

L - период частоты

генератора 7j п - любое целое число; иом период номинальной частоты, с которой сравнивается частота входного сигнала .

График изменения фазы задающего генератора 7 при представлен на фиг.2.Прямыми АВ, А4В, показаны прямые изменения фазы задающего генератора 7 по отношению к фазе ..„., , точI (Г I с - А

ками А -А , и т.д. показано положение переднего фронта задающего генератора 7.

Как видно из формулы (1), через п периодов задающего генератора 7

частоты f генератора 7

MOM

и частоты задаю- сравняются, т.е.

ш

п-Т (n-H)-T,,

(2)

Таким образом, точки А , А , A,...,A,j (фиг.2) находятся на одной прямой и представляют собой одну реализацию номинальной частоты.

точки А,, ...,А

из

вторая реали0

25

зация номинальной частоты. Таким образом при получаем пять реализаций номинальной частоты (фиг.2).Одна из реализаций частоты подается на вход га-отводной линии 18 задержки, с отводов которой получают с меньшим сдвигом фазы реализации (1-8, фиг.2) по числу отводов га-отводной линии 18 задержки. Первоначальная задача заключается в нахождении ближайшей реализации номинальной частоты такой, чтобы график изменения фазы входного сигнала (CD, фиг.2)

30 пересекал реализации частоты (1-8, фиг.2). Для этого первый импульс с тфазного перестраиваемого генератора 1 (инвертор 14) подается на вход гаотводной линии 18 задержки, сигна35 лы с отводов га-отводной линии 18 задержки используются в качестве синхронизирующих, по которым идет зат пись входного сигнала в фазовые детекторы 2,-2„. Если реализация сигна40 ла f

НОА

2 2. с отводов ш-отводной линии

18 задержки не пересекает передний фронт входного сигнала, то во все фазовые детекторы 2,-2 будут записаны либо нули, либо единицы. На вы45 ходах блока 3 в том и другом случаях будут нули, так как число 16,0 10000, а старший разряд не используется. На элементе И 30 происходит совпадение четырех высоких уров50 ней с инверторов 22-25 так, что второй сдвинутый сигнал с т-фазного перестраиваемого генератора 1 проходит через элемент И 30 и устанавливает в единицу установочный триггер 32.

55 При этом на формирователь 27 поступает сигнал с единичного выхода установочного триггера 32 и единичный сигнал с выхода D-триггера 26. В первоначальный момент времени состояние D-триггера 26 неопределенно.Предположим, что он находится в состоянии единицы, тогда на формирователе 27 происходит совпадение и сигнал с вы- хода поступает в качестве сигнала управления Н в т-фазный перестраиваемый генератор 1, в котором инвертор 11 и элемент И-НЕ 13 подключают в п-раз- рядном регистре 8 сдвига один триг- гер. При отсутствии сигналов управления коэффициент деления га-фазного перестраиваемого генератора 1 равен п (формула I). В даном случае (при поступлении сигнала управления fia цепоч- ку инвертор 11 - элемент И-НЕ 13) коэффициент деления увеличивается и равен п+1, при поступлении сигнала управления на цепочку инвертор 10 - элемент И-НЕ 12 коэффициент деления уменьшается (так как отключает в п- разрядном регистре В сдвига последний триггер) и равен п-1.

Первый импульс следующего цикла работы т-фазного перестраиваемого генератора 1 устанавливает установочный триггер 32 в нуль, тем самым снимает сигнал управления с т-фазного перестраиваемого генератора 1 и восстанавливает коэффициент деления,разный п, но к этому- моменту уже происходит сдвиг фазы работы т-фазного перестраиваемого генератора 1 и теперь на вход т-отводной линии 18 задержки подается следующая реализация номи- нальной частоты А. .. , . Таким образом, находится реализация частоты, при подаче которой на т-отводную линию 18 задержки количество единиц,записанных в фазовые детекторы , , отлично от нуля и 1. Четвертым импульсом с т-фазного перестраиваемого генератора 1 значение четырех разрядов с блока 3 записывается в четырехразрядный блок 4 оперативной памяти.

В следующем цикле работы т-фазного перестраиваемого генератора 1 четырехразрядный цифровой компаратор 31 сравнивает текущее и предыдущее значения суммы количества единиц и формирует два сигнала: текущее значение () меньше предыдущего, текущее значение () больше предьщущего. Запись результата сравнения производится в D-триггер 26 по третьему им- пульсу с т-фазного перестраиваемого генератора 1 через элемент И 30, на другой вход которого подается сигнал с элемента ИЛИ 29, который срабатывает при наличии одного из двух выходных сигналов четырехразрядного цифрового компаратора 31.

По третьему входу элемент И 34 разрешается нулевым вьосодом установочного триггера 32, который запрещает элемент И 34 в последующей цикл работы т-фазного перестраиваемого генератора 1 после изменения его фазы сигналом управления с формирователем 27 т.е. когда в установочном триггере 32 записана единица,которая по треть- ему импульсу т-фазного перестраиваемого генератора 1 переписывается в 1К-триггер 33 и запрещает элемент И 34 на один цикл работы т-фазного перестраиваемого генератора 1.

Выходы D-триггера 26 являются выходом цифрового частотного демодулятора, кроме того, они используются в качестве обратной связи для управления изменением фазы счета т-фазного перестраиваемого генератора 1. В случае изменения фазы входного сигнала, как показано на фиг.2 (CD), количество единиц в фазовых детекторах 2 с каждым циклом работы т-фазного перестраиваемого генератора 1 уменьшается, следовательно, () последующее значение меньше предыдущего и после четырехразрядного цифрового компаратора 31 в D-триггер 26 записывается единица. Этот сигнал означает

что fax fnoMЕдиничный сигнал с выхода D-триггера 26 разрешает работу формирователя 27, выходной сигнал которого в Случае срабатывания установочного триггера увеличивает коэффициент да- ления т-фазного перестраиваемого генератора 1 на единицу и (фиг.2) при выходе фазы входного сигнала из зоны реализации номинальной частоты (А , А,. .. ,А, ) происходит переключение на вход т-отводной линии 18 задержки реализации частоты (А,... ,А ) . В случае изменения фазы входного сигнала (DE, фиг.2) количество единиц в фазовых детекторах 2 постоянно увеличивается, следовательно, после сравнения в четырехразрядном цифровом компараторе 31 (А - В) в D-триггер 26 записывается нуль, это означает, что f эх ноАл Нулевой сигнал с выхода D-триггера 26 разрешает работу формирователя 28, сигнал с которого уменьшает коэффициент деления т-фазного перестраиваемого генератора 1 на единицу, и вызьшает переход с pea5 12988456

лизации А , Aj,...,Al;, на реализациюго через инверторы соединены с перА , А ,..,А, , когда фаза входноговыми входами первого и второго элесигнала выходит из мелких реализацийментов И-НЕ соответственно, выходы

номинальной частоты А ,А% .. . ,A,j икоторых соединены с (п-1)-м и п-м вхофазовые детекторы 2 заполняются еди- дами п-входового элемента И-НЕ,треницами.тий, четвертый, пятый и шестой инверторы, входы которых соединены с

Формула изобретенияпервым, вторым, третьим и четвертым

выходами п-разрядного регистра сдвиЦифровой частотный демодулятор, О га, а также т-отводную линию задерж- содержащий т-фазный перестраиваемыйк которой соединен с выходом генератор, га фазовых детекторов,пер-третьего инвертора, m отводов ш-от- вые-входы которых объединены и явля-водной линии задержки являются фазны- ются входом цифрового частотного де- выходами т-фазного перестраивае- модулятора, последовательно соеди- 5 мого генератора, а выходы третьего, ненные блок выбора максимальногочетвертого, пятого и шестого инверто- сигнала, каждый из m входов которогоР° являются соответственно первым, подключен к выходу соответствующеговторым, третьим и четвертым дополни- фазового детектора, четырехразряд-тельными выходами т-фазного перестра- ный блок оперативной памяти и разли-20 иваемого генератора, причем различи- читель фазы, содержащий -элемент И,тель фазы дополнительно содержит че- элемент ИЛИ и первый и второй форма-тырехразрядный цифровой компаратор, рователи импульсов знака разности,четыре инвертора и D-триггер, прямой первые входы которых объединены и яв-« инверсный выходы которого соедине- ляются входом импульсов тактовой син- ны соответственно с вторыми входами хронизации, а выходы являются пер-первого и второго формирователей Им- вым и вторым выходами различителя фа-пульсов знака разности и являются вы- зы и соединены с первым и вторымходами цифрового частотного демодуля- входами управления т-фазного пере-тора, вход синхронизации D-триггера страиваемого генератора, каждый из-30 является первым входом управления т-фазных выходов которого соединен сразличителя фазы, а D-вход соединен вторыми входами соответствующих фа- выходом Больше четырехразрядного зовых детекторов, а также блок такто-цифрового компаратора и первым вхо- вой синхронизации, первый вход кото- элемента ИЛИ, второй вход которо- рого соединен с первым дополнитель-35 го соединен с выходом Меньше четы- ным выходом т-фазного перестраивае-рехразрядного цифрового компаратора, мого генератора, первый выход блока выход элемента ИЛИ является первым тактовой синхронизации соединен сдополнительным выходом различителя входом импульсов тактовой синхрониза-фазы, входы первого сравниваемого ции различителя фазы, а второй выход40 числа четырехразрядного цифрового соединен с первым входом управления компаратора являются основньми инфор- различителя фазы,при этом выходы бло-мационными входами различителя фазы, ка выбора максимального сигнала сое-каждый из входов второго сравниваемо- динены с соответствующими дополни-го числа четырехразрядного цифрового тельными информационными входами раз- З компаратора соединен с входом одно- личителя фазы, отличающий-.го из четырех соответствующих инвер- с я тем, что, с целью повышения бы-торов, выходы которых соединены с со- стродействия, т-фазный перестраивае-ответствующими входами элемента И, мый генератор содержит задающий ге-пятый вход которого является вторым нератор, п-разрядный регистр сдвига,50 входом управления различителя фа- вход синхронизации которого соединензы, а вьпсод элемента И является вто- С выходом задающего генератора,п-вхо-рым дополнительным выходом различите- довый элемент И-НЕ, п-2 входов кото-ля фазы, входы второго сравниваемого роге соединены с п-2 выходами млад-числа четырехразрядного цифрового ших разрядов п-разрядного регистра55 компаратора являются дополнительными сдвига, а выход соединен с информа-информационными входами различителя ционным входом п-разрядного регистрафазы, блок выбора максимального сиг- сдвига, (п-1)-й и п-й выходы которо-нала содержит первый и второй т/2входовые сумматоры, входы которых являются входами блока выбора максимального сигнала, и третий сумматор, выходы которого являются выходами блока выбора максимального сигнала,а входы первого и второго сравниваемых чисел третьего сумматора соединены соответственно с выходами первого и второго m/2-входовьгх сумматоров,блок тактовой синхронизации содержит ус- тановочный триггер, входы сброса и установки которого являются соответственно первым и вторым входами блок тактовой синхронизации, 1К-триггер, I- и R-входы которого соединены со- ответственно с прямым и инверсным выходами установочного триггера, и элемент И, первый вход которого соединен с инверсным выходом 1К-тригге- ра, второй вход соединен с входом синхронизации 1К-триггера и являет- ;ся входом синхронизации блока тактовой синхронизации, третий вход элемента И является третьим входом блока тактовой синхронизации, прямой выход установочного триггера и выход элемента И являются соответственно первым и вторым выходами блока тактовой синхронизации, при этом второй,третий и четвертый дополнительные выходы га-фазного перестраиваемого генератора соединены соответственно с вторым входом управления различителя фазы, входом синхронизации блока тактовой синхронизации и входом управления записью четырехразрядного блока оперативной памяти, второй и третий входы блока тактовой синхронизации соединены соответственно с вторым дополнительным выходом и первым дополнительными выходами различителя фазы а выход блока тактовой синхронизации соединен с первым входом управления различителя фазы.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОВЫСОТОМЕР | 2001 |

|

RU2212684C1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Детектор частотно-манипулированных сигналов | 1982 |

|

SU1067610A2 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| РАДИОЛОКАТОР-ИНТРОСКОП | 1994 |

|

RU2096767C1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Устройство для измерения отклонения частоты от номинального значения | 1984 |

|

SU1322450A1 |

Изобретение относится к радиотехнике и может использоваться в устр-вах частотной и сказовой автоподстройки. Цель изобретения - повышение быстродействия. Цифровой частотный демодулятор содержит т-фазный перестраиваемый генератор 1, m фазовых детекторов 2, блок 3 выбора макс. сигнала, четырехразрядный блок 4 оперативной памяти, различитель 5 фазы и блок 6 тактовой синхронизации.Генератор 1 состоит из задающего генератора 7, п-разрядного регистра 8 сдвига, п-входового элемента И-НЕ 9, инверторов 10, 11, 14-17, элементов И-НЕ 12, 13 и т-отводной линии задержки 18. Блок 3 состоит из т/2- входовых сумматоров 19, 20 и сумматора 21. Различитель 5 фазы содержит инверторы 22-25. D-триггер 26, формирователи 27, 28 импульсов знака разности, элементы ИЛИ 29, И 30 и четырехразрядный цифровой компаратор 31. Блок 6 состоит из установочного триггера 32, 1К-триггера 33 и элемента И 34 . 2 ил . с (Л

0

/3

2 А,з

Редактор В. Петраш

Составитель И. Грабилин , Техред Н.Глущенко Корректор С. Шекмар

Заказ 895/56 Тираж 902 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

13

Фиг. 2

| Цифровой частотный демодулятор | 1979 |

|

SU881973A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство определения знака разности двух частот | 1983 |

|

SU1159151A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1984-06-22—Подача