(54) УСТРОЙСТВО ДЛЯ СЖАТИЯ ИНФОРМАЦИИ ;.-..,.Г.,. I

г - - й-;лйг;/ ГШ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1978 |

|

SU731452A1 |

| Устройство для сжатия информации | 1979 |

|

SU830484A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| Устройство для передачи сигналов приращений с предсказанием | 1978 |

|

SU783824A2 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Функциональный преобразователь | 1978 |

|

SU805337A1 |

| Устройство для измерения экстремумов | 1983 |

|

SU1108465A1 |

| Устройство для дискретной записи и воспроизведения функций | 1977 |

|

SU742914A1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

t

Изобретение относится к области (Телеметрии и может быть использовано в многоканальных цифровых телеметрических системах для передачи информации с малой избыточностью. 5

Известно устройство для передачи телеметрической информации, содержащее синхронизатор, выход которого подключен к коммутатору каналов, к блоку памяти полных кодов и собствен- 10 но через блок кодирования адресов и блок кодирования времени - к первому и второму входам буферного запоминающего устройства, выход коммутатора каналов через блок кодиро- вания подключен к блоку памяти полных кодов и к анализатору сигналов, выход блока памяти полных кодов соединен с анализатором сигналов, выход которого подключен соответственно к 20 первому входу и через блок памяти кодов приращения - ко второму входу блока сравнения кодов приращения, выход блока памяти полных кодов подключен к .входу элемента И, выхбй 25 блока сравнения кодов приращения подключен ко второму входу элемента И, к входу буферного запоминающего устройства, выхсд элемента И соединен с другим входом буферного запомина- ЗО

ющего устройства, а один выход синхронизатора соединен с соответствующим входом блока памяти кодов приращения ij.

Это устройство обеспечивает большой коэффициент сжатия, но является сложным по своей технической реализации и обладает сравнительно низким быстродействием.

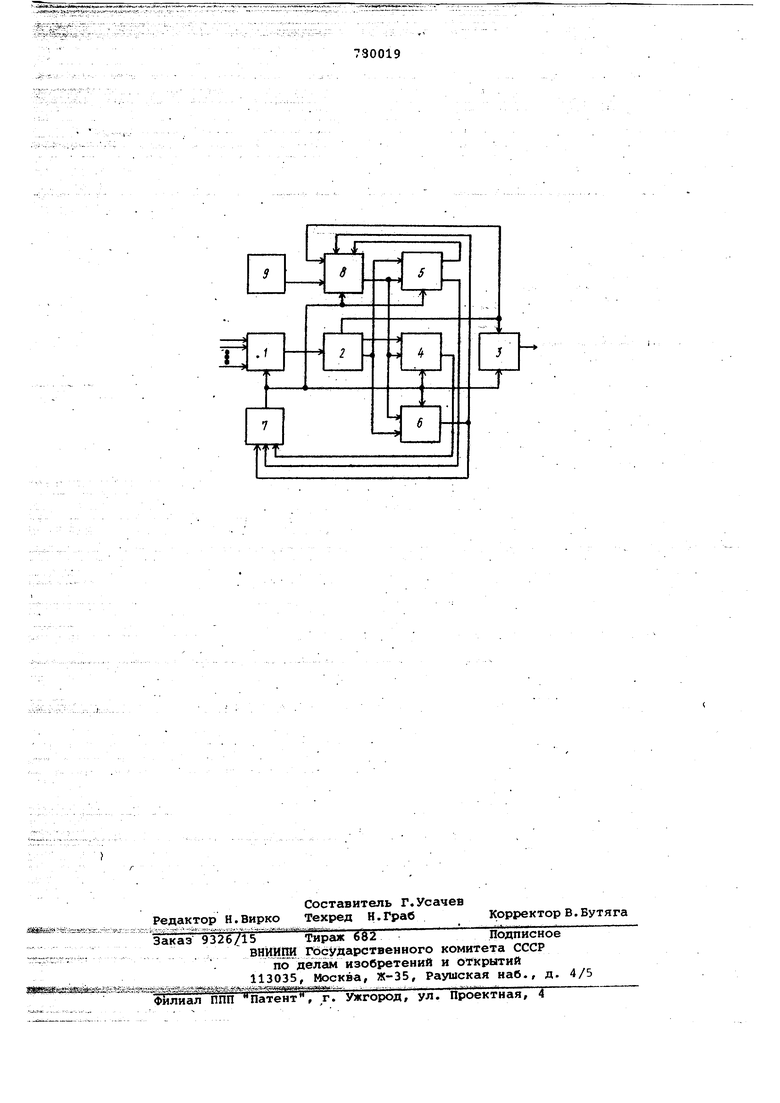

Известно также устройство для сжатия информации, содержащее коммутатор, выход которого подключен ко входу аналого-цифрового пЕ еобразователя, первый выход которого соединен с информационным входом первого блока буферной памяти и первым входом сумматора, второй блок памяти, который подключен ко второму входу сумматора, первый блок сравнения, первый вход которого соединен со вторым выходом аналого-цифрового преобразователя, третий выход которого подключен к первому входу второго блока сравнения, первый выход которого соединен с третьим входом сумматора, выход которого подключен ко второму входу первого блока сравнения, выход первого блока сравнения и второй выход второго блока сравнения подключены соответственно к первому и второму входам блока синхроЯйэацйи, выход которого соединен с управляющими входами коммутатора, сумматора, первого и второго блока сравнения и первого блока памяти 2 Однако это устройство участки поступающего на вход сигнала с бли ким к нулю значением первой произво ной обрабатывает с мальом коэффициен том сжатия. За счет этого понижается общий коэффициент сж,атия. Этот недостаток обуславливается тем, что экстраполяция процесса- ведется поли номами aiB.t (где B const), т.е. прямыми с постоянным углом наклона. Цель изобретения - повышение коэффициента сжатия при сохранении быстродействия устройства и простоты его технической р еализации. Поставленная цель.достигается тем, что в устройство, содержащее коммутатор, выход которбго подключен ко входу аналого-цифрового преобразователя, первый выход которого соединен G информационным входом первого блока буферной памяти и пер вым входом сумматора,.второй блок памяти, который подключен ко второму входу сумматора, первый блок сравнения, первый вход которого соединен со вторым выходом аналогоцифрового преобразователя, третий выход которого подключен к первому входу второго блока сравнения, первый выход которого соединен с третьим входом ci viMaTOpa, выход которого подключен ко второму входу пер вого блока сравнения, выход первого блока сравнения и второй выход второго блока сравнения подключены соответственно к первому и второму вх дам блока синхронизации, выход которого соединен с управляющими входами коммутатора сумматора, первого и второго блока сравнения и первого блока памяти, введен третий блок сравнения,первый вход которого соединен с третьим выходом аналогоцифрового преобразователя, второй вход третьего блока сравнения подкл чен к выходу сумматора, который соединен со вторым входом второго бло ка сравнения, управляющий вход третьего блока сравнения подключен к выходу блока синхронизации, третий вход которого соединен с выходом третьего блока сравнения и с четвер тым входом сумматора. На чертежепредставлена блок-схе ма устройства. Она содержит коммутатор 1, аналого-цифровой преобразо ватель 2, первый блок памяти 3, пер вый, второй и третий блоки сравнени 4, 5 и 6, блок синхронизации 7, сум матор 8, второй блок памяти 9, Устройство работает следующим об разом. Во второй блок памяти 9 до начала обработки сообщения заносят значение постоянного приращения rf--lt)lut где д1 - интервал дискретизации исследуемого процесса; /в/ - коэффициент, численно равный среднему значению модуля первой производной обрабатываемого процесса, иго Определяют исходя из априорных данных об исследуемом процессе. По сигналу из блока синхронизации 7 обрабатываемый процесс через коммутатор 1 поступает на вход аналого-цифрового преобразователя 2, где преобразуется в цифровую форму. Полученный код поступает на вход первого блока памяти 3, на вход сумматора 8 и на входы блоков сравнения 4, 5 и б, которые имеют- порог чувствительности. На другие входы блоков сравнения 4, 5 и 6 из сумматора 8 поступает предсказанное значение, соответствующее предьщущему моменту времени. По сигналу из блока синхронизации, сравнивая поступившие на их входы-значения процесса, второй и третий блоки сравнения 5 и 6 определяют знак первой производной процесса на данном интервале дискретизации, jBHaK первой производной поступает на один из управляющих входов сумматора 8. Предположим, что на предыдущем интервале дискрети-зации первая производная Обрабатываемого процесса была положительной. Тогда, если первая про.изводная процесса на данном интервале дискретизации имеет положительный знак, то по сигналу из блока синхронизации 7 содержимое Второго блока памяти 9 прибавляется к значению процесса, предсказанному в предыдущий момент времени и хранящемся в сумматоре 8. Таким образом, в Сумматоре 8 образуется предсказанное значение процесса, соответствующее настоящему моменту времени. Это предсказанное значение поступает на вход блока 4 сравнения и по сигналу из блока синхронизации 7 сравнивается с истинным значением процесса в настоящий момент времени. Если эти значения равны или отличаются на величину,-меньшую допустимой абсолютной погрешности, то на выходе первого блока сравнения 4. вырабатывается сигнал О, который через блок синхронизации 7 не разрешает первому блоку памяти 3 принимать данное значение процесса. Если же сравни-., ваемые значения отличаются на величину, большую допустимой абсолютной погрешности, то на выходе первого блока сравнения 4 вырабатывается сигнал единица, который через блок синхронизации 7 разрешает первому блоку памяти 3 запомнить значение процесса,в данный момент времени. По этому же сигналу рассматриваемое значение процесса с выхода аналогоцифрового преобразователя 2 переписывается в сумматор 8, и дальнейшее предсказание значений процесса теперь будет происходить относительно этого значения. Е(ли же первая производная процесса на данном интервале дискреуизации имеет отрицательный знак, то второй блок сравнения 5 вырабатьшает сигнал об изменении знака первой производной, Этот сигнал через блок синхронизации 7 разрешает первому блоку памяти 3 запомнить рассматриваемое значение процесса. По этому же сигналу данное значение процесса переписывается из аналого-цифрового преобразователя 2 в сумматор 8. После этого блок синхронизации 7 не выдает разрешающих сигналов на выполнение последующих операций вплоть до момента следующего аналого-цифрового преобразователя. Если теперь на следующем интервале дискретизации первая производная процесса сохранит отрицательный знак, то по сигналу со второго блока сравнения 5 постоянное приращение будет вычитаться из значе ния процесса, предсказанного в .предыдущий момент времени. . В том случае, когда первая производная процесса станет равной нулю с точностью до 1д{91: 1Ш) ; третий блок сравнения 6 вырабатывает сигнал, который через блок синхронизации 7 передает в первый блок памяти 3 знак первой производной. Кроме того, этот сигнал запрещает дередачу информации из второго блока памяти 9 в сумматор 8. Поэ1ому в сумматоре 8 предсказанное значение сохраняется постоянным..Таким образом все устройство начинает работать в режиме Предсказателя нулевого порйдка и работает так до тех пор, пока первая производная процесса не изме нит свой знак. Предположим, что на некотором интервале дискретизации знак первой производной стал положительным. В этом случае второй бло сравнения 5 вырабатывает сигнал, ко рый через блок синхронизации 7 пере дает в первый блок памяти 3 знак пе вой производнрй процесса. Этот же сигнал и отсутствие управляю1чего:сигнала с третьего блока сравнения б разрешают передачу постоянного пр ращения из второго блока 9 в сумматор 8 иустройство начинает работать в соответствии с выше описанным алгоритмом. Дополнительно введенный третий блок сравнения, анализируя величину первой производной и воздействуя на один из управляющих входов сумматора, переводит предлагаемое устройство либо в режим предсказателя нулевого порядка, либо в режим устройства-прототипа. , Вследствие этого повы-г шается коэффициент сжатия при обработке отдельных участков процесса, а следовательно, повышается и общий коэффициент сжатия. . Формула, изобретения Устройство для сжатия информации, содержащее коммутатор, выход которого подключен ко входу аналого-цифрового преобразователя, первый выход которого соединен с информационным входом первого блока буферной пзмя- ти и первым входом сумматора, второй блок памяти, который подключён ко второму входу сумматора, первый блок сравненг.я, первый вход кото)рого соединен со вторым выходом аналогоцифрового преобразователя, третий выход которого подключен к первому входу второго блока сравнения, первый выход которого соединен с третьим входом сумматора, выход которого подключен ко второму входу первого блока сравнения, выход первого блока сравнения и .второй выход второго блока сравнения подключены соответственно к первому и второму входам блока синхронизации, выход которого соединен с управл яющими входами коммутатора, сумматор а, первого и второго блока сравнения и первого блока памяти, о тличающееся тем, что, с целью повышения информационной емкости путем увеличения коэффициента сжатия устройства, в него введен третий блок сравнения, первый вход которого соединен с третьим выходом аналого-цифрового преобразователя, второй вход третьего блока сравнения подключен к выходу сумматора, который соединен со вторым входом второго блока сравнения , управляющий вход третьего блока сравнения подключен к выходу блока синхронизации, третий вход которого соединен с выходом третьего блока сравнения и с четвертым входом сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 458851, кл. G 08 С 19/28, 07.01.74. , 2.Авторское свидетельство СССР по заявке № 2602383/18-24, кл. G 08 С 19/28, 22.08.78 (прототип) .

Авторы

Даты

1980-11-15—Публикация

1978-12-25—Подача