Изобретение относится к вычислительной технике и может быть использовано для.высокоскоростной обработки входной информации, представленной в цифровом коде.

Суть обработки, выполняемой устройством, заключается в аппроксимации входного сигнала, представленного последовательностью цифровых кодов, степенным полиномом, и вычислении коэффициентов этого полинома, усредненных производных интер- и экстраполяции

Цель изобретения - повышение быстродействия.

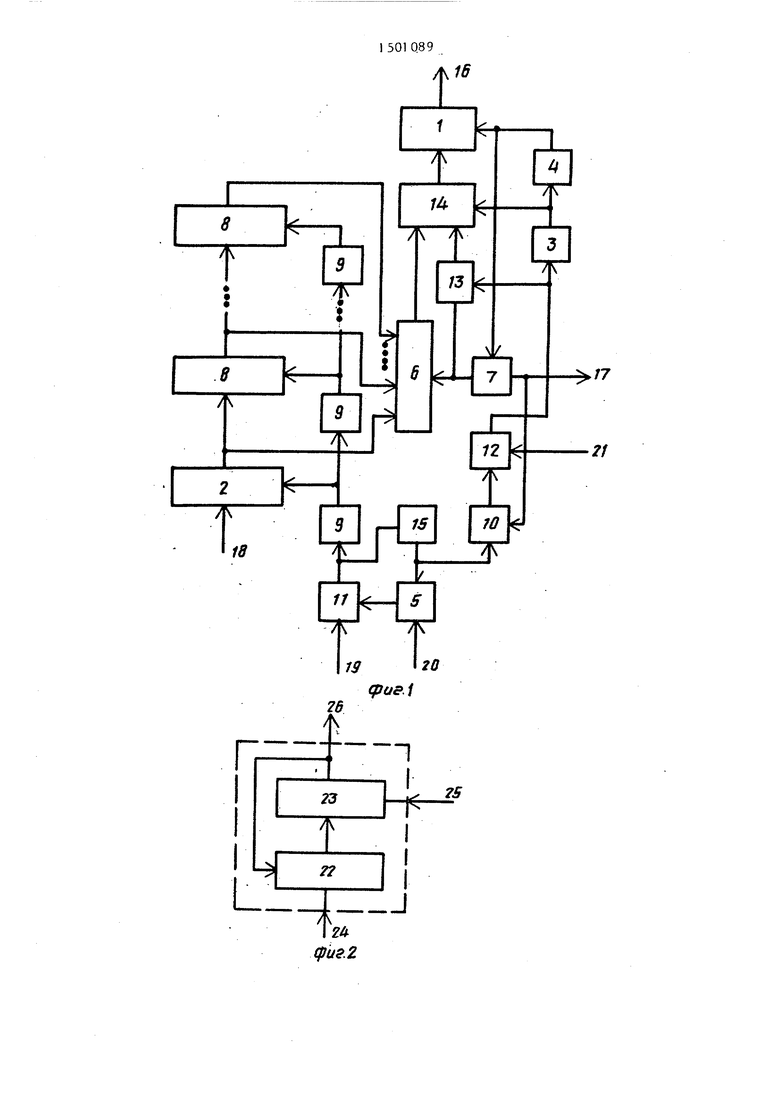

На фиг.1 представлена блок-схема процессора; на фиг„2 - блок-схема накапливающего сумматора.

Процессор содержит выходной сумматор 1 , накапливающий суьгматор 2, элементы 3 и 4 задержки, триггер 5, коммутатор 6, счетчик 7, накапливающие сумматоры 8, элементы 9 задержки, триггер 10, элементы И 11 и 12, -блок 13 памяти коэффициентов, блок 14 умножения, .счетчик 13, информационный выход 16 процессора, выход .17 сигнала готовности результата,информационный вход 18, вход 19 первой тактовой пох ледовательности, вход

00

со

150

20 запуска и вход 21 второй тактовой последовательности

Накапливающие сумматоры 2 и 8, а также выходной сумматор I содержат комбинационный сумматор 22, регистр 23, информационный вход 24, вход 25 разрешения записи и выход 26„

Рассмотрим основные математические соотношения, положенные в основу изобретенияо

Пусть функция непрёрьгансго аргут мента f(t) заданй на множестве дискретных равноотстоящих точек с шагом &t и образует функцию.дискретного аргумента f(iut) f(i), содержащую

2N+1 точек Аппроксимируем f(i) полиномом

. г

) а„ + a,i + +

X + я т

о « h

Коэффициенты а находим из минимума среднеквадратической ошибки:

п N :

а Х V Z.i f(i), k 0,n. (l)

U-N

Использование выражений (l) связано с определенньми трудностями.

Рассмотрим более простой и быстрый способ обработки В таблице представлены одно-, двух- и трехкратные суммы входной последовательности f(i).

| название | год | авторы | номер документа |

|---|---|---|---|

| Субоптимальный нелинейный фильтр | 1990 |

|

SU1714618A1 |

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Адаптивный цифровой измеритель параметров сигнала | 1981 |

|

SU1013867A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для измерения параметров частотных датчиков | 1989 |

|

SU1705757A1 |

| Устройство для градуировки датчиков силы | 1989 |

|

SU1682845A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для быстрого вычисления характеристик полиномов N-ой степени, аппроксимирующих входной сигнал, представленный в виде последовательности цифровых кодов. Цель изобретения - повышение быстродействия. Процессор содержит /п+1/ накапливающих сумматоров, выходной сумматор, блок умножения, блок памяти, два счетчика, коммутатор, элементы задержки и способен принимать входные коды с периодом, равным времени суммирования в накапливающем сумматоре. Принцип работы процессора связан с переходом от сумм вида ξХKB(X) к суммам вида ξ...ξВ(X). на первом этапе работы выполняется многократное суммирование входного сигнала. По окончании заданного объема выборки производится расчет конечных результатов обработки путем умножения многократных сумм входных кодов на постоянные коэффициенты. Процессор позволяет определять коэффициенты аппроксимирующего полинома, многократные интеграторы и усредненные производные входного сигнала, а также решать задачи интер- и экстраполяции. 2 ил., 1 табл.

,-к

i f(i) 2Рз - (2N+3)F2 +

+ (N + 1)

Подставляя (2) в (О, получаем ао bo,F, + b,,F + b.jF,;

, + b,2F

(1J 2

j - J,

где Ъ

J

b«.F, + + ,

- постоянные коэффициенты, цолзгчающиеся после приведения подобных членов.

Аналогичным образом могут быть получены выражения для коэффициенто аппроксимирующих полиномов и при

n+

N.

(3)

Выражения (З) значительно проще (1), так как предполагают только

входной функции

/(i)«Cf;; i) ka,/;.o,

и, таким образом, эта производная может быть вычислена через многократные интегралы. Зная коэффициенты ац, нетрудно рещить задачу интер- и экстраполяции:

.

W U (

f(t).(i )

&t

.

n+i

0

5

Z.C;F;, (4) .

где С; - постоянные коэффициенты

Таким образом, поскольку коэффициенты аппроксимирзпощего полинома п-й степени представляют собой линей- ную комбинацию интегралов , i 1, n + 1, входной функции f, то и любое линейное преобразование этого полинома также является линейной комбинацией указанных величин

Увеличение области аппроксимации (аппроксимация по выборке нарастающего объема) приводит к смещению центра аппроксимации - положения точки to, и к изменению коэффициентов Ь ;j (З), С; (4) и т.п., но не изменяет характер внутрицикловой обработки входной последовательности - многократного интегрирования. Окончательный результат обработки зависит только от коэффициентов, на которые умножаются эти интегралы

Процессор работает следующим образом

В исходном состоянии все сумматоры I, 2, 8 и счетчик 7 обнулены,счетчик 15 находится в исходном состоянии, определяемом заданным числом пересчета 2N+1о Триггеры 5 и 10 - в нулевом состоянии. В блоке 13 памАти записаны коэффициенты, соответствующие функции, которую должен выполнят процессор.

Запуск процессора происходит после подачи на вход 20 сигнала, которы переключает триггер 5 и открывает элемент И 11„ На вход 18 поступают обрабатываемые коды, сопровождаемые тактовым сигналом с входа 19, Первое значение информационного сигнала f(-N) поступает на вход 18 сумматора 2 и складывается с его предшествующим (нулевым) содержимым. Результат сложения записывается в регистр 23 сумматора 2 тактовым сигналом с входа 19, задержанным на первом элементе 9 задержки Аналогичным образом f(-N) с сумматора 2 поступает на вход следующего сумматора 8 и записывается в него сигналом с второго элемента задержки 9 и ТоДо В результате во всех сумматорах 2 и 8 будет записана в.еличина f(-N), Следующий тактовый сигнал с входа 19 может поступить до окончания суммирования во всех сумматорах 8, но задержка должна быть такой, чтобы новый тактовый сигнал не помешал процессу суммирования на предшествующем такте Поскольку разрядность сумматоров В увеличивается по мере удаления от входа устройства, максимальное время суммирования будет у последнего сумматора Во Это время и определяет максимальную скорость приема информации

Второй информационный код f(-N+l) на комбинационном сумматоре 22 сумматора 2 складывается с содержимым реь

й 5010В9б

гистра 23, а второр тяктовын сигнал записывается в регистр 23 сумматора 2 величину f(-N) + f (-Ы+1)Затем в первом сумматоре 8 получаем 2f(-N)+ + f(-N+1) и (cMj таблицу). В результате в сумматоре 2 накапливается однократная, во втором сумматоре В - двухкратная и ТоД суммы

IQ входного сигнала Процесс продолжается до тех пор, пока не будет достигнут требуемый объем выборки, о чем свидетельствует сигнал с выхода счетчика 15, который переключает

15 триггеры 5 и 10, закрывая элемент И 11 и открывая элемент И 12 На вход процессора начинают поступать тактовые сигналы по входу 21

Нулевое содержимое счетчика 7 пос2Q тупает на коммутатор 6 и обеспечивает подключение сумматора 2 к входу блока 14 умножения Кроме того,нулевой код подается и на адресный вход блока 13 памяти, в нулевой ячейке

25 которого записано значение коэффициента, стоящего перед однократной суммой входного сигнала По тактовому сигналу с входа 21 происходит считывание этого коэффициента из блока 13

30 памяти на вход блока 14 умножения Кроме того, этот сигнал, пройдя элемент 3 задержки, запускает блок 14 умножения, на выходе которого формируется произведение однократной суммы на соответствующий коэффициент По окончани и умножения и суммирования в сумматоре 1 сигнал с выхода элемента 4 задержки записывает результат в регистр 23 сумматора 1 и

40 увеличивает на единицу содержимое счетчика 7 Новое содержимое счетчика 7 обеспечивает подачу на вход блока 14 умножения содержимого второго сумматора В и соответствующего

45 коэффициента из блока 13 памяти и .

35

В дальнейшем процесс протекает аналогично, пока не будут опрошены

все сзгмматоры 8 и соответствующие ячейки блока 13 памяти По окончании этого процесса на выходе сумматора 1 появляется результат обработкИоПос- ледний тактовый сигнал по входу 21,

обеспечивающий выч.исление этого результата, вызьгоает переполнение счетчика 7. Его сигнал переключает триггер 10, закрывает элемент И 12 и поступает на выход 17, сигнализируя о готовности результата обработки.

Формула изобретения

Процессор аппроксимационной обработки информации, содержащий два триггера, два счетчика, коммутатор.

15010898

2,.с.,п) соединен с выходом (i-l)- го элемента задержки и входом разрешения записи (i-l)-ro накапливающего сумматора, выход которого соединен с информационным входом i-ro накапливающего сумматора и (1-1)-м информационным входом коммутатора, п-й информационный вход которого

блок памяти коэффициентов, блок умно- ю соединен с выходом п-го накапливаюжения, выходной сумматор и первый накапливающий сумматор, причем вход запуска процессора соединен с входом установки в 1 первого триггера, выход разрядов первого счетчика соединен с адресным входом блока памяти коэффициентов, выход которого соединен с входом множителя блока умножения, выход выходного сумматора соединен с выходом процессора, отличающийся тем, что, с целью повьшения быстродействия, в него введены п+2 элементов задержки, где п+1 - степень аппроксимирующего полинома, с второго по п-й накапливающие сумматоры и два элемента И, причем вход первой тактовой последовательности процессора соединен с первым входом первого элемента И, выход которого соединен со счетным входом второго счетчика, выход переполнения которого соединен с входами установки соответственно в 1 второго триггера и в О первого триггера, прямой выход которого соединен с вторым входом первого элемента И, выход которого соединен с с входом первого элемента задержки, вход i-ro элемента задержки (где i

щего сумматора, вход разрешения записи которого соединен.с выходом п-го элемента задержки, информационный вход первого накапливающего сумматора соединен с информационным входом процессора, .вход второй тактовой последовательности, которого соединен с первым входом второго элемента И, второй вход которого соединен с прямьм выходом второго триггера, вход установки в О которого соединен с выходом переполнения первого счетчика и выходом сигнала готовности результата процессора, выход второго элемента И соединен с входом разрешения считывания блока памяти коэффициентов и входом ()-ro элемента задержки, выход которого соединен с тактовьм входом блока умножения и входом (п+2)-го элемента за- дер.жки, выход которого соединен с входом разрешения записи выходного сумматора и счетным входом первого счетчика, выход разрядов которого соединен с адресным входом коммутатора, выход которого соединен с входом множимого блока умножения,выход которого соединен с информационным входом выходного сумматора

26

gju&.

| Авторское свидетельство СССР № 1246775, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-09—Подача