(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ С ВРЕМЕННЫМ УПЛОТНЕНИЕМ КАНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Устройство для сжатия информации | 1976 |

|

SU567174A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056249A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Адаптивное адресное устройство | 1978 |

|

SU750538A1 |

| Устройство для сжатия информации | 1981 |

|

SU970421A1 |

| Аналого-цифровой функциональный преобразователь | 1988 |

|

SU1508249A1 |

| Многоканальное устройство для передачи информации с временным уплотнением каналов | 1978 |

|

SU720754A1 |

I

Изобретение относится к электросвязи и может быть использовано в многоканальных системах передачи данных с временным разделением каналов.

Известно многоканальное устройство для передачи данных с временным уплотнением каналов, содержащее регистр текущей выборки, информационный вход которого соединен с входом устройства, первый синхронизирующий вход которого соединен с тактовым входом блока буферной памяти и вычитающим входом счетчика заполнения, блок оперативной памяти, блок cpaвнeнияJ элемент ИЛИ и элемент И 1.

Однако это устройство обладает сравнительно низким коэффициентом сжатия данных и, следовательно, недостаточно разгружает канал связи при передаче данных измерений случайных процессов с существенной нестационарностью.

Цель изобретения - уменьшение требуемой полосы частот за счет сокращения избыточности данных (увеличения коэффициента сжатия данных).

Для этого в многоканальное устройство передачи данных с временным уплотнением каналов, содержащее регистр текущей выборки, информационный вход которого соединен с входом устройства, первый синхронизирующий вход которого соединен с тактовым входом блока буферной памяти и вычитающим входом счетчика заполнения, блок

5 оперативной памяти, блок сравнения, элемент ИЛИ, элемент И, введены два триггера, блок задержки, два ключа, арифметический блок, блок синхронизации и счетчик выборок, вход которого соединен с входом блока синхронизации и входом регистра текущей

10 выборки, а выход подключен к первому входу арифметического блока, второй вход которого соединен с выходом регистра текущей выборки, а третий вход соединен с первым входом блока сравнения и подключен к первому выходу блока оперативной памяти,

15 синхронизирующий вход которого подключен к выходу блока синхронизации, другие выходы которого подключены к синхронизирующим входам регистра текущей выборки, счетчика выборок, арифметического

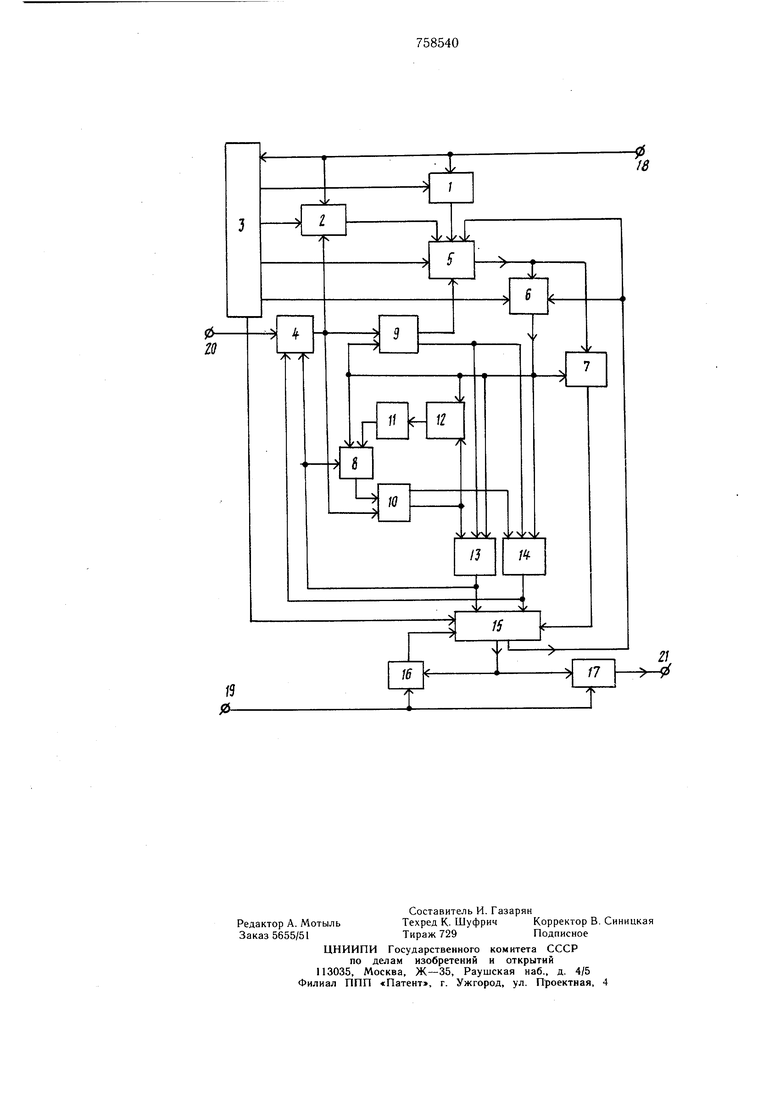

20 блока и блока сравнения, второй вход которого, объединенный с входом первого ключа, соединен с выходом арифметического блока, управляющий вход которого соединен с первым выходом первого триггера. ВХОД установки нуля которого соединен с соответствующими входами второго триггера и счетчика выборок и подключен к выходу элемента ИЛИ, первый вход которого подключен ко второму синхронизирующему входу устройства, а второй вход соединен со вторым управляющим входом блока оперативной памяти и выходом третьего элемента И, третий вход элемента ИЛИ соединен с первыми управляющими входами второго ключа, блока оперативной памяти и выходом второго элемента И, первые входы элементов И соединены с управляющим входом первого ключа, вторым управляющим входом второго ключа и входом первого триггера и подключены к выходу блока сравнения, вторые входы первых двух элементов И подключены ко второму выходу второго триггера, третьи входы второго и третьего элементов И подключены ко второму выходу первого триггера, а второй вход третьего элемента И соединен с первым выходом второго триггера, вход которого соединен с выходом второго ключа, вход которого подключен к выходу блока задержки, выход которого соединен с выходом первого элемента И, выход первого ключа соединен с входом блока оперативной памяти, третий управляющий вход которого подключен к выходу счетчика заполнения, а второй выход соединен с суммирующим входом счетчика заполнения и входом блока буферной памяти, выход которого подключен к выходу устройства. Ма чертеже представлена функциональная электрическая схема устройства. Устройство содержит регистр текущей выборки 1, счетчик выборок 2, блок синхронизации 3, элемент ИЛИ 4, арифметический блок 5, блок сравнения 6, ключи 7 и 8, первый 9 и второй 10 триггеры, блок задержки 11, первый 12, второй 13 и третий 14 элементы И, блок оперативной памяти 15, счетчик заполнения 16, блок буферной памяти 17, вход 18, первый 19 и второй 20 синхрони,зирующие входы и выход 21. Устройство работает следующим образом. Для простоты описания условимся, что данные, поступающие на вход, относятся к одному информационному каналу. Перед началом работы счетчик выборок 2 и оба триггера 9, 10 устанавливаются в нулевое состояние сигналом, поступающим через второй синхронизирующий вход устройства 20 и элемент ИЛИ 4. Сжатие данных, а также увеличение коэффициента сжатия достигаются за счет того, что вместо исходной последовательности отсчетов нестационарной реализации f(t.) в канал связи передаются значения коэффициентов М (или М и 0) аппроксимирующих полиномов fj(t) нулевой Ро(1;) (или первой Г(1)) степени. Поскольку аппроксимирующие полиномы строятся в виде рядов Фурье fj(t) Д Vif.-H; с системой степенных ортонормированных базисных функций с{)а(й) BQ; q)t(4) Bo + Bit|.} и коэффициентами разложения V. 2 :f (tl) 9:(t), соответствующие 1 1 значения среднего квадрата ощибки аппроксимации 8 могут быть вычислены по формулам:а)для полинома нулевой степени V-ljU i-) -f(b)J -m2; (1) б)для полинома первой степени lTrl,f)-f(b) K-nt -iV() () (2) Пулевое состояние счетчика выборок 2 соответствует началу интервала аппроксимации входных данных полиномом нулевой или первой степени. Выборки входного процесса f(t) поступают через равные промежутки времени At на вход регистра текущей выборки 1. С поступлением очередной выборки содержимое счетчика выборок увеличивается на единицу. Момент поступления на вход системы очередного отсчета фиксируется также в блоке синхронизации 3 для определения синхроструктуры алгоритма работы всей системы на протяжении времени At. Код выборки с выхода регистра 1 при наличии соответствующего синхросигнала считывания из блока 3 подается в арифметический блок 6, где начинается расчет текущих значений коэффициентов полиномов Мк , 0к для к выборок по реккурентным формулам М . V - JiiVi-i±f(K). т И + 1 д к-1 вк-и-г {к) « К+1 здесь , 0д... -соответствующие значения коэффициентов М., Q на интервале, содержащем (к-1) выборок, причем Мр f(0),), ео о. Указанные значения хранятся в ячейках блока оперативной памяти 15 и поступают в процессе вычислений в блок 6 по синхросигналам считывания. Вместе со значениями MK-I ®к-л 43 блока оперативной памяти 5 в блок сравнения 6 поступает величина допустимой погрещности аппроксимации 8д. Значение к поступает на вход арифметического блока из счетчика 2. При нулевом, состоянии триггера 9, т.е. при единичном сигнале на его первом выходе и соответственно на управляющем входе арифметического блока 5, в последнем в| 1числяется средний квадрат погрешности SOK аппроксимации f(L) полиномом нулевой folfl) степени. Значение 6Д поступает на второй вход блока сравнения 6. В случае 5 5 на выходе блока сравнения вырабатывается сигнал малого уровня со (Of, который открывает ключ 7 и пропускает коды величин Л.Уц, 9ц в блок 15 где они фиксируются на месте соответствующих величин М,, Х.,, ©к-, . На этом работа системы прекращается до поступления очередного отсчета в регистр текущей выборки 1. В случае 5 ЗА блок сравнения 6 вырабатывает сигнал высокого уровня (о (ог, который переводит первый триггер 9 в единичное состояние, вследствие чего на входах первого элемента И 12 появляются единичные сигналы. Выходной импульс элемента И 12 задерживается в блоке задержки 11 на время второго цикла вычислений Тгц Второй цикл вычислений начинается в арифметическом блоке 5 с момента изменения сигнала на его управляющем входе. Вычисляется средний квадрат §, погрещности аппроксимации данных(f(i); i O-f-K) полиномом первой степени f(i). Значение блока 6 по соответствующему синхросигналу поступает на второй вход блока сравнения б и сравнивается с допуском бд. Блок сравнения выбирает сигнал Si l ((it, если со.| Рассмотрим случай ш со j. Он свидетельствует о превыщении погрещности аппроксимации данных-(i); i 0гк} полиномом как нулевой, так и первой степени на интервале в к отсчетов. И в то же время нулевое состояние второго триггера 10 свидетельствует о возможности аппроксимации данных {f(i)J на интервале (к-1)| полиномом нулевой степени. Это дает основание для передачи в канал связи, т.е. перезаписи в блок буферной памяти 17 из блока оперативной памяти 15 коэффициента М,,, необходимого для восстановления f(i) на приемной стороне полиномом нулевой степени fo(i) с погрещностью, не превыщающей 6д. Перезапись осуществляется по единичному сигналу, поступающему на первый управляющий вход блока оперативной памяти 15 с выхода второго элемента И 13, т.е. в том случае, если на всех трех входах элемента И 13 присутствуют единичные сигналы:а)с выхода блока сравнения 6 (и wa); б)со второго выхода триггера 9; в)с первого выхода триггера 10. При перезаписи М содержимое счетчика заполнения 16 увеличивается на единицу. Единичный сигнал выхода элемента И 13, проходя элемент ИЛИ 4, обнуляет оба триггера 9, 10 и счетчик заполнения 16, а также разрывает цепь между блоками 10 и 11, препятствуя выходному импульсу блока задержки 11 изменить состояние триггера 10 по истечении времени Тгд;. На этом работа системы заканчивается до поступления очередного отсчета в регистр 1. Рассмотрим случай сигнала ш и i на выходе блока сравнения 6 при заверщении второго цикла работы системы. Сигнал свидетельствует о возможности аппроксимации данных f(i) полиномом первой степени f(i) на интервале о.-к Сигнал ш, открывает ключ 7 и значения MH,YK ,вц, необходимые для дальнейщих расчетов, запоминаются в соответствующих ячейках блока оперативной памяти 15. Импульс, появляющийся на выходе блока задержки 11 по истечении времени Тгд, проходит ключ 8 и переводит триггер 10 в противоположное состояние. На этом работа системы прекращается до поступления очередного отсчета в регистр текущей выборки 1. Дальнейшая работа системы проходит при единичном состоянии триггера 9, т.е. при нулевом сигнале на управляющем входе арифметического блока 5. С поступлением очередного отсчета к к + 1) проводится вычисление 5( и сравнение с допуском бд в блоке 6. При сигнале ш oji на выходе блока 6 значения Мк,Уц, 6 переписываются в блок оперативной памяти 15. При со cot интервал аппроксимации прерывается, т.к. SIK А На выходе третьего элемента И 14 возникает единичный сигнал, который воздействует на второй управляющий вход блока оперативной памяти 15. По данному сигналу из блока 15 в блок буферной памяти 17 переписываются последовательно значения М., и 9к-( , необходимые для восстановления данных {f(i)} на приемной стороне полиномом первой степени f(i) с погрещностью, не превышающей бд При перезаписи к содержимому счетчика последовательно добавляются две единицы. Сигнал с выхода элемента И 14, пройдя элемент ИЛИ 4, задает начальные условия для нового интервала аппроксимации, т.е. устанавливает в нуль оба триггера 9, 10 и счетчик выборок 2. Блок буферной памяти 17 предназначен для выравнивания во времени неравномерного потока данных, поступающих на его вход и представляющих собой либо коэффициент М для полинома fo(i), либо коэффициенты Ми© для полинома f(i). Для выравнивания данных их считывание из блока буферной памяти 17 на выход 20 системы производится с равномерной частотой по сигналам, поступающим на первый синхронизирующий вход устройства 18. При считывании содержимое счетчика уменьшается на единицу. Счетчик 16 в зависимости от числа заполненных ячеек блока буферной памяти 17 устанавливает значение бд, с которым производится сравнение докя блоке 6, причем большему заполнению со5 тветствуют большие значения . Сравнительные испытания показали, что предлагаемое устройство позволяет приблизительно на порядок повысить коэффициент сжатия данных и соответственно снизить требования к полосе частот канала связи по сравнению с прототипом. Формула изобретения Многоканальное устройство передачи данных с временным уплотнением каналов, содержащее регистр текущей выборки, информационный вход которого соединен с входом устройства, первый синхронизирующий вход которого соединен с тактовым входом блока буферной памяти и вычитающим входом счетчика заполнения, блок оперативной памяти, блок сравнения, элемент ИЛИ, элемент И, отличающееся тем, что, с целью уменьшения требуемой полосы частот за счет сокращения избыточности данных, введены два триггера, блок задержки, два ключа, арифметический блок, блок синхронизации и счетчик выборок, вход которого соединен с входом блока синхронизации и входом регистра текущей выборки, а выход подключен к первому входу арифметического блока, второй вход которого соединен с выходом регистра текущей выборки, а третий вход соединен с первым входом блока сравнения и подключен к первому выходу блока оперативной памяти, синхронизирующий вход которого подключен к выходу блока синхронизации, другие выходы которого подключены к синхронизирующим входам регистра текущейвыборки, счетчика выборок, арифметического блока и блока сравнения, второй вход которого, объединенный с входом первого ключа, соединен с выходом арифметического блока, управляющий вход которого сое динен с первым выходом первого триггера, вход установки нуля которого соединен с соответствующими входами второго триггера и счетчика выборок и подключен к выходу элемента ИЛИ, первый вход которого подключен ко второму синхронизирующему входу устройства, а второй вход соединен со вторым управляющим входом блока оперативной памяти и выходом третьего элемента И, третий вход элемента ИЛИ соединен с первыми управляющими входами второго ключа, блока оперативной памяти и выходом второго элемента И, первые входы элементов И соединены с управляющим входом первого ключа, вторым управляющим входом второго ключа и входом первого триггера и подключены к выходу блока сравнения, вторые входы первых двух элементов И подключены ко второму выходу второго триггера, третьи входы второго и третьего элементов И подключены ко второму выходу первого триггера, а второй вход третьего элемента И соединен с первым выходом второго триггера, вход которого соединен с выходом второго ключа, вход которого подключен к выходу блока задержки, выход которого соединен с выходом первого элемента И, выход первого ключа соединен с входом блока оперативной памяти, третий управляющий вход которого подключен к выходу счетчика заполнения, а второй выход соединен с суммирующим входом счетчика заполнения и входом блока буферной памяти, выход которого подключен к выходу устройства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 531158, кл. G 06 F 15/00, 1976 (прототип).

Авторы

Даты

1980-08-23—Публикация

1978-06-06—Подача