1325- 13

Изобретение относится к янтомати,

ке и может быть использовано для управления объектами с приводами на основе шаговых двигателей, требующими высркостабильных скоростей вращения в широком диапазоне их задания в виде цифровых кодов.

Цель изобретения - повьпиение точности преобразования кода требуемой скорости в частоту импульсов за счет получения однозначности преобразования при разгоне и торможении двигателя.

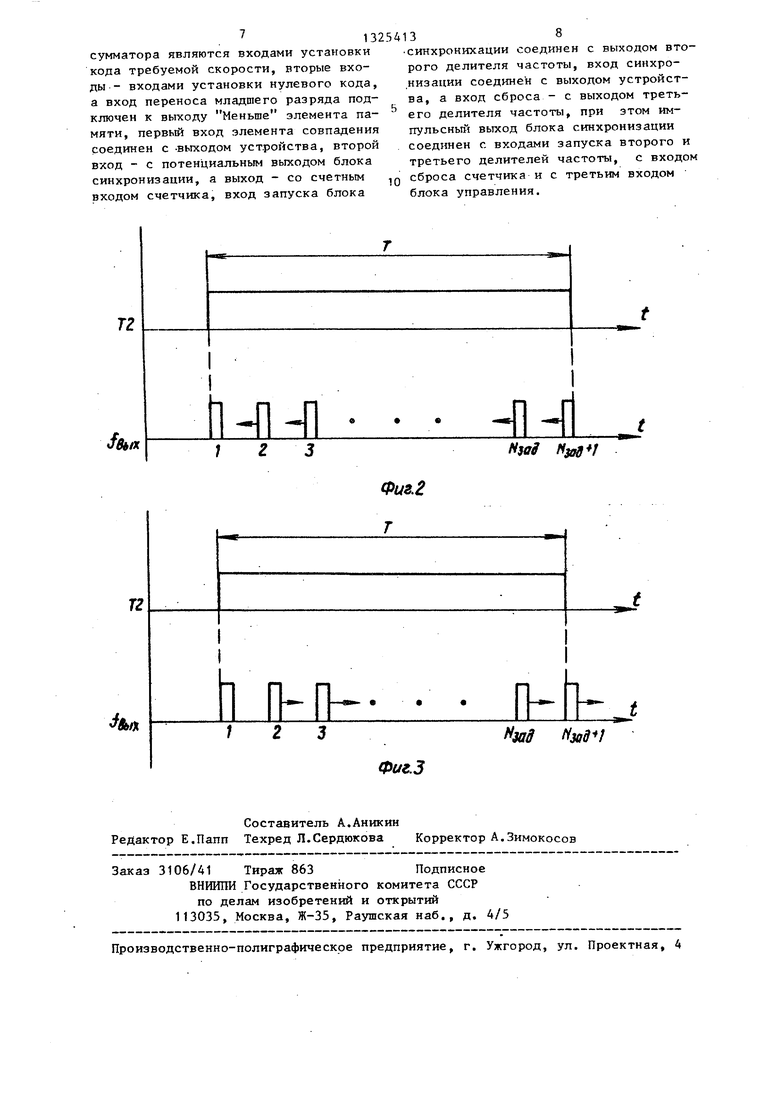

F a фиг, 1 приведена блок-схема предла аемого устройства; на фиг. 2 и 3 - временные диаграммы работы счетчика соответственно при разгоне и торможении двигателя.

Устройство содержит задающий генератор 1, первый 2 делитель частоты, реверсивньй счетчик 3, счетчик Д, блок 5 сравнения кодов, элемент 6 памяти, блок 7 управления, второй 8 и третий 9 делители частоты, блок 10 синхронизации, сумматор 11 и элемент 12 совпадения.

Первый делитель 2 частоты содержит счетчик 13 импульсов и блок 14 совпадения кодов. Элемент 6 памяти содержит первый 15 и второй 16 D- триггеры. Блок 7 управления состоит из первого 17 и второго 18 элементов совпадения. Второй делитель 8 частоты содержит счетчик 19 импульсо и блок 20 совпадения кодов. Третий делитель 9 частоты содержит счетчик 21 импульсов и блок 22 совпадения кодов. Блок 10 синхронизации имеет первый 23 и второй 24 RS-триггеры и элемент 25 совпадения.

Устройство работает следующим образом.

Частотный сигнал выхода задающего генератора 1 поступает на входы первого 2, второго 8 и третьего 9 делителей частоты, имеющих коэффициенты деления соответственно

К

1

К и K;j.

Выход 2 частоты является ства.

вих

(П

f

ВПК

гек

-частота сигнала на выходе устройства ,

-частота сигнала задающего генератора-,

К, коэффициент деления первого делителя частоты, численно равный значению ко- да на его управляющих входах,,

Первый 2, второй 8 и третий 9 делители частоты имеют одинаковое схемное решение и аналогичный принцип ра- боты. Например, импульсы частоты с выхода задающего генератора 1 поступают на счетньй вход счетчика 13 импульсов, которьш является счетным входом первого делителя частоты. Ниф- ровой код с выходов счетчика 13 импульсов сравнивается блоком 14 совпадения кодов с кодом, поступающим на управляющие входы первого 2 усилителя частоты, В момент равенства кодов на выходе блока 14 совпадения

вырабатывается сигнал , который

5

и является выходным сигналом первого делителя 2 частоты. После подачи сигнала на вход обнуления счетчика 13

5 импульсов, который является входом запуска первого делителя 2 частоты, цикл работы повторяется.

Импульсный сигнал с выхода второго делителя 8 частоты поступает на

0 вход запуска блока 10 синхронизации, устанавливает первый триггер 23, который разрешает прохождение импульса выходной частоты через элемент 25 совпадения блока 10 синхронизации на вход запуска третьего делителя 9 частоты, вход сброса счетчика 4 и на суммирующий или (в зависимости от сигналов на выходах или элемента 6 памяти) вычитающий вход

Q реверсивного счетчика 3, на выходе которого формируется код коэффициента деления К первого делителя частоты, а также сбрасывает первый триггер 23 и устанавливает второй триггер

g 24 блока 10 синхронизации. Сигнал с потенциального выхода блока синхронизации (прямой выход второго триггера 24) разрешает прохождение импульсов выходной частоты через элемент 12 совпадения на счетный вход счетчика 4. Таким образом осуществляется синхронизация начала преобразования выходной частоты в код текущий ско- с импульсами выходной час5

тек 8ыу (первый импульс на фиг. 2

рости N то ты и 3),

Код текущей скорости fтeк. ходов счетчика 4 непрерывно сравнивается блоком 5 сравнения кодов с кодом заданной скорости N , поступающим с выходов сумматора Г1.

В момент появления импульса на выходе третьего делителя 9 частоты результат сравнения кодов текущей и заданной скорости переписывается с выходов и блока 5 сравнения кодов в первый 15 и второй 16 триггеры элемента 6 памяти. Этот импульс сбрасывает также второй триггер 24 блока 10 синхронизации, прекращая поступление импульсов fg(, на вход счетчика А.

Коэффициент деления Kj третьего делителя 9 частоты выбран таким образом, что выполняется соотношение

- f

ген

6ЫХ.Зад 1

(2)

где N

iiXA

ген

8ЫУ. 1о(А

К

го

-код заданной.скорости двигателя,

-частота сигнала задающего генератора,

-частота сигнала на выходе устройства, соответствующая заданной скорости двигателя N ;

-коэффициент деления третьего делителя 9 частоты.

Следующий импульс с выхода второделителя 8 частоты, поступающий на вход запуска блока 10 синхронизации, приводит к изменению коэффициента деления К первого делителя 2 частоты в зависимости от результата сравнения кода текущей скорости с кодом заданной скорости, полученного в предыдущем цикле преобразования, тем самым увеличивая или уменьЩая выходную частоту. Далее цикл преобразования выходной частоты в код повторяется.

Изменение кода коэффициента деления К neipBoro делителя 2 частоты производится до тех пор, пока не сравняется код , формируемый в счетчике 4, с кодом, поступающим с выходов сумматора 11.

Таким образом, в момент f

ых

f

выу-га

КОДЫ счетчика 4 и сумматора 11 совпадают, сигналы и на выходах блока 5 сравнения кодов отсутствуют и на выходах реверсивного счетчика 3 фиксируется код коэффици g окончания разгона, т.е. при достижении равенства кодов счетчика А и сумматора 11, в интервале преобразов ния Т помещается число периодов вы ходкой частоты f g,|x , равное Nj«,.

gQ Стрелками показано направление дискретного изменения периода импульсов выходной частоты при разгоне двигателя (увеличение частоты).

ента деления венству

К.

соответствующий ра

f

ВИХ, ioiA

55 При задании кода скорости %af N fg частота на выходе устройства начинает уменьшаться (3)(торможение двигателя), так как импульсы с блока синхронизации постуВыбор коэффициента деления Kj второго делителя 8 частоты определяется требуемой скоростью разгона двигателя (чем он больше 5 тем меньше скорость разгона) и должен удовлетворять соотношению

К, - (Кя+п 2К

i

где п , 1,

До подачи на вход сумматора 11 кода заданной скорости с его выходов снимается нулевой код и частота на выходе устройства минимальна.

После подачи на вход сумматора

N

зад

частота на выходе устройкода

ства f.,,.. начинает увеличиваться

вы

5

(разгон двигателя), так как импульсы с блока 10 синхронизации поступают на вычитающий вход реверсивного счетчика 3, задающего коэффициент деления К первого делителя 2 частоты.

Выход .элемента 6 памяти подключен к входу переноса младшего разряда сумматора 11, на вторые входы которого подается нулевой код. Таким образом, при увеличении выходной час- 0 тоты (разгоне) код заданной скорости увеличивается в сумматоре 11 на единицу и изменение коэффициента деления К первого делителя 2 частоты прекращается при

1.

5

N,

N.

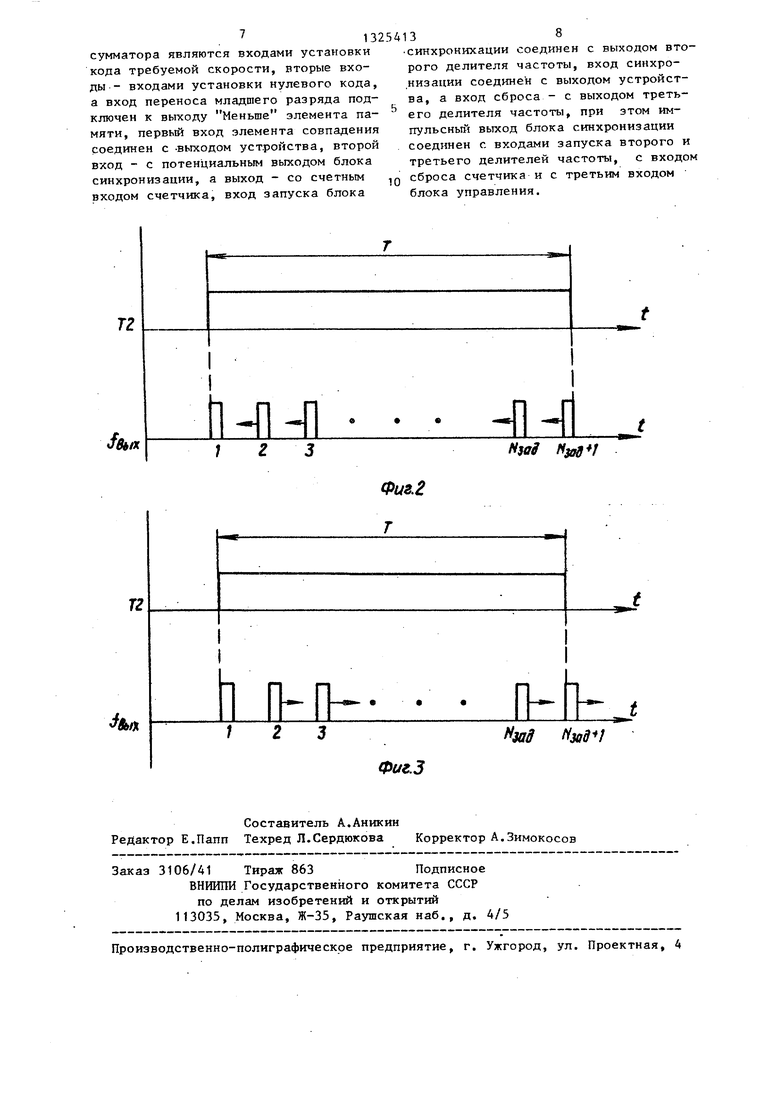

тек ioft На фиг. 2 приведена временная диаграмма работы счетчика 4, в котором формируется, код текущей скорости

тск

за интервал преобразования

T./i-.

ген Из фиг. 2 видно, что к моменту

окончания разгона, т.е. при достижении равенства кодов счетчика А и сумматора 11, в интервале преобразования Т помещается число периодов вы ходкой частоты f g,|x , равное Nj«,.

Стрелками показано направление дискретного изменения периода импульсов выходной частоты при разгоне двигателя (увеличение частоты).

5

пают на суммирующий вход реверсивно- .го счетчика 3, и так как зод сигнал с выхода -i элемента 6 памяти на вход переноса сумматора 11 не поступает и изменение коэффициента деления первого 2 делителя частоты Kj прекращается при N N5, .

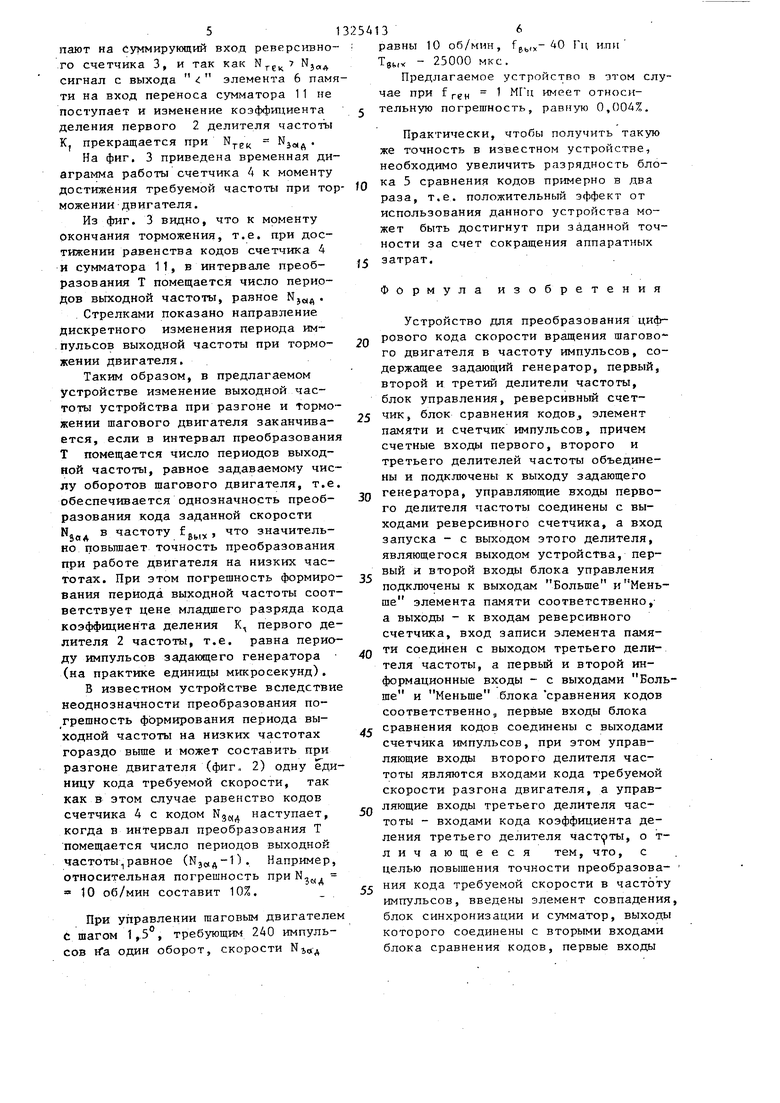

На фиг. 3 приведена временная диаграмма работы счетчика 4 к моменту достижения требуемой частоты при торможении двигателя .

Из фиг. 3 видно, что к моменту окончания торможения, т.е. при достижении равенства кодов счетчика 4 И сумматора 11, в интервале преобразования Т помещается число периодов выходной частоты, равное Nj.

Стрелками показано направление дискретного изменения периода импульсов выходной частоты при торможении двигателя.

Таким образом, в предлагаемом устройстве изменение выходной частоты устройства при разгоне и торможении шагового двигателя заканчивается, если в интервал преобразования Т помещается число пе1риодов выходной частоты, равное задаваемому числу оборотов шагового двигателя, т.е. обеспечивается однозначность преобразования кода заданной скорости Нцд . в частоту f g, , что значительно повьшает точность преобразования при работе двигателя на низких частотах. При этом погрешность (})ормиро- вания периода, выходной частоты соответствует цене младшего разряда кода коэффициента деления К, первого делителя 2 частоты, т.е. равна периоду импульсов задающего генератора (на практике единицы мрпсросекунд) .

В известном устройстве вследствие неоднозначности преобразования погрешность формирования периода выходной частоты на низких частотах гораздо вьше и может составить при разгоне двигателя (фиг. 2) одну единицу кода требуемой скорости, так как в этом случае равенство кодов счетчика 4 с кодом Njj,, наступает, когда в интервал преобразования Т помещается число периодов выходной частоты,равное (Нзо(. Например, относительная погрешность при N . 10 об/мин составит 10%.

При управлении шаговым двигателем t шагом 1,5°, требующим 240 импульсов rfa один оборот, скорости Nj

254136

равны 10 об/мин, fgj,,-40 Гц или Tg(,,v - 25000 МКС.

Предлагаемое устройство в -этом случае при fpgH Ш п имеет относн- 5 тельную погрешность, равную 0,004%.

Практически, чтобы получить такую же точность в известном устройстве, необходимо увеличить разрядность блоjg ка 5 сравнения кодов примерно в два раза, т.е. положительный эффект от использования данного устройства может быть достигнут при заданной точности за счет сокращения аппаратных

J5 затрат.

Формула изобретения

Устройство для преобразования циф2Q рового кода скорости вращения шагового двигателя в частоту импульсов, содержащее задающий генератор, первый, второй и третий делители частоты, блок управления, реверсивный счет25 чик, блок сравнения кодов, элемент памяти и счетчик импульсов, причем счетные входы первого, второго и третьего делителей частоты объединены и подключены к выходу задающего

jg генератора, управляющие входы первого делителя частоты соединены с выходами реверсивного счетчика, а вход запуска - с вьпсодом этого делителя, являющегося выходом устройства, первый и второй входы блока управления подключены к выходам Больше и Меньше элемента памяти соответственно,- а выходы - к входам реверсивного счетчика, вход записи элемента памя д ти соединен с выходом третьего делителя частоты, а первый и второй информационные входы - с выходами Больше и Меньше блока сравнения кодов соответственно, первые входы блока

сравнения кодов соединены с выходами счетчика импульсов, при этом управляющие входь второго делителя частоты являются входами кода требуемой скорости разгона двигателя, а управгл ляющие входы третьего делителя частоты - входами кода коэффициента деления третьего делителя част(ты, о т- личающееся тем, что, с целью повышения точности преобразова-

ния кода требуемой скорости в частоту импульсов, введены элемент совпадения, блок синхронизации и сумматор, выходы которого соединены с вторыми входами блока сравнения кодов, первые входы

35

сумматора являются входами установки кода требуемой скорости, вторые входы - входами установки нулевого кода, а вход переноса младшего разряда подключен к выходу Меньше элемента памяти, первый вход элемента совпадения соединен с -выходом устройства, второй вход - с потенциальным выходом блока синхронизации, а выход - со счетным входом счетчика, вход запуска блока

/л

/X

141-Л- Ч1Ч1 t

; г 3

Njai Njffgf/

8ыи

I

h fbib

1 г 3

%

Составитель А.Аникин Редактор Е.Папп Техред Л.Сердюкова Корректор А.Зимокосов

Заказ 3106/41 Тираж 863Подписное

ВНЙИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

8

10

синхронихации соединен с выходом второго делителя частоты, вход синхронизации соединен с выходом устройства, а вход сброса - с выходом третьего делителя частоты, при этом импульсный выход блока синхронизации соединен с входами запуска второго и третьего делителей частоты, с входом сброса счетчика и с третьим входом блока управления.

Njai Njffgf/

Физ.2

%

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для позиционного программного управления с самоконтролем | 1982 |

|

SU1072002A1 |

| Устройство для программного управления | 1984 |

|

SU1223209A1 |

| Устройство для управления шаговым электродвигателем | 1980 |

|

SU928592A1 |

| Цифровая система для программного управления двигателем | 1986 |

|

SU1320793A1 |

| Устройство для программного управления скоростью подачи | 1982 |

|

SU1067473A1 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1374395A1 |

| Устройство для управления шаговым двигателем | 1987 |

|

SU1607071A1 |

| Устройство для разгона и торможения электропривода | 1989 |

|

SU1725183A1 |

| Устройство для управления п-шаговыми двигателями | 1983 |

|

SU1144183A1 |

Изобретение относится к автоматике и может быть использовано для управления объектами с приводами на основе шаговых двигателей, требующими высокостабильных скоростей вращения в широком диапазоне их задания в виде цифровых кодов. Цель изобретения - повьш1ение точности преобразования кода требуемой скорости в частоту импульсов. Устройство содержит задающий генератор 1, первый 2делитель частоты, реверсивный счетчик 3, счетчик 4, блок 5 сравнения кодов, элемент 6 памяти, блок 7 управления, второй 8 делитель частоты, третий 9 делитель частоты, блок 10 синхронизации, сумматор 11 и элемент 12 совпадения. Точность преобразования достигается путем обеспечения однозначности преобразования при разгоне и торможении шагового двигателя, для чего в схему устройства введены элемент 12 совпадения, блок 10 синхронизации и сумматор 11. 3ил. (Л f/ l/IW l/ г 1 I 5 l CTl1| ТТЖ : Г 4f A 11 б ji TTT,

| Устройство для преобразования цифрового кода в частоту импульсов | 1972 |

|

SU595858A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для программного управления | 1984 |

|

SU1223209A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-28—Подача