Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в аналого-цифровых преобразователях.

Целью изобретения является повышение быстродействия устройства.

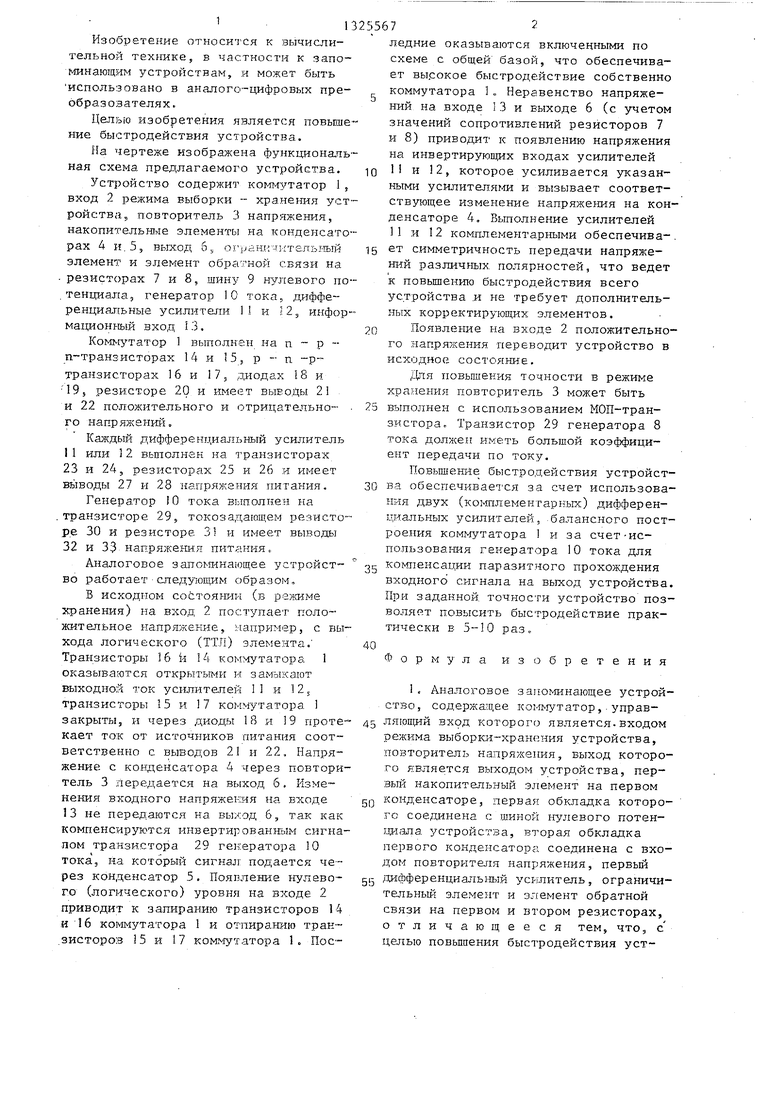

Fta чертеже изображена функтдиональ- нал схема предлагаемого устройства.

Устройство содержит коммутатор 1, вход 2 режима выборки -- хранения устройства, повторитель 3 напряжения, накопительн1.1е элементы на конденсаторах Д и. 55 выход б; orijarar iiTenbHbiH элемент и элемент обратной связи на резисторах 7 и 8, шину 9 нулевого по- тенциала, генератор 10 тока, дифференциальные усилители 1 и 12, инфор- мационртьгй вход i 3.

Комментатор 1 выполнан на п - р - п-транзисторах 14 и 15, р - п -р- транзисторах 16 и 17, диодах 18 и 195 резисторе 20 и имеет выводы 21 и 22 положительного и отрицательно- го напряжений.

Каждый дифференциальный усилитель I1 или I2 вьшолнен на транзисторах 23 и 24, резисторах 25 и 26 и имеет вьшоды 27 и 28 напряжения питания.

Генератор 10 тока выполнен на транзисторе 29, токозадагащем резистое 30 и резисторе 31 и имеет выводы 32 и 33 напряжения питания.

Аналоговое залоьшнаюиее устройство работает следующим образом,

В исходном состоянии (в режиме хранения) на вход 2 поступает полоительное напряжение, например, с выхода логического (ТТЛ) элемента. Транзисторы 16 k 14 ком;хгутатора 1 оказываются открытьми и замыкают выходной ток усилителей 1I и 12; транзисторы 15 и 17 коммутатора 1

закрыты, и через диоды 18 и 19 проте- 45 ляюпрй вход которого является-входом

кает ток от источников питания соответственно с выводов 21 и 22. Напряженке с конденсатора 4 через повторитель 3 /передается на выход 6. Изменения входного напряжения на входе 13 не передаются на выход 6, так как компенсируются инвертированным сигналом транзистора 29 генератора 10 тока, на который сигнал: подается через конденсатор 5. Появление нулевого (логического) уровня на входе 2 приводит к запиранию транзисторов 14 и 16 коммутатора 1 и отпираьшю транзисторов 15 и 17 коммутатора 1. Последние оказываются включенными по схеме с общей базой, что обеспечивает вы.сокое быстродействие собственно коммутатора 1„ Неравенство напряжений на входе I3 и выходе 6 (с учетом значений сопротивлений резисторов 7 и 8) приводит к появлению напряжения на инвертируюпщх входах усилителей

II и 2, которое усиливается указанными усилителями и вызывает соответствующее изменение напряжения на конденсаторе 4, Выполнение усилителей 11 и 12 комплементарными обеспечива-.

ет симметричность передачи напряжений различных полярностей, что ведет к повьщ1ению быстродействия всего устройства ,и не требует дополнительных корректирующих элементов.

Появление на входе 2 положительного напря7кения переводит устройство в исходное состояние.

JlfiH повьпцения точности в режиме хранения повторитель 3 может быть

выполнен с использованием МОП-транзистора. Транзистор 29 генератора 8 тока иметь большой коэффициент передачи по току.

Повышение быстродействия устройства обеспечивается за счет использования двух (ко1 тлементарных) дифференциальных усилителей, балансного построения коммутатора 1 и за счет-ис- пользоваг-ия генератора 10 тока для

компенсации паразитного прохождения входного сигнала на выход устройства. При заданной, точности устройство позволяет повысить быстродействие практически в 5-10 раз.

40

Формула из.:)бретения

1, Аналоговое запоминающее устройство, содержащее .тop, управрежима выборк:; -хранения устройства, повторитель напряжения, выход которого является выходом устройства, первый накопительный элемент на первом

конденсаторе, первая обкладка которого соединена с шиной нулевого потенциала устройства, вторая обкладка первого конденсатора соединена с вхоом повторителя напряжения, первый

да1фференциальный усилитель, ограничительный элемент и элемент обратной связи на первом и втором резисторах, отличающееся тем, что, с целью повьппения быстродействия устройства , в него введены второй дифференциальный усилитель, второй накопительный элемент, на втором конденсаторе и генератор тока, вход которого соединен с первой обкладкой второго конденсатора, выход генератора тока соединен с выходом повторителя напряжения и первым выводом второго резистора, второй вывод которого соединен с первым выводом первого резистора, с инвертирующими входами дифференциальных усилителей и с другой обкладкой второго конденсатора, неинвертирующие входы дифференциальных усилителей соединены с шиной нулевого потенциала устройства, вькоды дифферен- . циальных усилителей соединены соответственно с информационными входами коммутатора, выход которого соединен с входом повторителя напряжения, второй вывод первого резисто- .ра является информационным входом устройства.

2. Устройство по п.1, о т л и - чающееся тем, что коммутатор содержит два диода, два п - р - п- транзистора, два р - п - р-транзисто- ра и третий резистор, выводы которого, соединены соответственно с эмиттерами первого п - р - п-транзистора и первого р - п - р-транзистора, база первого п - р - п-транзистора соединена с управляющим входом коммутатора, база первого р - п -р-транзис- тора соединена с шиной нулевого потенциала устройства, коллектор первого п - р - п-транзистора является первым информационным входом коммутатора и соединен с эмиттером второго р - п - р-транзистора и катодом первого диода, анод которого соединен с выводом положительного напряжеРедактор Н.Лазаренко

Составитель А.Воронин

Техред А.Кравчук Корректор Л.Пилипенко

Заказ 3116/49

Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ния и базой второго р - п - р-тран-. зистора, коллектор первого р - п -р-транзистора является вторым ин- формационным входом коммутатора и

соединен с эмиттером второго п - р -п-транзистора и анодом второго диода , катод которого соединен с выводом отрицательного напряжения и баЗОЙ второго п - р - п-транзистора, коллектор второго р - и - р-транзистора является выходом коммутатора и соединен с коллектором второго п -р - п-транзистора.

3. Устройство по П.1, о т л и - чающееся тем, что каждый дифференциальный усилитель содержит два транзистора одного типа проводимости, четвертый и пятьш резисторы, первые.

выводы которых соединены с первым и вторым выводами напряжения питания устройства соответственно, базы транзисторов являются неинвертирующим и инвертирующим входами дйфференциального усилителя, второй вывод четвертого резистора является выходом дифференциального усилителя и соединен с коллектором первого транзистора, эмиттер которого соединен с вторым

выводом пятого резистора и эмиттером второго транзистора, коллектор второго транзистора соединен с первым выводом напряжения питания устройства.

4. Устройство по П.1, отличающееся тем, что дифференциальные усилители вьтолнены по комплементарной структуре.

5. Устройство по П.1, отличающееся тем, что величина сопротивления второго резистора равна величине сопротивления токозадаю- щего резистора генератора тока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1986 |

|

SU1325566A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Операционный усилитель | 1989 |

|

SU1721614A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU780048A1 |

| Восстановитель постоянной составляющей импульсных сигналов напряжения | 1982 |

|

SU1069148A1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

| Способ искробезопасного дистанционного питания и устройство для его осуществления | 1985 |

|

SU1305398A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| Пиковый детектор импульсов | 1985 |

|

SU1272259A1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1732382A2 |

Изобретение относится к вычислительной технике, в частности к за- поминаюпщм устройствам, и может быть использовано в аналого-цифровых преобразователях. Цель изобретения - повышение быстродействия - достигнута за счет введения в устройство второго дифференциального усилителя, второго накопительного элемента на втором конденсаторе, генератора тока И их связей с известными элементами. Появление на„входе 2 положительного напряжения (логической единицы) приводит к отпиранию транзисторов 14 и 16 коммутатора 1, которые замыкают выходной ток усилителей 11 и 19. С конденсатора 4 напряжение передается На выход 6 устройства и, в изменения выходного напряжения, оно компенсируется генератором 10 тока. Появление на входе 2 логического нуля приводит к запиранию транзисторов 14 и 16 и отпиранию транзисторов 15 и 17, в результате чего на входах усили-Гелей 11 и 12 появляется напряжение, которое усиливается ими и вызывает изменение напряжения на конденсаторе 4. Вьшолнение усилителей 11 и 12 комплементарными обеспечивает симметричность передачи напряжения, что обеспечивает повышение быстродействия устройства. 4 з.п. ф-лы, . 1 ил. с (Л ю сд ел сз:

| Патент США № 4321488, | |||

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР 754481, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-10—Подача