Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, может быть использовано при построении аналого-цифровых преобразователей и является усовершенствованием изобретения по авт. ев, № 1325567.

Известно устройство, содержащее коммутатор, управляющий вход которого соединен с шиной управления, первый и второй информационные входы - с выхо- дами соответственно первого и второго дифференциальных усилителей, неинвертирующие входы которых соединены с шиной нулевого потенциала, инвертирующие - через форсирующий конденсатор с входом ге- нератора тока и непосредственно с точкой соединения входного резистора и резистора обратной связи, второй вывод которого , соединен с выходной шиной устройства, выходом генератора тока и выходом повтори- теля напряжения, вход которого соединен с выходом коммутатора и через накопительный элемент на конденсаторе с шиной нулевого потенциала, второй вывод входного резистора соединен с входной шиной уст- ройства.

Недостаток известного устройства заключается в принципиально существующем ограничении тока заряда накопительного конденсатора, что ограничивает динамиче- скую точность устройства. Ток заряда нако- пительного элемента на конденсаторе определяется величиной тока через транзисторы дифференциального усилителя, который не зависит от режима работы устройства (выборка - хранение) и по этой причине принципиально ограничен допустимой мощностью, рассеиваемой на транзисторах дифференциального усилителя.

Цель изобретения - повышение дина- мической точности.

В устройство введены элемент связи на конденсаторе, первый и второй выводы которого соединены с вторыми выходами - точками соединения эмиттеров транзисто- ров соответственно первого и второго дифференциальных усилителей, и первый и второй инверторы тока (токовые зеркала), входы которых соединены с третьими выходами соответственно первого и второго дифференциальных усилителей, выходы - с первыми выходами соответственно первого и второго дифференциальных усилителей. Кроме того, второй выход дифференциального усилителя соединен с эмиттерами пер- вого и второго транзисторов, коллектор первого транзистора - с третьим выходом дифференциального усилителя.

Таким образом, обеспечивается возможность заряда накопительного элементу

на конденсаторе током, величина которого ограничена лишь импульсными возможностями по току транзисторов устройства. Ре- зистивная нагрузка дифференциального усилителя оказывается подключенной параллельно транзистору инвертора тока, что способствует сохранению частотных свойств устройства в режиме статического слежения.

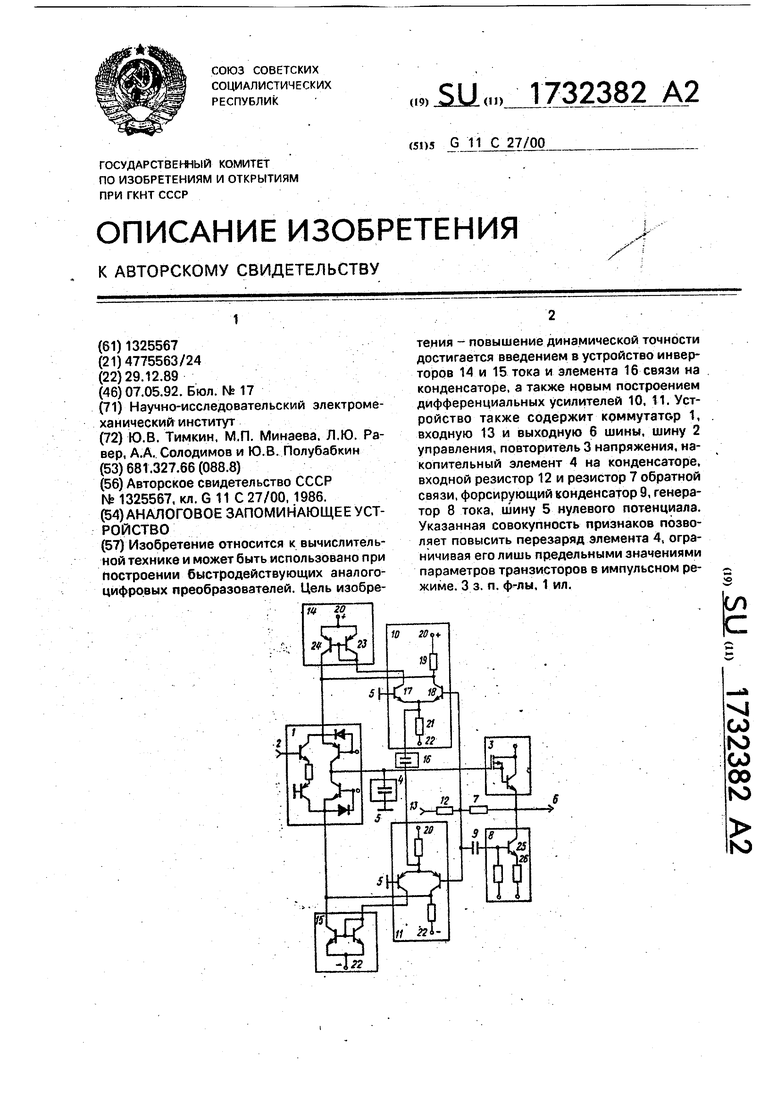

На чертеже приведена электрическая функциональная схема устройства.

Аналоговое запоминающее устройство содержит коммутатор 1, управляющий вход которого соединен с шиной 2 управления, выход- с входом повторителя 3 напряжения и накопительным элементом 4 на конденсаторе, другой вывод которого соединен с шиной 5 нулевого потенциала устройства, выход повторителя 3 напряжения соединен с выходной шиной 6, первым выводом резистора 7 обратной связи и выходом генератора 8 тока, вход которого через форсирующий конденсатор 9 соединен с вторым выводом резистора 7 обратной связи, инвертирующими входами первого 10 и второго 11 дифференциальных усилителей, неинвертирующие входы которых подключены к шине 5 нулевого потенциала, и с первым выводом входного резистора 12, второй вывод которого соединен с входной шиной 13. Первые выходы первого 10 и второго 11 дифференциальных усилителей соединены соответственно с первым и вторым входами коммутатора 1 и с выходами соответственно первого 14 и второго 15 инверторов тока, второй выход первого дифференциального усилителя 10 через элемент 16 связи на конденсаторе соединен с вторым выходом второго дифференциального усилителя 11, третий выход которого соединен с входом второго инвертора 15 тока, вход первого инвертора 14 тока соединен с третьим выходом первого дифференциального усилителя 10.

Каждый из дифференциальных усилителей 10 и 11 содержит первый 17 и второй 18 транзисторы, базы которых соединены соответственно с неинвертирующим и инвертирующим входами дифференциального усилителя, первый выход которого через первый резистор 19 соединен с первой шиной 20 питания устройства и непосредственно с коллектором второго транзистора 18, эмиттер которого соединен через второй резистор 21с второй шиной 22 питания устройства и непосредственное вторым выходом дифференциального усилителя и эмиттером первого транзистора 17, коллектор которого соединен с третьим выходом дифференциального усилителя. Каждый инвертор 14 и 15 тока содержит первый 23 и второй 24 транзисторы одного типа проводимости, эмиттеры которых соединены с соответствующей шиной (20 или 22) питания устройства, базы - с коллектором первого транзистора 23 и входом инвертора тока, выход которого соединен с коллектором второго транзистора 24. Для обеспечения симметричности и линейности характеристик устройства дифференциальные усилители 10 и 11 и инверторы 14 и 15 тока выполнены по комплементарной структуре. Генератор 8 тока содержит транзистор 25 с большим коэффициентом усиления и токо- задающий резистор 26.

Аналоговое запоминающее устройство работает следующим образом,

В исходном состоянии на шину 2 поступает высокий потенциал, обеспечивающий отключение элемента 4 коммутатором 1 от его информационных входов (устройство находится в режиме хранения), при этом токи, поступающие на инфррмационные входы коммутатора 1, замыкаются между собой. Напряжение с элемента 4 через повторитель 3 поступает на шину 6. Изменения напряжения на шине 13 через резистор 12 и конденсатор 9 поступают на базу транзистора 25 генератора 8, ток которого изменяется и компенсирует прямое прохождение входного сигнала на шину 6 (через резисторы 12 и 7 и паразитные емкостные связи), Токи транзисторов 17 и 18 усилителя 10 (аналогично и усилителя 11) приблизительно равны между собой, а их величина определяется величиной резистора 21 и источника 22. Указанные токи через инвертор 14 замыкаются на источник 20. При этом втекающий в первый информационный вход коммутатора 1 ток определяется величинами резистора 19 и источника 20.

При подаче на шину 2 низкого потенциала элемент 4 оказывается подключенным к первому и второму информационным входам коммутатора 1, При этом начинается перезаряд элемента 4, происходящий до тех пор, пока напряжения на шинах 6 и 13 не удовлетворят соотношению, справедливому для операционных усилителей:

Увых Roc/Rex VBX,

где Увых и UGX - напряжение соответственно на шинах 6 и 13;

Roc и RBX - величины сопротивлений резисторов соответственно 7 и 12,

Однако до выполнения указанного соотношения в суммирующей точке, образованной точкой соединения резисторов 12 и 7, появляется напряжение рассогласования, поступающее на инвертирующие входы усилителей 10 и 11. Если полярность

этого напряжения положительная, то увеличивается ток через второй транзистор 18 усилителя 10, что приводит к уменьшению токов через транзистор 17 усилителя 10 и через транзисторы инвертора 14. Это приводит к соответствующему уменьшению втекающего в первый информационный вход коммутатора 1 тока. Одновременно уменьшается ток, протекающий через вто0 рой транзистор усилителя 11, но увеличивается ток, протекающий через первый транзистор усилителя 11 и транзисторы инвертора 15, что приводит к увеличению вытекающего из второго информационного

5 входа коммутатора 1 тока.

Разность токов первого и второго информационного входов коммутатора 1 перезаряжает элемент 4 до тех пор, пока выходное напряжение устройства не соот0 ветствует указанному соотношению. Элемент 16 исключает ограничение токов инверторов 14 и 15 и усилителей 10 и 11 в динамическом режиме. При подаче на шину 2 высокого потенциала аналоговое запоми5 нающее устройство вновь переходит из режима слежения в режим хранения.

Проведенное математическое моделирование показало, что по сравнению с известным устройством возможно уменьшение

0 времени слежения (времени выборки) в сотни раз, а быстродействие устройства ограничивается лишь предельными значениями токов через транзисторы в импульсном режиме и быстродействием самих транзисто5 ров.

При подаче на шину 13 устройства сигналов с несанкционированной скоростью нарастания в реальном устройстве (при низ- коомных источниках питания) возможен вы0 ход из строя транзисторов устройства, Для исключения этого явления ток перезаряда элемента 4 должен быть ограничен известными техническими приемами, например введением резистора в цепь элемента 4 или

5 в цепь элемента 16.

Формула изобретения 1 Аналоговое запоминающее устройство по авт. се. № 1325567, отличающее- с я тем, что, с целью повышения динамиче0 ской точности, в него введены первый и второй инверторы тока и элемент связи на конденсаторе, первый и второй выводы которого подключены соответственно к вторым выходам соответственно первого и

5 второго дифференциальных усилителей, третьи выходы которых подключены к входам соответственно первого и второго инверторов тока, выходы которых подключены к первым выходам соответственно первого и второго дифференциальных усилителей.

2. Устройство по п. 1, отличающее- с я тем, что каждый инвертор тока содержит первый и второй транзисторы одного типа проводимости, эмиттеры которых объединены и подключены к соответствующей шине питания, базы объединены и подключены к коллектору первого транзистора и к входу инвертора тока, выход которого подключен к коллектору второго транзистора соответствующего тока.

0

3.Устройство по п. 1, отличающее- с я тем, что первый и второй инверторы тока выполнены по комплементарной структуре.

4.Устройство поп. 1, отличающее- с я тем, что коллектор первого транзистора дифференциального усилителя является выходом дифференциального усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1986 |

|

SU1325566A1 |

| Аналоговое запоминающее устройство | 1986 |

|

SU1325567A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1976 |

|

SU633073A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство выборки и хранения | 1979 |

|

SU826564A1 |

| Устройство для измерения электрической проводимости и магнитной проницаемости | 1989 |

|

SU1659928A1 |

| Устройство для хранения и выборкииНфОРМАции | 1979 |

|

SU841058A1 |

| Функциональный преобразователь | 1982 |

|

SU1111181A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих аналого- цифровых преобразователей. Цель изобретения - повышение динамической точности достигается введением в устройство инверторов 14 и 15 тока и элемента 16 связи на конденсаторе, а также новым построением дифференциальных усилителей 10, 11. Устройство также содержит коммутатор 1, входную 13 и выходную б шины, шину 2 управления, повторитель 3 напряжения, накопительный элемент 4 на конденсаторе, входной резистор 12 и резистор 7 обратной связи, форсирующий конденсатор 9, генератор 8 тока, шину 5 нулевого потенциала. Указанная совокупность признаков позволяет повысить перезаряд элемента 4, ограничивая его лишь предельными значениями параметров транзисторов в импульсном режиме. 3 з. п. ф-лы, 1 ил. Ё 1 00 hO GO 00 ю ю

| Аналоговое запоминающее устройство | 1986 |

|

SU1325567A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-05-07—Публикация

1989-12-29—Подача