Изобретение относится к области накопления информации, а именно к устройствам для регистрации информации.

Цель изобретения - снижение погрешности регистрации информации за счет обнаружения и обработки ошибочных участков информации.

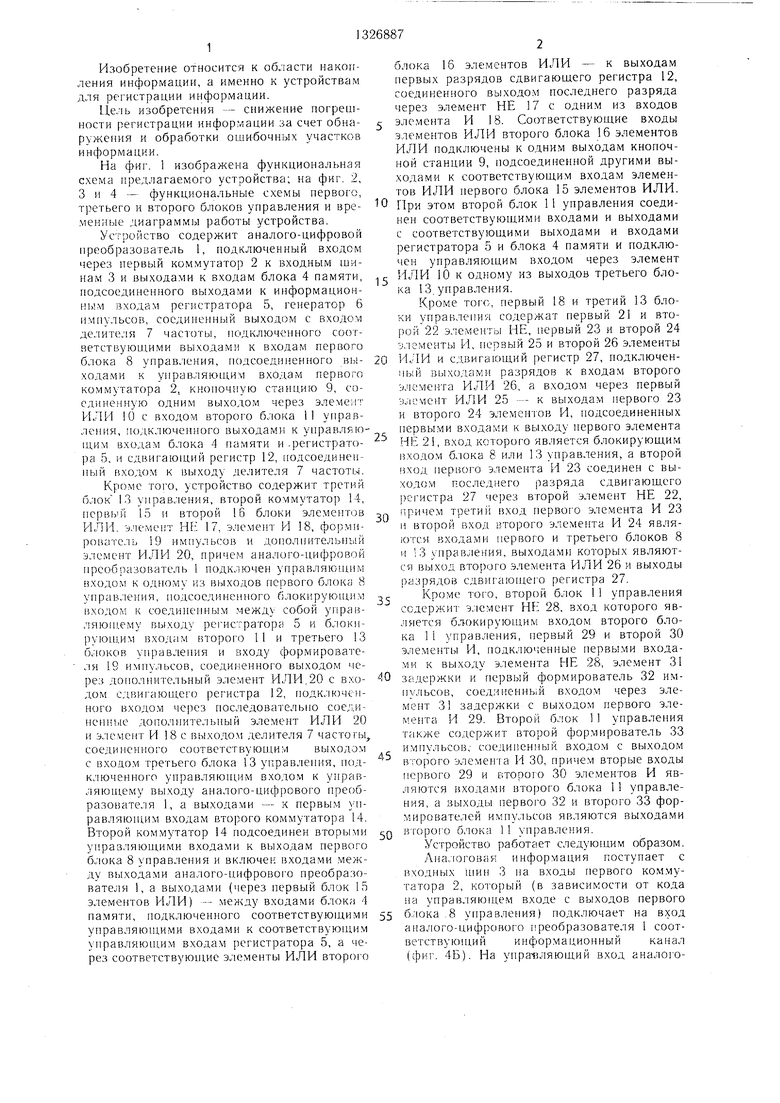

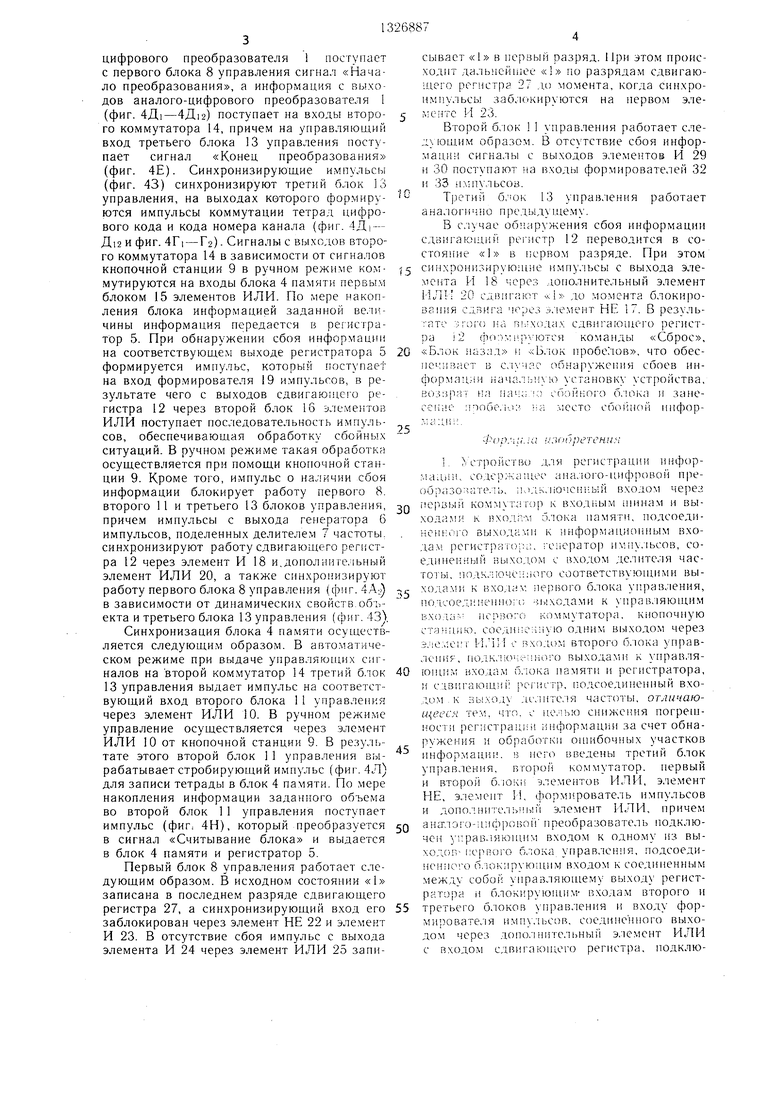

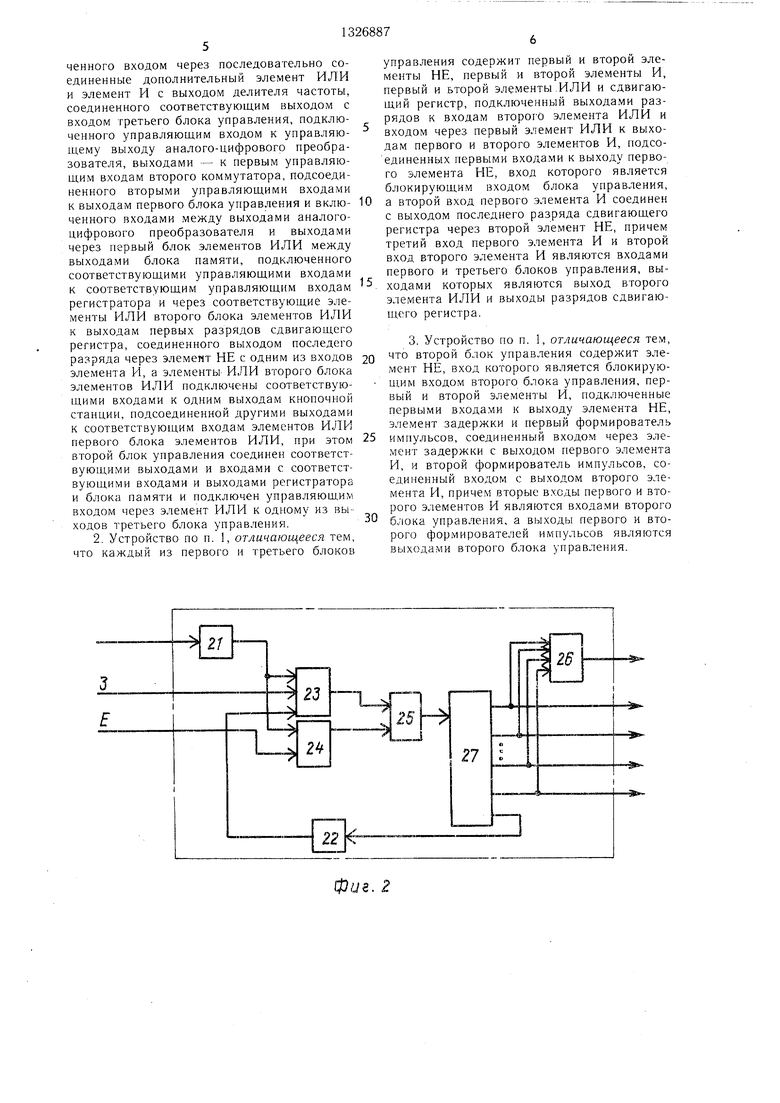

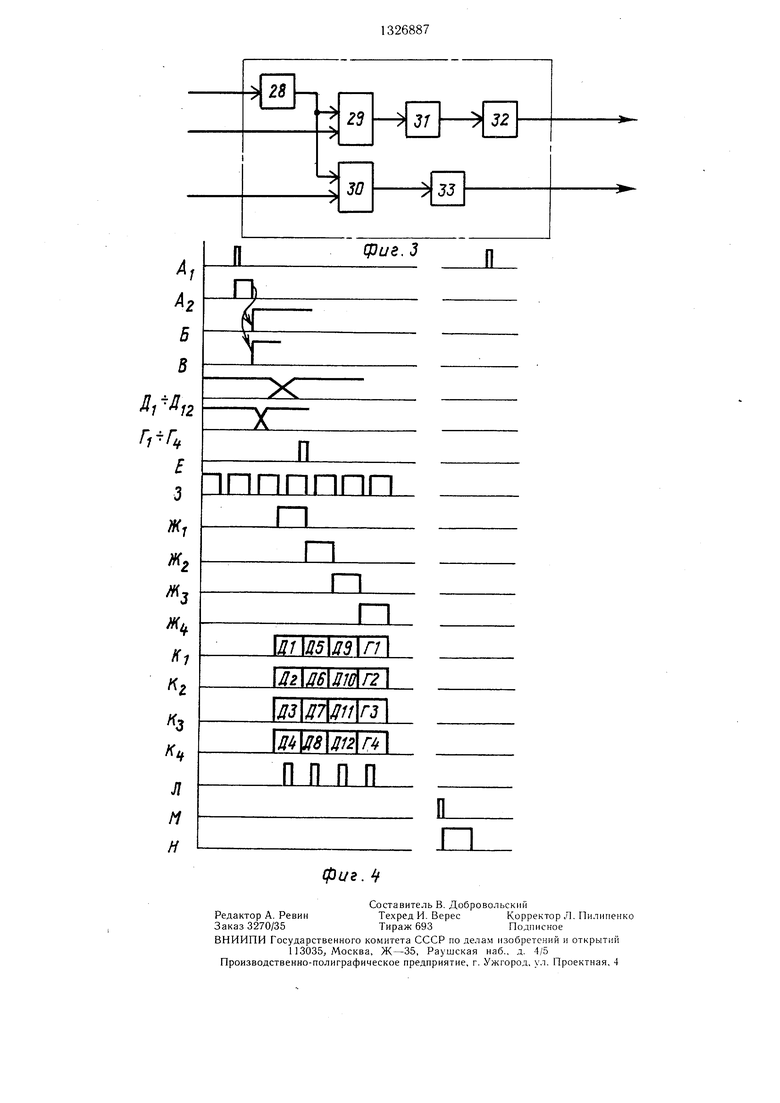

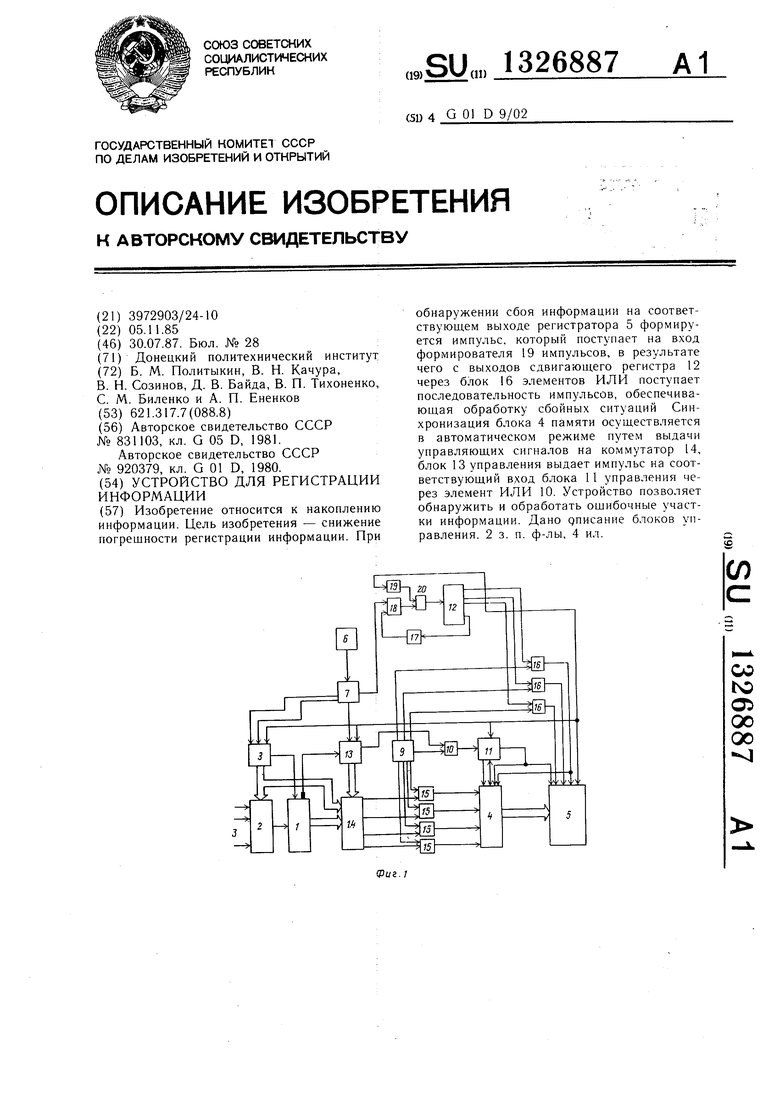

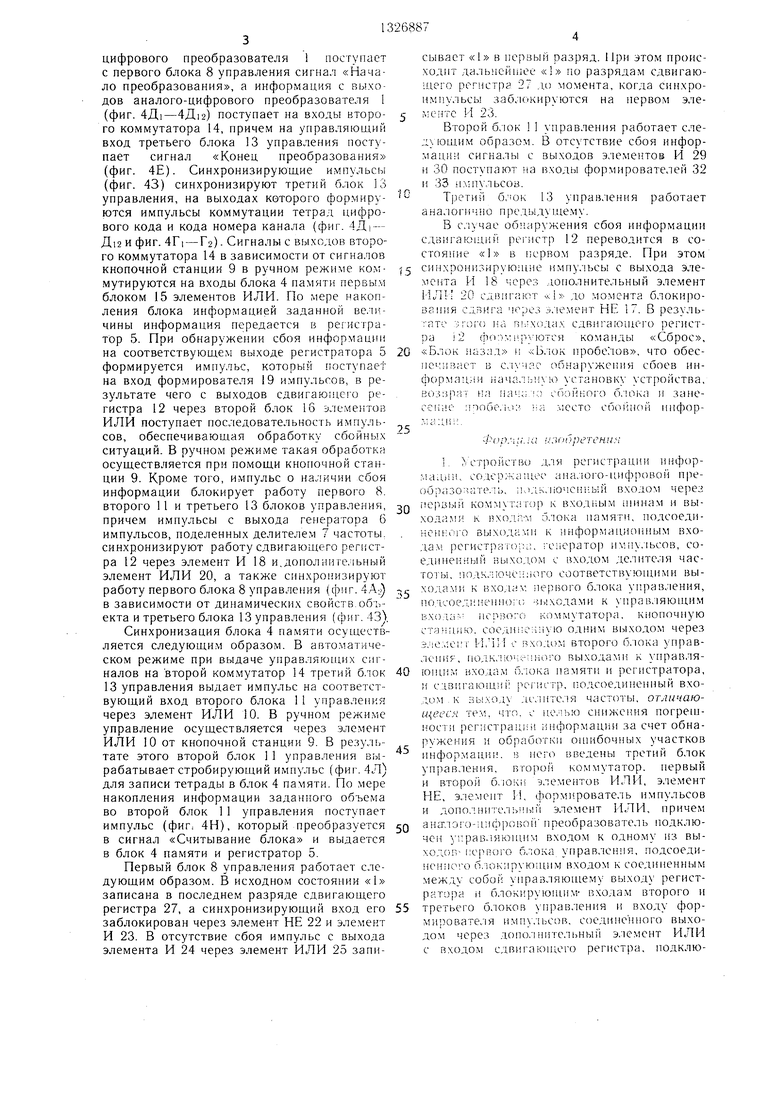

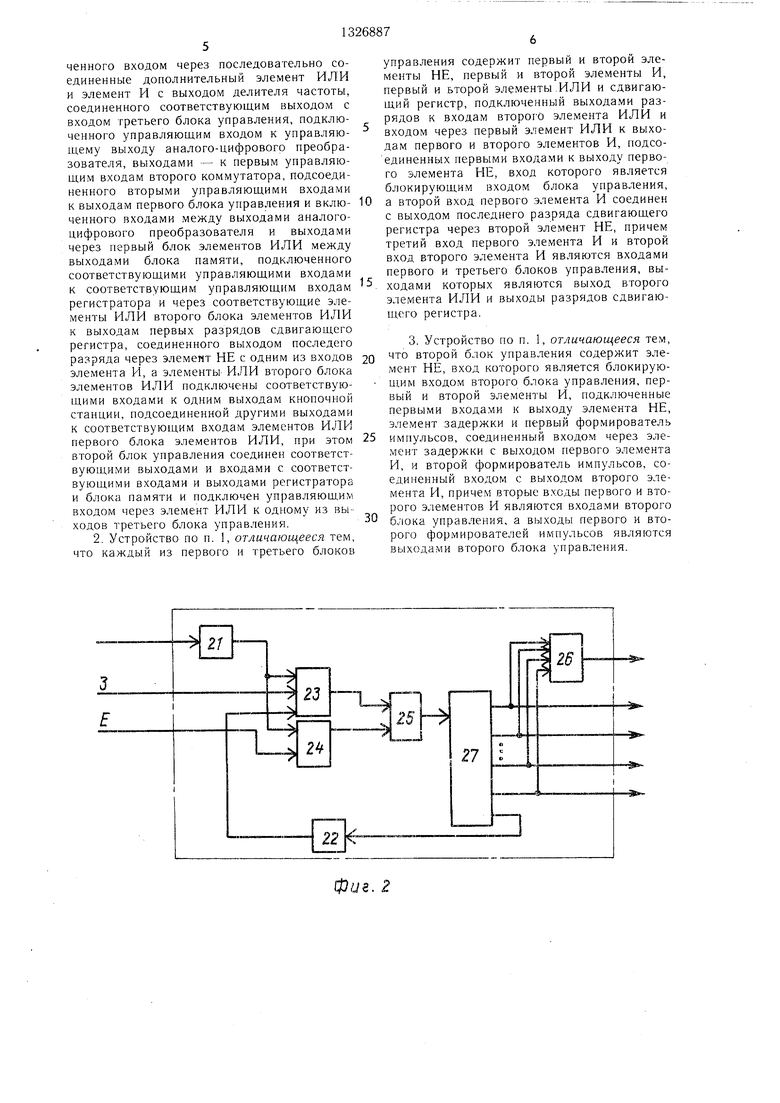

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2, 3 и 4 - функциональные схемы первого, третьего и второго блоков управления и вре- .мениые диаграммы работы устройства.

Устройство содержит аналого-цифровой преобразователь 1, подключенный входом через первый коммутатор 2 к входным шипам 3 и выходами к входам блока 4 памяти, подсоединенного выходами к информационным )зходам регистратора 5, генератор 6 импульсов, соединенный выходом с входом делителя 7 частоты, подключенного соот- ветствуюп1ими выходами к входам первого б:1ока 8 управления, подсоединенного ходами к управляющим входам первого коммутатора 2, кнопочную станцию 9, соединенную одним выходом через элемент ИЛИ 10 с входом второго блока И управ- лепня, подключенного выходами к управляющим входам блока 4 памяти и .регистратора 5, и сдвигаю1ций регистр 12, подсоединенный входом к выходу делителя 7 частоты.

Кроме того, устройство содержит третий блок 13 управления, второй коммутатор 14, первый 15 и второй 16 блоки элементов ИЛИ. элеме1. т HI: 17, эле.мент И 18, фор.мп- рователь 19 импульсов и догюлпительный э.лемент ИЛИ 20, причем аналого-цифровой нреобразователь 1 подключен управляющим входом к одному из выходов первого блока 8 управ.ленпя, нодсое,чипенного блоки.руютцим 1 ходом к соедине1П ым между собой ynpafs- ляюп..ему Г5ЫХОДУ регистратора 5 и б;1окп- руюшпм входам П орого 11 и третьего 13 блоков управлепия и входу формирователя 19 импульсов, соединенного выходом через дополнительный элемент ИЛИ.20 с входом сдвигаюп1.его регистра 12, нодключен- ного входом через последовательно соединенные дополнительный элемент ИЛИ 20 и И 18 с выходом делителя 7 частогы,, соединенного еоответствуюп.шм выходом с в.ходом третьего блока 13 управлепия, подключенного управляющим входом к управляющему выходу аналого-цифрового преобразователя 1, а выходами - к первым ун- равляюп1им входам второго коммутатора 14. Второй коммутатор 14 подсоединен вторыми управляющими входами к выходам первого блока 8 управления и включен входами между выходами аналого-цифрового преобразователя 1, а выходами (через первый блок 15 элементов ИЛИ) -- между входами блока 4 па.мяти, подключенного еоответствуюшими унравляюши.ми входами к соответствуюш,им управляюп1им входам регистратора 5, а через соответствующие элементы ИЛИ вторО|-о

5

0

5

блока 16 элементов ИЛИ - к выходам первых разрядов сдвигающего регистра 12, соединенного выходом последнего разряда через элемент НЕ 17 с одним из входов элемента И 18. Соответствующие входы элементов ИЛИ второго блока 16 элементов ИЛИ подключены к одним выходам кнопочной станции 9, подсоединенной другими выходами к соответствующим входам элементов ИЛИ первого блока 15 элементов ИЛИ. 0 При этом второй блок 11 управления соединен соответствующими входами и выходами с соответствуюпхими выходами и входами регистратора 5 и блока 4 памяти и подключен управляющим входом через элемент ИЛИ 10 к одному из выходов третьего блока 3.управления.

Кроме того, первый 18 и третий 13 блоки управлепия содержат первый 21 и второй 22 элементы НЕ, первый 23 и второй 24 э.лементы И, первый 25 и второй 26 элементы ИЛИ и сдвигающий регистр 27, подключенный выходами разрядов к входам второго элемента ИЛИ 26, а входом через первый элемент ИЛИ 25 - - к выходам первого 23 и второго 24 элементов И, подсоединенных первыми входами к выходу первого элемента НЕ 21, вход которого является блокирующим входом блока 8 или 13 управления, а второй вход нервого элемента И 23 соединен с выходом последнего разряда сдвигающего регистра 27 через второй элемент НЕ 22, причем третий вход первог О эле.мента И 23 и второй вход -ггорого элемента И 24 являются входами нервого и третьего блоков 8 и )3 управления, выходами которых являются выход вто)ого элемента ИЛИ 26 и выходы разрядов сдвпгаюпгего регистра 27.

Кроме , второй блок 11 управления содержит элемент НН 28, вход которого яв- .ляется блокирую1цим входом второго блока 1 1 управления, первый 29 и второй 30 элементы И, подключенные первыми входами к выходу э.темента НЕ 28, эле.мент 31 задержки и первый формирователь 32 им- (п/льсов, соединенный входом через элемент 31 задержки с выходом первого эле- И 29. Второй б.лок 11 управления также содержит второй формирователь 33 импульсов,- соединенный входо.м с выходом второго элемента И 30, причем вторые входы первого 29 и второго 30 элементов И являются входа.ми второго блока 1 1 управления, а выходы первого 32 и второго 33 формирователей импу;1ьсов являются выходами второго блока 11 управления.

Устройство работает следующим образом.

Аналоговая информация поступает с входных шин 3 на входы нервого ком.му- татора 2, кото)ый (в зависимости от кода на управляющем входе с выходов первого блока ,8 управления) подключает на вход аналого-цифрового преобразователя 1 соответствующий информационный канал (фиг. 4Б). На упра { ляющий вход аналого0

0

5

0

5

цифрового преобразователя 1 поступает с первого блока 8 управления сигнал «Начало преобразования, а информация с выходов аналого-цифрового преобразователя 1 (фиг. 4Д1-4Д|2) поступает на входы второго коммутатора 14, причем на управляющий вход третьего блока 13 управления поступает сигнал «Конец преобразования (фиг. 4Е). Синхронизирующие импульсы (фиг. 43) синхронизируют третий блок 13 управления, на выходах которого формируются импульсы коммутации тетрад цифрового кода и кода номера канала (фиг. 4Д - Д12 и фиг. 4Г| - Г2). Сигналы с ВЫХОДОЕ; второго коммутатора 14 в зависимости от сигналов кнопочной станции 9 в ручном режиме коммутируются на входы блока 4 памяти первым блоком 15 элементов ИЛИ. По мере накопления блока информацией заданной вель:- чины информация передается в регистратор 5. При обнаружении сбоя информации на соответствующем выходе регистратора 5 формируется импульс, который iiocTynaet на вход формирователя 19 импульсов, в результате чего с выходов сдвигаю цего регистра 12 через второй блок 16 элементов ИЛИ поступает последовательность импульсов, обеспечивающая обработку сбойных ситуаций. В ручном режиме такая обработка осуществляется при помощи кнопочной станции 9. Кроме того, импульс о наличии сбоя информации блокирует работу первого 8. второго 11 и третьего 13 блоков управления, причем импульсы с выхода генератора 6 импульсов, поделенных делителем 7 частоты, синхронизируют работу сдвигающего регистра 12 через элемент И 18 и,дополнительный элемент ИЛИ 20, а также синхрО П13ируют работу первого блока 8 управления (фиг. 4А: в зависимости от динамических свойств.об ь- екта и третьего блока 13 управления (фиг. 43

Синхронизация блока 4 памяти осуществляется следующим образом. В автолтатиче- ском режиме при выдаче управлярощих сигналов на второй коммутатор 14 третий блок 13 управления выдает импульс на соответствующий вход второго блока 11 управления через элемент ИЛИ 10. В ручном режиме управление осуществляется через элемент ИЛИ 10 от кнопочной станции 9. В результате этого второй блок 11 управления вырабатывает стробирующий импульс (фиг. 4Л) для записи тетрады в блок 4 памяти. По мере накопления информации заданного объема во второй блок 1 1 управления поступает импульс (фиГ: 4Н), который преобразуется в сигнал «Считывание блока и выдается в блок 4 памяти и регистратор 5.

Первый блок 8 управления работает следующим образом. В исходном состоянии «Ь записана в последнем разряде сдвигающего регистра 27, а синхронизирующий вход его заблокирован через элемент НЕ 22 и элемент И 23. В отсутствие сбоя импульс с выхода элемента И 24 через элемент ИЛИ 25 запиЭ

0

сывает «1 в иеррзый разряд. При этом происходит дальнейшее « по разрядам сдвигающего регистра 27 до момента, когда синхроимпульсы заблокируются на нервом элементе И 23.

Второй блок 1 1 управления работает сле- дуюпдим образом. В отсутствие сбоя информации сигналы с выходов элементов И 29 и 30 поступают iia входы формирователей 32 и 33 н лпульсов.

Третий б. нэк 13 управления работает ана;1оги 1но предыдчч.це.му.

В c.iyqae об аружения сбоя информации сдв и-аю1ций pei-.истр 12 переводится в состояние «1 в первом разряде. При этом синхронизирующие импульсы с выхода эле- veiiTa И 18 через дополнительный элемент МЛИ 20 сдвпгг .куг :ч до момента блокирования че;)ез з. емент Н1 17. В результате :ч)Ч) на пь ходах сдви1-ающего регистра ;2 фо:)-ир чотся команды «Сброс, «Блок и «Блок пробелов, что обеспечивает в обнаружения сбоев ин- 1О установку устройства, сбойного б, 11 зане- сбог1П(:1Й пнфор0

0

5

0

5

.iaiuiii, содержащее ана.чого-цифровой пре- обр 3о:игге.-;ь, ,lioчeнl;ый входом через г е|1ВыГ1 кo iм тarap к вход|-.ым пщнам и вы- ходам -; к 1 хода-м блока памяти, подсоеди- неь11;о1-о выходами к информационным входам регистрат()1:а, ; енератор имну.мьсов, соединенный ныхо;1ом с входом делителя частоты, подключенного соответствующими вы- xo;ia .ii-i к входал; первого блока ,:|ения, подсоединенного выходами к управ,тяюп1им входа- iiepBiX o коммутатора, кнопочную станцию. соедн1:с:;; ую одним выходом через г И, И о входом второго б. юка управ- подк,1; 1 ;гмного выходами к управ.тя- входам б,к)ка памятг. и регистратора, ); с двнгающ -; : регистр, Г:одсоединенный вхо- зыход} дс,11гге,1я частоты, отличаю- тем, тто. с iie.Tbio снижения norpein- HocTii регистращ: :;11формации за счет обнаружения и обработки ошибочных участков информаци. в iierci введены третий блок управления, второй коммутатор, первый и второй 6,iOi;ii элементов ИЛИ, э,чемент НЕ, элемент И, форм1 рователь импульсов и допо,- нительнь Й элемент ИЛИ, причем ана ло о-;и1(Ьровой преобразователь подключен управляющим входом к одному из выходов- iiei Roi-o б,ока управления, подсоеди- ненпого блокирующим входом к соединенным между собой упра;5ляющему выходу регистратора и блокирующим- входам второго и третьего б, юков управления и входу формирователя импу, 1ьсов, соединенного выходом через дополнительньи э.пемент ИЛИ с входом сдвигающего регистра, подклюценного входом через последовательно соединенные дополнительный элемент ИЛИ и элемент И с выходом делителя частоты, соединенного соответствующим выходом с входом третьего блока управления, подключенного управляюпдим входом к управляющему выходу аналого-цифрового преобразователя, выходами - к первым управляющим входам второго коммутатора, подсоединенного вторыми управляющими входами

управления содержит первый и второй элементы НЕ, первый и второй элементы И, первый и второй элементы-ИЛИ и сдвигающий регистр, подключенный выходами разрядов к входам второго элемента ИЛИ и входом через первый элемент ИЛИ к выходам первого и второго элементов И, подсоединенных первыми входами к выходу первого элемента НЕ, вход которого является блокирующим входом блока управления.

к выходам первого блока управления и вклю- 10 а второй вход первого элемента И соединен

с выходом последнего разряда сдвигающего регистра через второй элемент НЕ, причем третий вход первого элемента И и второй вход второго элемента И являются входами первого и третьего блоков управления, выходами которых являются выход второго элемента ИЛИ и выходы разрядов сдвигающего регистра.

ченного входами между выходами аналого- цифрового преобразователя и выходами через первый блок элементов ИЛИ между выходами блока памяти, подключенного соответствующими управляющими входами к соответствующим управляющим входам регистратора и через соответствующие элементы ИЛИ второго блока элементов ИЛИ к выходам первых разрядов сдвигающего регистра, соединенного выходом последего разряда через элемент НЕ с одним из входов элемента И, а элементы ИЛИ второго блока элементов ИЛИ подключены соответствующими входами к одним выходам кнопочной станции, подсоединенной другими выходами к соответствующим входам элементов ИЛИ первого блока элементов ИЛИ, при этом второй блок управления соединен соответствующими выходами и входами с соответствующими входами и выходами регистратора и блока памяти и подключен управляющ,им входом через элемент ИЛИ к одному из выходов третьего блока управления.

2. Устройство по п. 1, отличающееся тем, что ка.ждый из первого и третьего блоков

15

20

25

30

3. Устройство по п. 1, отличающееся тем, что второй блок управления содержит элемент НЕ, вход которого является блокирующим входом второго блока управления, первый и второй элементы И, подключенные первыми входами к выходу элемента НЕ, элемент задержки и первый формирователь импульсов, соединенный входом через элемент задержки с выходом первого элемента И, и второй формирователь импульсов, соединенный входом с выходом второго элемента И, причем вторые входы первого и второго элементов И являются входами второго блока управления, а выходы первого и второго формирователей импульсов являются выхода.ми второго блока управления.

Фие. 2

управления содержит первый и второй элементы НЕ, первый и второй элементы И, первый и второй элементы-ИЛИ и сдвигающий регистр, подключенный выходами разрядов к входам второго элемента ИЛИ и входом через первый элемент ИЛИ к выходам первого и второго элементов И, подсоединенных первыми входами к выходу первого элемента НЕ, вход которого является блокирующим входом блока управления.

а второй вход первого элемента И соединен

3. Устройство по п. 1, отличающееся тем, что второй блок управления содержит элемент НЕ, вход которого является блокирующим входом второго блока управления, первый и второй элементы И, подключенные первыми входами к выходу элемента НЕ, элемент задержки и первый формирователь импульсов, соединенный входом через элемент задержки с выходом первого элемента И, и второй формирователь импульсов, соединенный входом с выходом второго элемента И, причем вторые входы первого и второго элементов И являются входами второго блока управления, а выходы первого и второго формирователей импульсов являются выхода.ми второго блока управления.

фиг. 4

Составитель В. Добровольский

Редактор А. РевинТехред И. ВересКорректор Л. Пилипенко

Заказ 3270/35Тираж 693Подписное

ВНИИПИ Государствеиного комитета СССР по делам изобретений и открытий

113035, Москва, , Раушская иаб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой записи воспроизведения речевой информации | 1990 |

|

SU1771533A3 |

| Устройство дл прогнозирования неисправностей радиоэлектронной аппаратуры | 1978 |

|

SU742958A1 |

| Цифровой электропривод постоянного тока | 1990 |

|

SU1709485A1 |

| Устройство для определения коэффициентов линейной регрессии | 1981 |

|

SU993291A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1986 |

|

SU1327174A1 |

| Устройство для регистрации информации | 1982 |

|

SU1027710A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Устройство для определения условного математического ожидания | 1981 |

|

SU1003097A1 |

| Устройство для решения задач теплопроводности | 1985 |

|

SU1278900A1 |

Изобретение относится к накоплению информации. Цель изобретения - снижение погрешности регистрации информации. При обнаружении сбоя информации на соответствующем выходе регистратора 5 формируется импульс, который поступает на вход формирователя 19 импульсов, в результате чего с выходов сдвигающего регистра 12 через блок 16 элементов ИЛИ поступает последовательность импульсов, обеспечивающая обработку сбойных ситуаций Синхронизация блока 4 памяти осуществляется в автоматическом режиме путем выдачи управляющих с гналов на коммутатор 14, блок 13 управления выдает импульс на соответствующий вход блока 11 управления через элемент ИЛИ 10. Устройство позволяет обнаружить и обработать ошибочные участки информации. Дано дписание блоков управления. 2 3. п. ф-лы, 4 ил. (О сл со го ot 00 00 v3

| Устройство для регистрации,воспроизведенияи АНАлизА физиОлОгичЕСКиХ СигНАлОВ | 1979 |

|

SU831103A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровой регистратор | 1980 |

|

SU920379A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-07-30—Публикация

1985-11-05—Подача