Изобретение относится- к вычислительной технике и может быть использовано в системах автоматического контроля и -в автоматизированных системах управления технологическими про-/ цеесами.

Известно устройство для измерения коэффициентов линейной регрессии, содержащее два входных блока, аналогоцифровой преобразователь, элемент сравнения, два временных селектора, счетчик импульсов, пересчетный блок и триггер. Устройство позволяет измерять коэффициенты линейной регрессии. Действительно, если в уравнении ли нейной регрессии

Л Х/;С--№у + Ъг/х (x-wy) полагать ту-О yryiO W х-Хс, то Xcbv/ c

Таким образом, алгоритм определения коэффициента линейной регрессии Ь /Хс сводится к определению условного математического ожидания центрированного случайного процесса j(-fc) по центрированному случайному процессу к (Ч:) при фиксированном значении . Следовательно, если в устройстве входные блоки - это центрирующие фильтры, то его можно использовать для измерения коэффициента Ьу/х flj .

Наиболее близким по технической сущности к предлагаемому является устройство для определения коэффициентов линейной регрессии, содержащее центрирующие фильтры, модульную схему, аналого-цифровой преобразователь, дискриминатор .знака, элемент сравнения, блок регулируемой задержки, два элемента совпадений, временной селек10тор, пересчетный блок, реверсивный счетчик импульсов, триггер, кнопкуи переключатв.г1и с соответствующими связями 2 J.

Известные устройства не поэволя ют определить текущие значения коэффициентов регрессии.

Цель изобретения - расширение функциональных возможностей устройства путем определения текущих зна20чений коэффициентов линейной регрессии.

Поставленная цель достигается тем, что в устройство для определения коэффициентов линейной регрессии,содержащее

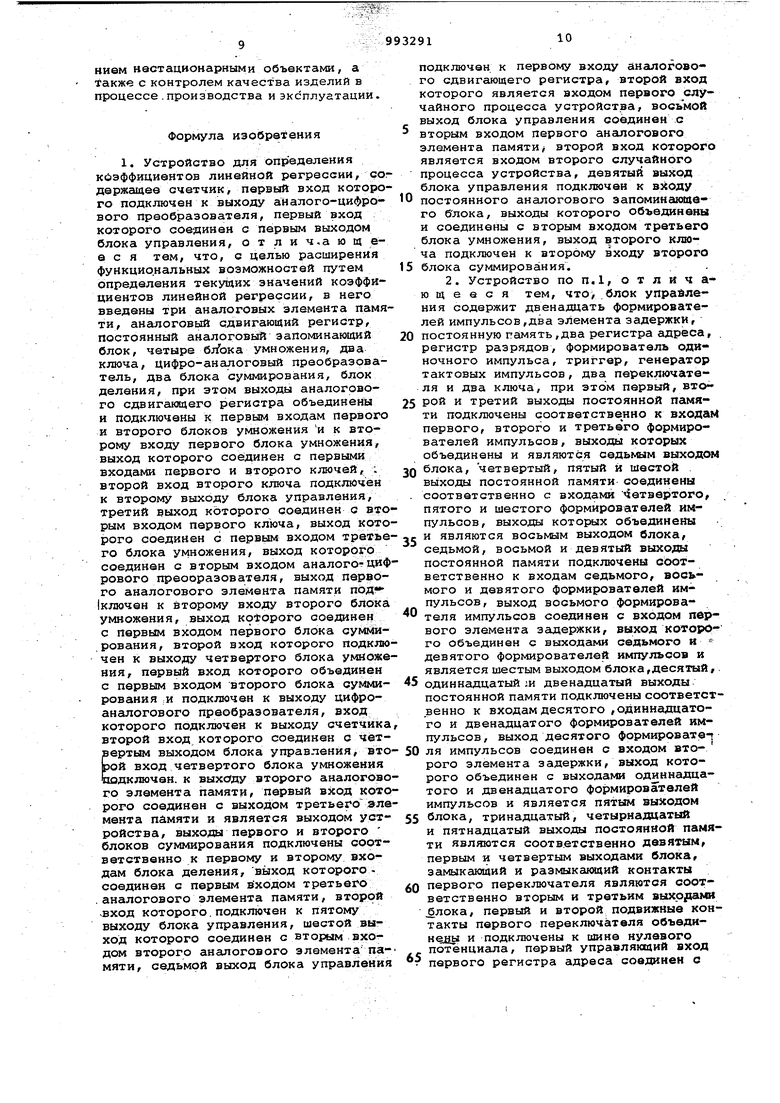

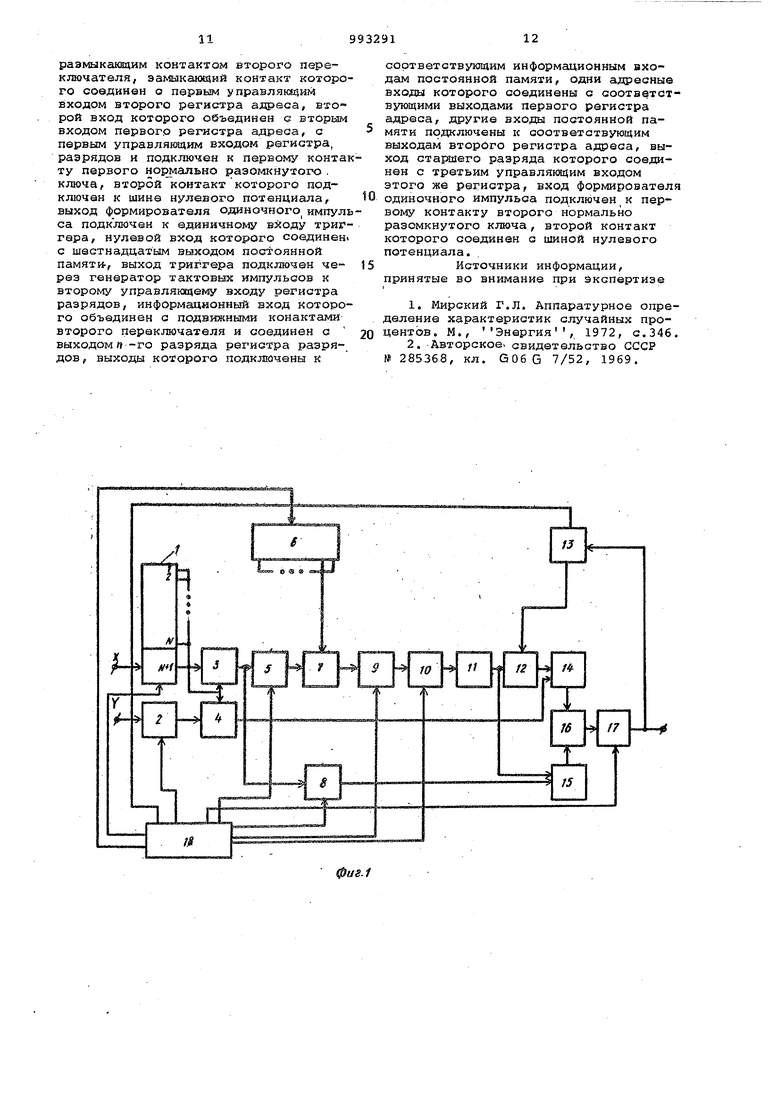

25 счетчик, первый вход которого подключен к выходу аналого-цифрового преобразователя, первый вход которого соединен с первым выходом блока управленик, введены три аналоговых эле30мента памяти, аналоговый сдвигающий { вгистр, постоянный аналоговый заиоминаквдий блок, четыре блока умножения, ;.дВа ключа, цифро-аналоговый преобразователь, два блока суммирования, йлок деления, при этом выходы аналогового сдвигающего регистра объединены и подключены к первым входам первого и второго блоков умножения: к к второму входу первого блока умножения, выход которого соединен с первыми входами первого и второго ключей, второй вход РТОРОГО ключа подключен к второму ВЫ оду блока управления, третий выход кЭторого соединен о вторым входом , первого ключа,выход которого соединен с первым входом третьего блока умножения, выход которого соединен с вторым входом аналого-цифрового преобразователя, выход первого аналогового элемент памяти подключен к второму входу второго блока умножения, выход которого соединен с первым входом пер вого блока суммирования, второй вход которого подключен к выходу четвертог блока умножения, первый вход которого объединен с первым входом второго блока суммирования,и подключен к выходу, цифро-аналогового преобраэозате™ ля, выход которого подключен к выходу счетчика, второй вход которого соединен с четвертым выходом блока управления, второ.й вход четвертого блока умножения подключен к,выходу второго аналогового элемента памяти, парный вход которого соединен с выходом третьего элемента памяти и является выходом устройства, выходы первого и второго блоков суммирования подключены, соответственно к первому и второ му входам блока деления, выход кото рого соединен с первым входом третьего аналогового .элемента памяти, второй вход которого подключен к пятому выходу блока управления, шестой выход которого соединен с вторым входом второго аналогового элемента памяти, седьмой выход блока управления подклю чен к первому входу аналогового сдвигающего регистра, второй вход которого является входом первого случайного процесса устройства,восьмой выход блока управления соединен с эторым входом первого аналогового эле™ Мента памяти, второй вход которого является входом второго случайного процесса устройства, девятый выход блока управления подключен к входу постоянного аналогового запоминающе го блока, выходы которого объединены и соединены с вторым входо третьего блока умножения, выход второго ключа ..подключен к второму входу второго (блока суммирования. Кроме того, блок управления содержит двенадцать формирователей импульров, два элемента зещержки, постоянНую память, два регистЬа адреса, регистр разрядов, формиррватель одиночногй импульса, триггер,| генератор тактовых импульсов, два переключателя и два нормально раэомкн1утых ключа, при этом первый, второй и третий выходы постоянной памяти подключены соо гветственно к входаЦ первого, второго и третьего формирователей импульсов, выходы которых объединены и являются седьмым выходом блока, четвертый, пятый и шестой выходы постоянной памяти соединены соответственно с входами четвертого, пятого и шестого формирователей импульсов, выходы которых объединены и являютсявосьмым выходом блока,седьмой,восьмой и девятый выходы-постоянной памятиподключены соответственно к входам седьмого, восьмого и девятого формирователей импульсов , выход восьмого формирователя импульсов соединен с входом первого элемента задержки, выход которого объединен с выходами седьмого и девятого формирователей импульсов является шестым выходом блока,десятый, одиннадцатый и двенадцатый выходы постоянной памяти подключены соответственно к входам десятого, одиннадцатого и двенадцатого формирователей им- пульсов, выход десятого формирователя импульсов соединен с входом второго элемента задержки,выход которого .объеди-. нен с выходами одиннадцатого и двенадцатого формирователей импульсов и является пятым выходом блока, тринадцатый, четырнадцатый и пятнадцатый выходы постоянной памяти .являются соответственно девятым, первым и четвертым выходами блока, замыкающий и размыкающий контакты первого переключателя являются собтветственно вторым и третьим выходами блока, первый и второй подвижные контакты первого переключателя объединены и подключены к шине нулевого потенциала, первый управляющий вход первого регистра адреса соединен с размыкающим контактом второго переключателя, замыкающий контакт которого соединен с первым управляющим входом второго регистра адреса, второй вход которого объединен с вторым входом первого регистра адреса, с первым управлякщим входом регистра разрядов и подключен к первому контакту первого нормально разомкнутого ключа, второй контакт которого подключен к шине нулевого потенциала, выход формирователя одиночного импульса подключен к единичному входу тригг гера, нулевой вход которого соединен с шестнадцатым выходом постоянной памяти, выход триггера подключен через генератор тактовых импульсов к второму управляющему входу регистра разрядов, информационный вход которого объединен с переключающими контактами второго переключателя и соединвн с выходом и-го разряда регистр разрядов, выходы которого подключены к соответствующим информационным вхо дам постоянной памяти, одни адресные входы которого соединены с соответст вующими выходами первого регистра адреса, другие входы постоянной памя ти подключены к соответствующим выхо ДИМ второго регистра адреса,выход старшего разряда которого соединен с третьим управляющим входом этого .же регистра, вход формирователя одиночного импульса подключен к первому контакту второго нормально -разомкнутого ключа, второй контакт которог соединен с шиной нулевого потенциала На фиг.1 представлена блок-схема устройства; на фиг.2 - блок-схема блока управления. Устройство содержит аналоговый сдвигающий регистр 1, первый аналоговый элемент 2 памяти, первый блок 3 умножения, второй блок 4 -умножения первый ключ 5, постоянный аналоговый запоминающий блок 6, третий блок 7 умножения, второй ключ 8, аналогоцифровой преобразователь 9, счетчик 10,цифро-аналоговый преобразователь 11,четвертый блок 12 умножения, вто рой аналоговый элемент 13 пгьмяти, первый блок 14 суммирования, второй Дпок 15 суммирования, блок 16 делени третий аналоговый элемент 17 памяти., блок 18 управления. В состав блока 18 управления вхо.дят двенадцать формирователей 19-30 импульсов, два элемента 31 и 32за-« держки, постоянная память 33, регист 34 разрядов, первый регистр 35 адреса, второй регистр 36 адреса, формирователь 37 одиночного импульса, триггер 38, генератор 39 тактовых импульсов, первый и второй переключатели 40 и 41, первый и второй нормально разомкнутые ключи 42 и 43. Оценку коэффициента линейной регрессии BCn+oi+l) можно определить д+«Л по следующему вы через оценку ражению: (ICillllXCi+i) .н).,,,,,;,---„,. Ь.1н)-ие1н)1Гвиы)3, (,) где llC4r-(ll -iH nillllKVll)i . „ 1|.ХД1ЬХаЫ-.ХцМ II-матрица з IvtVVv f v,M зависимой XiU),Xa.(l),--, манной менной; матрица значе U,.j} ний функции .uj; са) О (л,) J -. параментр функ ции веса; //Х( + 1)|| (1+1) , X(i+l),..., х(л+1) - вектор (-1 + 1) X значений . независимых переменных; значен пере (i + 1) - {-T+Dre значение зависимой переменной Т - знак транспонирова// А// - матрица, обратная матрице //А//;,, Н.,- -H vi4i4 -j) Для одного независимого диаметра X и при (JN зависимость (1) упрощается:Цg|1X. . BlN+A)--blM).M учитывая, что I, Ч чпосле преобразований получим (М)ь1,(4) xt.,.J .i внесем j под знак суммы и обоэмачим А , тогда будем иметь %1кч). .v.;. Хц. « Предлагаемое устройство реализует зависимость (2). Устройство работает следующим образом. В первые N+1 тактов работы устроййхва происходит заполнение аналогового сдвигающего регистра 1. Для этого блок 18 управления последоватдлъйо выдает команды на запись и сдвиг значений в аналоговый сдвигаивдий регистр B(NJ+1)-M такте. Блок 18 формирует сигнал на запись значений N4. в первый аналоговый элемент 2 памяти. После этого первый ключ 5 открывается, второй ключ 8 закрыт и начинается попарное считывание N значений Х из аналогового сдвигающего регистра и N значений А из постоянной дамяти б. В процессе считывания величина, пропорциональная . ), с первого блока умножения через первый ключ.попадает на блок 7 умножения, где вычисляется произведение X(i)Ay . Аналого-цифровой преобразователь преобразует эту величину в числе импульсов, которое считывается счетчиком. Таким образом, после N тактов считывания в счетчике образуется величина, пропорциональная .Х x(i ) А- . Преобразованная в аналогоЪую величину эта сумма подается на вход блока 12 умножения. Спусти Ы тактов считывания второй ключ 8 открывается, а первый ключ 5 закрывается. В (Ы+1)-м такте считывают значения XN соответственно из аналогового сдвигакмдаго регистра 1 И первого аналогового элемента 2 памяти одновременно. После небольшой задержки t/, , необходимой для того/ чтобы установились переходные процессы в блоках 3 и 4 умножения, считывают значение fe(N) из второго элемента 13 памяти. Величина ё (М) значение коэффициен та линейной регрессии, в М-й момен времени - хранится в элементе 13 памяти в исходном состоянии (значение этой величины берут из предварительного статического анализа процессов X и или, как правило, принимают равной единице) , В результате считывание информаци из аналогового сдвигающего регистра первого и второго элементов 2 и 13 памяти на второй вход первого блока 14 суммирования поступает величина, №опорциональная произведению B(W) н i. .( i) , А , на первый вход первого блока суглмирования - величина. XN+I второй вход блрка 15 суммирования ,. . Таким образом, на первый вход блока деления (вход делимого) поступает величина, пропорциональная числителю выражения (2), на второй выход - величина пропорциональная знаменателю выражения (2) , и на вход третьего элемента 17 памяти подается величина, пропорциональная ё(М+1). После небольшой задержки T{t, необходимой для переходных процессов в блоке деления,подае ся команда на запись значения В(к1+1) в третий элемент 17 памяти. Затем подается команда на стирание,информации во втором элементе 13 памяти. После этого значение ё(М+,1) выдает-, ся из третьего элемента 17 памяти.,на выход устройства и одновременно зано сится во второй элемент 13 памяти. Цикл измерения коэффициента В(Ы+1 по значению В(К1) и X с учетом предыдущей информации окончен, устройство возвращается в исходное состояние. Для этого по командам бло ка 18 управления приводится в исходное состояние аналого-цифровой преоб разователь, счетчик, стирается информация в первом и третьем элемента памяти. После этого осуществляется сдвиг информаи ии в аналоговом сдвигающем регистре (т.е. (N+l)-e значение записывается на место Ы-го, М-е - на место (Sl-l)-ro и т.д,) . Затем записываются значения Х. и и повторяются все циклы считывани я для получения промежуточных величин и значения e(N+2), считывание (М+2) на выход, перезапись значения B(N+2) на место В(Ы + 1), возвращение схе№з в исходное состояние и т.д. Следовательно, начиная с (М + 1)-го момента времени есть возможность измерять те кущие значения коэффициента линейной регрессии. БЛОК 18 управления работает следующим образом. Ключом 42 блок приводится в исходное состояние. Для этого регистры 34-36 очищают, записывают в первую ячейку, а в остальные - . При нажатии ключа 43 триггер 38 опрокидывается и, открывает генератор 39. Тактовые импульсы начинают поступать на регистр разрядов 34. Из матрицы 33 считывается первое слово, записанное заранее по первому адресу. После считывания слова последним разрядным импульсом записаниая сдвигается в регистре 35 и из матрицы считывается вторбе слово и т.д. Записанное в матрице 16-разрядное слово представляет собой совокупность нулей и единиц. Если в данном такте необходимо, чтобы формировался сигнал на какой-либо блок, необходимо в разряде, подключенном к соответствующему формирователю или шине, записать . Например, в 1-м такте необходимо, чтобы подавалась команда на запись значения Х . Первое ело-, .во будет выглядеть следующим образом 1000000000000000.BCN+1)-м такте йеобходимо подать команду на запись какХ-..- так и N+-1. Команда в этом случае выглядит так:1001000000000000.Если необходимо, чт.обы после выполнения очередной ко- манды блок остановился, в 16 разряде последней записывают да после выполнения команды импульс 16 разряда перебрасывает триггер 38 в противоположное состояние и генератор 39 перестает работать. Для продолжения работы блока необходимо повторно нажать ключ 43. Команды, позволяющие заполнить аналоговый сдвигающий регистр значениями XL/выполняются только в первые Ы тактов работы устройства, в дальнейшем их выполнять не надо. Для осуществления этого режима с помощью второго переключателя 4 отключают регистр 35 адреса и подключают регистр 36 адреса, Для формирования задержек t и т г использованы элементы 31 и 32 задержки. Управление работой ключа 5 и блока 6 осуществляется непосредственно от первого переключателя 40. Таким образом, предлагаемое устройство обеспечивает измерение текущего значение коэффициента- линейной регрессии B(K+k) по вновь посту- пившим значениям . случайного процесса | и значениям .к случайного процесса X, нестационарно связанного с процессом У. Устройство можно использовать для решения задачи параметрической идентификации. Применение устройства позволяет решить цвлый ряд задач, связанных с управлением нестационарными объектами, а также с контролем качества изделий в процессе.производства и эксплуатации.

Формула изобретения

1. Устройство для определения коэффициентов линейной регрессии, cor держащее счетчик, первый вход которого подключен к выходу аналого-цифрового преобразователя, первый вход которого соединен с Первым выходом блока управления, о т л и ч,а ю щ ее с я тем, что, с целью расширения функциональных возможностей путем определения текущих значений коэффициентов линейной регрессии, в него введены три аналоговых элемента памяти, аналоговый сдвигающий регистр, постоянный аналоговый запоминающий блок, четыре умножения, два ключа, цифро-аналоговый преобразователь, два блока суммирования, блок деления, при этом выходы аналогового сдвигающего регистра объединены и подключены к первым входам первого и второго блоков умножения и к второму входу первого блока умножения, выход которого соединен с первыми входами первого и второго ключей, : второй вход второго ключа подключен к второму выходу блока управления, третий выход которого соединен с вторым входом первого ключа, выход которого соединен с первым входом третьего блока умножения, выход которого соединен с вторым входом аналого-цифрового преооразователя, выход первого аналогового элемента памяти под ключен к второму входу второго блока умножения, выход которого соединен с первым входом первого блока суммирования, второй вход которого подключен к выходу четвертого блока умножения, первый вход которого объединен с первым входом второго блока cyt uрования ;И подключен к выходу цифроаналогового преобразователя, вход которого подключен к выходу счетчика, второй вход которого соединен с четвертым выходом блока управления, второй вход четвертого блока умножения подключен, к выходу второго аналогового элемента памяти, первый вход которого соединен с выходом третьего элемента памяти и является выходом устройства, выходы первого и второго блоков суммирования подключены соотетственно к первому и второму вхоам блока деления, выход которого оединен с первым входом третьего аналогового элемента памяти, второй вxoд которого.подключен к пятому выходу блока управления, шестой выход которого соединен с вторым входом второго аналогового элемента па-/ яти, седьмой выход блока управления

подключен к первому входу аналогового сдвигающего регистра, второй вход которого является входом первого случайного процесса устройства, восьмой выход блока управления соединен чс вторым входом первого аналогового элемента памятиj второй вход которого является входом второго случайного процесса устройства, девятый выход блока управления подключен к в:ХОЯУ

0

постоянного аналогового запоминающе

го блока, выходы которого объединены и соединены с вторым входом третьего блока умножения, выход второго ключа подключен к второму входу второго

5 блока суммирования.

2. Устройство по п.1,о т л и ч ающееся тем, что/,блок управления содержит двенададать формирователей импульсов,два элемента задержки,

0 постоянную гамять,два регистра адреса, регистр разрядов, формирователь одиночного импульса, триггер, генератор тактовых импульсов, два переключателя и два ключа, при этом первый, вто5 рой и третий выходы постоянной памяти подключены соответстве нно к вxoдa 4 первого, второго и третьего формирователей импульсов, выходы которых объединены и являются седьмым выходом

Q блока, четвертый, пятый и шестой . выходы постоянной памяти соединены . соответственно с входами ieTBejiToro/ пятого и шестого формирователей импульсов, выходы которых объединены

с н являются восьмым выходом блока, седьмой, восьмой и девятый выходы постоянной памяти подключены соответственно к входам седьмого, восьмого и девятого формирователей импульсов , выход восьмого формирова0теля импульсов соединен с входом первого элемента задержки, выход которого объединен с выходами седьмого и девятого формирователей импульсов и является шестым выходом блока,десятый,.

5 одиннадцатый :и двенадцатый выходы

постоянной памяти подключены соответственно к входам десятого , одиннадцатого и двенадцатого формирователей импульсов, выход десятого формировате-т

0 ля импульсов соединен с входом второго элемента задержки, выход которого объединен с выходами одиннадцатого и двенадцатого формирователей импульсов и является пятым выходом

5 блока, тринадцатый, четырнадщатый

и пятнадцатый выходы постоянной памяти являются соответственно девятым, первым и четвертым выходами блока, замыкающий и размыкакнций контакты

Q первого переключателя являются соответственно вторым и третьим аыхр;|ами блока, первый и второй подвижные контакты первого переключателя объеди-

нелы и подключены к шине нулевого потенциала, первый управляющий вход

65 первого регистра адреса соединен с

размыкающим контактом второго переключателя, замыкающий контакт которого соединен о первьзм управлянж им входом второго регистра адреса, вто рой вход которого об-ьвдинен с вторым входом первого регистра адреса, с первым управляющим входом регистра, разрядов и подключен к первому контакту первого нормально разомкнутого . ключа, второй контакт которого подключен к шине нулевого потенциала, выход формирователя одиночного импульса подключен к единичному входу триггера, нулевой вход которого соединен с шестнадцатым выходом постоянной памяти-, выход триггера подключен через генератор тактовых импульсов к второму управляющему входу регистра разрядов, информационный вход которого объединен с подвижными конактами второго переключателя и соединен с выходом ч -го разряда регистра разрядов , выходы которого подключены к

соответствующим информационным входам постоянной памяти, одни адресные входы которого соединены с соответствующими выходами первого регистра адреса, другие входы постоянной памяти подключены к соответствующим выходам второго регистра адреса, выход старшего разряда которого соединен с третьим управляющим входом этого же регистра, вход формирователя одиночного импульса подключен к первому контакту второго нормально разомкнутого ключа, второй контакт которого соединен с цшной нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1.Мирский Г.Л. Аппаратурное определение характеристик случайных процентов. М., Энергия, 1972, с.346.

2.Авторское, свидетельство СССР № 285368, кл. G06G 7/52, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения условного математического ожидания | 1981 |

|

SU1003097A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Цифровой компандер | 1986 |

|

SU1427575A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Вероятностный коррелометр | 1978 |

|

SU942037A1 |

| Система контроля параметров | 1984 |

|

SU1190364A1 |

| Генератор широкополосных случайных процессов | 1980 |

|

SU881743A1 |

| Устройство для определения момента изменения свойств случайного процесса | 1983 |

|

SU1166149A1 |

0US. 1

Авторы

Даты

1983-01-30—Публикация

1981-06-29—Подача