(5) ЦИФРОВОЙ РЕГИСТРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| ИЗМЕРИТЕЛЬ ХАРАКТЕРИСТИК ФАЗОВЫХ ФЛУКТУАЦИЙ | 1992 |

|

RU2041469C1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Усреднитель-анализатор спектра Фурье | 1980 |

|

SU955086A1 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1538143A2 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Цифровой регистратор импульсных процессов | 1979 |

|

SU864551A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| ЦИФРОВОЙ МАЛОГАБАРИТНЫЙ USB ОСЦИЛЛОГРАФ | 2009 |

|

RU2402024C1 |

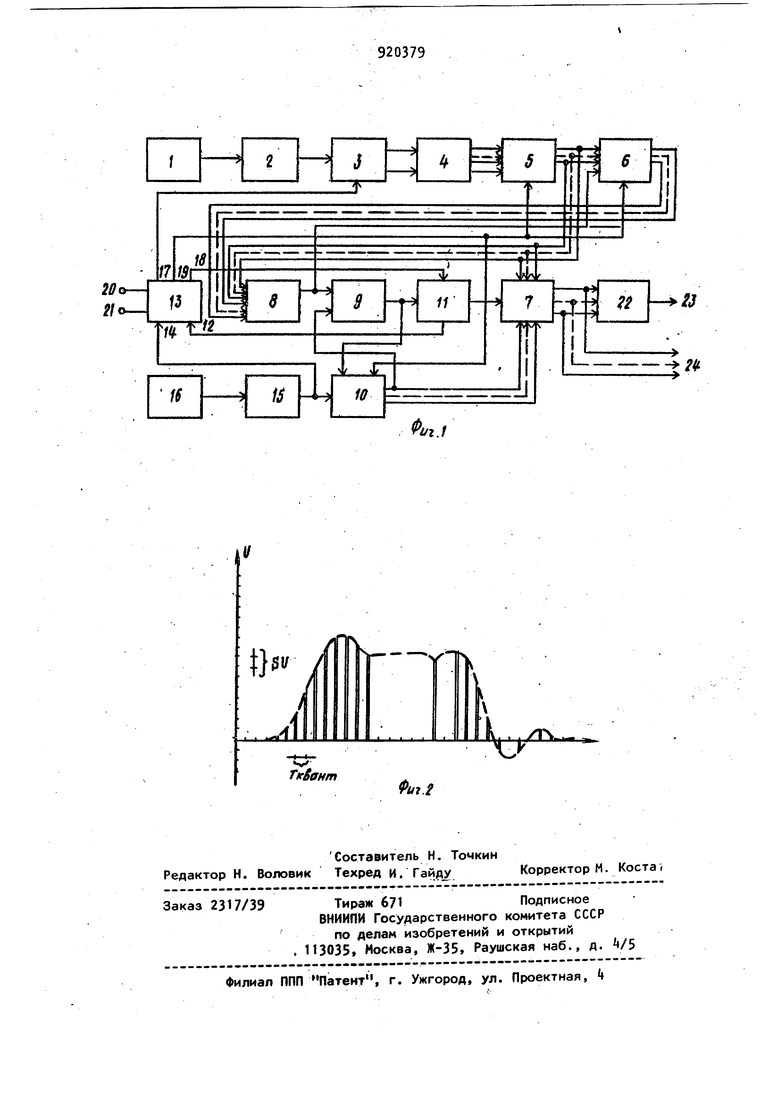

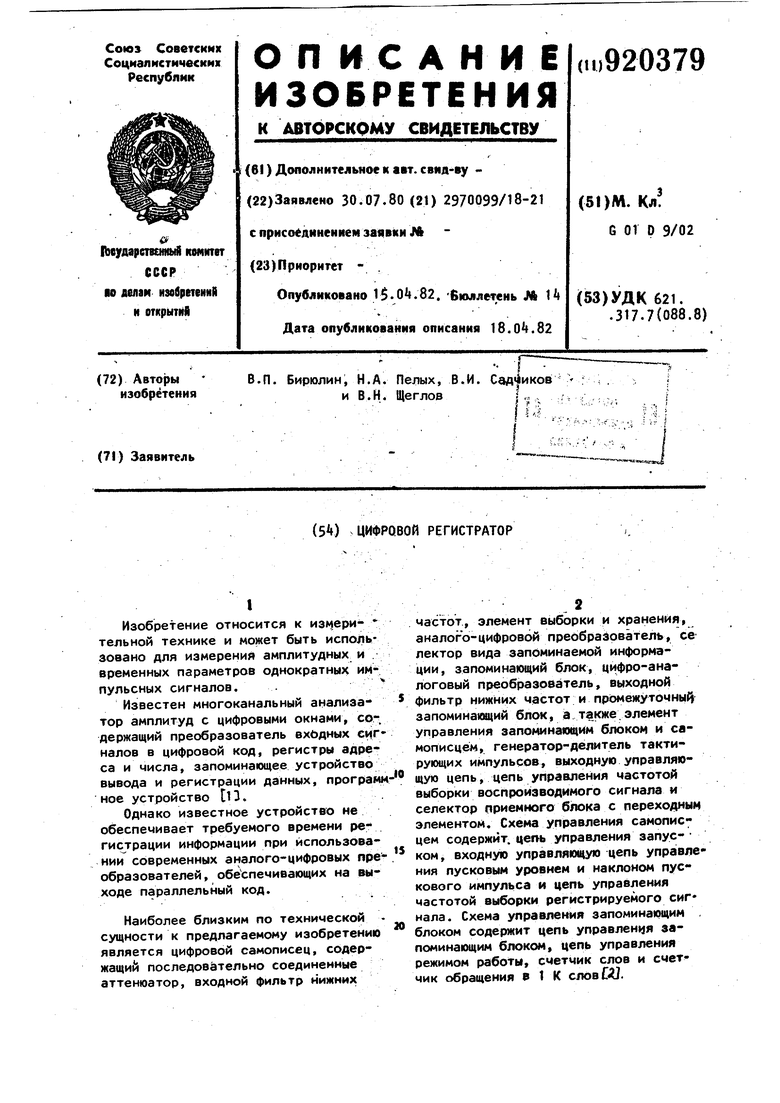

I , . Изобретение относится к тельной технике и может быть использовано для измерения амплитудных и временных параметров однократных импульсных сигналов. Известен многоканальный анализатор амплитуд с цифровыми окнами, содержащий преобразователь вхЬдных ciir налов в цифровой код, регистры адреса и числа, запоминающее устройство вывода и регистрации данных, програм ное устройство П. Однако известное устройство не обеспечивает требуемого времени регистрации информации при использовании современных аналого-цифровых пре образователей , обеспечивающих на выходе параллельный код. Наиболее близким по технической сущности к предлагаемому изобретению является цифровой самописец, содержащий последовётельно соединенные аттенюатор, входной фильтр нижних частот, элемент выборки и хранения, аналого-цифровой преобразователь, се лектор вида запоминаемой информации , запоминающий блок, цифро-аналоговый преобразователь, выходной фильтр нижних частот и промежуточный запоминащий блок, а .элемент управления запоминающим блоком и самописцем, генератор-делитель тактирующих импульсов, выходную управляющую цепь, цепь управления частотой выборки воспроизводимого сигнала и селектор приемного блока с переходным элементом. Схема управления самописцем содержит. цегн| управления запуском , входную управляю1чую цепь управления пусковым уровнем и наклоном пускового импульса и цепь управления частотой выборки регистрируемого сигнала. Схема управления запоминающим блоком содержит цепь управления запоминающим блоком, цепь управления режимом работы, счетчик слов и счет чик обращения в 1 К слов И. Недостатком данного устройства является постоянный период времени выборок входного сигнала в запоминающий блок, который не зависит от скорости изменения входного сигнала. В результате этого самописец имеет недостаточно большой период развертки (под периодом развертки понимается интервал времени, в течение которого можно регистрировать сигнал на заданной частоте квантования), Период развертки определяется емкостью памяти и равен емкости памяти, делен ной на частоту квантования, требует применения запоминающего блока со значительным объемом памяти и приводит к избыточности запоминаемой информации при регистрации формы импульсных сигналов, имеющих плоскую вершину. Кроме того, в этом устройстве времени записи одной выборки входного сигнала в запоминающем блоке определяется суммой времени преобразования аналого-цифрового преобразователя и времени записи информации из аналого-цифрового преобразователя в запоминающем блоке. За счет наличия последнего времени снижается быстродействие устройства. Цель изобретения - повышение быст родействия цифрового регистра и увеличение периода развертки. Поставленная цель достигается тем что в цифровой регистратор-содержащий аттенюатор, фильтр нижних частот, элементы выборки и хранения, аналого цифровой преобразователь, блок памяти, два элемента управления, генератор тактовых импульсов, и делитель частоты, введены дополнительно гистра хранения, блок сравнения, счетчик тактовых импульсов и логический элемент ИЛИ, причем регистры хранения соединены между собой последователь-но и подключены к выходу аналого-цифрового преобразователя, выход первого регистра хранения подключен к входу блока сравнения и бло ку памяти, выход второго регистра хранения соединен с входом блока сравнения, выход которого соединен с управляющим входом второго регистра хранения и с одним из входов логического элемента ИЛИ другой вход которого соединен с выходом счетчика тaкtoвыx импульсов, а выход подключен к входу второго элемента управле ния и к установочному входу счетчи994 ка тактовых импульсов, выход которс го соединен с входом блока памяти. Новая совокупность признаков позволяет записывать в запоминающий блок каждую последующую выборку вхг ного сигнала только в том случае, если ее амплитуда превышает амплиту ду предыдущей выбоки на абсолютную величину шага квантования входного сигнала по амплитуде (crV), задаваемого блоком сравнения. Если же колебания амплитуды входного сигнала не превышают (сЛ/), например при измерении плоской вершины импульса,. то запись последующей выборки в запоминающем блоке производится при переполнении счетчика тактовых импульсов о При этом время между моментами записи соседних выборок увеличивается в число раз, пропорциональное емкости счетчика тактовых импульсов, в результате чего период развертки регистраторЭ существенно увеличивается. На фиг. 1 представлена структурная схема цифрового регистратора; на фиг. 2 - кривые, поясняющие процесс измерения и регистрации формы однократного импульса напряжения, пунктирной линией показан регистрируемый импульс напряжения, сплошной линией - выборки, записываемые в запоминающем блоке, Цифровой регистратор содержит последовательно соединенные аттенюатор 1, фильтр 2 нижних частот, элемент 3 выборки и хранения, аналогоцифровой преобразователь , выходы которого через регистр 5 хранения подсоединены к соответствующим информационным входам регистра 6 хранения, к первым информационным входам блока 7 памяти и первым входам элемента 8 сравнения, ко вторым входам которой подсоединены соответствующие выходы регистра 6 хранения. Выход элемента 8 сравнения подключён к управляющему входу регистра 6 хранения и одному из входов логического элемента ИЛИ 9, к другому входу которого подключен выход старшего разряда счетчика Ю тактовых импульсов, при этом выходы всех разрядов счетчика 10 тактовых импульсов подключены к соответствующим вторым информационным входам блока 7 памяти. Выход логического элемента ИЛИ 9 подключен к входу установки . в ноль счетчика 10 тактовых импульСОВ и к второму входу второго элемента 11 управления, первый выход которой подключен к первому входу 1 первой элемента J3 управления, а вт рой выход - к управляющему входу бл ка 7 памяти, при этом второй вход I первого элемента 13 управления подключен к счетному входу счетчика 10 тактовых импульсов и к выходу делителя 15 частоты, вход которого подключен к выходу генератора 16 такто вых импульсов. Первый выход 17 первого элемента 13 управления подключен к управляющему входу элемента 3 выборки и хранения, а второй выход 18 - к первому входу второго элемента 11 управления, при этом третий выход 19 первого элемента 13 управления подключен к входам установки в ноль регистров 5 и 6. Кроме того, первый элемент управления имеет два входа: вход 20 для подачи сигнала Сброс и вход 21 для подачи сигнала Пуск, которые поступают в регистратор от внешних устройств. Информация из блока 7 памяти регистра может выводиться в аналоговом виде через цифро-аналоговый преобразователь 22 с выхода 23, либо в цифровом виде непосредственно из блока 7 памяти с .выхода 2А. Цифровой регистратор работает сле дующим образом. После включения напряжения питания и подачи импульса Сброс на вхо 20 первого элемента 13 управления по следняя формирует на выходе 19 сигнал, устанавливающий регистры 5 и 6 и счетчик 10 тактовых импульсов в ноль. После подачи импульса Пуск на вход 21 первого элемента 13 управ .ления последняя формирует на выходе 18 сигнал для второго элемента tl управления, запрещающий считывание информации из блока 7 памяти, после чего начинается обработка аналогового сигнала, поступающего на вход аттенюатора 1.При этом аналоговый сиг нал через аттенюатор 1, фильтр 2 ниж них частот, элемент 3 выборки и хра нения поступает на. вход аналого-цифрового преобразователя k. По сигналу Конец преобразования, поступающего от аналого-цифрового преобразователя 4, производится перезапись цифровой информации из аналого-цифрового преобразователя в регистр 5 хранения, после чего от первого элемента 13 управления с выхода 17 через эле793 выборки и хранения поступает следующий сигнал запуска аналого-цифрового преобразователя . При этом период квантования входного сигнала X-fcciHT. определяется частотой колебаний генератора 16 тактовых импульсов и коэффициентом деления делителя 15 частоты. Минимальный же период квантования определяется временем преобразования аналого-цифрового преобразователя. Тактовые импульсы с выхода делителя 15 частоты поступают на вход 14 элемента 13 управления и на счетный вход счетчика 10 тактовых импульсов. Во время преобразования следующей выборки входного сигнала информация об амплитуде предыдущей выборки с выходов регистра 5 хранения поступает на соответствующие первые входы блока 8 сравнения, на вторые входы которой поступает цифровая информация 00..О с соответствующих выходов регистра 6 хранения. При увеличении амплитуды входного сигнала увеличивается значение кода .числа на выходах регистра 5 хранения, и как только разность чисел, поступающих на первые и.вторые входы элемента 8 сравнения, по абсолютной величине станет равной или больше шага квантования . по амплитуде, задаваемого элементом 8 сравнения, на выходе последней формируется сигнал, который через логический элемент ИЛИ 9 поступает на вход второго элемента 11 управления, формирующей сигнал разрешения записи информации в блок 7 памяти. По .этому, сигналу число с выходов регистра 5 хранения и количество импул1 сов из счетчика 10 тактовых импульсов, пропорцио.нальное времени, прошедшему с момента поступления импульса Пуск, записываются в блок 7 памяти, после чего производится перезапись числа из регистра 5 в регистр 6 хранения и установка счетчика 10 тактовых импульсов в ноль, и процесс сравнения повторяется, но при этом сравнение чисел, посту/1ающих через регистр 5 хранения от аналого-цифрового преобразователя t, в блоке 8 сравнения производится с предыдущим записанным числом. Запись информации в блок 7 памяти роизводится во время преобразования налого-цифровым преобразователем k ледующей выборки входного сигнала. сли же колебания амплитуды входно- . 79 го сигнала по абсолютной величине не превышают шага квантования по амплитуде, задаваемого элементом 8 сравнения, запись информации в блок 7 памяти производится при переполнении счетчика 10 тактовых импульсов, при этом период квантования определяется емкостью счетчика 10 тактовых импуль сов, причем каждый раз при записи амплитуды выборки одновременно произ водится запись числа импульсов из счетчика 10 тактовых импульсов, кото рое пропорционально времени, прошедшему с момента записи предыдущей выборки . ПоследнееЪбеспечивает однозначное соответствие между амплитудными и временными параметрами .регист рируемого сигнала. После заполнения всех ячеек блока 7 памяти от второго элемента 11 управления на вход 12 первого элемента 13 управления npctynaeT сигнал, с помощью которого формируются сигна лы, запрещающие прохождение аналогового сигнала и пусковых импульсов для аналого-цифрового преобразователя k через элемент 3 выборки и хранения, и сигнал для второго элемента 11 управления, разрешающий считывание информации. После этого осуществляется хранение информации в блоке 7 памяти при возможности ее считывания без разрушения. Считывание информации осуществляется в цифровом виде с выхода 2, в. аналоговом виде - с выхода 23 через цифроаналоговый преобразователь 22. При использовании в макете цифрового регистратора аналого-цифрового преобразователя и блока памяти с такими же характеристиками, как и у используемых в известном, а именно восьмиразрядного аналого-цифрового преобразователя с временем преобразования 3 МКС и блока памяти с объемом памяти-1,7 К, были получены следующие характеристики: минимальный период квантования входного сигнала (при измерении быстроизменяющегося сигнала) 3,3 мкс, максимальный период квантования входного сигнала (при измерении постоянного напряжения) МКС. Э В обоих случаях период следования, тактовых импульсов на выходе делителя частоты равен мкс. Таким образом, быстродействие устройства увеличивается по сравнению с известным примерно в три раза, а период развертк-и при использовании восьмиразрядного двоичного счетчика тактовых импульсов при регистрации прямоугольного импульса напряжения увеличивается более чем в-200 раз. формула изобретения .Цифровой регистратор, содержащий аттенюатор, фильтр низких частот, элемент выборки и хранения, аналогоцифровой преобразователь, блок памяти, два элемента управления, генератор тактовых импульсов и делитель частоты, отличающийся тем, что, с целью повышения быстродействия и увеличения периода развертки, в негр введены два регистра хранения, блок сравнения, счетчик, тактовых импульсов и логический элемент ИЛИ, причем регистры хранения соединены между собрй последовательно и подключены к выходу аналогоцифрового преобразователя, выход первого регистра хранения подключен к входу блока сравнения и блоку памяти, выход второго регистра храйения соединен с входом блока сравнения, выход которого соединен с управляющим входом второго регистра хранения и с одним из входов логичесйого элемента ИЛИ, другой вход которого соединен с счетчика такто- -вых импульсов, а выход подключен к входу второго элемента управления; к установочному, входу счетчика тактовых импульсов, выход которого соединен с входом блока памяти. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР; № , кл. 6 01 D 5/00, 1968, 2.Цифровой самописец типа 7502 . Описание и применение, фирма Брюль и К-ьер, Дания, 1972.

Авторы

Даты

1982-04-15—Публикация

1980-07-30—Подача