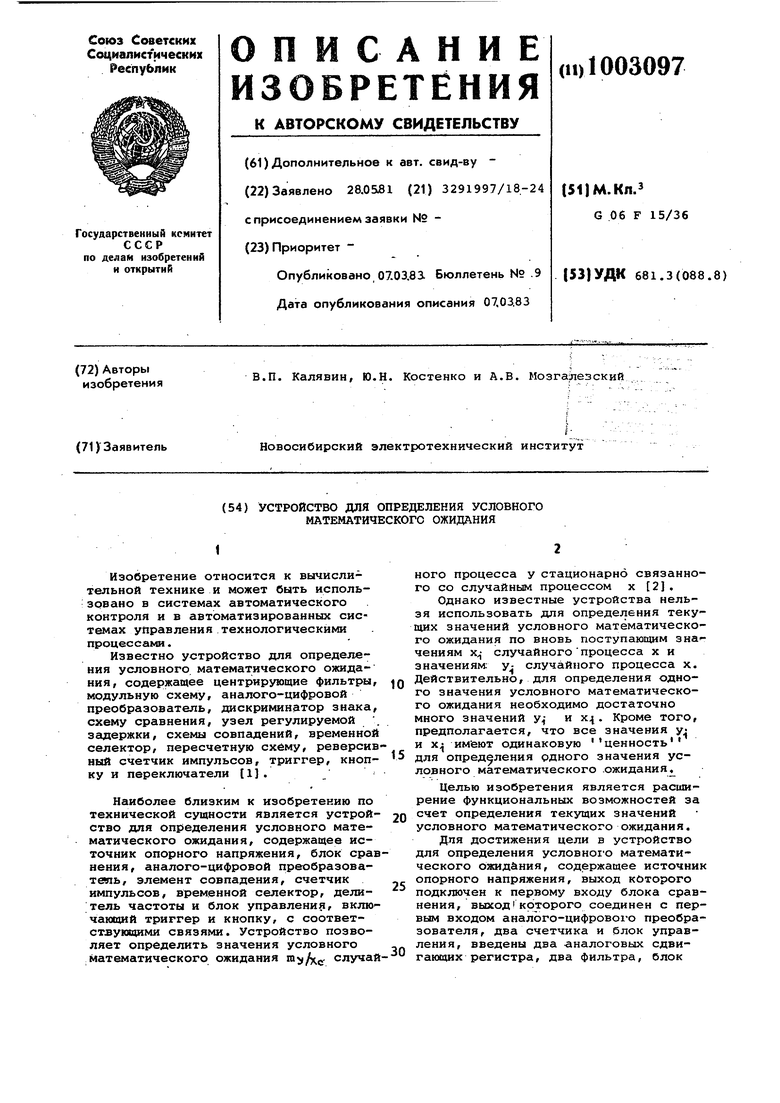

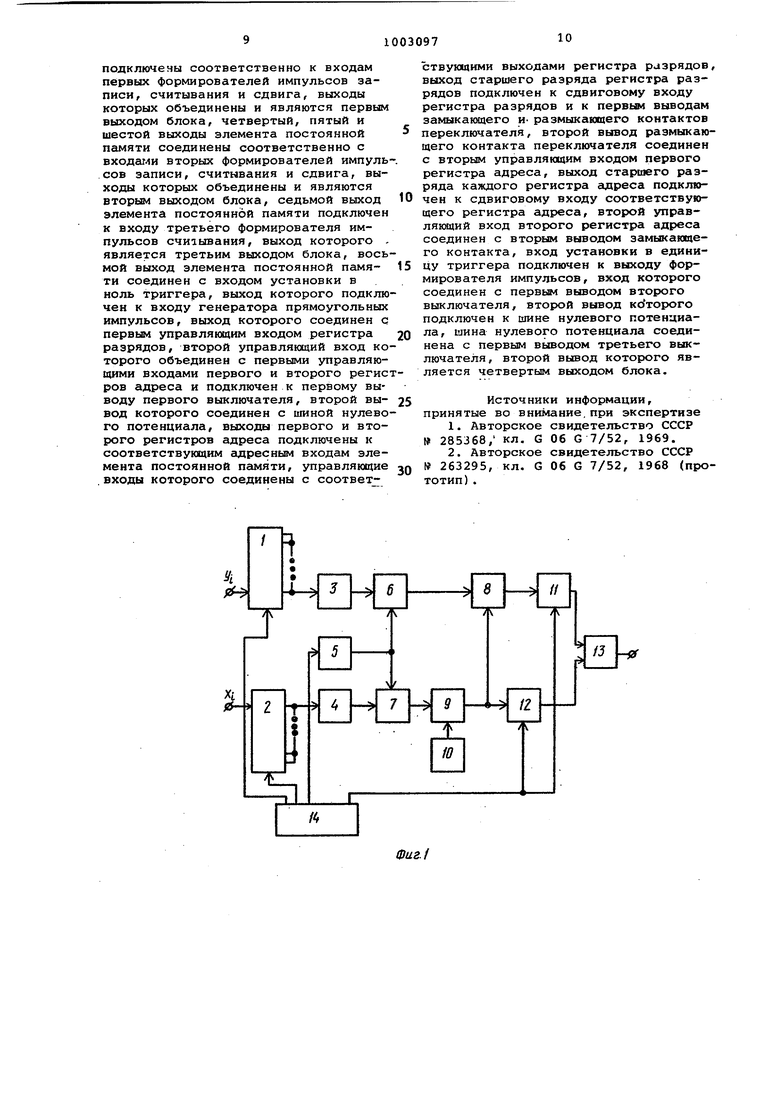

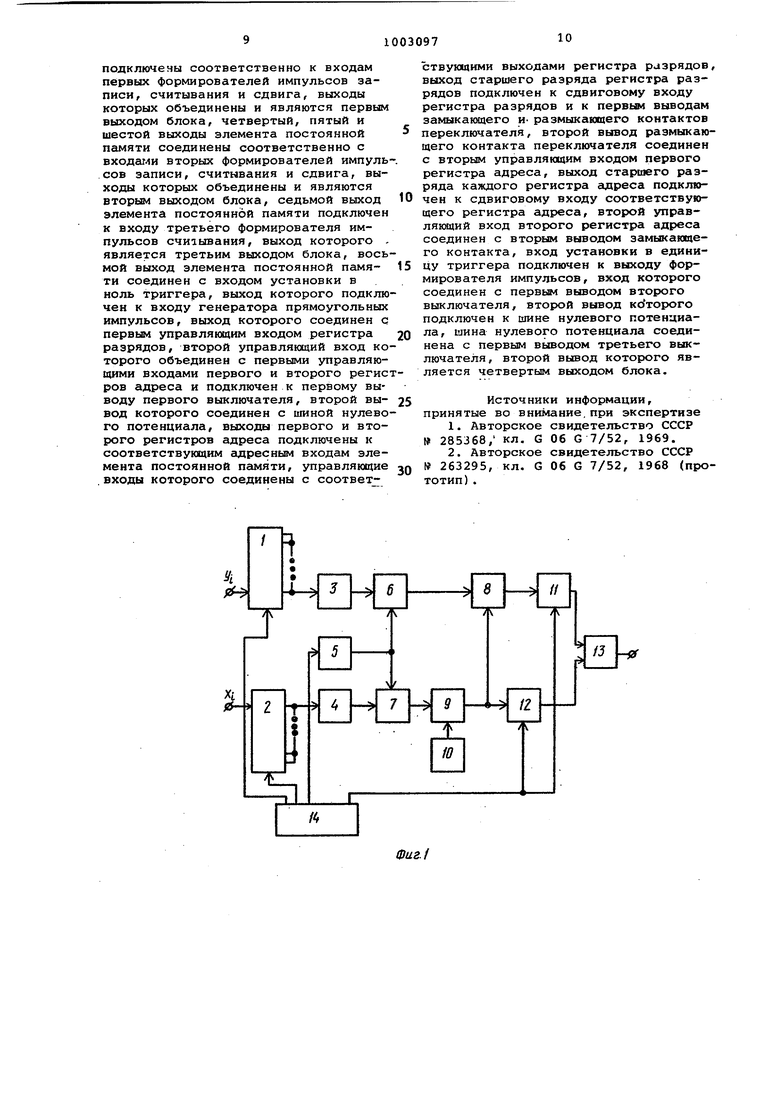

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического контроля и в автоматизированных системах управления технологическими процессами. Известно устройство для определения условного математического ожидания, содержащее центрирующие фильтры модульную схему, аналого-цифровой преобразователь, дискриминатор знака схему сравнения, узел регулируемой задержки, схемы совпадений, временно селектор, пересчетную схему, реверси ный счетчик импульсов, триггер, кноп ку и переключатели 1. Наиболее близким к изобретению по технической сущности является устрой ство для определения условного математического ожидания, содержащее источник опорного напряжения, блок сра нения, аналого-цифровой преобразователь, элемент совпадения, счетчик импульсов, временной селектор, делитель частоты и блок управления, вклю чающий триггер и кнопку, с соответствующими связями. Устройство позволяет определить значения условного математического ожидания ту/у случа ного процесса у стационарно связанного со случайным процессом х 2 . Однако известные устройства нельзя использовать для определения текущих значений условного математического ожидания по вновь поступающим зна чениям случайногопроцесса х и значениям; у- случайного процесса х. Действительно, для определения одного значения условного математического ожидания необходимо достаточно много значений и х. Кроме того, предполагается, что все значения ценность и х имеют одинаковую jrx л ,,ЛЛ jr nj..г«Х 114.4 л JLf для определения одного значения условного математического .ожидания. Целью изобретения является расширение функциональных возможностей за счет определения текущих значений условного математического ожидания. Для достижения цели в устройство для определения условнохО математического ожидания, содержащее источник опорного напряжения, выход которого подключен к первому входу блока сравнения, выход ксЬторого соединен с первым входом аналого-цифрово1о преобразователя, два счетчика и блок управления, введены два -аналоговых сдвигающих регистра, два фильтра, блок постоянной аналоговой памяти, два блока умножения и блок деления, при этом первый и второй выходы блока управления подключены соответственно к первым входам первого и второго аналоговых сдвигающих регистров, выход первого аналогового сдвигающего регистра через первый фильтр соединен с первым -входом первого блока умножения, второй вход которого объединен с первым входом второго блока умножения и соединен с выходом блока постоянной аналоговой памяти, вход: которого подключен к третьему выходу блока управления, выход первого блока умножения соединен с вторым входом аналого-цифрового преобразователя, выход которого.подключен.к.первому входу первого счетчика, второй вход которого объединен с первым входом второго счетчика и соединен с четвер тым выходом блока управления, выход второго аналогового сдвигающего регистра подключен через второй фильтр к второму входу второго блока умножения, выход которого соединен с вторым-входом блока сравнения, выход которого подключен к второму входу второго счетчика, выходы первого и второго счетчиков соединены соответственно с первым и вторым входами блока деления, выход которого является выходом устройства, вторые входы первого и второго аналоговых сдвигаю щих регистров являются соответствен но первым и вторым входами устройстгва. Кроме того, блок управления содержит два формирователя импульсов записи, три формирователя импульсов считывания, два формирователя импульсов сдвига, элемен-т постоянной памяти, регистр разрядов, два регистра адреса, формирователь импульса, триггер, генератор прямоугольных импульсов, переключатель и три выключателя, при этом первый, второй и третий выходы элемента постоянной памяти подключены соответственно к входам первых ; формирователей импульсов записи, считывания и сдвига,выходы которых объединены и являются первьом выхрдом блока, четвертый, пятый, шестой вьргоды элемента постоянной памяти соединены соответственно с входами вторых формирователей импульсов записи, считывания и сдвига, выходы которых объединены и являются вторым выходом блока, седьмой выход элемента постоянной памяти подключен к входу третьв го формирователя импульсов считыва- . шГя, выход которого является третьим выходом блока, восьмой выход элемента Постоянной памяти соединен.с входом установки в ноль триггера, выход которого подключен к входу, генератора прямоугольных импульсов, выход которого соединен с первым управляющим входом регистра разрядов, второй управляющий вход которого объединен с первыми управляющими входами первого и второго регистров адреса и подключен к первому выводу первого выключателя, второй вывод которого соединен с ишной нулевого потенциала, выходы первого и второго регистров адреса подключены к соответствующим адресным входам элемента постоянной памяти, управляющие входы которого соединены с соответствующими выходами регистра разрядов, выход старшего разряда регистра разрядов подключен к сдвиговому входу регистра разрядов и к первым выводам замыкающего и размыкающего переключателя, второй вывод размыкающего контакта переключателя соединен с вторым управляющим входом первого регистра адреса, выход старшего .разряда каждого регистра адреса подключен к сдвиговому входу соответствующего регистра адреса, второй управляющий вход второго регистра адреса соединен с вторым выводом замыкающего контакта, вход установки в единицу триггера подключен к выходу формирователя импульсов, вход которого соединен с первым выводом второго выключателя, второй вывод которого подключен к шине нулевого потенциала, шина нулевого потенциала соединена с первым выводом третьего выключателя, второй вывод которого является четвертым выходом блока. На фиг, 1 представлена блок-схема устройства на фиг. 2 - структурная схема блока управления. Устройство содержит первый аналоговый сдвигающий регистр у,- - АСР 1, служащий для запоминания текущих значений у, 1 1,2... kи допускающий, считывание без расширения информации, а также второй аналоговый сдвигающий регистр х - АСР 2, служащий для запоминания текущих значений , i 1,2... k и допускающий считывание без разрешения информации, кроме того, первый 3 и второй 4 фильтры, блок 5 постоянной -аналоговой памяти, в котором хранятся значения функции веса Ч , первый блок 6 умножения, служащий для получения значений y.f. , второй блик 7 умножения, служащий для получения значений ,,- , аналогоцифровой преобразователь (АЦП) 8, блок 9 сравнения, источник 10 опорного напряжения, первый счетчик 11 импульсов, второй счетчик 12 импульсов, блок 13 деления и блок 14 управления. Блок 14 управления содержит первый формирователь импульсов записи 15, первый формирователь импульсов считывания 16, первый формирователь импульсов сдвига 17, второй формирователь импульсов записи 18, второй формирователь импульсов считывания 19, второй формирователь импульсов сдвига 20, третий формирователь импульсов считывания 21, элемент постоянной памяти 22, регистр разрядов 23, первый и второй регистры адреса 24 и 25 формирователь импульса 26, триггер 27,генератор прямоугольных импульсо 28,выключатели 29-31 и переключател 32. Известно, что оценку условного ма тематического ожидания ini;A(j эргодического случайного стационарного про цесса y(t) по значению х эргодического, стационарно связанного с иссле дуемым, случайного стационарного x(t можно определить, располагая двумя реализациями: по одной каждого из названных процессов по выражению . N rv/Xc Ti |,tt)/X,i CD .., П О, 1 , где N - количество пересечений к(t ) Xj, в реализации х (t) ; X - значение, относительно кото рого определяется оценка условного математического ожидания. Если же процессы х t) и y(t) не стационарные или нестационарно связанные, т.е. имеют дрейф параметров во времени, то оценка условного математического ожидания будет сильно смещенной..В этом случае необходимо знать текущее значение определяемой оценки. Один из возможных способов решения этой задачи известен как метод замороженных коэффициентов или метод скользящего интервала . Считается, что в течение некоторо го интервала наблюдений Т + а можно принять, что -vcons t, где i k + а, k - 1 + - Т; a 0,1,2,. . . ; D k. Тогда, пользуясь информацией, получаемой в интервале наблюдений T(i k - Т, ..., kj,можно найти наилучшие в смысле минимума среднего квадрата ошибки значения оценок .(k + а) . Кроме этого, влияния информации, полученной в моменты времени k,k - 1 и.т.д., на точ ность оценки m,/yj.(k + а) неодинаково. Для учета изменения ценности информации вводится функция веса 4(k, i, j ) , где k - число наблюдений в выборке; i - номер текущего наблюд ния: (f - некоторый параметр функции веса. Как правило, полагают, что с увеличением возраста наблюдений ценность их для определения оцен ки if, (k + а) убывает, т.е. функция веса уменьшается с ростом (k - i). Функции веса могут быть, например, вида: If, ( 1 -Г) «/гТ где - (О - 1) и другие. Предлагаемое устройство реализует алгоритм определения текущих оценок условного математического ожидания по выражению (1) с использованием метода скользящего интервала и с учетом ценности информации о процессах x(t) и y(t) с помсядью выбранной заранее функции веса. Устройство работает следующим образом. В первые к тактов работы устройства происходит заполнение ДСР 1 и АСР 2 измереннЕлми значениями х- и У|- соответствунлдих t . Для этого блок 14 управления последовательно подает команды ha запись и сдвиг значений в регистрах. В следующие к тактов осуществляется попарное считывание значений х if из регистров и значений Ц из блока 5. В процес-i се считывания на выходах блоков умножений 2 имеем непрерывные реализации соответственно случайных процессов x(t) и y{t) с учетом функции веса. При совпадении значений реализации x(t) со значением х, которое выдается источником опорного напряжения 10, блок 9 сравнения выдает импульс, который записывается во второй счетчик 12 импульсов и открывает АЦП 8. Напряжение реализации у процесса Y(t), соответствующее х х, преобразуется в число импульсов, которое считается первьт счетчиком 11 импульсов. После считывания последней тройки у , х , if показание счетчика 11 будет: , где h - коэффициент-пропорциональности АЦП 8. В счетчике 12 будет зафиксировано значение N, равное числу пересечений х X(j в отрезке реализации x(t). Блок 13 деления определит.значение, которое и будет пропорционально оценке (k); ь. --Vim jy Ск). К 14 Таким образом, после тактов считывания будет определена k-ая оценка условного математического ожидания. Далее устройство приводится в исходное состояние. Для этого блок 14 управлениявьщает импульс на сброс счетчиков в О и подает команду на сдвиг информации в регистрах, т.е. N-oe значение переписывается на место (N-l)-ro, ()-e переписывается на место {N-2)-го и т.д. Затем подается команда на запись х, и значений В следующем такте осуществ л(ется считывание троек значений х. , У(гЧ, . В конце последнего такта считывания блок 13 деления определит -. (k+l)-oe значение искомой оценки ™;з/Хс ) Снова устройство приводйтся в исходное состояние, далее записываются значения х..„ У, , 1 Т 2. К, . и т.д. Таким образом, в конце каждого (k+ 3)-го цикла считывания устройство будет определять (k+j)-ое значение оценки условного математического ожидания, т.е. устройсто обеспечивает определение текущего значения условного математического ожидания по вновь поступающим значениям х случайного процесса x(t) и значениям у. случайного процесса Y(t)c учетом предьадущей информации о процессах. Работает устройство следующим об разом. -.... Первой кнопкой блокприводится в Исходное состояние. Для чего регистры 23-25 очищают и записывают в первые ячейки . При нажатии второй кнопки триггер 27 опрокидывается и открывает генератор 28, с которого импульсы поступают на регистр разрядов 23. Из элемента постоянной памяти считывается первое слово. По окон чанию считывания последним -разрядным импульсом происходит сдвиг 1 в регистре адреса для считывания-второ го слова и т.д. до тех пор, пока не будут считаны k слов и не произо дет заполнение АСР 1 и АСР 2 устройс ва измеренными значениями х| и соответствукадих t. Затем переключатель 32 переключают в противоположное положение. После этого в цикле происходит генерация команд,обеспечивающих последовательное считывание данных из АСР 1 и 2 и блока 5, сдвиг данных в АСР 1 и 2, запись вновь пос тупающих текущих значений х и , вновь считывание данных из 1,2,5 и .т.д. Каждый раз, когда необходимо ос тановит генерацию команд в послед то щем такте, в 8 разряде слова, соответствующего предыдущему такту, долж на быть записана . Эта i по окончанию считывания очередного слова перебросит триггер 27, который запретит работу генератора 28. Для продолжения работы блока необходимо повторно нажать выключатель 30. Применение устройства, дает возмож ность решить задачи прогнозирования изменения состояния изделий, благода ря чему становится возможным решить многие производственные и эксплуатационные задачи. Формула изобретения 1. Устройство для определения условного математического ожидания, содержащее источник опорного напряжения, выход которого подключен к первому входу блока сравнения, выход которого соединен с первЕлм входом аналого-цифрового преобразователя, два счетчика, блок управления, отличающееся тем, что, с целью расширения его функциональных возможностей за счет определения текущих значений условного математического ожидания, в него введены два аналоговых сдвигающих регистра, два фильтра, блок постоянной аналоговой памяти, два блока умножения и блок деления, причем первый и второй выходы блока управления подключены соответственно к первым входам первого и второго аналоговых сдвигающих регистров, выход первого аналогового сдвигающего регистра через первый фильтр соединен с первым входом первого блока умножения, второй вход которого объединен с первым входом второго блока умножения и соединен с выходом блока постоянной аналоговой памяти, вход которого подключен к третьему выходу блока управления, выход первого блока умножения соединен с вторым входом аналого-цифрового преобразователя , выход которого подключен к первому входу первого счетчика, второй вход которого объединен с nepBi jM входом второго счетчика и соединен с четвертым выходом блока управления, выход второго аналогового сдвигакадего регистра подключен через второй фильтр к второму входу второго блока умножения, выход которого соединен с вторым входом блока сравнения, выход которого подключен к второму входу второго счетчика, выходы первого и второго счетчиков соединены соответственно с первым и вторым входами ; блока деления, выход которого является выходом устройства, вторые входы первого и второго аналоговых сдвигающих регистров являются соответственно .перВЕЛм и вторым входами устройства. -2. Устройство по п. 1, о т л и чающееся тем, что блок управления содержит два фopмиpJвaтeля импульсов записи, три формирователя импульсов сдвига, элемент постоянной памяти, регистр разрядов,.два регистра адреса, формирователь импульса, триггер, генератор прямоугольных импульсов, переключатель.и три выключателя, причем первый, второй и третий выходы элемента постоянной памяти

подключены соответственно к входам первых формирователей импульсов записи, считывания и сдвига, выходы которых объединены и являются первым выходом блока, четвертый, пятый и шестой выходы элемента постоянной памяти соединены соответственно с входаг и вторых формирователей импуль.сов записи, считывания и сдвига, выходы которых объединены и являются вторым выходом блока, седьмой выход элемента постоянной памяти подключен к входу третьего формирователя импульсов счиаывания, выход которого является третьим выходом блока, восьмой выход элемента постоянной памяти соединен с входом установки в ноль триггера, выход которого подключен к входу генератора прямоугольных импульсов, выход которого соединен с первым управлякадим входом регистра разрядов, второй управляющий вход которого объединен с первыми управляющими входс1ми первого и второго регистров адреса и подключен к первому выводу первого выключателя, второй вывод которого соединен с шиной нулевого потенциала, выходы первого и второго регистров адреса подключены к соответствующим адресным входам элемента постоянной памяти, управляющие .входы которого соединены с соответствующими выходами регистра разрядов выход старшего разряда регистра разрядов подключен к сдвиговому входу регистра разрядов и к первым выводам замыкающего и размыкающего контактов переключателя, второй вывод размыкающего контакта переключателя соединен с вторым управляющим входом первого регистра адреса, выход старшего разряда каждого регистра адреса подключен к сдвиговому входу соответствующего регистра адреса, второй управлякадий вход второго регистра адреса соединен с вторым выводом замыкающего контакта, вход установки в единицу триггера подключен к выходу формирователя импульсов, вход которого соединен с первь№( выводом второго выключателя, вторюй вывод КОТОЕЮГО подключен к шине нулевого потенциала, шина нулевого потенциала соединена с первым выводом третьего выключателя, второй вывод которого является четвертым выходом блока.

Источники информации, принятые во внимание,при экспертизе

1.Авторское свидетельство СССР 285368/ кл, G 06 G 7/52, 1969.

2.Авторское свидетельство СССР

263295, кл. G 06 G 7/52, 1968 (прототип) .

У Г

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения коэффициентов линейной регрессии | 1981 |

|

SU993291A1 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1553919A1 |

| Устройство для определения среднеквадратического значения переменного сигнала | 1989 |

|

SU1781686A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для считывания контуров изображений | 1981 |

|

SU1007114A1 |

| Вероятностный коррелометр | 1978 |

|

SU942037A1 |

| Статистический анализатор | 1988 |

|

SU1675904A1 |

| Устройство для измерения вероятностных характеристик фазы случайного сигнала | 1985 |

|

SU1320822A1 |

| Вероятностный коррелометр | 1979 |

|

SU1023338A1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

Авторы

Даты

1983-03-07—Публикация

1981-05-28—Подача