1132

{ТэсГбретение относится к цифровой вычислительной технике и может быть использовано в устройствах цифровой обработки сигналов.

Цель изобретения - повышение точности цифрового фильтра за счет уменьшения ошибок округления без повьше- ния разрядности элементов цифрового фильтра.

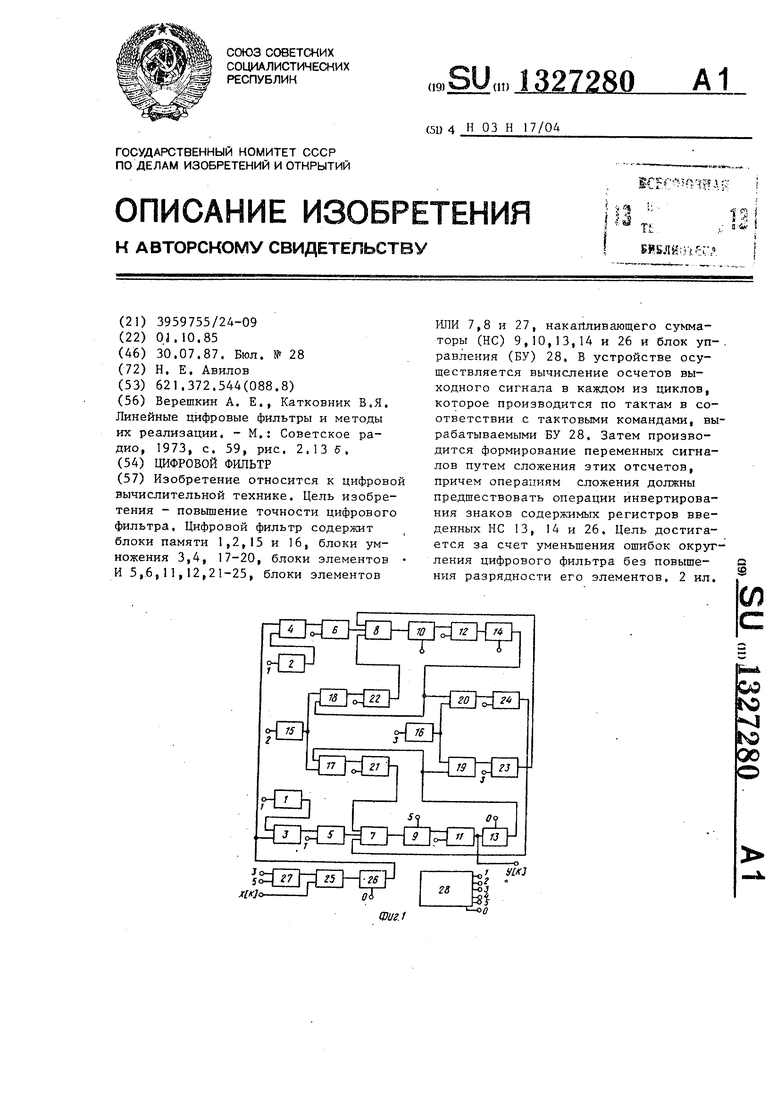

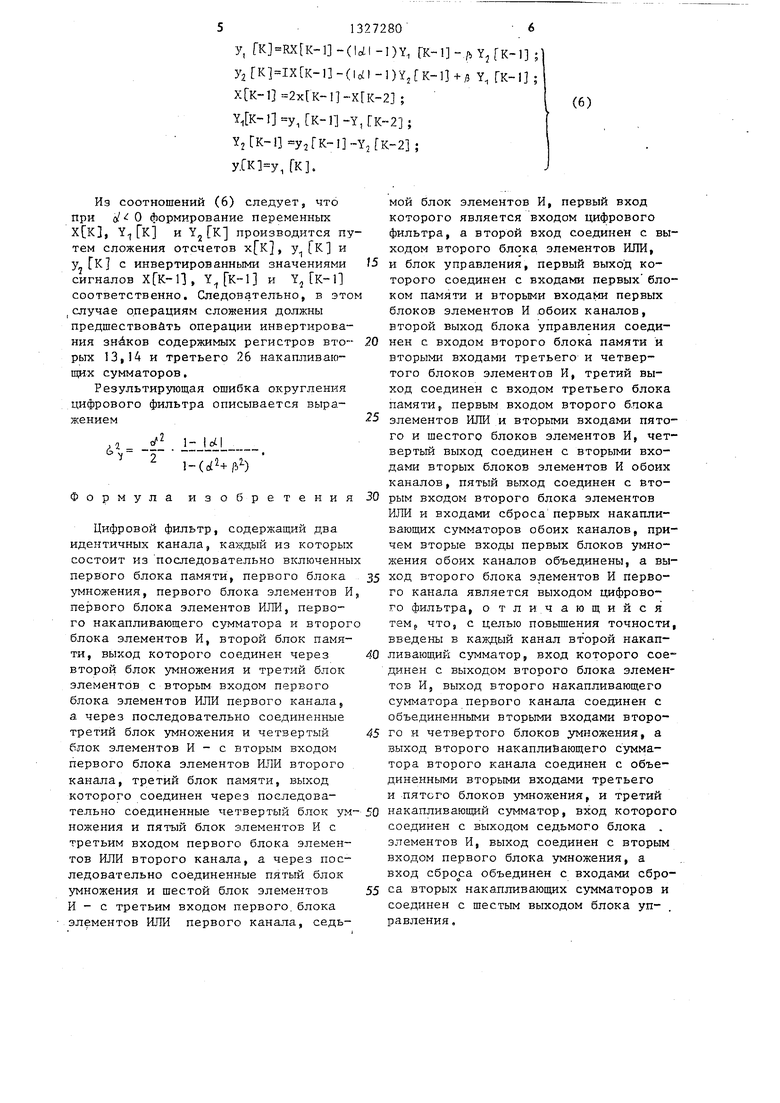

На фиг, 1 представлена структурная электрическая схема цифрового фильтра; на фиг. 2 - то же, блока управления.

Цифровой фильтр содержит первый и второй каналы, состоящие из первого блока 1(2) памяти, первого блока ,3(4) умножения, первого блока 5(6)

(signc)(|ot|-I)YjKyjK IX K-l +(signc)()Y2rKX K-l 2x K-ll+(signo)xrK-2 ;

Yi K-I yjK-l +(signo)Y, .

+ (sign )Yj K-21;

,

реализующей передаточную aiZ

H(Z)

+a,Z-2

1+b +biZ

b - параметры передаточной функции;

a + d a-, .

(3)

у + ()Y K-ijyj CK Ix K-J + (oi-l) хГк-1 2х К-1 +Х К-21 ; Yi K-l yJk-l +Y, Y2CK- yjK-l Y2 K-2 ;

.

Работа цифрового фильтра при с( О заключается в следующем. Вычис ле,ние отсчетов выходного сигнала в каждом из циклов производится по тактам в соответствии с тактовыми командами 1-5, вырабатываемыми блоком 28 управления. До начала вычислительного процесса в первый 12, втор.ой 15 и третий 16 блоки памяти записываются .соответствующие значения коэффициен02

элементов И, первого блока 7(8) элементов И.ПИ, первого накапливающего сумматора 9(10), второго блока 11(12)

элементов И и второго накапливающего сумматора 13(14), второй блок 15 ра- мяти, третий блок 16 памяти, ; второй 17, третий 18, четвертый 19 и пятый 20 блоки умножения, третий 21, четвертый 22, пятый 23, шестой 24 и седьмой 25 блоки элементов И, третий накапливающий сумматор 26, второй блок 27 элементов ИЛИ и блок 28 управления, содержащий задающий

генератор 29, счетчик 30 импульсов, дешифратор 31.

Работа цифрового фильтра описы - вается системой уравнений .

(1)

0

o( действительная часть комплексно-сопряженных полюсов; /5 - мнимая часть комплексно-сопряженных полюсов ЦИФРОВОГО фильтра;

. U . и 2

(4)

5

--,

ft

°.

, I 2

При положительных значениях коэффициента система уравнений (1) принимает вид

(5)

тов Rj 1,,/;,; первые 9,10, вторые 13,14 и третий 26 накапливающие сумматоры устанавливаются в нулевое- состояние.

В первом такте вычислительного цикла команда подается на входы первых блоков 1 и 2 памяти и первых блоков 5 и. 6 элементов И. При этом на входы первого блока 3 умножения перого канала поступают значения коэфициента R и отсчет сигнала , а с выхода первого блока 3 произвеение через первый блок 5 элементов И подается на первый вход ервого блока 7 элементов ИЛИ и с выхода этого блока - на вход первого накапливающего сумматора 9, Аналогично на вход накапливающего сумматора 10 второго канала поступает сигнал произведения .

Во втором такте вычислений разрешающая команда 2 от блока 28 управения подается на вход второго блока 15 памяти и третьего 21 и четвертого 22 блоков элементов И, По этой комане с выхода второго блока 15 памяти а входы второго и третьего 18 блоов умножения подается значение ко- эффициента () . Одновременно на второй вход второго блока 17 умножеия с выхода второго накапливающего сумматора 13 поступает сигнал Гк-1, а на второй вход третьего блока 18 умножения с выхода второго накапливающего сумматора 14 - сигнал , С выходов второго 17 и третьего 18 блоков умножения сигналы произведений (o/-l)Y К-1 и (с/-1) через третий 21 и четвертый

22блоки элементов И и первые блоки 7,8 элементов ИЛИ соответственно подаются на входы первых накапливающих сумматоров 9,10, где складываются с

записанными в первом такте значениями произведений и 1ХСк-1.

В третьем такте, выполняемом по команде 3 блока 28 управления, разрешающие команды подаются на входы третьего блока 16 памяти и пятого

23и шестого 24 блоков элементов И, При этом с выхода третьего блока 16 памяти на входы четвертого 19 и пятого 20 блоков умножения подается код коэффициента . С выхода второго накапливающего сзгмматора 13 на второй вход четвертого блока 19 умножения поступает отсчет сигнала , а

с выхода второго накапливающего сумматора 14 на вход пятого блока 20 умножения - отсчет сигнала Y. К-1 , Произведение /ь с выхода четвертого блока 19 умножения через пятый блок 23 элементов И и первый блок 5 элементов ИЛИ подается на вход первого накапливающего сумматора 10, а произведение с выхода пятого блока 20 умножения через шестой блок 24 элементов И и первый блок 7

0

5

5

0

5

0

5

0

5

элементов ИЛИ - на вход первого накапливающего сумматора 9.

В результате трех тактов вычисления в регистрах первых накапливающих сумматоров 9,10 соответственно образуются сигналы сумм:

у, K RXfK-l + U-l)Y, K-lj- /jYj К-1 ; у K IXlK-l +() /jYjK-1 .

Кроме того, по команде 3, подаваемой на первые входы второго блока 27 элементов РШИ, отсчет входного сигнала через седьмой блок 25 элементов И поступает на вход третьего накапливающего сумматорй 26, где складывается с кодом сигнала .

В четвертом такте разрешающая команда 4 подается на входы вторых блоков 11, 12 элементов И. В этом такте отсчет выходного сигнала у к с выхода первого накапливающего сумматора 9 через второй блок 1I подается на выход фильтра и на вход второго накапливающего сумматора 13, где образуется сумма Y ,Гк1+ +Y к- , от&чет сигнала с выхода первого накапливающего сумматора 10 через второй блок 12 поступает на вход второго накапливающего сумматора 14 и образует сумму yjKl .

В пятом такте по команде 5 производится повторное сложение отсчета входного сигнала с содержимым регистра третьего накапливающего сумматора 26 и формируется сигнал , а также прбизво- дится установка в О первых накапливающих сумматоров 9,10,

Таким образом, в К-м цикле вычислений получаются значения отсчетов выходного сигнала у К , определяются и записываются значения сигналов XtK, Y, к, YiTK, производятся в нулевое состояние регистры первых накапливающих сумматоров 9, 10, т.е. в регистрах накапливающих сумматоров записывается вся информация, необходимая для вычисления последующего отсчета выходного сигнала,

В следующем (К+1)-м цикле порядок работы цифрового фильтра повторяется.

При о/ О работа предлагаемого цифрового фильтра описывается системой уравнений

1327280

у, (UI-l)Y, (1о(1-1)УДкХ К-1 2хГК-1 -хГК-2 ;

,,rK--2 ;

Y2rK-l y2rK-I -YjK-2 ;

y..

Из соотношений (6) следует, что при (У О формирование переменных , YTГК и YjTK производится путем сложения отсчетов , и у к с инвертированными значениями сигналов ХГК-П, и соответственно. Следовательно, в этом случае операциям сложения должны предшествовйть операции инвертирования зн-.ков содержимых регистров вто- рых 13,14 и третьего 26 накапливающих сумматоров,

Результирующая ошибка округления цифрового фильтра описывается выражением

л2

Цифровой фильтр, содержащий два идентичных канала, из которых состоит из последовательно включенны первого блока памяти, первого блока умножения, первого блока элементов И первого блока элементов ИЛИ, первого накапливающего сумматора и второг блока элементов И, второй блок памяти, выход которого соединен через второй блок умножения и третий блок элементов с вторым входом первого блока элементов ИЛИ первого канала, а через последовательно соединенные третий блок умножения и четвертый блок элементов И - с вторым входом первого блока элементов ИЛИ второго канала, третий блок памяти, выход которого соединен через последовательно соединенные четвертый блок ум ножения и пятый блок элементов И с третьим входом первого блока элементов ИЛИ второго канала, а через последовательно соединенные пятый блок умножения и шестой блок элементов И - с третьим входом первого.блока элементов ИЛИ первого канала, седь(6)

мой блок элементов И, первый вход которого является входом цифрового фильтра, а второй вход соединен с выходом второго блока элементов ИЛИ, и блок управления, первый выход которого соединен с входами первых блоком памяти и вторыми входами первых блоков элементов И .обоих каналов, второй выход блока управления соединен с входом второго блока памяти и вторыми входами третьего и четвертого блоков элементов И, третий выход соединен с входом третьего блока памяти, первым входом второго блока элементов РШИ и вторыми входами пятого и шестого блоков элементов И, четвертый выход соединен с вторыми входами вторых блоков элементов И обоих каналов, пятый выход соединен с вторым входом второго блока элементов ИЛИ и входами сброса первых накапливающих сумматоров обоих каналов, причем вторые входы первых блоков умножения обоих каналов объединены, а выход второго блока элементов И первого канала является выходом цифрового фильтра, о тли,чающийся теМр что, с целью повьш1ения точности введены в каждый канал второй накапливающий сумматор, вход которого соединен с выходом второго блока элементов И, выход второго накапливающего сумматора первого канала соединен с объединенными вторыми входами второго и четвертого блоков умножения, а выход второго накапливающего сумматора второго канала соединен с объединенными вторыми входами третьего и пятого блоков умножения, и третий накапливающий сумматор, вход которого соединен с выходом седьмого блока . элементов И, выход соединен с вторым входом первого блока умножения, а вход сброса объединен с входами сброса вторых накапливающих сумматоров и соединен с шестьм выходом блока управления ,

фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1982 |

|

SU1059669A1 |

| Субоптимальный нелинейный фильтр | 1990 |

|

SU1714618A1 |

| Цифровой фильтр с перестраиваемым комплексным коэффициентом передачи | 1975 |

|

SU596953A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

| Цифровой анализатор спектра | 1981 |

|

SU974374A1 |

| Цифровой фильтр | 1987 |

|

SU1390784A1 |

| Цифровой коррелометр | 1985 |

|

SU1298767A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Цифровой фильтр | 1988 |

|

SU1555826A1 |

Изобретение относится к цифровой вычислительной технике. Цель изобретения - повышение точности цифрового фильтра. Цифровой фильтр содержит блоки памяти 1,2,15 и 16, блоки умножения 3,4, 17-20, блоки элементов И 5,6,11,12,21-25, блоки элементов ИЛИ 7,8 и 27, накапливающего сумматоры (НС) 9,10,13,14 и 26 и блок управления (БУ) 28. В устройстве осуществляется вычисление осчетов выходного сигнала в каждом из циклов, которое производится по тактам в соответствии с тактовыми командами, вырабатываемыми БУ 28. Затем производится формирование переменных сигналов путем сложения этих отсчетов, причем операциям сложения должны предшествовать операции инвертирования знаков содержимых регистров введенных НС 13, 14 и 26. Цель достигается за счет уменьшения ошибок округления цифрового фильтра без повышения разрядности его элементов. 2 ил. с S С Ф1/г.г -00

| Верешкин А | |||

| Е., Катковник В,Я | |||

| Линейные цифровые фильтры и методы их реализации | |||

| - М.: Советское радио, 1973, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-07-30—Публикация

1985-10-01—Подача