ф1/г.

Изобретение относится к средствам, используемым в системах цифровой обработки сигналов, и может быть реализовано на основе элементов цифровых вычислительных устройств.

Известен цифровой фильтр, coдep жащий счетчик, выходы которого соединены с дешифраторами, а вход счетчика соединен с входом управляемого ключа, управляющий вход которого через блок управления соединен с выходами дешифраторов, причем выход ключа является выходом фильтра СIX

Однако известный цифровой фильтр не обеспечивает высокой точности.

Наиболее близким к предлагаемому техническим решением является цифровой фильтр, содержащий два блока памяти коэффициентов, блок управления, последовательно соединенные первый блок умножения и первый накаливающий сумматор, выход которого подключен к первым входам первого и второго элементов И, а также третий, четвертый, пятый и шестой элементы И и последовательно соединенные второй блок умножения и второй накапливающий сумматор, выход которого подключен к первому входу четвертого элемента И, выход которого является выходом фильтра, информационным входом которого является первый вход пятого элемента И, при этом выход шестого элемента И .подключен к первому входу первого накапливающего сумматора а к входам первого и BTopoio блоков памяти коэффициентов, вторцм входам первого и второго накапливающих сумматоров, первого, второго, четвертого и пятого элементов И и первому входу третьего элемента И подключены соответствующие выходы блока управления, а также два блока округления, преобразователь аналог - код, преобразователь код - аналог, блок памяти, седьмой, восьмой и девятый элементы И 2 .

Однако известный цифровой фильтр обладает низкой точностью за счет большой ошибки округления.

Цель изобретения - повышение точности.

Для достижения поставленной цели в известный цифровой фильтр, содержащий два блока памяти коэффициентов, блок управления, последовательно соединенные первый блок умножения и первый накапливающий сумматор выход которого подключен к первым входам первого и второго элементов И, а также третий, четвертый, пятый и шестой элементы И последовательно . соединенные второй блок умножения и второй накапливающий сумматор, выход которого подключен к первому

входу четвертого элемента И, выход которого является выходом фильтра, информационным входом которого является первый вход пятого элемента И, при этом выход шестого элемента И подключен к первому входу первого накапли-ваквдего сумматора, а к входа первого и второго блоков памяти коэффициентов, вторым входам первог и второго накапливающих сумматоров, первого, второго, четвертого и пятого элементов И и первому входу третьего элемента И подключены сортветствующие выходы блока управления, введены третий и четвертый накапливакяцие сумматоры, ппичем выход первого блока памяти коэффициентов подключен к первому йходу первого блока умножения, а выход первого элемента И черейтретий накапливающий сумматор подключен к второму, входу третьего элемента И, выход которого подключен к второму входу перв.ого блока умножения, а к первому и второму входам второго блока умножения подключены соответственно выходы второго элемента И и второго блока памяти коэффициентов, к первому входу четвертого накапливающего сумматора подключен выход пятого элемента И, к первому и второму входам шестого элемента И подключены соответственно выход четвертого накапливающего cyfiMaTopa и соответствующий выход блока управления.

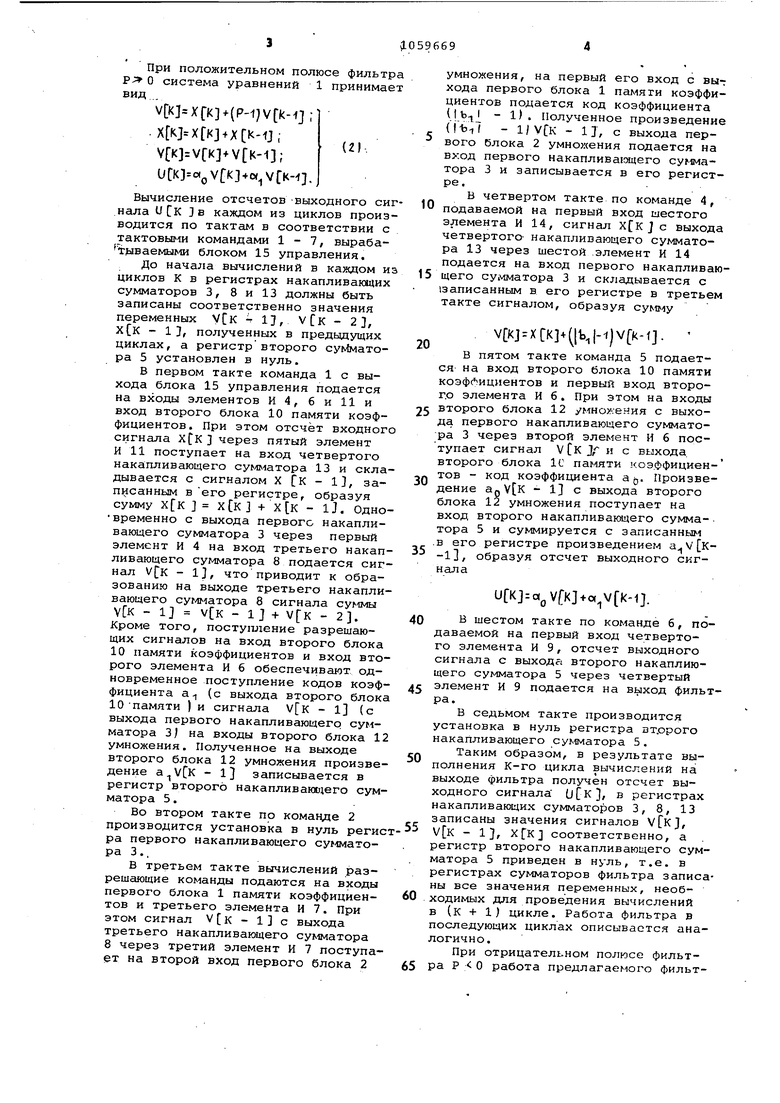

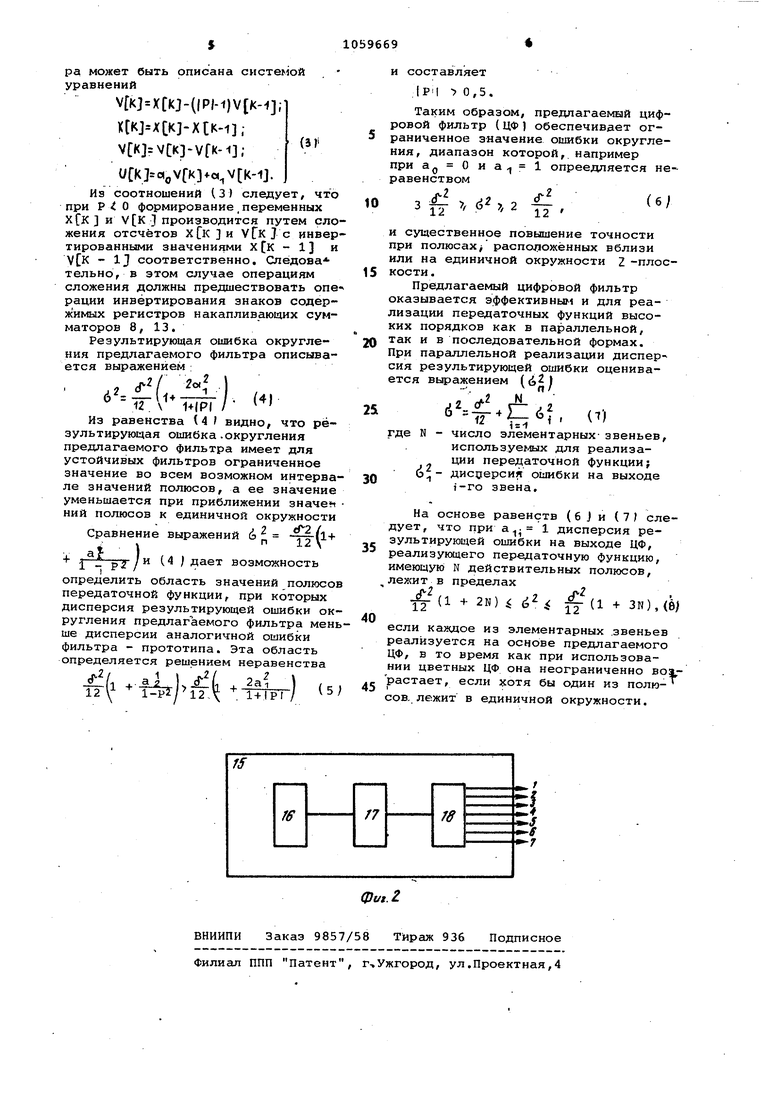

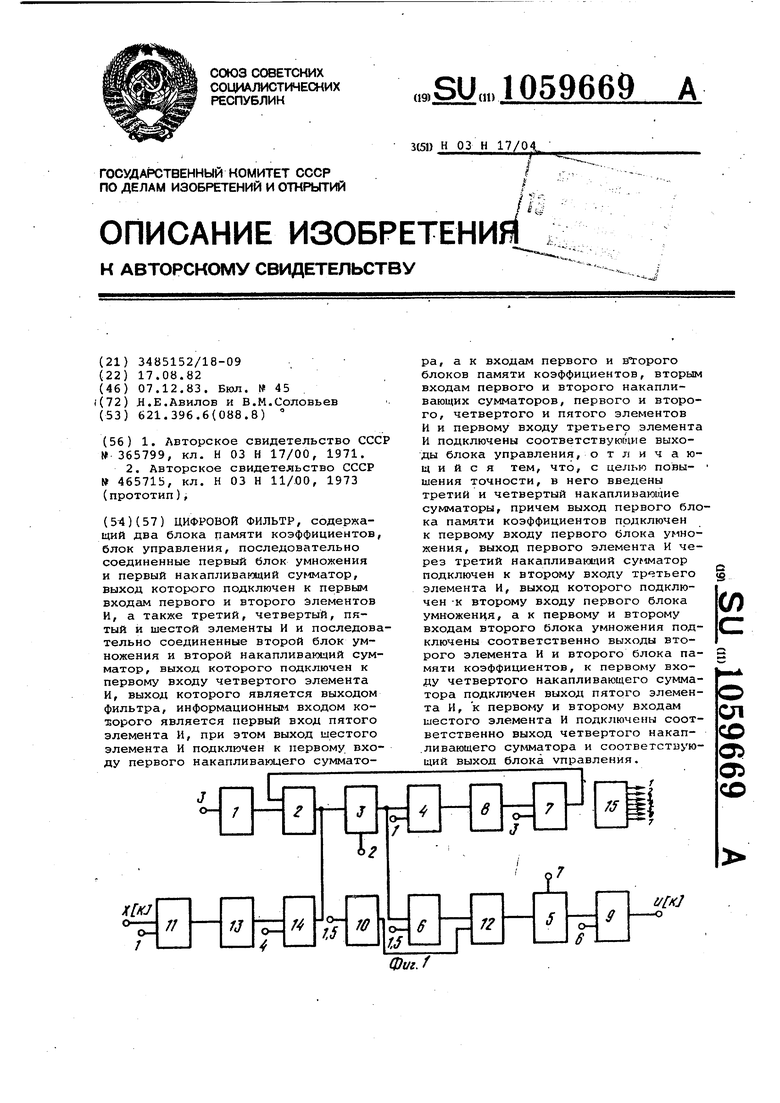

На фиг. 1 представлена структурная электрическая схема цифрового фильтра; на фиг. 2 - структурная электрическая схема блока управления .

Цифровой фильтр- содержит первый блок 1 памяти коэффициентов, первый блок 2 умножения, первый накапливающий cyr-iMaTop 3, первый элемент И 4, .второй накапливанвдий сумматор 5, второй элемент И б, третий элемент И 7, третий накапливающий сумматор 8, четвертый элемент И9, второй блок 10 памяти коэффициентов, пятый элемент И 11, второй блок 12 умножения, четвертый накапливающий сумматор 13, шестой элемент И 14, блок 15 управления, содержащий задаю1дий генератор 16, счетчик 17 и шyльcoв, 1дешифратор 18.

Работа цифрового фильтра описывается системой уравнений

vCKj yfKj+( (iPf-JjvfK-f}; хГк()Х(;к-1};

(Я

.(si jnp|v(;K-ij,), реализующих передаточную функцию

положительном полюсе фильтра Р- О система уравнений 1 принимает

(P-i;V k-fJ; + XCk-1J;

(21 ( ,(J.

Вычисление отсчетов выходного сигнала иСк 3 в каждом из циклов производится по тактам в соответствии с тактовыми командами 1 - 7, выраба туваемыл-ш блоком 15 управления.

До начала вычислений в каждом из циклов К в регистрах накапливакадих сумматоров 3, 8 и 13 должны быть записаны соответственно значения переменных -т 13, - 2, xfK - 1 }, полученных в предыдущих циклах, а регистр второго суМматора 5 установлен в нуль.

В первом такте команда 1 с выхода блока 15 управления подается на входы элементов И 4, б и 11 и вход второго блока 10 памяти коэффициентов. При этом отсчёт входного сигнала XfK через пятый элемент И 11 поступает на вход четвертого накапливающего сумматора 13 и складывается с сигналом X CK - 1, записанным вего регистре, образуя сумму - iJ. Одно временно с выхода первого накапливающего сумматора 3 через первый элемент И 4 на вход третьего накапливающего сумматора 8 подается сигнал - 1, что приводит к образованию на выходе третьего накапливающего cyr iaTopa 8 сигнала - 1J - 1 + - 2. Кроме того, поступление разрешающих сигналов на вход второго блока 10 памяти коэффициентов и вход второго элемента И 6 обеспечивают одновременное поступление кодов коэффициента а-, (с выхода второго блока 10-памяти ) и сигнала - 1 (с выхода первого накапливающего сумматора 3 на входы второго блока 12 умножения. Полученное на выходе второго блока 12 умножения произведение - 1} записывается в регистр второго накапливающего сумматора 5.

Во втором такте по команде 2 производится установка в нуль регисра первого накапливающего сумматора 3.,

В третьем такте вычислений разрешающие команды подаются на входы первого блока 1 памяти коэффициентов и третьего элемента И 7. При этом сигнал - 1 с выхода третьего накапливающего сумматора 8 через третий элемент И 7 поступает на второй вход первого блока 2

умножения, на первый его вход с вы-: хода первого блока 1 памяти коэффициентов подается код коэффициента (I Ь; j - 1) . Полученное произведение (Iti-if - - 1J, с выхода первого блока 2 умножения подается на вход первого накапливающего сумматора 3 и записывается в его регистре. . В четвертом такте по команде 4,

подаваемой на первый вход шестого

элемента И 14, сигнал с выхода четвертого- накапливающего сумматора 13 через шестой .элемент И 14 подается на вход первого накапливающего cyiviMaTopa 3 и складывается с 1записанным в его регистре в третьем такте сигналом, образуя сумму

V KJ-XCKh(|m-()

в пятом такте команда 5 подается на вход второго блока 10 памяти коэфс ициентов и первый вход второг.о элемента И 6. При этом на входы

второго блока 12 умножения с выхода первого накапливающего сумматора 3 через второй элемент И 6 поступает сигнал V Ск J, и с выхода, второго блока 1C памяти коэ.ффициентов - код коэффициента а. Произведение - 1 с выхода второго блока 12 умножения поступает на вход второго накапливающего сумма- тора 5 и суммируется с записанным .в его регистре произведением , образуя отсчет выходного сигнала

UCKJra VfKj o,.

шестом такте по команде 6, подаваемой на первый вход четвертого элемента И 9, отсчет выходного сигнала с выхода второго накаплиющего сумматора 5 через четвертый

элемент И 9 подается на выход фильтра.

В седьмом такте производится установка в нуль регистра вт.орого накапливающего сумматора 5.

Таким образом, в результате выполнения К-го цикла вычислений на выходе фильтра получен отсчет выходного сигнала в регистрах накапливающих сумматоров 3, 8, 13 записаны значения сигналов VfKj,

- 1, XtKJ соответственно, а . регистр второго накапливающего сумматора 5 приведен в нуль, т.е. в регистрах сумматоров фильтра записаны все значения переменных, необходимых для проведения вычислений в (к + 1) цикле. Работа фильтра в последующих циклах описывается аналогично.

При отрицательном полюсе фильтра Р О работа пpeдлaгae 1oгo фильтpa может быть описана системой уравнений

Vj:Kj XCKJ-(|PM)

К К хСК -Х1:к-1 ;

(3)

V K} VCK -VfK-i ;

.Ск-1.

Из соотношений (3) следует, что при PiO формирование , переменных ХСК и производится путем сложения отсчётов VCKjc инвертированными значениями - 1 и - 1J соответственно. Следова тельно, в этом случае операциям сложения должны предшествовать one рации инвертирования знаков содержимых регистров накапливающих сумматоров 8, 13.

Результирующая ошибка округления предлагаемого фильтра описывается выражением :

).

,v2/

2oi

-wVi

(4)

Из равенства (4 видно, что результирующая ошибка .округления предлагаемого фильтра имеет для устойчивых фильтров ограниченное значение во всем возможном интервале значений полюсов, а ее значение уменьшается при приближении значе НИИ полюсов к единичной окружности

Сравнение выражений (i (l+ % п 1 V

+ а I

(4 J дает возможность + 1 р2 /и

определить область значений полюсов передаточной функции, при которых дисперсия результирующей ошибки округления предлагаемого фильтра меньше дисперсии аналогичной ошибки фильтра - прототипа. Эта область определяется решением неравенства

/1 ..all . 2ai ) /..,

- .1 .ттгрт-/ 5;

12

и составляет

;|Р| 0,5.

Таким образом, предлагаемый цифровой фильтр {ЦФ1 обеспечивает ограниченное значение ошибки округления, диапазон которой, например при а ()иа,, 1 опреедляется неравенством

(6/

3 / db, 2 f ,

и существенное повышение точности при полюсг1Х расположённых вблизи или на единичной окружности Z-плоскости ,

Предлагаемый цифровой фильтр оказывается эффективным и для реализации пе редаточных функций высоких порядков как в параллельной, так и в последовательной формах. При параллельной реализации дисперсия результирующей ошибки оценивается вьлражением (

, („

где N - число элементарных-звеньев, используемых для реализации передаточной функции; дисперсия ошибки на выходе )-го звена.

На основе равенств (6 J и (71 следует, что при а 1 дисперсия результирующей ошибки на выходе ЦФ, реализующего передаточную функцию, имеющую N действительных полюсов, ,лежит в пределах

- (1 + 2N) й

(1 + 3N),(

если каждое из элементарных .звеньев реализуется на основе предлагаемого ЦФ, в то время как при использовании цветных ЦФ она неограниченно ворастает, если хотя бы один из полюсов. лежит в единичной окружности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1985 |

|

SU1327280A1 |

| Рекурсивный цифровой фильтр | 1983 |

|

SU1171993A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| ЦИФРОВОЙ ФИЛЬТР | 1993 |

|

RU2096911C1 |

| Цифровой фильтр | 1983 |

|

SU1146798A1 |

| Цифровой фильтр | 1985 |

|

SU1280390A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ЦИФРОВОЙ РЕГУЛЯТОР | 1992 |

|

RU2036502C1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

ЦИФРОВОЙ ФИЛЬТР, содержащий два блока памяти коэффициентов, блок управления, последовательно соединенные первый блок умножения и первый накапливакядий сумматор, выход которого подключен к первым входам первого и второго элементов И, а также третий, четвертый, пятый и шестой элементы И и последовательно соединенные второй блок умножения и второй накапливанвдий сумматор, выход которого подключен к первому входу четвертого элемента И, выход которого является выходом фильтра, информационным входом ко:ЕОрого является первый вход пятого элемента И, при этом выход шестого элемента И подключен к первому входу первого накапливаюцего сумматора, а к входам первого и второго блоков памяти коэффициентов, вторым входам первого и второго накапливающих сумматоров, первого и второго, четвертого и пятого элементов И и первому входу третьего элемента И подключены соответствуюгпие выходы блока управления, о т л и ч а ющ и и с я тем, что, с целью повы- шения точности, в него введены третий и четвертый накапливающие сумматоры, причем выход первого блока памяти коэффициентов прддключен к первому входу первого блока умножения, выход первого элемента И через третий накапливающий cy Iмaтop i подключен к второму входу тргтьего элемента И, выход которого подклю(Л чен -к второму входу первого блока умножения, а к первому и второму входам второго блока умножения подключены соответственно выходы второго элемента И и второго блока памяти коэффициентов, к первому входу четвертого накапливающего сумматора подключен выход пятого элемента И, к первому и второму входам сл шестого элемента И подключены соотф а ветственно выход четвертого накап.ливающего сумматора и соответств ющий выход блока управления. о: со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЦИФРОВОЙ ФИЛЬТР | 0 |

|

SU365799A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аналого-цифровой фильтр | 1973 |

|

SU465715A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-12-07—Публикация

1982-08-17—Подача