Изобретение относится к радиотехнике, может использоваться в радиотехнических устройствах различного назначения и является усовершенствованием устройства по авт. св. № 1059662

Цель изобретения - повышение быстродействия за счет увеличения коэффициента передачи в переходном режиме.

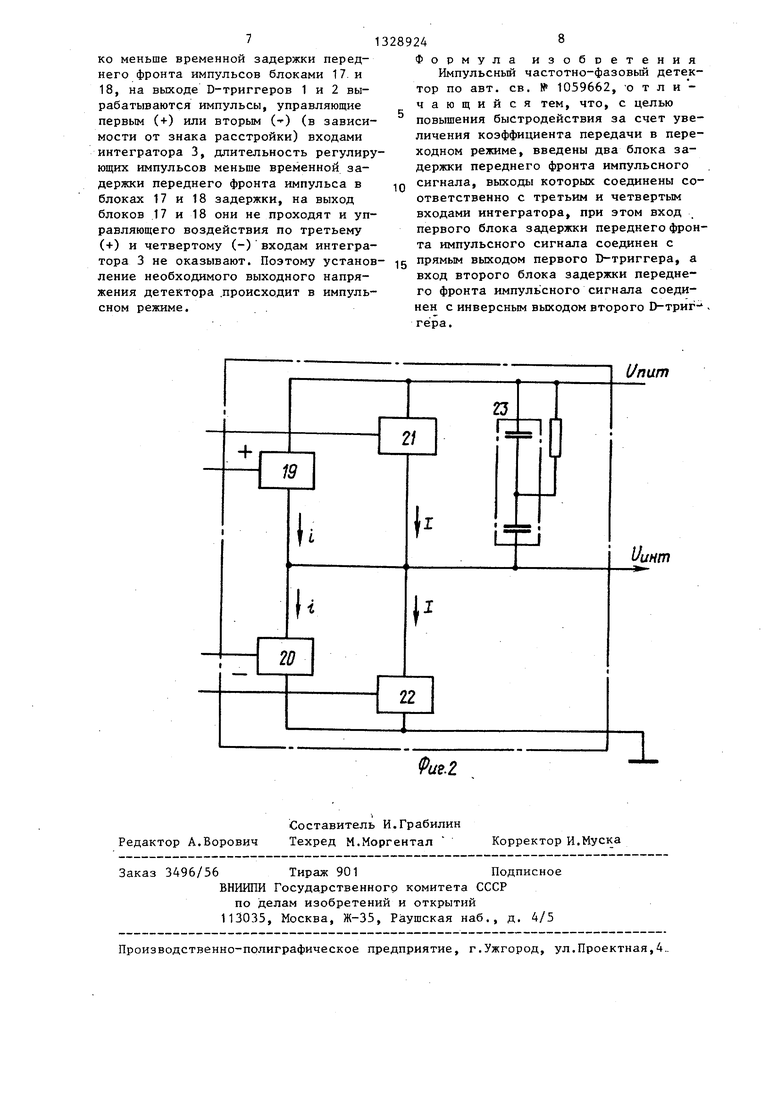

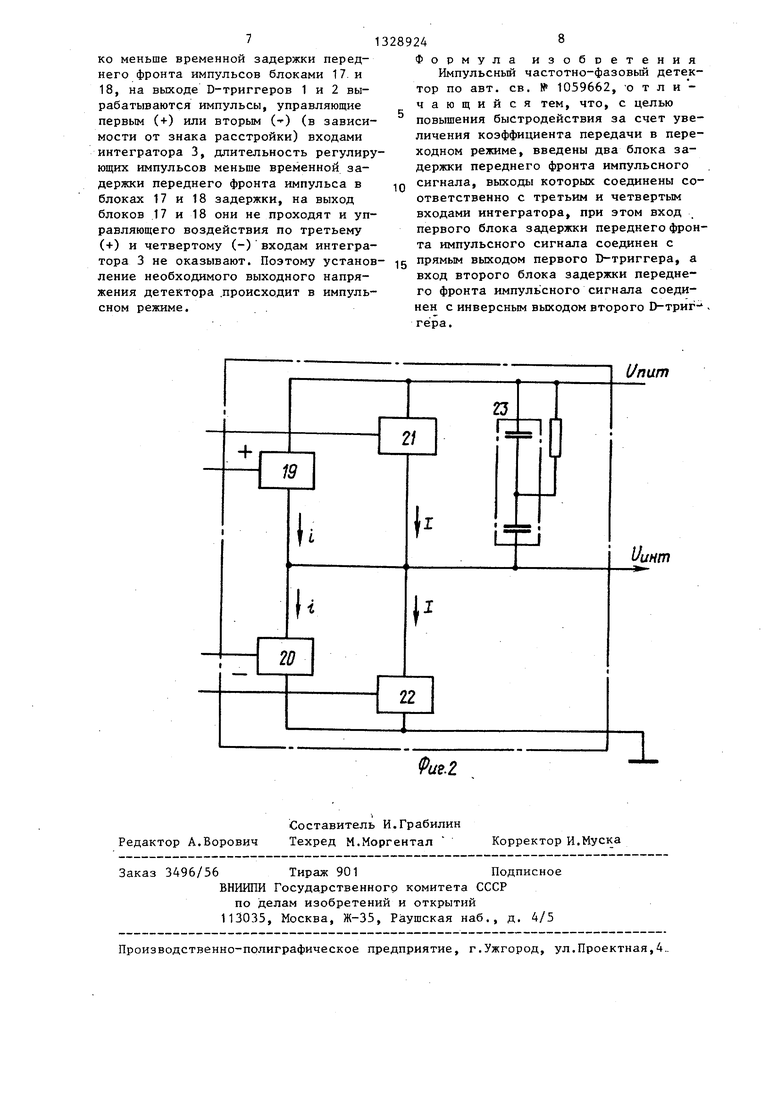

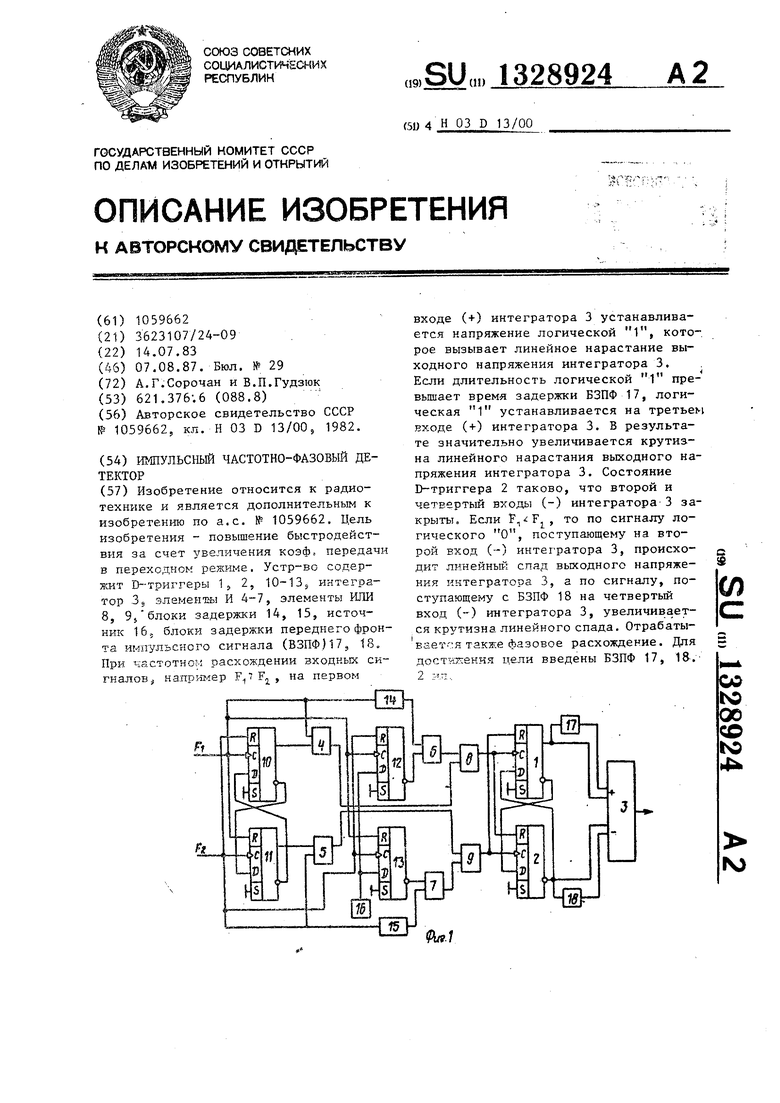

На фиг.1 приведена структурная электрическая схема предлагаемого импульсного частотно-фазового детектора; на фиг.2 - структурная электрическая схема интегратора.

Импульсный частотно-фазовый детектор содержит первый 1 и второй 2 D-трйггеры, интегратор 3, первые 4 (5) и вторые 6(7) элементы И, элементы ИЛИ 8 и 9, третий 10(11) и четвертый 12(13) D-триггеры, блоки 14 и 15 задержки, источник 16 логической 1, блоки 17 и 18 задержки переднего фронта импульсного сигнала.

Интегратор 3 содержит первьш 19, второй 20, третий 21 и четвертый 22 генераторы стабильного тока (ГСТ) и конденсатор 23.

Импульсньй частотно-фазовьш детектор работает следующим образом.

Б D-триггерах 1,2,10,11,12 и 13 входы синхронизации и сброса срабаЛ

тывают по переднему фронту j импульса. Будем считать исходным состояние D-триггеров, когда напряжение на прямых выхода соответствует логическому О, соответственно на инверсных- логической

FI - Fj.

где F.J - частота входных импульсов, поступаюш;их на вход синхронизации D-триггера 10; F - частота входных импульсов, поступающих на вход синхро низации Б-триггера 11. Первьм импульс Up , поступающий на входы синхронизации D-триггеров 10 и 12 и входы установки О D-тpиr геров 11 и 13, устанавливает на ;прямом выходе D-триггеров 10 и 12 напряжение логической 1, а на инверсных - логического О, так как в момент прихода импульса на информационном входе (D-входе) D-триггеров 10 и 12 было напряжение логической 1 (D- вход D-триггера 10 соединен с инверсным выходом -триггера 11, на кото

ром в исходном состоянии логическая I, D-вход D-триггера 12 соединен с источником 16), D-триггеры t1 и 13 остаются в исходном состоянии.

8 Одновременно с этим первый импульс поступает на входы элементов И 4 и 6. Установившееся состояние D-триггера 10 разрешает прохождение первого импульса на выход элемента И 4, далее через элемент ИЛИ 8 поступает на вход синхронизации D-триггера 1 и вход установки О D-триггера 2 и устанавливает на прямом выходе D-триггера 1

напряжение логической 1, так как в момент прихода импульса на информационном входе (D-входе) D-триггера . 1, соединенном с инверсным выходом D-триггера 2, было напряжение логической 1, D-триггер 2 остается в исходном состоянии.

Установившийся логический О на инверсном выходе D-триггера , 1 2 за- прещает прохождение входного импульса через элемент И 6.

В таком состоянии все D-триггеры остаются и при дальнейшем поступлении импульсов UF на вход синхронизации D-триггера.10, которые через элементы И 4 и ИЛИ 8 поступают на вход синхронизации D-триггера 1 и вход установки в О D-триггера 2.

Напряжение логической 1 с прямого выхода D-триггера 1 поступае.т на первый вход (+) интегратора 3 и вход

блока 17 задержки переднего фронта импульса. Под действием напряжения ло1 ической 1 в интеграторе 3 происходит заряд конденсатор а 23 интегратора от первого (ГСТ 19) с током заряда i. Через время, равное задержке блока 17, напряжение логической 1 поступает на третий вход (+) интегратора 3, под действием которого происходит заряд емкости интегратора по ГСТ 21 током заряда I, причем I 7 i. Импульс Up , поступаюш.йй на вход синхронизации В триггеров 11 и 13 и входы установки в О D-триггеров 10 и 12, не изменяет исходного состояния D-триггеров 11, так как в момент прихода импульса на его информационном входа (D-входе), соединенном с инверсным выходом D-триггера 10, было напряжение логического О,

на прямом выходе D-триггера 13 уста

навливается логическая

1

так как

на его D-входе напряжение логической 1, D-триггеры 10 и 12 по приходу

3

импульса UF на их входы установки О переходят в исходное состояние.

Установившееся состояние D-триг- геров 11 и 13 запрещает прохождение импульса Up через элементы И 5 и 7 тем самым D-триггеры 1 и 2 остаются в прежнем состоянии, которое обеспе .чивает дальнейший заряд конденсато- ра 23 интегратора 3 по ГСТ 19 и 21. С инверсного выхода D-триггера 2 и с выхода второго блока 18 задержки переднего фронта импульсного сигнал поступает напряжение логической 1 на второй и четвертый входы (-) интегратора 3, которое обеспечивает выключенное состояние ГСТ 20 и 22 итегратора 3.

Таким образом, при наличии частоного расхождения входных сигналов

Up , и F, на первом входе (+) интегратора 3 устанавливается напряжение логической 1, которое вызывает линейное нарастание выходного напряжения интегратора 3, При действии логической 1, превьшающем время задержки блока 17 задержки, логическая 1 устанавливается на третьем входе (+) интегратора 3, что значительно увеличивает крутизну линейного нарастания выходного напряжения интеграто- ра 3. D-триггер 2 находится в исходном состоянии, при котором второй и четвертый входы.(-) интегратора 3 закрыты .

В случае F с Fj и ввиду полной симметрии схемы по отношению к входным сигналам Up и Up , на инверсном выходе D-триггера 2 по приходу первого импульса UF, устанавливается напряжение логического О, поступающее на второй вход (-) интегратора 3, что вызывает линейный спад выходного напряжения интегратора 3 через ГСТ 20 током разряда i. При де йствии логического О, превышающем время задержки блока 18, логический О устанавливается на четвертом входе (-) интегратора 3, что увеличивает крутизну линейного спада выходного напряжения интегратора 3 через ГСТ 22 током разряда I. D-триггер 1 находится в исходном состоянии, при котором первьй и третий входы () интегратора 3 закрыты.

Чр 7 ч.. г-( Р

где - фаза, характеризующая последовательность импульсов.

5

0

5

0

5

0

поступающих на вход синхронизации D-триггера 10, uf - фаза, характеризующая по- следовательность импульсов, поступающих на вход синхронизации D- триггера 11. Первый импульс Up , поступающий

на входы синхронизации D-триггеров 11 и 13 и входы установки в О D- триггеров 10 и 12, устанавливает на прямом выходе D-триггеров 11 и 13 напряжение логической 1, на инверсных - соответственно логического О, так как в момент прихода импульса на D-входах D-триггеров 11 и 13 было напряжение логической 1 (D-вход D- триггера 11 соединен с инверсным выходом D-триггера 10, на котором в исходном состоянии логическая 1, D-вход D-триггера 13 подключен к источнику логической 1), D-триггеры 11 и 12 остаются в исходном состоянии.

Одновременно с этим первый импульс поступает на входы элементов И 5 и 7. Установившееся состояние D-триггера 11 разрешает прохождение первого импульса на вход элемента И 5, далее через элемент ИЛИ 9 поступает на выход синхронизации D-триггера 2 и вход установки в О D-триггера 1 и устанавливает на прямом выходе D-триггера 2 напряжение логической 1, так как в момент прихода импульса на D-входе D-триггера 2, соединенном с инверсным выходом D-триггера 1 было напряжение логической 1, D-триггер 1 остается в исходном состоянии.

Установившийся логический О на инверсном выходе D-триггера 13 запрещает прохождение входного импульса через элемент И 7.

Напряжение логического О с инерсного выхода D-триггера 2 поступает на второй вход (-) интегратора 3 и вход блока 18 задержки переднего фронта импульсного сигнала. Под действием напряжения логического О в интеграторе 3 происходит разряд конденсатора 23 интегратора 3 через ГСТ 20 током разряда i. Через время, равное задержке блока 18 задержки, напряжение логического О поступает на четвертый вход (-) интегратора 3, под действием которого происходит разряд конденсатора 23 интегратора 3 через ГСТ 22 током разряда I.

513

X Следующим приходит импульс Up на входы синхронизации D-триггеров 10 и 12 и входы установки в О D-триггеров 11 и 13. D-триггер 10 не изменяет своего исходного состояния, так как в момент прихода импульса на D-входе D-триггера 10, соединенном с инверсным выходом D-триггера 11,, было напряжение логического О.-На прямом выходе- D-триггера 12 с прихо

дом импульса Up устанавливается логическая 1, так как на его D-вход подан потенциал логической 1.

D-триггеры 11 и 13 переходят в исходное состояние. Установившееся состояние D-триггеров 10 и 12 запрещает прохождение импульсов Up через элементы И 4 и 6. Тем самым D-триггеры 1 и 2 остаются в прежнем состоянии, которое обеспечивает дальнейший разряд интегратора 3 через ГСТ 20 и 22. С прямого выхода D тpиггepa 1 и с выхода первого блока 17 задержки переднего фронта импульсного сигнала поступает напряжение логического О на первый и третий входы () интегратора 3, которое обеспечивает выключенное состояние ГСТ 19 и 21 интегратора 3.

Таким образом, при наличии фазового расхождения с, 7 ц-р входных сигналов Up , UF, на втором входе {-) интегратора 3 устанавливается напряжение логического О, которое вызывает линейный спад выходного напряжения интегратора 3, При действии напря жения логического О, поеныша- ющего время задержки блока 18, логический О устанавливается на четвертом входе (-) интегратора 3, что значительно увеличивает крутизну спада

выходного напряжения интегратора 3. D-триггер 1 находится в исходном состоянии, при котором первый и третий входы (+) интегратора 3 закрыты.

В случае 4V ив виду полной симметрии схемы по отношению к входным сигналам Up , U f, на вы- ходе D-триггера 1 по приходу первого им- пульса и f устанавливается напряжение ;логической 1, поступающее на первый вход (+) интегратора 3, что вызывает линейное нарастание напряжения на конденсаторе 23 интегратора 3 от ГСТ 19

Временному совпадению лередних фронтов входных импульсов Up , Up , которые поступают на входы синхронизации и установки О D-триггеров 10, 12, 11 и 13, соответствует случай .

При этом D-триггеры 10, 12, 11 и 13 остаются в исходном состоянии (на 5 прямых выходах - логической О, на инверсных - логическая 1), так как входы установки О являются независимыми от информационных входов (D- входов).

Установившиеся логические О на прямых выходах D тpиггepoв 10 и 11 запрещают прохождение входных импульсов UF , f через элементы И 4 и 5.

Установившиеся логические 1 на инверсных выходах D-триггеров 12 и 13 разрешают прохождение импульсов Up , Up через элементы И 6 и 7 и далее через ШТИ 8 и 9 поступают на входы синхронизации и установки О 30 D-триггеров 1 и 2 одновременно, и устанавливают D-триггеры 1 и 2 в ис20

25

.Л

вьш и через блок 17 задержки переднего фронта импульсного сигнала на

35 третий ВХОДЫ1 (+) интегратора 3 одновременно поступает логический О, на второй и через блок 18 задержки переднего фронта импульса на четвертый входы (-) интеграторов 3 - логи40 ческая 1, чем обеспечивается закрытое состояние интегратора 3. Интегратор 3 запоминает напряжение, накопленное на конденсаторе 23. Такой режим работы импульсного частотно-фазо45 вого детектора в цифровом синтезаторе частот соответствует реж1-1му синхронизма.

Блоки 14 и 15 задержки выполнены 50 на логических элементах И и обеспечивают задержку входных импульсов Up , Ur на величину времени задержTI гл

ки D-триггеров 12 и 13 для обеспечения одновременного прихода передних

д..

При действии логичес- 55 фронтов входных импульсов Up ,

и

и

FI

с интоком заряда

кой 1, превышающем время задержкипереднего фронта логической 1

блока 17, логическая 1 устанавлива-.версных выходов D-триггеров 12 и 13. ется на третьем входе (+) интеграто- В случае расхождения входных имра 3, что увеличивает крутизну линей-пульсов,-длительность которых несколь

ного нарастания напряжения на конденсаторе 23 интегратора 3 под действием ГСТ 21 током заряда I. D-триггер 2 находится в исходном состоянии, при котором второй и четвертый входы (-) интегратора 3 закрыты.

Временному совпадению лередних фронтов входных импульсов Up , Up , которые поступают на входы синхронизации и установки О D-триггеров 10, 12, 11 и 13, соответствует случай .

При этом D-триггеры 10, 12, 11 и 13 остаются в исходном состоянии (на прямых выходах - логической О, на инверсных - логическая 1), так как входы установки О являются независимыми от информационных входов (D- входов).

Установившиеся логические О на прямых выходах D тpиггepoв 10 и 11 запрещают прохождение входных импульсов UF , f через элементы И 4 и 5.

Установившиеся логические 1 на инверсных выходах D-триггеров 12 и 13 разрешают прохождение импульсов Up , Up через элементы И 6 и 7 и далее через ШТИ 8 и 9 поступают на входы синхронизации и установки О D-триггеров 1 и 2 одновременно, и устанавливают D-триггеры 1 и 2 в ис

-

вьш и через блок 17 задержки переднего фронта импульсного сигнала на

35 третий ВХОДЫ1 (+) интегратора 3 одновременно поступает логический О, на второй и через блок 18 задержки переднего фронта импульса на четвертый входы (-) интеграторов 3 - логи40 ческая 1, чем обеспечивается закрытое состояние интегратора 3. Интегратор 3 запоминает напряжение, накопленное на конденсаторе 23. Такой режим работы импульсного частотно-фазо45 вого детектора в цифровом синтезаторе частот соответствует реж1-1му синхронизма.

Блоки 14 и 15 задержки выполнены 50 на логических элементах И и обеспечивают задержку входных импульсов Up , Ur на величину времени задержTI гл

ки D-триггеров 12 и 13 для обеспечения одновременного прихода передних

и

и

FI

с инко меньше временной задержки переднего фронта импульсов блоками 17. и 18, на выходе D-триггеров 1 и 2 вырабатываются импульсы, управляющие первьм () или вторым () (в зависимости от знака расстройки) входами интегратора 3, длительность регулирующих импульсов меньше временной задержки переднего фронта импульса в блоках 17 и 18 задержки, на выход блоков 17 и 18 они не проходят и управляющего воздействия по третьему (+) и четвертому (-) входам интегратора 3 не оказывают. Поэтому установление необходимого выходного напряжения детектора .происходит в импульсном режиме.

Формула изобретения

Импульсный частотно-фазовый детектор по авт. св. № 1059662, -отличающийся тем, что, с целью повышения быстродействия за счет увеличения коэффициента передачи в переходном режиме, введены два блока задержки переднего фронта импульсного

сигнала, выходы которых соединены соответственно с третьим и четвертым входами интегратора, при этом вход . первого блока задержки переднего фронта импульсного сигнала соединен с прямым выходом первого D-триггера, а вход второго блока задержки переднего фронта импульсного сигнала соединен с инверсным выходом второго В-триг- гёра.

Unam

V 4

Уинт

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1982 |

|

SU1059662A1 |

| Импульсный частотно-фазовый детектор | 1980 |

|

SU985929A1 |

| Устройство для измерения произведения двух напряжений | 1983 |

|

SU1195265A1 |

| Устройство тактовой синхронизации сигналов с расщепленной фазой | 1985 |

|

SU1297243A1 |

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Корреляционный измеритель скорости | 1985 |

|

SU1327009A1 |

| Устройство для подгонки частоты одного источника напряжения к частоте другого источника напряжения | 1983 |

|

SU1141509A2 |

| Широтно-импульсный преобразователь | 1986 |

|

SU1413715A1 |

| Устройство для управления трехфазным тиристорным преобразователем частоты с широтноимпульсным регулированием | 1986 |

|

SU1411901A1 |

Изобретение относится к радиотехнике и является дополнительным к изобретению по а.с. № 1059662. Цель изобретения - повышение быстродействия за счет увеличения коэф. передачи в переходном реташ-ле, Устр-во содержит -триггеры 1, 2, 10-135 интегратор 3,, злементй И 4-7, элементы ИЛИ 8, 9, блоки задержки 14, 15, источник 16, блоки задержки переднего фронта импульсного сигнала (ВЗПФ)175 18, При частотном расхождении входных сигналов напрж ер , на первом входе (+) интегратора 3 устанавливается напряжение логической 1, которое вызывает линейное нарастание выходного напряжения интегратора 3. Если длительность логической 1 превышает время задержки БЗПФ 17, логическая 1 устанавливается на третьем входе (+) интегратора 3. В результате значительно увеличивается крутизна линейного нарастания выходного напряжения интегратора 3. Состояние D-триггера 2 таково, что второй и четвертый входы (-) интегратора 3 за- крытьт. Если F , то по сигналу логического О, поступающему на второй вход (-) интегратора 3, происходи линейный спад выходного напряжения интегратора 3, а по сигналу, поступающему с БЗПФ 18 на четвертый вход () интегратора 3, увеличивается крутизна, линейного спада. Отрабаты- вается также фазовое расхождение. Для достикення цели введены БЗПФ 17, Ш.- 2 у-.. (Л N

fe.2

J.

Составитель И.Грабилин Редактор А.Ворович Техред М.Моргентал l.:...

Заказ 3496/56 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4.

| Импульсный частотно-фазовый детектор | 1982 |

|

SU1059662A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-08-07—Публикация

1983-07-14—Подача