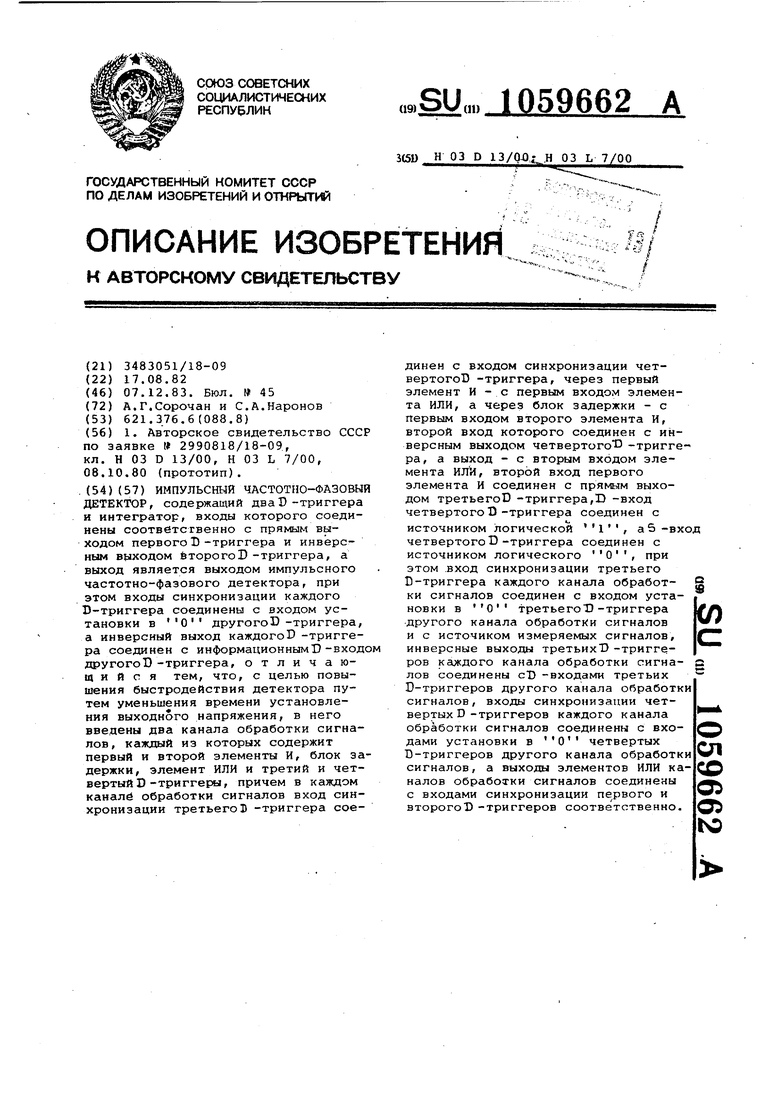

Изобретение относится к радиотехнике и может использоваться в радиотехнических устройствах различного назначения, в частности в синтезаторах частот. Наиболее близким к предлагаемому по технической сущности является импульсный час.тотно-фазовый детектор, содержащий дваD -триггера и ин тегратор, входы которого соединены соответственно с прямым выходом первого Б -триггера и инверсным выходом второгоD-триггера, а выход является выходом импульсного частотно-фазового детектора, при этом входы синхронизации каждого)-триггера соединены с входом установки в О другогоD -триггера, а инверсный выход каждогоD-триггера соединен с информационным)-входом друго оВ -триггера Щ ., Однако известными импульсный частотно-фазовый детектор из-за длител ного времени установления выходного напряжения имеет недостаточное быстродействие. Цель изобретения - повышение .быстродействия путем уменьшения времени установления выходного напряжения. Для достижения цели в импульсный частотно-фазовый детектор, содержащий два D -триггера и интегратор, входы которого соединены соответственно с прямым выходом первого D-триггера и инверсным выходом второго) -триггера, а выход является выходом импyльcнoJo частотно-фазового детектора, при этом входы синхронизации каждого) -триггера соеди нены с входом установки в О дру гого) -триггера, а инверсный выход каждого) -триггера соединен с информационным D -входом другого -три .гера, введены два канала обработки сигналов, каждый из которых содержит первый и второй элементы И, блок задержки, элемент ИЛИ и третий и четвертыйD -триггеры, причем в каждом канале обработки сигналов вход синхронизации«третьего) -триггера соединен с входом синхронизации четвертого) -триггера, через первый элемент И - с первым входом элемента ИЛИ, а через блок задержки - с первым входом второго элемента И, второй вход которого соединен с инверсным выходом четвертоroD -триггера, а выход - с вторым входом элемента ИЛИ, второй вход . первого элемента И соединен с прямы вьрсодом третьего)-триггера, 1 -вход четвертого}) -триггера соединен с источником логической , а 5-вход четвертого) -триггера соеди: нен с источником логического О при этом вход синхронизации третьего D -триггера каждого канала обрабо ки сигналов соединен с входом установки в о третьегоТ)-триггера другого канала обработки сигналов и с источником измеряемых сигналов , инверсные выходы третьих D-триггеров каждого каналаобработки сигналов соединены cD -входами третьих л) -триггеров другого канала обработки сигналов, входы синхронизации четвертых) -триггеров каждого канала обработки сигналов соединены с входами установки в вертых)-триггеров другого канала обработки сигналов, а выходы элементов ИЛИ каналов обработки сигналов соединены с входами синхронизации- первого и второго) -триггеров соответственно. На чертеже приведена электрическая структурная схема.импульсного частотно-фазового детектора (ИЧФД). Импульсный частотно-фа-зовый детектор содержит первый и второйD-триггеры 1 и 2, интегратор 3, содержащий два ключа на транзисторах, генераторы стабильного тока и конденсатор (не показаны), первые и вторые элементы И4, 5 и И6, 7, элементы ИЛИ 8 и 9, третьи и четвертые D-триггеры 10, 11 и 12, 13, блоки 14 и 15 задержки, источник 16 логической I 11 11 Импульсный частотно-фазовый детектор работает следующим образом. В D-триггерах входы синхронизасрабатываютции и установки по переднему фронту (-) импульса. Будем считать исходным состояние D-триггеров, когда напряжение на прямых выходах соответствует логическому , соответственно на инверсных - логической . В случае F , где Ff - частота входных импульсов, поступающих на вход синхронизации) -триггера 10; частота входных импульсов, поступающих на вход синхронизации) -триггера 11. Первый импульс иF поступающий на входы синхронизации О-триггеров10 и 12 и входы установки в Ц-триггеров 11 и 13, устанавливает на прямом выходе) -триггеров 10 и 12 напряжение логической , на инверсных - логического О, так как в момент прихода импульса на информационном входе (0-входе)1Э триггеров 10 и 12 было напряжение логической 1.D-входТЭ -триггера 10 соединен с инверсным выходом D-триггера 11, на котором в исходнок состоянии логическая , Ф-вход В-триггера 12 соединен с источником 16,13 -триггеры 11 и 13 остаются в исходном состоянии. Одновременно первый импульс поступает на входы элементов И 4 и 6.

Установившееся состояние)-триггера 10 разрешает прохоисдение первого импульса на выход элемента И 4, далее через элемент ИЛИ 8 поступает ,на вход синхронизацииD -триггера 1 и вход установки -триггера 12 и устанавливает на прямом выходеВ -триггера 11 напряжение логической поскольку в момент прихода импульса на информационном входе (О-входё)Р -триггера 1, соеда ненном с инверсным выходом Б-триггера 2, было напряжение логической 1,D -триггер 2 остается, в исходном состоянии. :

Установившийся логический . на инверсном выходе 1}.-триггера 12 запрещает прохождение входного импульса через элемент И 6.

В таком состоянии всеВ -триггег ры остаются и при дальнейшем прступ Ленин импульсов (Up,) на вход синхронизации D -триггера 10 J. которое через элеме.нты И 4 и ИЛИ 8 поступает на вход синхронизации D-триггера 1 и вход установки в OD-триггера 2.

Напряжение логической Ч с прямого выходаD -триггера 1 поступает на вход (+) интегратора 3, что обеспечивает заряд емкости интеграторЭот генератора стабильного тока.. .

Импульс Up,, , поступающий на .вход синхронизации D-триггеров И и- 13 и входы установки в OD-триггеров 10 и 12, не изменяет исходг. ного состоянияD -триггеров 11, так как в момент прихода импульса на его информационном входе Ш-входе) соединенном с инверсным выходом 0-триггера 10, было напряжение логического О, на прямом выходе D -триггера 13 устанавливается ло, поскольку на его

гическая

О-вход подана логическая , D-триггеры 10 и 12 по приходу импул са Ор на Hjf вход установки в О переходят в исходное состояние.

Установившееся состояние)-триггеров 11 и 13 запрещает прохождевне импульса ЧР через элементы И 5 и 7. Тем самым В-триггеры 1 и 2 остаются в прежнем состоянии, которое обеспечивает дальнейший заряд емкости интегратора 3 от генератора стабильного тока. С инверсного выходаD-триггера 2 на вход {-) ин..тегратора 3 поступает напряжение логической , которое обеспечивает разомкнутое состояние ключа интегратора 3. .

Таким образом, при наличии частотного расхождения входных сигналов Up. Upj на прямом выходе 1)-триггера 1 устанавливается напряжение логической , которое вызывает

линейное нарастание выходного напряжения интегратора З.Б -триггер 2 находится в исходном состоянии.

В случае F,F2 и ввиду полной симметрии схемы по отн(Ж1ению к входным сигналам UF,, и Uf на инверсном выходе D-триггера 2 по приходу первого импульса Upj устанавливается напряжение логического О, которое закикает ключ интегратора 3 и вызывает линейный спад вькодного напряжения интегратора 3, при этом D-триггер 1 остается в исходном состоянии. Напряжение логического О с прямого выхода) -триггера 1 обеспечивает разомкнутое состояние ключа в интеграторе 3.

В случае l|f, Чр, г

где - фаза, характеризующая поV следовательность импульсов, поступающих на вход синхронизации) -триггера Cfp - фаза, характеризующая последовательность нмпульсов, поступающих на вход синхронизацииi-триггера 11.

Первый импуль/Ь ( Uf, ) поступающий на входы синхронизации)-триггеров 11 и 13 и входы установки в О.D-три г геров 10 и 12, устанавливает на прямом выходе) гтриггеррв 11 и 13 напряжение логической , на инверсных - .логического О, поскйльку в момент прихода импулЬ|Са наЗЗ-вхоЛахВ-триггеров 11 н 13 было напряжение логической . D -вход)-триггера 11. соединен с иНверсн«лм выходом)-триггера 10, на котором в исходном сос.тоянии логическая 1,)-ёход, В-триггера 13 подключен к источнику логической 1,D -триггеры 11 и 1 остаются в исходнч м состоянии.

одновременно с этим.первый импульс поступает на входа элементов И 5 и 7. Установившееся состояние D-триггера 11 разрешает прохождение первого импульса на вход элемента И S, дашее через элемент ИЛИ 9 поступает на вход синхронизации 1 -Триггера 2 и вход установки в -триггера 1 и устанавливает на прямом выходеБ -триггера 2 напряжение логической , так как в момент прихода импульса наD -входе D-триггера 2, соединенном с инверсным выходом D-триггера 1, было напряжение логической 1J D -триггер 1 остается в исходном состоянии..

Установившийся логический О ,на инверсном выходе)-триггера 13 запрещает прохождение входного импульса через элемент И 7.

Напряжение логического версного выхода D-триггера 2 поступает на вход (-) интегратора 3, эа 1Ча1кает его ключ, что обеспечивает разряд емкости интегратора 3 через генератор стабильного тока. Следующим приходит импульс { Up, на входы синхронизации D-триггеров 10 и 12 и входы установки в С-триггеров 11. и 13.D -триггер 10 не .изменяет своего исходного состояния, так как в момент прихода импульса наD-входе) -триггера 10, соединенном с инверсным выходом ,1)-триггера fl, было напряжение логического О . На прямом выходеD -триггера 12 с приходом импульса Uv, устанавливается логическая , поскольку на его I) -вход подан потенциал логической . I) -триггеры 11 и 13 переходят в исходЛ)е состояние. Установившееся состояние D -триггеров 10 и 12 запрещает прохождение импульсов ( Up ) через элементы g| 4 и 6. Тем самымБ -триггеры 1 и 2 остаются в прежнем состоянии, которое обеспечивает дальнейший разряд инте ратора 3 через генератор стабильно тока, так как с прямого выхода О-триггера 1 на вход (4-) интегратора 3 поступает напряжение логическо го О , которое обеспечивает разомкнутое состояние ключа интегратора 3, Таким образом, при наличии фазового расхождения входных сигналов Up, и Up D-триггер 1 находится в исходном состоянии, на инверсном выходе D-триггера 2 устанавливаетс напряжение логического , которое вызывает линейный спад выходного напряжения интегратора 3. В случае / Uip и ввиду полной симметрии схемы по отношению к вход ным сигналам Up и-F прямом выходе D-триггера 1 по приходу пер вого импульса Uf, устанавливается напряжение логической , которое замыкает ключ интегратора 3 и вызывает линейное нарастание выход ного напряжения интегратора 3, при этомD-триггер 2 остается в исходном состоянии. Напряжение логичесс инверсного выхода D-триггера 2 обеспечивает разомкнутое cbcit)HHHe ключа в интеграторе 3. Временному совпадению входных импульсов IJf: И Ир t которые поступают на входы синхронизации и установки в ОD-триггеров 10, 12, 11 и 13, одновременно соответствует случай cfp Чр2 Р этомБ-триггеры 10, 12, 11 и 13 остаются в исходном состоянии (на прямых выходах логический О, на инверсных логическая ), так как входы установки и О являются независимыми от информационных входов (D-входов). Установившиеся логические О на прямых выходах D-триггеров 10 и 11 запрещают прохождение входных импульсов (Up и Up ) через элементы И 4 и 5. Установившиеся логические , на инверсных выходах D-триггеров 12 и 13 разрешают прохождение входных импульсов ((lf иО ) через элементы И 6 и 7, которые далее через элементы ИЛИ 8 и 9 поступают на входы синхронизации и установки в D-триггеров 1 и 2, одновременно)-триггеры 1 и 2 устанавливаются в исходное состояние, при котором на вход(-) интегратора 3 поступает логический О, на вход (-) логическая Ч , что обеспечивает разомкнутое состояние ключей интегратора 3. Интегратор 3 запоминает напряжение, накопленное на конденсаторе. Такой режим работы ИЧФД в кольце автоподстройки частоты соответствует синхронизму. Элементы 17-20 образуют блоки 14 И 15 задержки и обеспечивают задержку входных нмпульсов Up иУр на величину времени задержки D-триггеров 12 и 13 для обеспечения одновременного прихода передних фронтов входных импульсов UF, и Up и переднего фронта сформирован ных логических 1 на инверсных выходах D-триггеров 12 и 13. Применение предлагаемого ИЧФД позволит значительно сократить количество комплектующих изделий, тем самым подавление частоты сравнейия в выходном напряжении составит более 100 дБ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1328924A2 |

| Импульсный частотно-фазовый детектор | 1980 |

|

SU985929A1 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Импульсный частотно-фазовый детектор | 1985 |

|

SU1312718A1 |

| Импульсный частотно-фазовый детектор | 1987 |

|

SU1483594A1 |

| Импульсный частотно-фазовый детектор | 1986 |

|

SU1424114A2 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1702539A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1285558A1 |

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР, содержащий дваD -триггера и интегратор, входы которого соединены соответственно с прямым выходом первого)-триггера и инверсным выходом бторого) -триггера, а выход является выходом импульсного частотно-фазового детектора, при этом входы синхронизации каждого D-триггера соединены с входом установки в О другого) -триггера, а инверсный выход каждогоD -триггера соединен с информационным)-входом другогоВ -триггера, о т л и ч а ющ и и с я тем, что, с целью повышения быстродействия детектора путем уменьшения времени установления выходного напряжения, в него введены два канала обработки сигналов, каждый из которых содержит первый и второй элементы И, блок задержки, элемент ИЛИ и третий и четвертый D -триггеры, причем в каждом канале обработки сигналов вход синхронизации третьего -триггера соединен с входом синхронизации четвертогоС -триггера, через первый элемент И - с первым входом элемента ИЛИ, а через блок задержки - с первым входом второго элемента И, второй вход которого соединен с инверсным выходом четвертого) -тригге ра, а выход - с вторым входом элемента ИЛИ, второй вход первого элемента И соединен с прямым выходом третьегоС -триггера,) -вход четвертогоD-триггера соединен с источником логической , а 5 -вход четвертого)-триггера соединен с О при источником логического этом .вход синхронизации третьего D-триггера каждого канала обработки сигналов соединен с входом уста(Л третьего) -триггера О новки в другого канала обработки сигналов и с источиком измеряемых сигналов, инверсные выходы третьих)-тригге ров каждого канала обработки сигналов соединены с) -входами третьих D-триггеров другого канала обработки сигналов, входы синхронизации четвертых D -триггеров каждого канала обработки сигналов соединены с входами установки в О четвертых ел D-триггеров другого канала обработки со сигналов, а выходы элементов ИЛИ каналов обработки сигналов соединены с входами синхронизации пе рвого и о: второгоБ -триггеров соответственно. ю

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свилетельство СССР по заявке 2990818/18-09, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| . | |||

Авторы

Даты

1983-12-07—Публикация

1982-08-17—Подача