единичное состояние инвертированным импульсом частоты F с БЗ 5, поступающим на его С-вход, и самоблокируется. С выхода ДТ I импульсы длительностью, пропорциональной разнос ти фаз импульсов частот „ к Tj , через элемент ИЛИ 7 поступают на ин- тегратор 9, на D-вход ДТ 3 и на R-вход ДТ 4. Выходное напряжение ин тегратора 9 нарастает со скоростью, определяемой его постоянной времени Когда ДТ 3 находится в единичном состоянии, напряжение с его инверсного выхода через элемент И-НЕ 10 поступает на управляющий вход интег ратора 9. В результате полоса пропускания интегратора 9 увеличивается и его выходное напряжение нарас1

Изобретение относится радиотехнике, может использоваться в быстродействующих схемах фазовой автоподстройки частоты с малым уровнем частот, кратных частоте сравнения в вы- ходнрм сигнале, и является усовершенствованием изобретения по авт. ев: СССР № 1124424.

Цель изобретения - увеличение быстродействия.

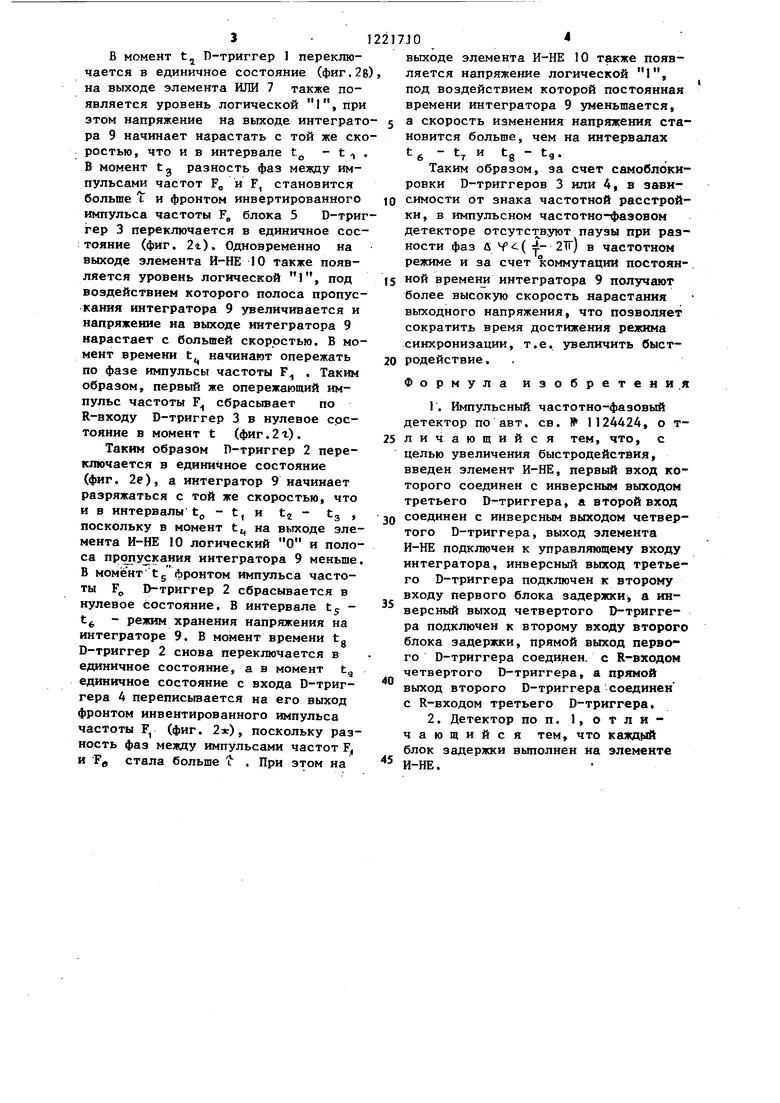

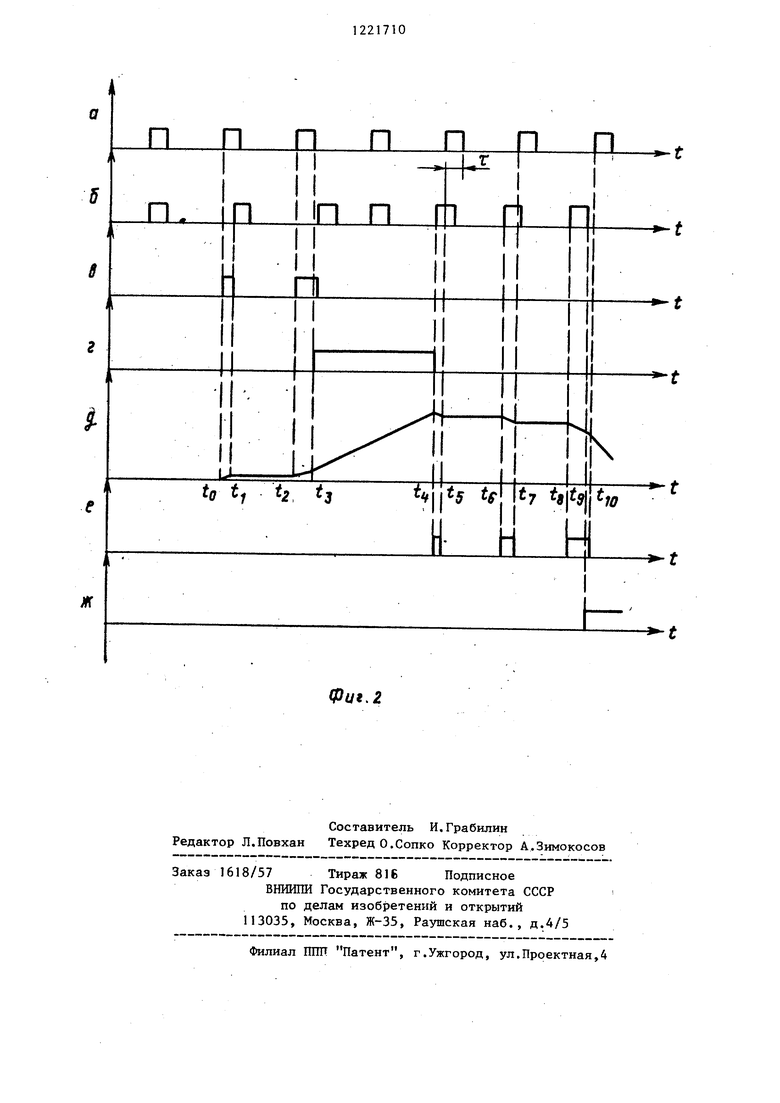

На фиг. 1 приведена структурная электрическая схема предложенного импульсного частотно-фазового детектора; на фиг. 2 - диаграммы, поясняющие его работу.

Импульсный частотно-фазовый детектор Содержит первый, второй, третий и четвертый D-триггеры 1-4, первый и второй блоки 5 и 6 задержки, первый и второй элементы ИЛИ 7 и 8, интегратор 9, элемент Й-НЕ 10.

Импульсный частотно-фазовый детектор работает слздуквдим образом.

С источника 11 входного сигнала поступает, например, частота F (фиг. 2а), а с источника 12 - частота F (фиг. 25).

В исходном состоянии на выходах D-триггеров 1 - 4 и выходах элементов ИЛИ 7 и 8 присутствует напряжение логического О. Пусть частота FO F , Когда разность фаз между FQ и FJ станет больше 1, Y

21710

тает с большей скоростью, В момент, когда опережают по фазе импульсы частоты FI , первый же импульс часто ты F, поступая с ДТ 2 на R-вход ДТ 3, устанавливает его в нулевое состояние. Импульсы, длительность которых определяется разностью фаз импульсов частот F и F,, , с ДТ 2 через злемент ИЖ 8 поступают на интегратор 9, разряжая его, и на В-вхоД| ДТ 4. При поступлении на С-вход ДТ импульса частоты F с БЗ 6, еди- ничный уровень с его выхода через злемент И-НЕ 10 поступает на управляющий вход интегратора 9, уменьшая его постоянную времени. В результате скорость изменения напряжения становится больше. 1 з.п. ф-лы, 2 ил.

где L- дремя задержки в блоке 5 задержки, например, при произвольном использовании в качестве блока задержки элемента И-НЕ 10 t LO ,

где tg- длительность входного импульса; TO -«период следования импульсов опорной частоты, to фронтом импульса частоты F D-TpHrrep 1 переключается в единичное состояние

(фиг. 2 б) в момент времени t , а в момент tj фронтом инвертированного импульса частоты F блока 5 в единичное состояние переключается D-триггер.З (фиг. 2г),который само5 блокируется в этом состоянии, поскольку напряжение логического О с инверсного выхода D-триггера 3 запрещает прохождение импульсов частоты FO на синхровход D-триггера

0 3. Таким образом, в интервале времени to - t, и t J - t.

на выходе D-триггера 1 (фиг. 2в) имеются импульсы с длительностью, пропорциональной разности фаз входных частот 5 FO и F,, в результате на выходе интегратора 9 в интервале t - Ц происходит нарастание выходного напряжения со скоростью, определяемой постоянной времени интегратора 9 в этом интервале времени (фиг. 2а).

В интервале t - t, на выходе элемента ИЛИ 7 логический О - интегратор 9 находится в режиме хранения.

В момент t D-триггер 1 переключается в единичное состояние (фиг.2в), на выходе элемента ИЛИ 7 также появляется уровень логической 1, при этом напряжение на выходе интегратора 9 начинает нарастать с той же скоростью, что и в интервале t - t В момент t,, разность фаз

-( .

между импульсами частот FO и F становится больше Т и фронтом инвертированного импульса частоты F, блока 5 D-тригер 3 переключается в единичное сос ;тояние (фиг. 2г). Одновременно на выходе элемента И-НЕ 10 также появляется уровень логической 1, под воздействием которого полоса пропускания интегратора 9 увеличивается и напряжение на выходе интегратора 9 нарастает с большей скоростью. В момент времени t начинают опережать по фазе импульсы частоты Р . Таким образом, первый же опережающий импульс частоты F сбрасьюает по R-входу D-триггер 3 в нулевое состояние в момент t (фиг. 2 г).

Таким образом D-триггер 2 переключается в единичное состояние (фиг. 2е), а интегратор 9 начинает разряжаться с той же скоростью, что и в интервалы to - t, и t - tg , поскольку в момент t на выходе элемента И-НЕ 10 логический О и полоса пропускания интегратора 9 меньше В MOMe HTtg фронтом импульса часто- D-триггер 2 сбрасывается в

t5 на t

ты 1

нулевое состояние. В интервале t - режим хранения напряжения интеграторе 9. В момент времени D-триггер 2 снова переключается в единичное состояние, а в момент t единичное состояние с входа D-триг- гера 4 переписывается на его выход фронтом инвентированного импульса частоты F, (фиг. 2ж), поскольку разность фаз между импульсами частот F. и F стала больше I . При этом на

выходе элемента И-НЕ 10 также появляется напряжение логической 1, под воздействием которой постоянная времени интегратора 9 уменьшается, а скорость изменения напряжения становится больше, чем на интервалах

t g - t и tg - tg .

Таким образом, за счет самоблокировки D-триггеров 3 или 4, в зависимости от знака частотной расстройки, в импульсном частотно-фазовом детекторе отсутств.уют паузы при разности фаз и V ( i- 2ТГ) в частотном режиме и за счет коммутаций постоянной BpeMeHji интегратора 9 получают более высокую скорость нарастания выходного напряжения, что позволяет сократить время достижения режима синхронизации, т.е. увеличить быстродействие.

Формула изобретения

Г. Импульсный частотно-фазовый детектор по авт. св. № 1124424, о т- личающийся тем, что, с целью увеличения быстродействия, введен элемент И-НЕ, первый вход которого соединен с инверсным выходом третьего D-триггера, а второй вход соединен с инверсным выходом четвертого D-триггера, выход элемента И-НЕ подключен к управляющему входу интегратора, инверсный выход третьего D-триггера подключен к второму входу первого блока задержки, а инверсный выход четвертого D-триггера подключен к второму входу второго блока задержки, прямой выход перво го D-триггера соединен, с R-входом четвертого D-триггера, а прямой выход второго D-триггера соединен с R-входом третьего D-триггера.

2. Детектор по п.1, отличающийся тем, что блок задержки выполнен на элементе И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1285558A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1246334A1 |

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

| Устройство сравнения частот и фаз | 1983 |

|

SU1171971A1 |

| Импульсный частотно-фазовый детектор | 1985 |

|

SU1312718A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

Изобретение относится к радиотехнике и является дополнительным к авт. св. № 1124424. Цель изобрете-:.; ния - увеличение быстродействия. Сигнал частоты о постзшает на С-вход D-триггера (ДТ) 1, ;на R-вход ДТ 2 и на блок задержки (fis) 5, Сигнал частоты F поступает на С-вход ДТ 2, R-вход ДТ 1 и на БЗ 6. БЗ 5 и 6 обес- 1печивают время задержки , равное длительности входного импульса. Когда FO F , фронтом импульса частоты FO ДТ 1 устанавливается в единичное состояние. ДТ 3 устанавливается в

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-03-30—Публикация

1984-06-21—Подача