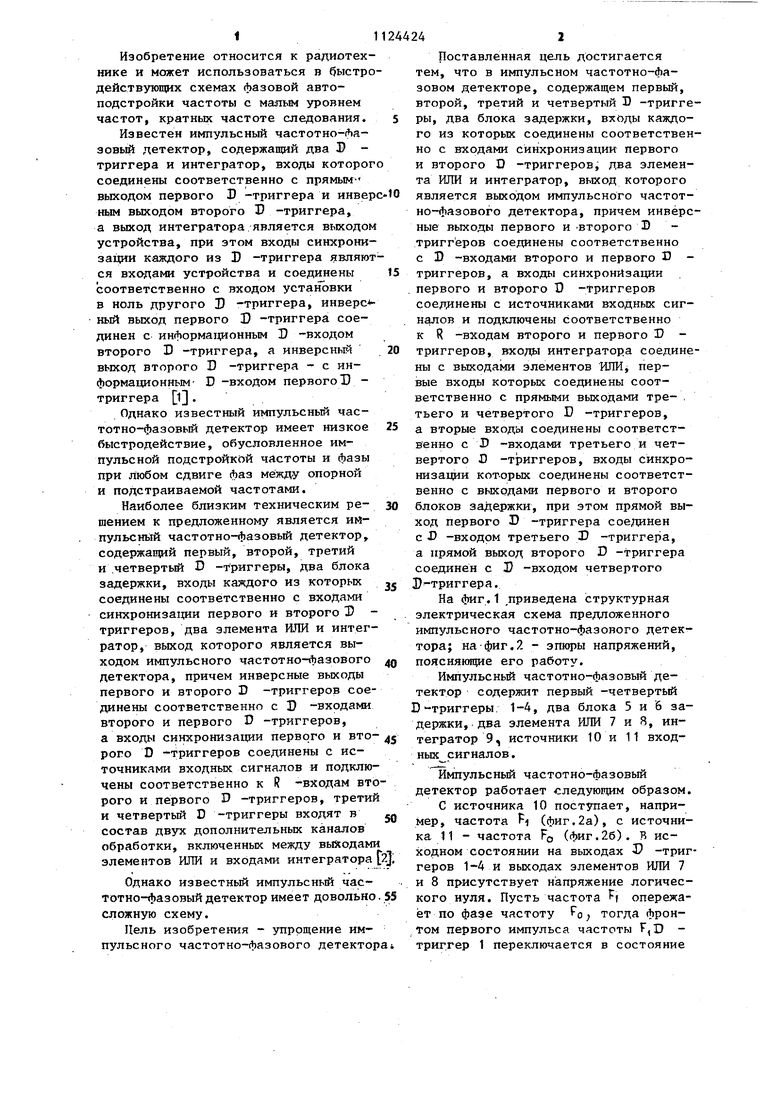

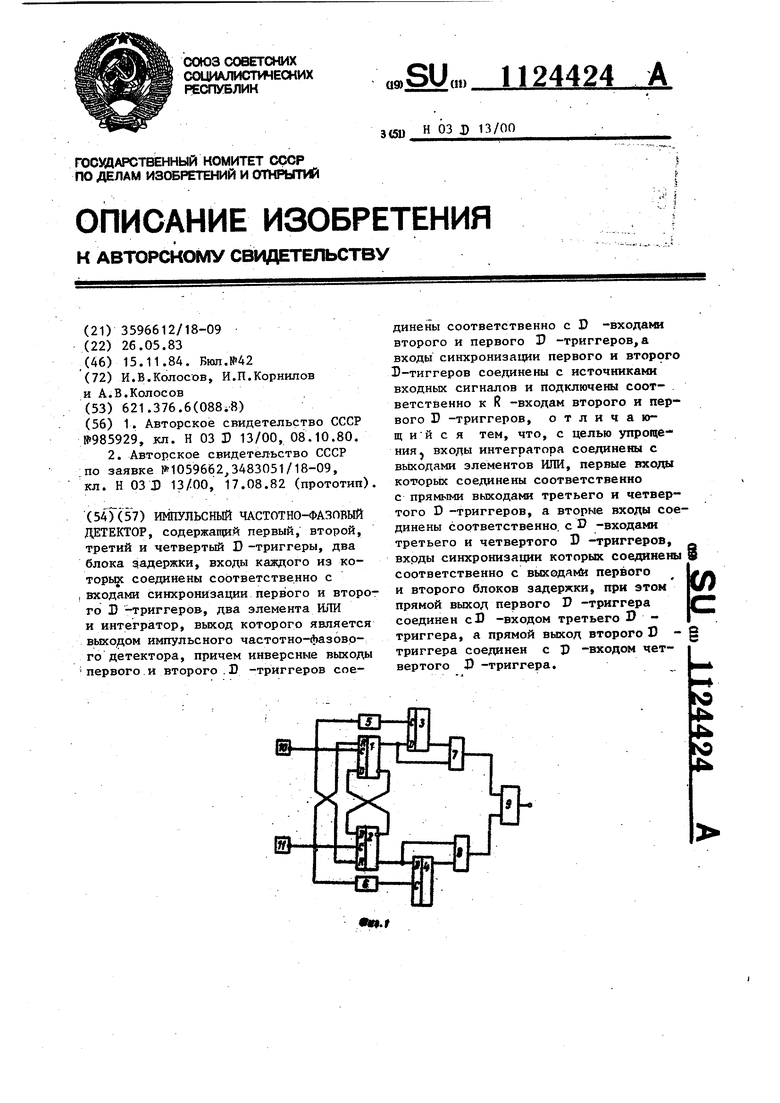

Изобретение относится к радиотехнике и может использоваться в быстро действую1Ш х схемах фазовой автоподстройки частоты с малым уровнем частот, кратных частоте следования. Известен импульсный частотно-Лазовый детектор, содержащий два 3 триггера и интегратор, входы которог соединены соответственно с прямымвыходом первого D -триггера и инвер ным выходом второго 33 -триггера, а выход интегратора является выходом устройства, при этом входы синхронизации каждого из D -триггера являют ся входами устройства и соединены соответственно с входом установки в ноль другого В -триггера, инверс ный выход первого D -триггера соединен с информатщонным D -входом второго D -триггера, а инверсный вмход второго D -триггера - с информационным- D -входом первого) триггера D1 Однако известный импульсный частотно-фазовый детектор имеет низкое быстродействие, обусловленное импульсной подстройкой частоты и фазы при любом сдвиге фаз между опорной и подстраиваемой частотами. Наиболее близким техническим решением к предложенному является импульсный частотно-фазовый детектор, содержащий первый, второй, третий и .четвертый D -триггеры, два блока задержки, входы каждого из которых соединены соответственно с входами синхронизации первого и второго 1) триггеров, два элемента ИЛИ и интегратор, выход которого является выходом импульсного частотно-фазового детектора, причем инверсные выходы первого и второго D -триггеров соединены соответственно с D -входами второго и первого D -триггеров, а входы синхронизации первого и вто рого D -триггеров соединены с источниками входных сигналов и подклю чены соответственно к R -входам вт рого и первого D -триггеров, трети и четвертый D -триггеры входят в состав двух дополнительных каналов обработки, включенных между элементов ИЛИ и входами интегратора Однако известньй импульсный частотно-фазовый детектор имеет довольно сложную схему. Цель изобретения - упрощение импульсного частотно-фазового детекто Поставленная цель достигается тем, что в импульсном частотно-фа зовом детекторе, содержащем первый, второй, третий и четвертый D -триггеры, два блока задержки, входы каждого из которых соединены соответственно с входами синхронизации первого и второго D -триггеров, два элемента ИЛИ и интегратор, выход которого является выходом импульсного частотно-фазового детектора, причем инверсные выходы первого и Второго D триггеров соединены соответственно с D -входами второго и первого D триггеров, а входы синхронизации первого и второго О -триггеров соединены с источниками входных сигналов и подключены соответственно к R -входам второго и первого D триггеров, входы интегратора соединены с выходами элементов ИЛИ первые входы которых соединены соответственно с прямыми выходами тре- , тьего и четвертого D -триггеров, а вторые входы соединены соответственно с D -входами третьего и четвертого Л -триггеров, входы синхронизации которых соединены соответственно с выходами первого и второго блоков задержки, при этом прямой выход первого D -триггера соединен с JD -входом третьего D -триггера, а прямой выход второго D -триггера соединен с U -входом четвертого г-триггера. На фиг.1 приведена структурная электрическая схема предложенного импульсного частотно-фазового детектора; на фиг.2 - эпюры напряжений, поясняющие его работу. Импульсный частотно-фазовый детектор содержит первый -четвертый триггеры. 1-4, два блока 5 и 6 задержки, два элемента ИЖ 7 и 8, интегратор 9, источники 10 и 11 входных сигналов. Импульсный частотно-фазовый детектор работает следующим образом. С источника 10 поступает, например, частота PI (фиг.2а), с источника 1 1 - частота FQ (фиг.26). В исходном состоянии на выходах J -триггеров 1-4 и выходах элементов ИЛИ 7 и 8 присутствует напряжение логического нуля. Пусть частота PI опережает по фазе частоту РО; тогда фронтом первого импульса частоты Г, D триггер 1 переключается в состояние

.3

логической единицы, и на выходе элемента ИЛИ 7 появляется также уровень логической единицы, причем если разность фаз между F, и Гь больше

j- 2и, где L - время задержки в блоке 5 задержки, а Т - период опорной частоты, то D -триггер 3 также переключается в состояние логической единицы, в котором находится до тех nopj пока разность- фаз между Гч и FQ больше - .2ii. При этом на выходе

TO . ,

элемента 1ШИ 7 также присутствует

напряжение логической единигда, пока /J/j

(фиг.2в). Приди -.2м

о.То

иьетульсы частоты f переключают в единичное состояние только D триггер 1, а импульсы частоты в нулевое состояние, при этом 33 триггер 3 остается в нулевом состоянии, и на выходе элемента ИЛИ 7 появляются импульсы, длительность которых пропорциональна фазовой раз: ности частот F, и FQ .. Причем пока частота FI FQ либо при опережении по фазе частоты F при F, на вьгходе элемента ИЛИ 8 поддерживается уровень логического нуля, поскольку Б -триггеры 2 и 4 находятся в состоянии логического нуля. Напряжение на выходе элемента ИЛИ 7 интегрируется в интеграторе 9 (фиг.2г, напряжение на выходе интегратора 9 увеличивается- до тех пор, пока не наступит синфазный режим, при этом-на выходах элементов ИЛИ 7 и 8 присутствует напряжение логического нуля. Эти сигналы удерживают интегратор 9 в-закрытом состоянии, при котором напряжение на выходе остается постоянным и пульсации напряжения отсутствуют.

Пусть теперь частота F, (фиг.2д) отстает по фазе от частоты Fg (фиг.2е), тогда Лронтом первого импульса частоты FQ D -триггер 2 переключается в состояние логической единицы, и на выходе элемента Ю1И 8

.появляется также уровень логической единицы, причем если разность фаз

2442Л4

FI и fj, больше 1 З I ToDI Тд I

триггер 4 также переключается в сос тояние логической единицы, в кото5 ром находится до тех пор, пока pas1 I

ность фаз между F, и F больше

На выходе элемента ИЛИ 8 также при0 сутствует напряжение логической единицы (фиг.2ж). При лср }- -2«1 пульсы частоты t-Q переключают . в единичное состояние только D -триггер 5 2, а импульсы частоты F в нулевое состояние, при этом D -Триггер

I

4 остается в нулевом состоянии, и на выходе элемента ИЛИ Я появляются импульсы, длительность которых

0 пропорциональна фазовой разности

частот f, и FO . Причем пока F, Fjj либо при опережении по фазе частоты FO при F РО- на выходе элемента ШШ 7 поддерживается уровень логичес5 кого нуля, поскольку D -триггеры 1 и 3 находятся в состоянии логического нуля. Напряжение на выходе элемента ИЛИ 8 поступает на другой вход интегратора 9, при этом напряжение на выходе интегратора 9 уменьшается (фиг.2з) до тех пор, пока не наступит синфазный режим.

По сравнению с базовьи объектом предлагаемый импульсньгЧ частотнофазовый детектор имеет большее быстродействие, поскольку на выходе одного из элементов ИЛИ в зависимости от знака разности частот или фаз поддерживается уровень логической

единицы все время, noKafitf - 2.1 , - -.

и выходное напряженне быстрее достигает уровня, при котором настзтает режим синхронизации. В результате значительного упрощения схемы предпоженньй и myльcный частотно-фазовый детектор по сравнению с про тотипом при ojE iHaKOBOM быстро действии имеет более низкую себестоимость.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1285558A1 |

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

| Устройство сравнения частот и фаз | 1983 |

|

SU1171971A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1246334A1 |

| Импульсный частотно-фазовый детектор | 1985 |

|

SU1312718A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР, содержащий первый, второй, третий и четвертый D -триггеры, два блока задержки, входы каждого из коTopi соединены соответственно с входами синхронизации первого и второго 3) -триггеров, два элемента ШШ и интегратор, выход которого является выходом импульсного частотно-фазового детектора, причем инверсные выходы первого.и второго . D триггеров соединены соответственно с D -входами второго и первого 3) -триггеров,а входы синхронизации первого и второго 3)-тиггеров соединены с источниками входных сигналов и подключены соответственно к R -входам второго и первого D -триггеров, отличающий с я тем, что, с целью упрощения, входы интегратора соединены с выходами элементов ШШ, первые входы которых соединены соответственно с прямыми выходами третьего и четвертого D -триггеров, а вторые входы соединены соответственно, с -входами третьего и четвертого D -триггеров, 9 вхрды синхронизации которых соединеш соответственно с выходами первого и второго блоков задержки, при этом прямой выход первого D -триггера соединен cD -входом третьего D триггера, а прямой выход второго D триггера соединен с р -входом четвертого D -триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Импульсный частотно-фазовый детектор | 1980 |

|

SU985929A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Телефонная трансляция с катодными лампами | 1922 |

|

SU333A1 |

Авторы

Даты

1984-11-15—Публикация

1983-05-26—Подача