(54) ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР .

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1982 |

|

SU1059662A1 |

| Импульсный частотно-фазовый детектор | 1986 |

|

SU1424114A2 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1328924A2 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1702539A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Широтно-импульсный частотно-фазовый детектор | 1982 |

|

SU1075368A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Импульсный частотно-фазовый детектор | 1985 |

|

SU1312718A1 |

| Импульсный частотно-фазовый детектор | 1987 |

|

SU1483594A1 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

Изобретение ртносжтся к ргцщогехнике и может использоваться в радиотехнических устройствах различного назначенияf в частности в устройствах фазовой автоподстройки частоты. .

( Известен импульсный частотно-фазоBbtil детектор (ИЧФД), содер)хащий первый и второй триггеры, каждый из которых имеет вход запуска, срабатывающий по переднему фронту, выход и вход сброса. алходы первого и второго формирователей импульсов соединены соответственно с входами запуска первого и второго триггеров, с одним из входов первой и второй схем совпадения. Выход каждого триггера соединен с одним из входов каждой схемы совпадения, а также с соответств1пощим входом интегратора, при зтом выход каждой схемы совпгщения соединен с входом сброса того триггера, вход запуска которого соединен с одним из входов схемы совпадения С13.

Наиболее близким к предлагаемому является импульсный частотно-фазовый детектор, содержащий два о-триггера и интегратор, входы которого соединены соответственно с прямым выТкоярм первого D-триггера и инверсным выходом второго D-триггера, а выход является выходом устройства, при зтом входы синхронизации каждого О-триггера являются входами устройства и соединены соответственно с входом установки в нуль;другого D-триггера, а на D-входы каждого о-триггера подан уровень логиче- .

10 ской единицы С2 .

Однако известные импульсные ч стотно-фазовые детекторы имеют значительный уровень импульсных помех в выходном сигнале.

15

Цель изобретения - уменьшение уровня импульсных помех в выходном сигнале.

Для достижения цели в частотно-фа.зовом детекторе, содержащем два

20 D-триггера и интегратор, входы которого соединены соответственно с прямым выхЬдом первого D-триггера и инверсным выходом второго О-триггера, а выход является выходом уст25ройства, при этом входы синхронизации каждого D-триггера являются входами устройства и соединены соответственно с входом установки в нуль другого О-триггера, инверсный выход

30 первого О-триггера соединен с информацйонным D-входом второго 0-триг гера, а инверсный выход второго D-триг гера - с информационным D-входом первого D-триггера.

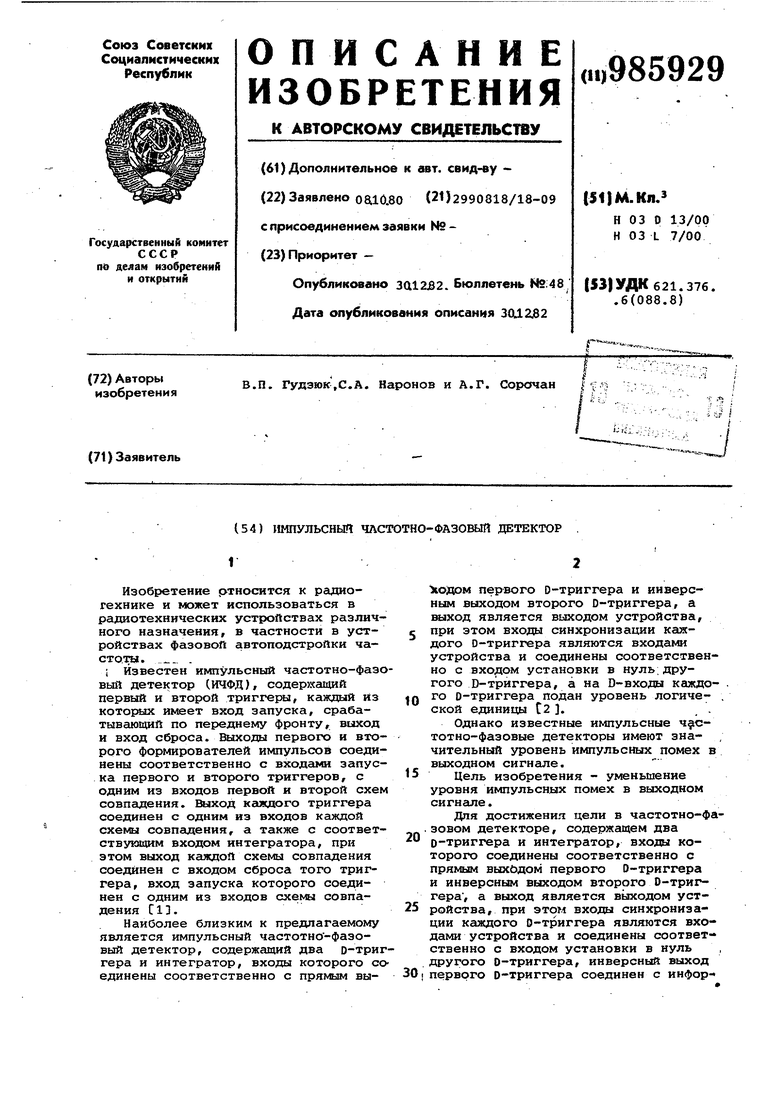

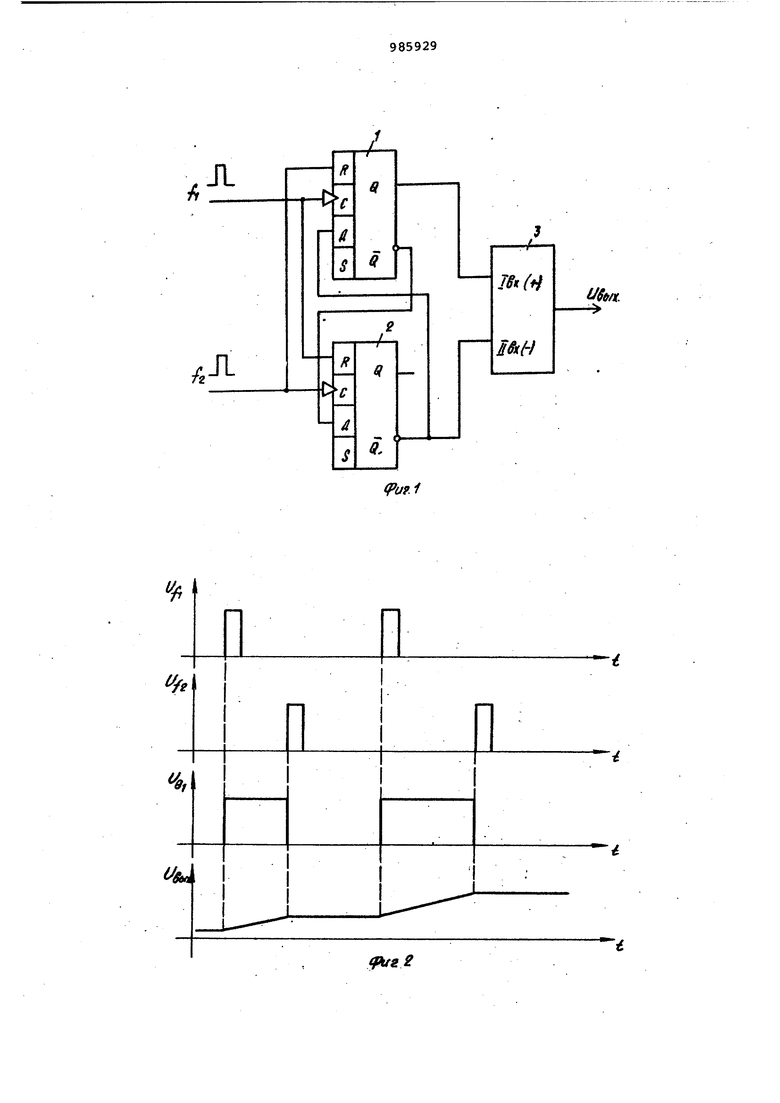

На фиг; 1 приведена структурная электрическая схема предлагаемого 5 устройства; на фиг. 2 и 3 - эпюры напряжений, поясняющие работу устройства.

Устройство содержит первый и второй О-триггеры 1 и 2, интегратор 3. 10

Устройство работает следующим образом.

В исходном состоянии на выходах D-триггеров 1 и 2 уровни напряжений соответствуют логическому нулю, а 15 на инверсных выходах уровни напряжений соответствуют логической единице. Первый импульс, подаваемый на вход запуска первого о-триггера и на вход сброса второго О-триггера 2, 20 устанавливает на выходе первого О-триггера 1 напряжение, соответствующее уровню логической единицы, так как информационный вход этого О-триггера соединен с инверсным выходом 25 второго D-триггера 2 и не изменяет логического состояния второго о-триггера 2. Второй импульс,-подаваемый на вход запуска второго D-триггера 2 и на вход сброса первого D-триггера 1, зо ,возвращает первый D-триггер 1 в исходное логическое состояние и не изменяет логического состояния второго D-триггера 2, так как в момент прихода второго импульса на информационном входе второго о-триггера 2, соединенном с инверсным выходом первого D-триггера 1, был уровень логического нуля. Выход первого р-триггера 1 соединен с первым входом Ig(+) интегратора 3, выход второго О .-триггера -2 соединен с входом Ilgx() интегратора 3. С выхода первого D-триггера 1 снимается положительный импульс, равный разности фаз первого и второго импульсов. 45 На фиг. 2 показаны эпюры напряжений для этого случая.

На фиг. 3 показаны эпюры напряжений, когда второй импульс опережает по фазе первый импульс. В этом слу- 50 чае логическое состояние первого D-триггера 1 не изменяется, а на

выходе второго О-триггера 2 возникает положительный импульс, равный разности фаз первого и второго импульсов. На выходе интегратора 3 происходит уменьшение напряжения, пропорциональное длительности импульса разности фаз с второго О-триггера 2. Минимальная длительность импульсов на выходах триггеров может быть не более времени задержки срабатывания триггера.Введение новых связей позволяет в установившемся режиме (при нулевом сдвиге фаз между напрях ениями входных сигналов ) получить на прямом выходе О-триггера 1 логический О, а на инверсном выходе другого О-триггера 2 - логическую . Эти сигналы удерживают интегратор 3 в закрытом состоянии. Выходное напряжение остается постоянным и пульсации напряжений отсутствуют.

; Таким образом, в предлагаемом устройстве по сравнению с прототипом значительно снижен уровень импульсны помех.

Формула изобретения

Импульсный частотно-фазовый детектор, содержащий два О-триггера и интегратор, выходы которого соединены соответственно с прямым выходом первого D-триггера и инверсным выходом второго О-триггера, а выход является выходом устройства, при этом входы синхронизации каждого D-триггера являются входами устройства и соединены соответственно с входом установки в нуль другого D-триггера, отличающийся тем, что, с целью уменьшения уровня импульсных помех в выходном сигнале, инверсный выход первого О-триггера соединен с информационным 0-входом второго О-триггера, а инверсный выход второго 0-трйггера - с информационным D-входом первого О-триггера.

Источники информации, принятые во внимание при экспертизе

кл. Н 03 В 3/04, 1980 (прототип).

ISn(

Щшк.

Риг г

%

1

I

Ue.

Авторы

Даты

1982-12-30—Публикация

1980-10-08—Подача