Изобретение относится к вычислительной технике для статистических исследований, в частности к обработке случайных сигналов механических на- пряжений в деталях машин.

Целью изобретения является повьопе- ние быстродействия устройства при высоких требованиях к точности определения параметров.

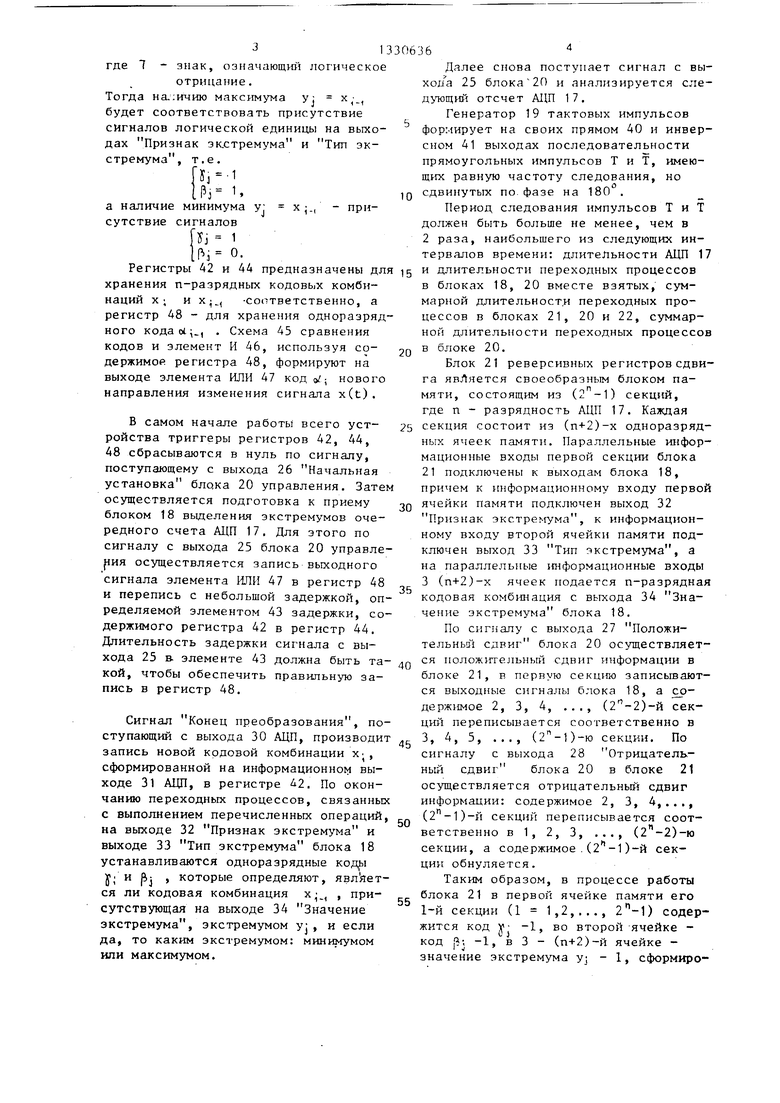

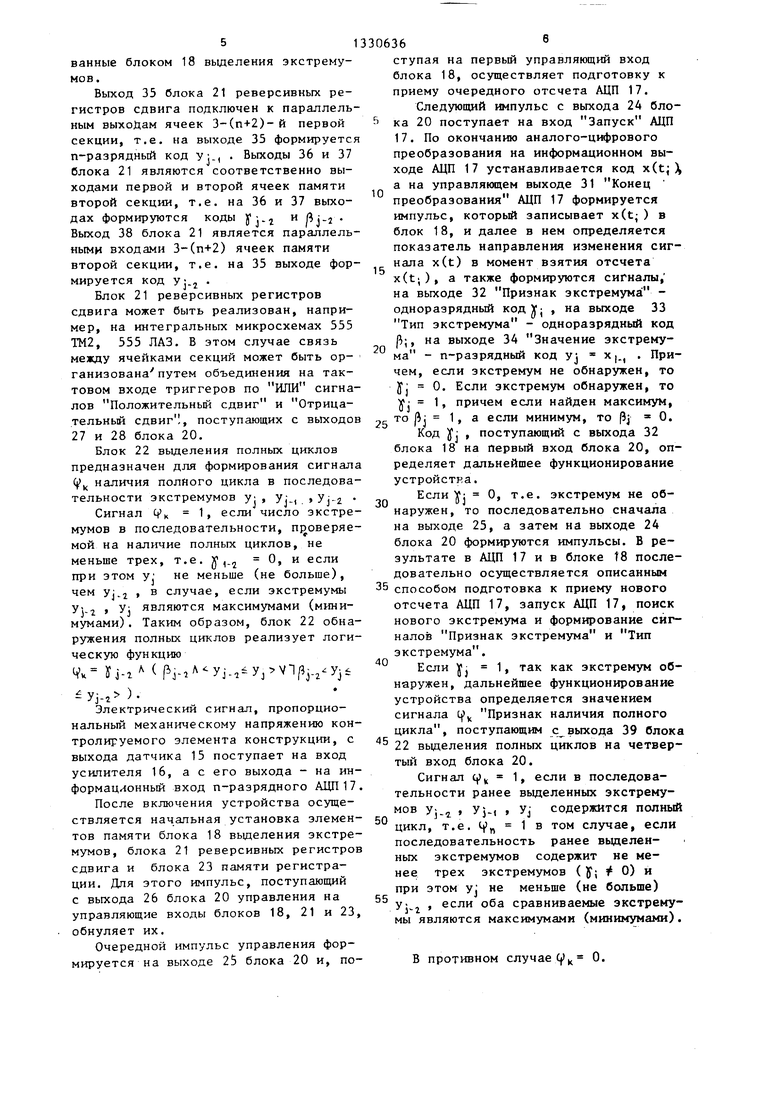

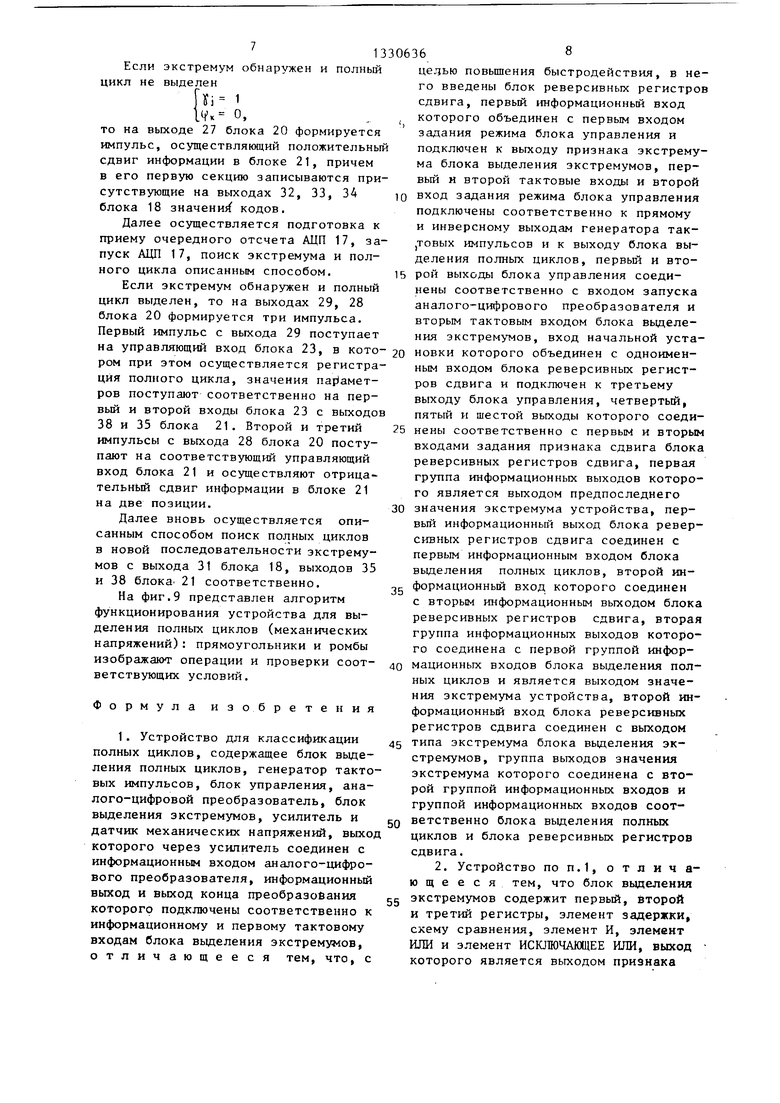

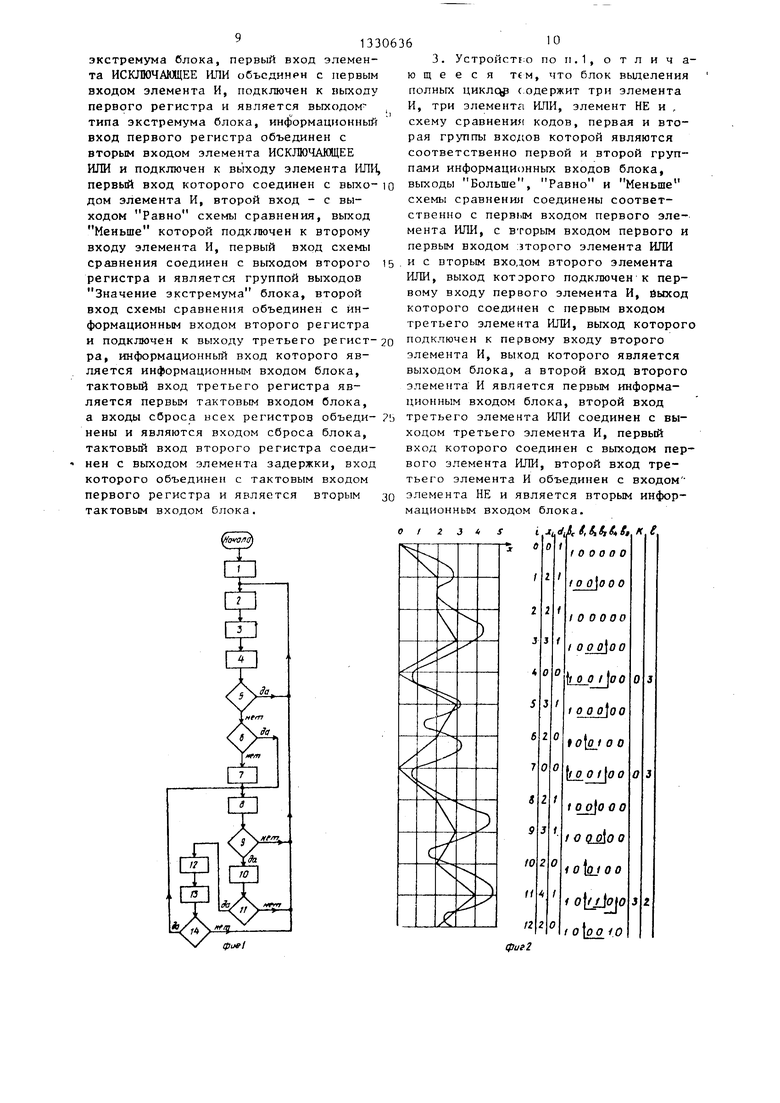

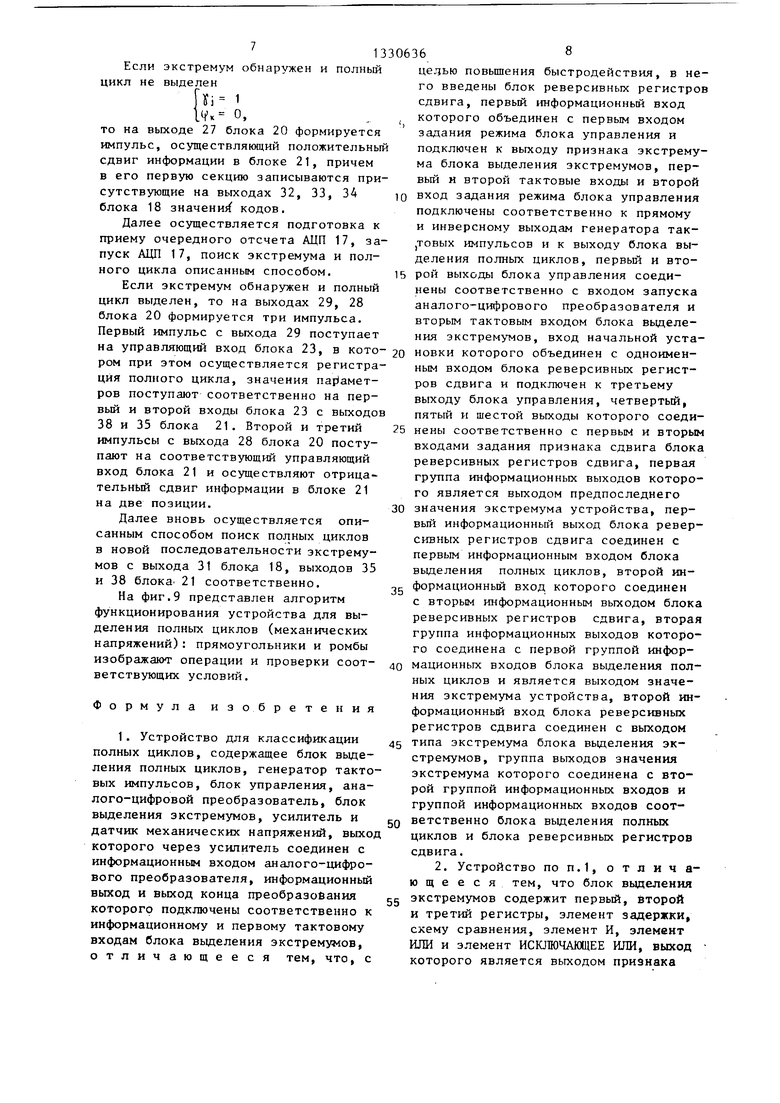

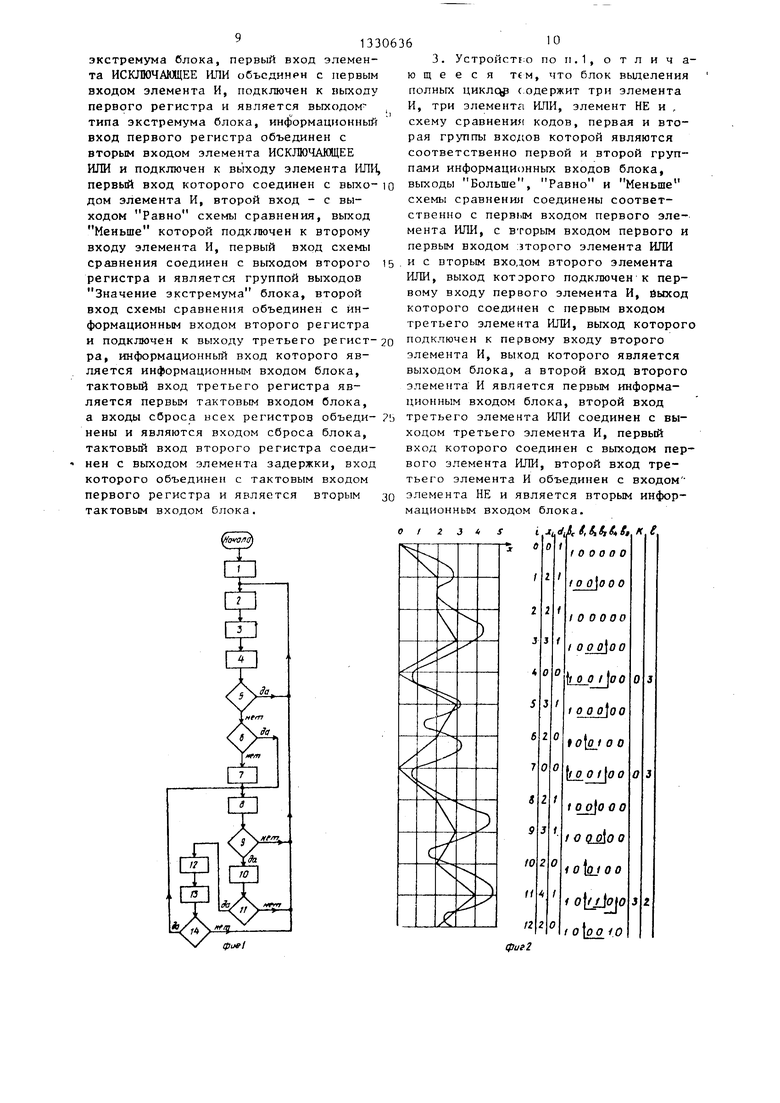

На фиг.1 представлена блок-схема алгоритма функционирования устройства} на фиг.2 - пример процесса поиска полных циклов при реализации сигнала (график) в форме гладкой кривой{ на фиг.З - структурная схема устройстваj на фиг.4 - функциональная схема блока вьщеления экстремумов} на фиг.З - ,то же, блока выделения полных циклов , на фиг.6 - то же, блока регистрации, на фиг.7 - автоматный граф блока управления; на фиг.З - функциональная схема блока управления на фиг.9 - блок-схема алгоритма функционирования блока выделения полных циклов; на фиг.1 О -.процесс поиска (определения) полных циклов в реализации сигнала механических напряжений с помощью данного устройства.

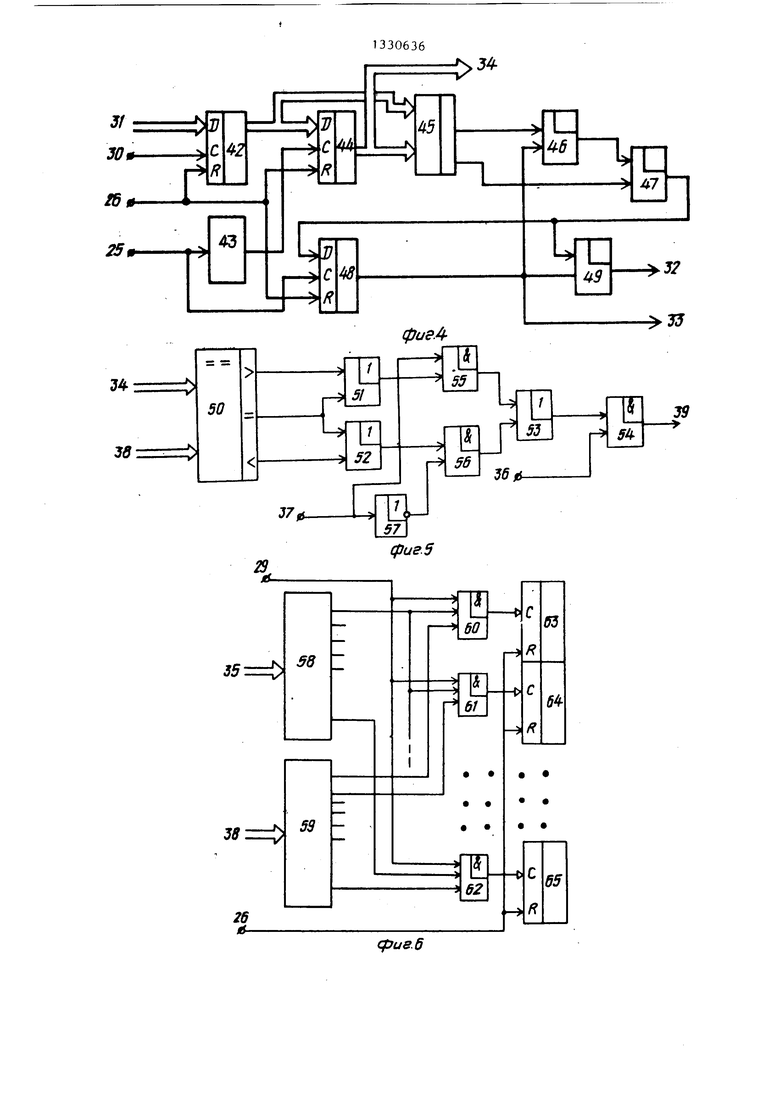

На фиг.1 позициями с 1 по 14 обо- значены соответствующая последовательность операций. Схема устройства (фиг.З) содержит датчик 15 механических напряжений, усилитель 16, аналого-цифровой преобразователь (АДП) 17, блок 18 выделения экстремумов, генератор 19 тактовых импульсов, блок 20 управления, блок 21 реверсивных регистров сдвига, блок 22 выделения полных циклов, блок 23 памяти регистра- ции, выходы 24-29 блока управления, 30-41 - входы и выходы различных узлов схемы.

Блок 18 выделения экстремумов (фиг.4) содержит регистры 42, эле- мент 43 запрета, регистр 44, схему 45 сравнения, элемент И 46, элемент ИЛИ 47, регистр 48, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 49,

Блок 22 выделения полных циклов (фиг.5) содержит схему 50 сравнения, элементы ИЛИ 51-53, элементы И 54-56, элемент НЕ 57.

Для регистрации может быть использована схема (фиг.6), содержащая де- шифраторы 58-59, элементы И 60-62, счетчики 63-65.

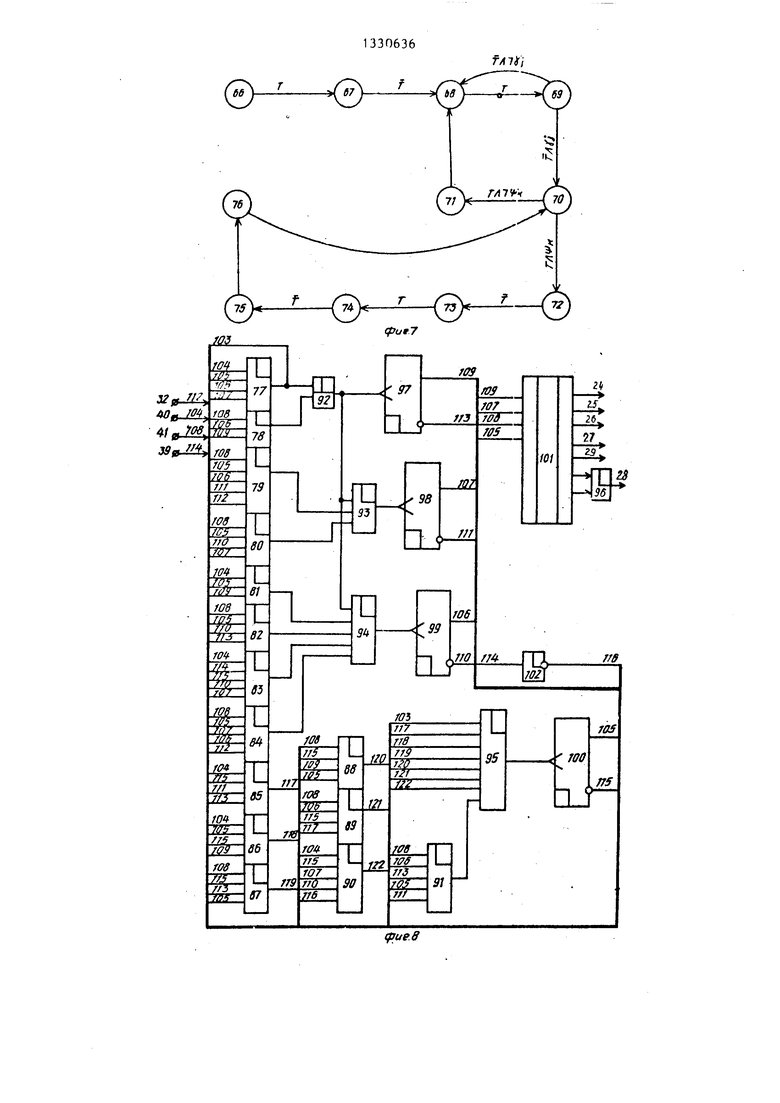

Позициями 66-7Ь обозначены верщины графа (фиг.7).

Блок 2 управления (фиг.8) содержи элементы И 77-91, элементы ИЛИ 92-96 триггеры 97-100, дешифратор 101, элемент НЕ 102, позиции 102-122 обозначают жгутовые соединения между элементами схемы.

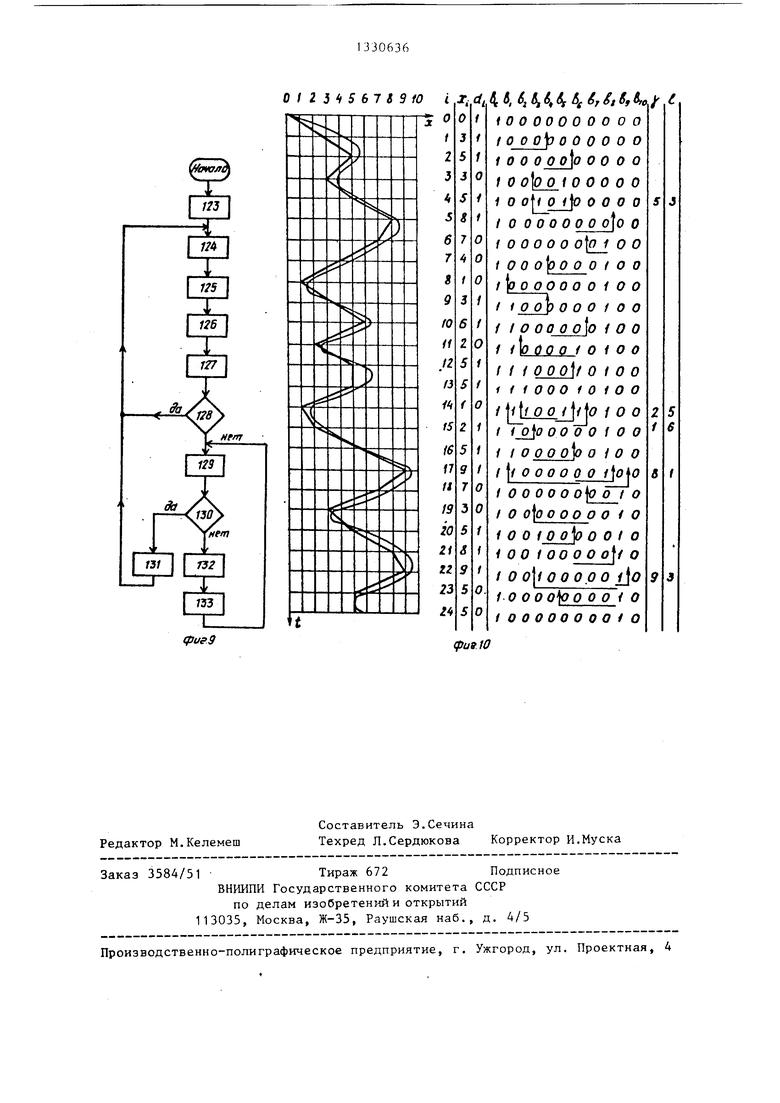

На фиг.9 приняты позиции 123-133.

Устройство работает следующим образом.

Блок 18 выделения экстремумов предназначен для нахождения экстрему мальных значений в последовательност п-разрядных кодовых комбинаций, поступающих с информационного выхода АЦ 17 и для формирования двух вспомогательных сигналов: сигнала Признак экстремума в случае нахождения экстремального значения и сигнала Ти экстремума, характеризующего тип найденного экстремума (минимум он ил максимум),

Работа блока 18 основана на следующем принципе.

Пусть Xj , X; - п-разрядные кодовые комбинации, являющиеся отсчетами АДП 17, полученными в результате аналого-цифрового преобразования выходного сигнала X;(t) усилителя 16 в моменты t.

t,Пусть oL И о,1-1показатели наклона изменения сигнала

x(t) в моменты t;, и t{, причем

X;

ot;

1, при X;.,

при X при X,

X;

X;

х:,

oi.;( О, или формально

.., Л

где р - логическая функция, принимающая значение 1 при выполнении условия р и значение О при невыполнении,

V и Л - знаки логических операций дизъюнкции и конъюнкции соответственно.

Отсчет Xj I будет экстремумом, когда

или Г ( О 1

UI да Г 1 ИЛИ Г (

loi;-, О Ы;-,

причем, если .,

О,

«;.,

то х;, будет

1, то

минимумом, а если будет максимумом.

Из этого следует, что значения вспомогательных сигналов блока выделения экстремумов Признак экстремума и Тип экстремума можно опреде- лить соответственно как значение функттий

.,yi., и

3

знак, означающш логическо

где 7 отрицание. Тогда на.;ичию максимума

Yj

X

будет соответствовать присутствие сигналов логической единицы на выходах Признак эк.стремума и Тип эк

стремума

т.е,

Sj -i Pj U

а наличие минимума у:

X

- присутствие сигналов

5j 1 ;f, 0.

Регистры 42 и 44 предназначены для 5 длительности переходных процессов хранения п-разрядных кодовых комби- в блоках 18, 20 вместе взятых, сумПериод следования импульсов Т и должен быть больше не менее, чем в 2 раза, наибольшего из следующих ин тервалов времени: длительности АЦП

наций X; и Х ( -соответственно, а регистр 48 - для хранения одноразрядного кодао1;, . Схема 45 сравнения кодов и элемент И 46, используя содержимое регистра 48, формируют на выходе элемента ИЛИ 47 код ; нового направления изменения сигнала x(t).

В самом начале работы всего устройства триггеры регистров 42, 44, 48 сбрасываются в нуль по сигналу, поступающему с выхода 26 Начальная установка блока 20 управления. Затем осуществляется подготовка к приему блоком 18 выделения экстремумов очередного счета А1Ш 17, Для этого по сигналу с выхода 25 блока 20 управле- рия осуществляется запись выходного сигнала элемента ИЛИ 47 в регистр 48 и перепись с небольщой задержкой, определяемой элементом 43 задержки, содержимого регистра 42 в регистр 44. Длительность задержки сигнала с выхода 25 в. элементе 43 должна быть такой, чтобы обеспечить правильную запись в регистр 48.

Сигнал Конец преобразования, поступающий с выхода 30 АЦП, производит запись новой кодовой комбинации Х , сформированной на информационном выходе 31 АЦП, в регистре 42. По окончанию переходных процессов, связанных

20

30

марной длительности переходных процессов в блоках 21, 20 и 22, суммарной длительности переходных процессо в блоке 20.

Блок 21 реверсивных регистров сдви га явЛяется своеобразным блоком памяти, состоящим из (2 -1) секций, где п - разрядность АДП 17. Каждая 25 секция состоит из (п+2)-х одноразряд ных памяти. Параллельные инфор мационные входы первой секции блока 21 подключены к выходам блока 18, причем к информационному входу первой ячейки памяти подключен выход 32 Признак экстремума, к информационному входу второй ячейки памяти подключен выход 33 Тип экстремума, а на параллельные информационные входы 3 (п+2)-х ячеек подается п-разрядная кодовая комбинация с выхода 34 Значение экстремума блока 18.

По сигналу с выхода 27 Положительный сдвиг блока 20 осуществляется положительный сдвиг информации в блоке 21, в первую секцию записываются выходные сигналы блока 18, а ср- держимое 2, 3, 4, ..., ()-й секций переписывается соответственно в 3, 4, 5, ..., ()-ю секции. По сигналу с выхода 28 Отрицательный сдвиг блока 20 в блоке 21 осуществляется отрицательный сдвиг информации: содержимое 2, 3, 4,...,

40

45

С выполнением перечисленных операций, ()-й секций переписывается соот- на выходе 32 Признак экстремума и ветственно в 1, 2, 3, ..., (2-2)-ю выходе 33 Тип экстремума блока 18 устанавливаются одноразрядные код. У; и - , которые определяют, явл йет- ся ли кодовая комбинация х

1-, . присутствующая на выходе 34 Значение экстремума, экстремумом yj, и если да, то каким экстремумом: минга умом или максимумом.

55

ветственно в 1, 2, 3, .. секции, а содержимое.()-й секции обнуляется.

Таким образом, в процессе работы блока 21 в первой ячейке памяти его 1-й секции (1 1,2,..., ) содержится код у- -1, во второй-ячейке - код Р-, -1, в 3 - (п+2)-й ячейке - значение экстремума yj - 1, сформиро

Далее снова поступает сигнал с вы- хо;/а 25 блока 20 и анализируется сле- д тощий отсчет А1Щ 17.

Генератор 19 тактовых импульсов формирует на своих прямом 40 и инверсном 41 выходах последовательности прямоугольных импульсов Т и Т, имеющих равную частоту следования, но сдвинутых по фазе на 180 .

Период следования импульсов Т и Т должен быть больше не менее, чем в 2 раза, наибольшего из следующих интервалов времени: длительности АЦП 17

0

0

марной длительности переходных процессов в блоках 21, 20 и 22, суммарной длительности переходных процессов в блоке 20.

Блок 21 реверсивных регистров сдвига явЛяется своеобразным блоком памяти, состоящим из (2 -1) секций, где п - разрядность АДП 17. Каждая 5 секция состоит из (п+2)-х одноразрядных памяти. Параллельные информационные входы первой секции блока 21 подключены к выходам блока 18, причем к информационному входу первой ячейки памяти подключен выход 32 Признак экстремума, к информационному входу второй ячейки памяти подключен выход 33 Тип экстремума, а на параллельные информационные входы 3 (п+2)-х ячеек подается п-разрядная кодовая комбинация с выхода 34 Значение экстремума блока 18.

По сигналу с выхода 27 Положительный сдвиг блока 20 осуществляется положительный сдвиг информации в блоке 21, в первую секцию записываются выходные сигналы блока 18, а ср- держимое 2, 3, 4, ..., ()-й секций переписывается соответственно в 3, 4, 5, ..., ()-ю секции. По сигналу с выхода 28 Отрицательный сдвиг блока 20 в блоке 21 осуществляется отрицательный сдвиг информации: содержимое 2, 3, 4,...,

0

5

()-й секций переписывается соот- ветственно в 1, 2, 3, ..., (2-2)-ю

()-й секций переписывается соот- ветственно в 1, 2, 3, ..., (2-2)-ю

5

ветственно в 1, 2, 3, .. секции, а содержимое.()-й секции обнуляется.

Таким образом, в процессе работы блока 21 в первой ячейке памяти его 1-й секции (1 1,2,..., ) содержится код у- -1, во второй-ячейке - код Р-, -1, в 3 - (п+2)-й ячейке - значение экстремума yj - 1, сформиро51

ванные блоком 18 выделения экстремумов.

Выход 35 блока 21 реверсивных регистров сдвига подключен к параллельным выходам ячеек 3-(п+2)-и первой секции, т.е. на выходе 35 формируется п-р аз рядный код у;., . Выходы 36 и 37 блока 21 являются соответственно выходами первой и второй ячеек памяти второй секции, т.е. на 36 и 37 выходах формируются коды If J-J и Aj.j .

Выход 38 блока 21 является параллельными входами 3-(п+2) ячеек памяти второй секции, т.е. на 35 выходе формируется код У;.2 .

Блок 21 реверсивных регистров сдвига может быть реализован, например, на интегральных микросхемах 555 ТМ2, 555 ЛАЗ. В этом случае связь между ячейками секций может быть организована путем объединения на тактовом входе триггеров по ИЛИ сигналов Положительный сдвиг и Отрица- тельньй сдвиг,, поступающих с выходов 27 и 28 блока 20.

Блок 22 выделения полных циклов предназначен для формирования сигнала 9 наличия полного цикла в последовательности экстремумов у- , у,- , , .

Сигнал Фк 1 если число экстремумов в последовательности, проверяемой на наличие полных циклов, не меньше трех, т.е. у,. О, и если при этом у не меньше (не больше), чем , в случае, если экстремумы У „, , у- являются максимумами (минимумами) . Таким образом, блок 22 обнаружения полных циклов реализует логическую функцию

Sj-i f r yj- -yj lf j-i yj

yj.,).

Электрический сигнал, пропорциональный механическому напряжению контролируемого элемента конструкции, с выхода датчика 15 поступает на вход усипителя 16, ас его выхода - на информационный вход п-разрядного АДП 1 7

После включения устройства осуществляется начальная установка элементов памяти блока 18 вьщеления экстремумов, блока 21 реверсивных регистров сдвига и блока 23 памяти регистрации. Для этого импульс, поступающий с выхода 26 блока 20 управления на управляющие входы блоков 18, 21 и 23, обнуляет их.

Очередной импульс управления формируется на выходе 25 блока 20 и, по10

15

30636б

ступая на первый управляющий вход блока 18, осуществляет подготовку к приему очередного отсчета АЦП 17.

Следующий импульс с выхода 24 блой ка 20 поступает на вход Запуск АЦП 17. По окончанию аналого-цифрового преобразования на информационном выходе АЦП 17 устанавливается код x(tj ) а на управляющем выходе 31 Конец преобразования АЦП 17 формируется импульс, который записывает x(t ) в блок 18, и далее в нем определяется показатель направления изменения сигнала x(t) в момент взятия отсчета x(t;), а также формируются сигналы, на выходе 32 Признак экстремума - одноразрядный код у; , на выходе 33 Тип экстремума - одноразрядный код Р;, на выходе 34 Значение экстремума - п-разрядный код yj х |., . Причем, если зкстремум не обнаружен, то Jj 0. Если экстремум обнаружен, то У; 1, причем если найден максимум,

2„ то |ij 1 , а если минимум, то Р| 0.

Код У: , поступающий с выхода 32 блока 18 на первый вход блока 20, определяет дальнейщее функционирование устройства.

Если У: о, т.е. экстремум не обнаружен, то последовательно сначала на выходе 25, а затем на выходе 24 блока 20 формируются импульсы. В результате в АЦП 17 и в блоке 18 последовательно осуществляется описанным

35 способом подготовка к приему нового отсчета АЦП 17, запуск АЦП 17, поиск нового экстремума и формирование сигналов Признак экстремума и Тип

20

30

0

экстремума .

Если If. 1, так как экстремум обнаружен, дальнейшее функционирование устройства определяется значением сигнала t Признак наличия полного цикла, поступающим с выхода 39 блока 22 выделения полных циклов на четвертый вход блока 20.

Сигнал V 1, если в последовательности ранее выделенных экстремумов у- , у5., , yj содержится полный цикл, т.е. ijJ 1 в том случае, если последовательность ранее выделенных экстремумов содержит не менее трех экстремумов ( У; i 0) и при этом у; не меньше (не больше) у- , если оба сравниваемые экстремумы являются максимумами (минимумами).

5

В противном случае Cf 0.

Если экстремум обнаружен и полный цикл не выделен

lfi 1

W. 0.

то на выходе 27 блока 20 формируется импульс, осуществляЕощий положительный сдвиг информации в блоке 21, причем в его первую секцию записываются присутствующие на выходах 32, 33, ЗА блока 18 значени кодов.

Далее осуществляется подготовка к приему очередного отсчета АЦП 17, запуск АЦП 17, поиск экстремума и полного цикла описанным способом.

Если экстремум обнаружен и полный цикл выделен, то на выходах 29, 28 блока 20 формируется три импульса. Первый импульс с выхода 29 поступает

на управляющий вход блока 23, в кото- 2о новки которого объединен с одноименром при этом осуществляется регистрация полного цикла, значения па1 амет- ров поступают соответственно на первый и второй входы блока 23 с выходо 38 и 35 блока 21. Второй и третий импульсы с выхода 28 блока 20 поступают на соответствующий управляющий вход блока 21 и осуществляют отрица- тельнЬй сдвиг информации в блоке 21 на две позиции.

Далее вновь осуществляется описанным способом поиск полных циклов в новой последовательности экстремумов с выхода 31 блока 18, выходов 35 и 38 блока 21 соответственно.

На фиг.9 представлен алгоритм функционирования устройства для выделения полных циклов (механических напряжений): прямоугольники и ромбы изображают операции и проверки соответствующих условий.

Формула изобретения

1. Устройство для классификации полных циклов, содержащее блок выделения полных циклов, генератор тактовых импульсов, блок управления, аналого-цифровой преобразователь, блок выделения экстремумов, усилитель и датчик механических напряжений, выхо которого через усилитель соединен с информационным входом аналого-цифрового преобразователя, информационный выход и выход конца преобразобания которого подключены соответственно к информационному и первому тактовому входам блока выделения экстремумов, отличающееся тем, что, с

целью повьппения быстродействия, в него введены блок реверсивных регистров сдвига, первый информационный вход

которого объединен с первым входом задания режима блока управления и подключен к выходу признака экстремума блока выделения экстремумов, первый и второй тактовые входы и второй

вход задания режима блока управления подключены соответственно к прямому и инверсному выходам генератора так- ,товых импульсов и к выходу блока выделения полных циклов, первый и второй выходы блока управления соединены соответственно с входом запуска аналого-цифрового преобразователя и вторым тактовым входом блока выделения экстремумов, вход начальной уста5

0

5

ным входом блока реверсивных регистров сдвига и подключен к третьему выходу блока управления, четвертый, пятый и шестой выходы которого соединены соответственно с первым и вторым входами задания признака сдвига блока реверсивных регистров сдвига, первая группа информационных выходов которого является выходом предпоследнего значения экстремума устройства, первый информационный выход блока реверсивных регистров сдвига соединен с первым информационным входом блока выделения полных циклов, второй информационный вход которого соединен с вторым информационным выходом блока реверсивных регистров сдвига, вторая группа информационных выходов которого соединена с первой группой информационных входов блока выделения полных циклов и является выходом значения экстремума устройства, второй информационный вход блока реверсивных регистров сдвига соединен с выходом типа экстремума блока выделения экстремумов, группа выходов значения экстремума которого соединена с второй группой информационных входов и группой информационных входов соответственно блока выделения полных циклов и блока реверсивных регистров сдвига.

2. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что блок выделения 5 экстремумов содержит первый, второй и третий регистры, элемент задержки, схему сравнения, элемент И, элемент ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом признака

0

5

0

13306

экстремума блока, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ объединен с первым входом элемента И, подключен к ныходу первого регистра и является выходом , типа экстремума блока, инф ормационный вход первого регистра объединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и подключен к выходу элемента ИЛИ, первый вход которого соединен с выхо-ю дом элемента И, второй вход - с выходом Равно схемы сравнения, выход Меньше которой подключен к второму входу элемента И, первый вход схемы сравнения соединен с выходом второго 15 регистра и является группой выходов Значение экстремума блока, второй вход схемы сравнения объединен с Информационным входом второго регистра и подключен к выходу третьего регист-20 ра, информационный вход которого является информационным входом блока, тактовый вход третьего регистра яв3. Устройст1:о по II. 1 , о т л и ч а ю щ е е с я , что блок выделения полных циклов содержит три элемента И, три элемента ИЛИ, элемент НЕ и , схему сравнения кодов, первая и вторая группы входов которой являются соответственно первой и второй группами информационных входов блока, выходы Больше, Равно и Меньше схемы сравнения соединены соответственно с первым входом первого элемента ИЛИ, с вторым входом первого и первым входом второго элемента ИЛИ и с вторым входом второго элемента ИЛИ, выход которого подключен к первому входу первого элемента И, йыход которого соединен с первым входом третьего элемента ИЛИ, выход которог подключен к первому входу второго элемента И, выход которого является выходом блока, а второй вход второго элемента И является первым информационным входом блока, второй вход

ляется первым тактовым входом блока, а входы сброса всех регистров объеди- ь третьего элемента ИЛИ соединен с вы- нены и являются входом сброса блока, ходом третьего элемента И, первьгй тактовый вход второго регистра соединен с выходом элемента задержки, вход которого объединен с тактовым входом

вторым 30

первого регистра и является тактовым входом блока.

вход которого соединен с выходом первого элемента ИЛИ, второй вход третьего элемента И объединен с входом элемента НЕ и является вторым информационным входом блока.

фае I

10

3. Устройст1:о по II. 1 , о т л и ч а ю щ е е с я , что блок выделения полных циклов содержит три элемента И, три элемента ИЛИ, элемент НЕ и , схему сравнения кодов, первая и вторая группы входов которой являются соответственно первой и второй группами информационных входов блока, выходы Больше, Равно и Меньше схемы сравнения соединены соответственно с первым входом первого элемента ИЛИ, с вторым входом первого и первым входом второго элемента ИЛИ и с вторым входом второго элемента ИЛИ, выход которого подключен к первому входу первого элемента И, йыход которого соединен с первым входом третьего элемента ИЛИ, выход которог подключен к первому входу второго элемента И, выход которого является выходом блока, а второй вход второго элемента И является первым информационным входом блока, второй вход

третьего элемента ИЛИ соединен с вы- ходом третьего элемента И, первьгй

третьего элемента ИЛИ соединен с вы- ходом третьего элемента И, первьгй

вход которого соединен с выходом первого элемента ИЛИ, второй вход третьего элемента И объединен с входом элемента НЕ и является вторым информационным входом блока.

t.J dj, t,gtg,f,,g, К t

ери 8.6

JOS

fur7

Df25 tS67S9fO

S9fO

)

4б,,/,,

10000000000

I о о о о о о о о

1 о о о о 0000 1 о о 1 00000 1 о /|0 0000 I о 0000 о о о

f 00000 1 о о

t00ороо о ( о о

t 0 о 00 000100

1100

) о о о I о о f t о о а о 1 о о

f / 0 00 о f 0100

I f f о 0100 1 1 1 о о о 1 о 1 о о

/ jrt/ о i о о t / ofo0000 too

1 I о 00 о i о о f 1 о 00 о о о /fojO

/ о о о о о о I о

I о о ОО о 010

lOOIOO OOOlO

100 t 00 00 о

f о 0 1000001 О

to 00 о о о i о tooooooooio

(fJuf9

Редактор М.Келемеш

Составитель Э.Сечина Техред Л.Сердюкова

Заказ 3584/51 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(pufW

Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Статистический анализатор | 1979 |

|

SU875388A1 |

| Цифровой фильтр | 1983 |

|

SU1249536A1 |

| ИЗМЕРИТЕЛЬ ГРУППОВОГО ВРЕМЕНИ ЗАПАЗДЫВАНИЯ | 2003 |

|

RU2255343C2 |

| Устройство для обработки и регистрации сигналов | 1987 |

|

SU1458845A1 |

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

| Аналого-цифровой анализатор спектра | 1988 |

|

SU1636787A1 |

Изобретение относится к вычислительной технике для статистических .исследований, в частности к обработке случайных сигналов механических напряжений усталостных повреждений деталей машин. Целью изобретения является повышение быстродействия при высоких требованиях к точности определения параметров. Устройство содержит датчик 15 механических напряжений, усилитель 16,аналого-цифровой преобразователь 17, блок 18 выделения экстремумов, блок 22 выделения полных циклов, генератор 19 тактовых импульсов, блок 23 регистрации, введены блок 21 реверсивных регистров сдвига и управляющий автомат 20. Поиск полных циклов в реализации сигнала механических напряжений выполняется не после взятия очередного отсчета, а лишь после обнаружения и измерения очередного экстремума в реализации или после обнаружения и регистрации полного цикла и исключения из последовательности экстремумов тех, которые определяют параметры полного цикла. Поиск полных циклов осуществляется оптимальным по числу операций способом. 2 з.п. ф-лы, 10 ил. (Л 00 00 о а 00 О) дзиг.з

| Смесь для приготовления образца для рентгеноспектрального определения примесей в электрокорунде | 1986 |

|

SU1374107A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ИЗВЛЕЧЕНИЯ БОРТОВЫХ КОЛЕЦ ИЗ АВТОПОКРЫШКИ | 2003 |

|

RU2225789C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-15—Публикация

1985-04-19—Подача