Изобретение относится к электроизмерительной технике и предназначено для выделения повторяющихся сигналов из шума, моменты появления которых распределены во времени случай- ным образом, и может быть использовано в биологии, медицине для анализа электроэнцефалограмм, диагностики в системах технологического контроля, автоматического управления и др. областях.

Цель изобретения - повьшение достоверности диагностических оценок исследуемых сигналов на фоне шумов, моменты появления которых распределены случайным образом..

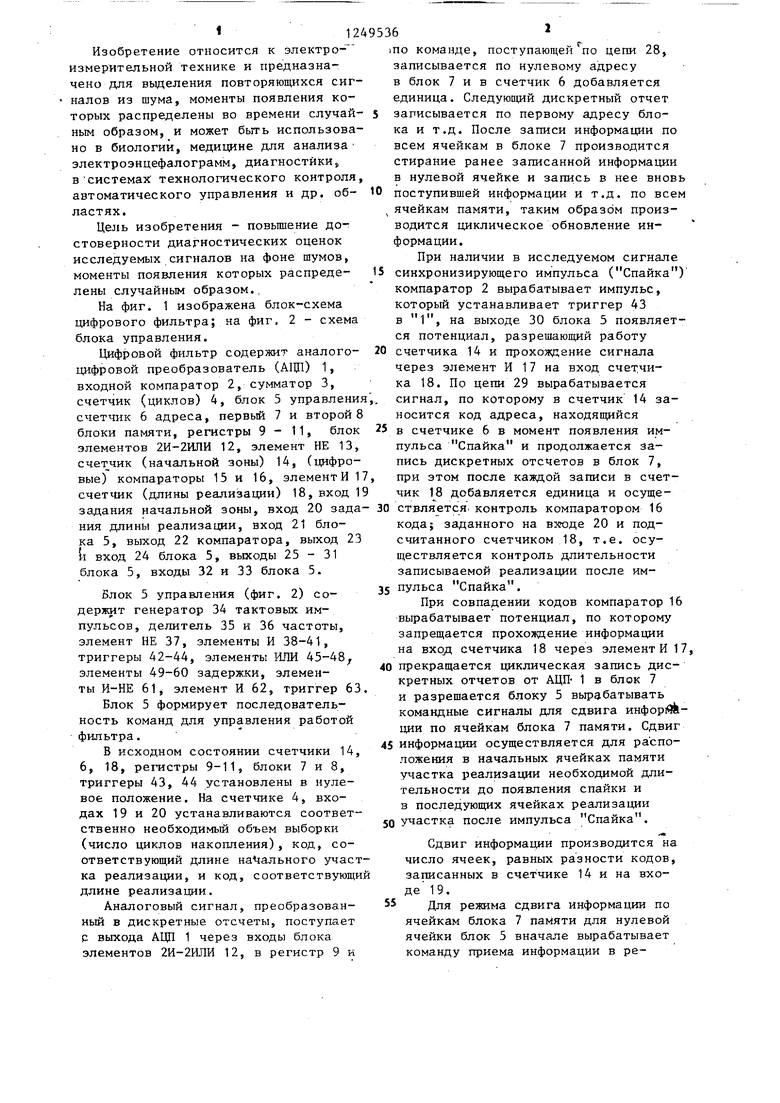

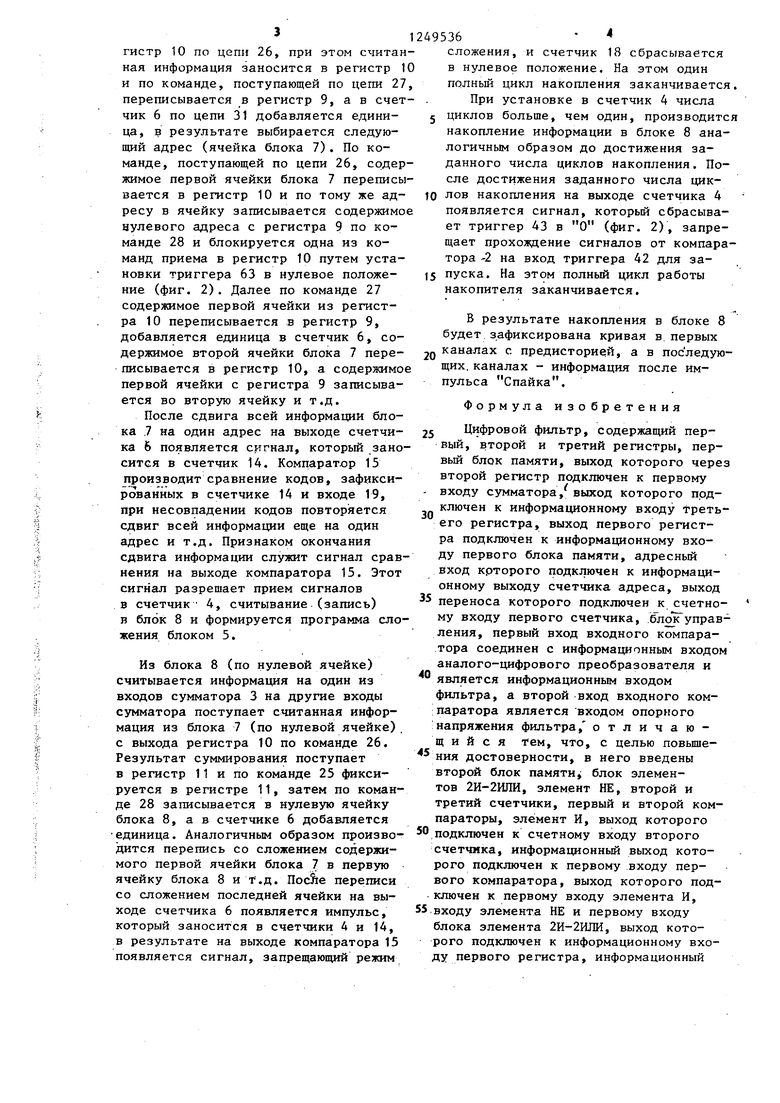

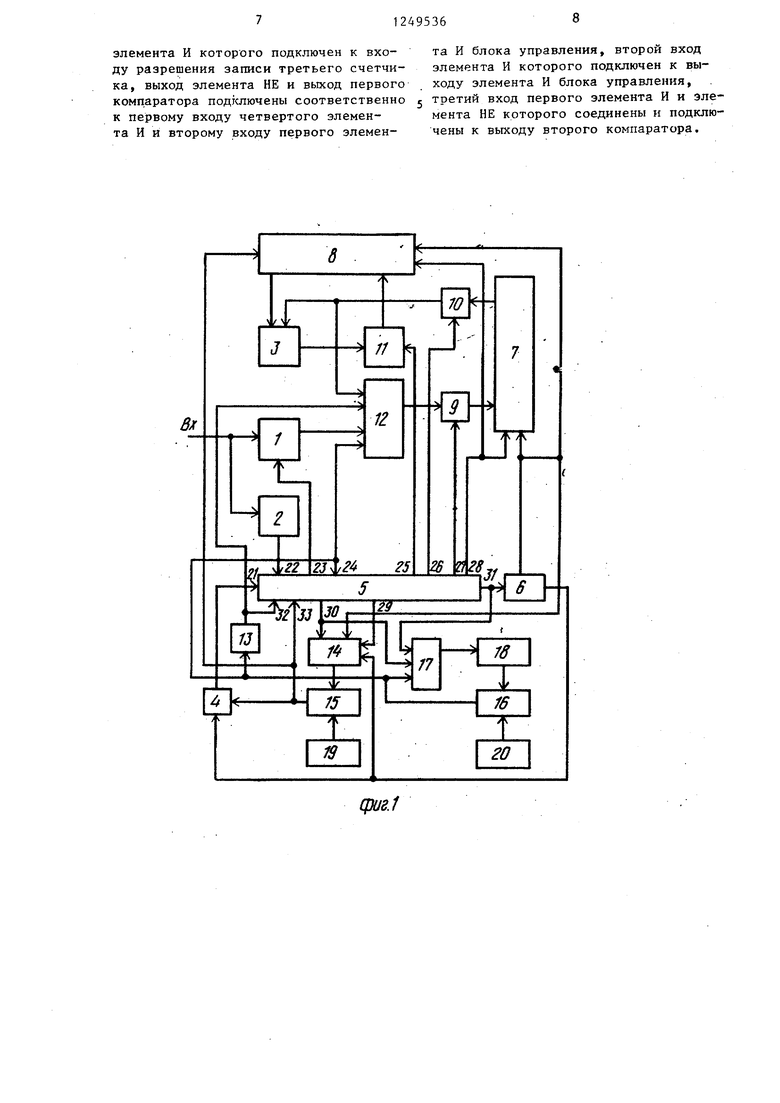

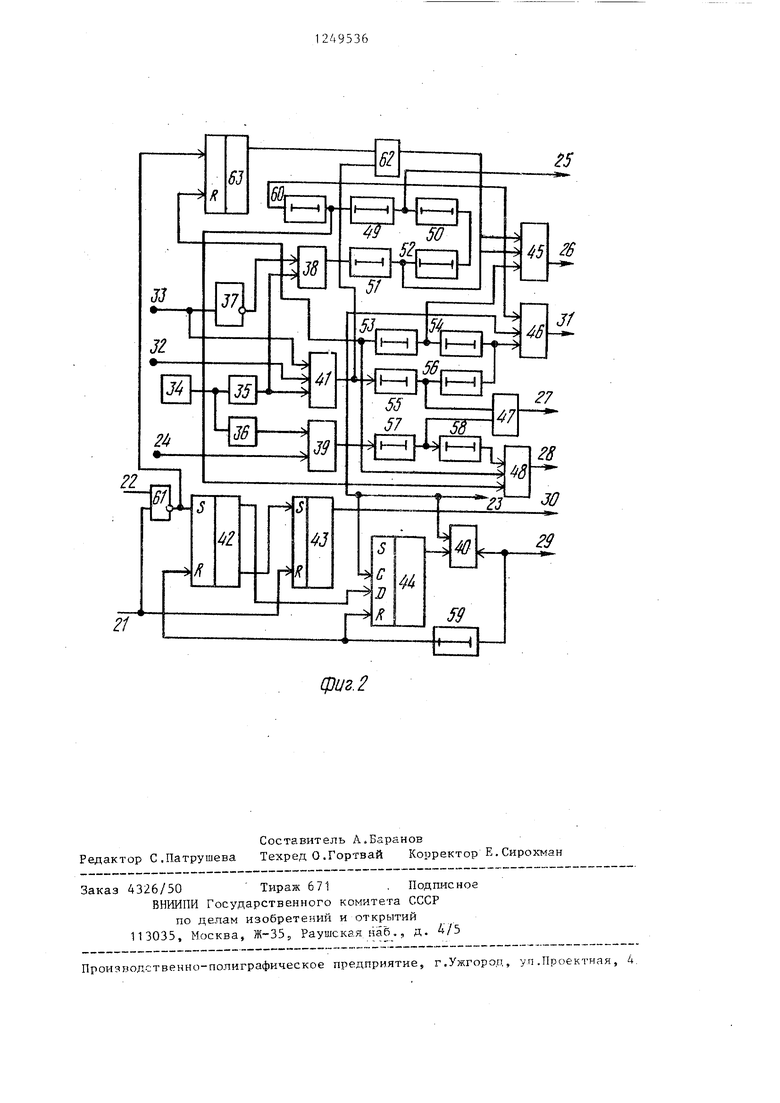

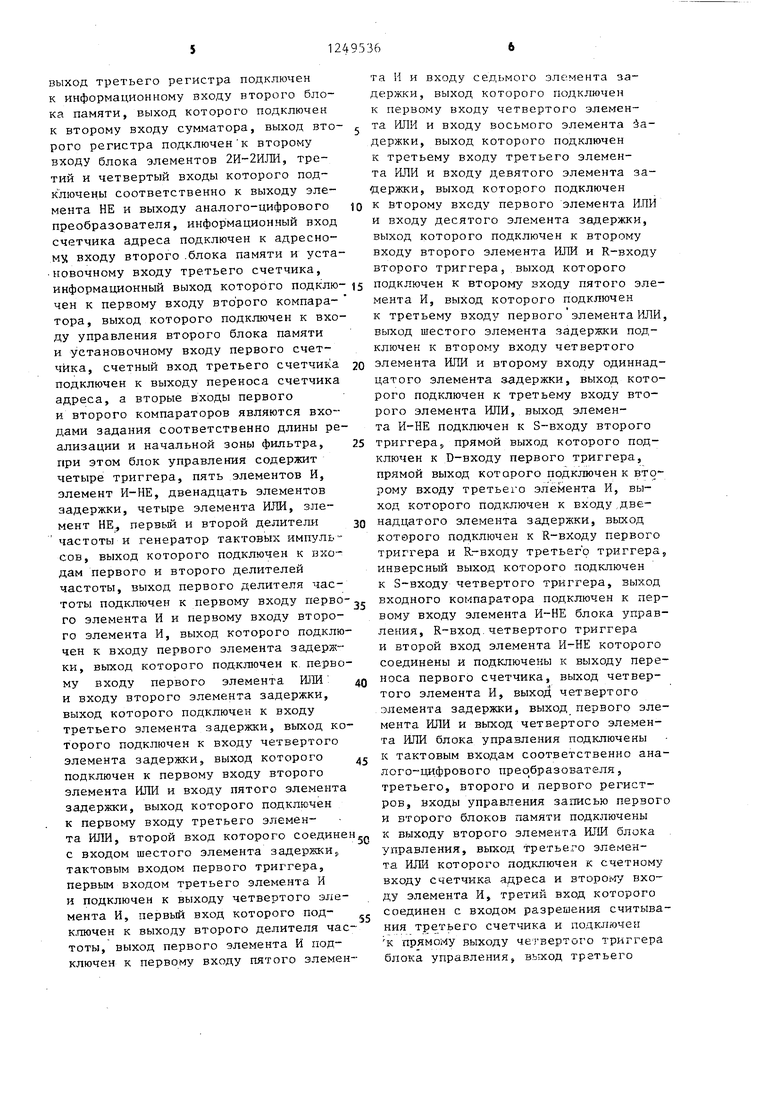

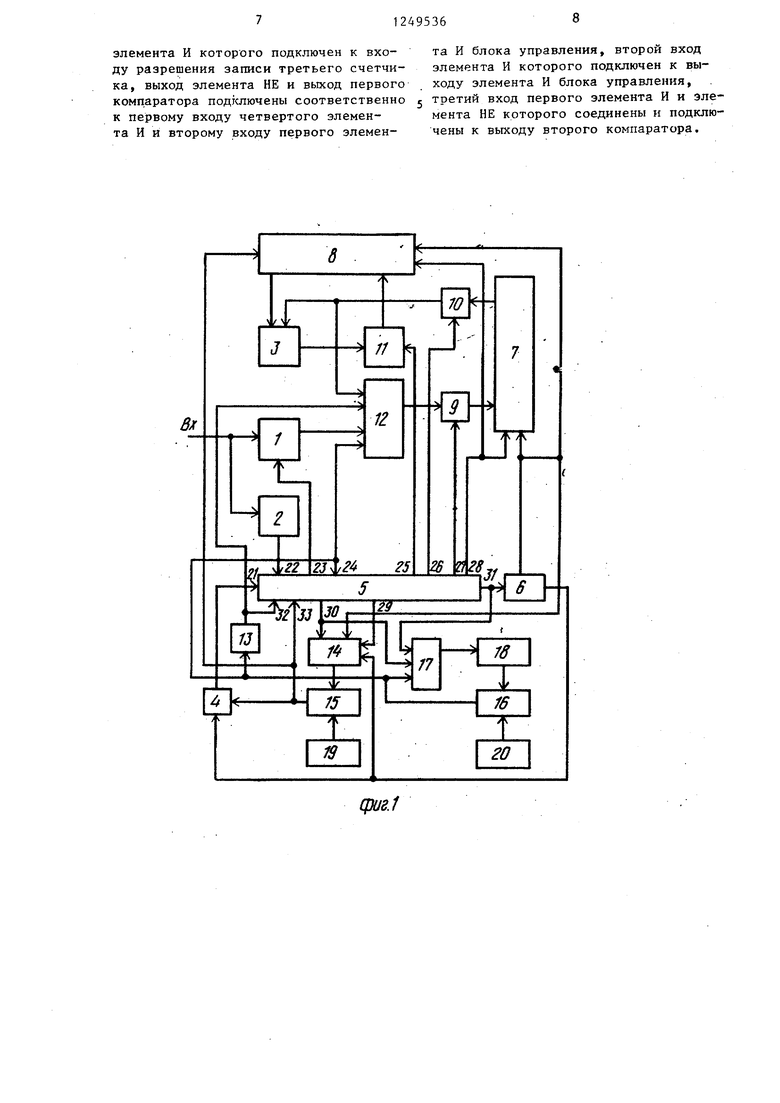

На фиг. 1 изображена блок-схема цифрового фильтра; на фиг, 2 - схема блока управления.

Цифровой фильтр содержит аналого- цифровой преобразователь (АЦП) 1, входной компаратор 2, сумматор 3, счетчик (циклов) 4, блок 5 управления счетчик 6 адреса, первый 7 и второй 8 блоки памяти, регистры 9-11, блок элементов 2И-2Ш1И 12, элемент НЕ 13, счетчик (начальной зоны) 14, (цифровые) компараторы 15 и 16, элемент И 17 счетчик (длины реализации) 18, вход 19

задания начальной зоны, вход 20 зада- 30 ствляется. контроль компаратором 16

ния длины реализации, вход 21 блока 5, выход 22 компаратора, выход 23 {i вход 24 блока 5, выходы 25-31 блока 5, входы 32 и 33 блока 5.

Блок 5 управления (фиг. 2) содержит генератор 34 тактовых импульсов, делитель 35 и 36 частоты, элемент НЕ 37, элементы И 38-41, триггеры 42-44, элементы ИЛИ 45-48 элементы 49-60 задержки, элементы И-НЕ 61, элемент И 62, триггер 63.

Блок 5 формирует последовательность команд для управления работой фильтра.

В исходном состоянии счетчики 14, 6, 18, регистры 9-11, блоки 7 и 8, триггеры 43, 44 установлены в нулевое положение. На счетчике 4, входах 19 и 20 устанавливаются соответственно необходимый объем выборки (число циклов накопления), код, соответствующий длине на 1ального участка реализации, и код, соответствующий длине реализации.

Аналоговый сигнал, преобразованный в дискретные отсчеты, поступает С выхода АЦП 1 через входы блока элементов 2И-2ИЛИ 12, в регистр 9 и

кода; заданного на входе 20 и подсчитанного счетчиком 18, т.е. осуществляется контроль длительности записываемой реализации после им35 пульса Спайка.

При совпадении кодов компаратор вырабатывает потенциал, по которому запрещается прохождение информации на вход счетчика 18 через элемент И

40 прекращается циклическая запись дис кретных отчетов от АЦП- 1 в блок 7 и разрешается блоку 5 вьфабатывать командные сигналы для сдвига инфорЙ ции по ячейкам блока 7 памяти. Сдви

45 информации осуществляется для распо ложения в начальных ячейках памяти участка реализации необходимой длительности до появления спайки и в последующих ячейках реализации

50 участка после импульса Спайка.

Сдвиг информации производится н число ячеек, равных разности кодов записанных в счетчике 14 и на входе 19.

55 Для режима сдвига информации по ячейкам блока 7 памяти для нулевой ячейки блок 5 вначале вырабатывает команду приема информации в ре

1ПО команде, поступающей по цепи 28, записывается по нулевому адресу в блок 7 и в счетчик 6 добавляется единица. Следуюищй дискретный отчет записывается по первому адресу блока и т.д. После записи информации по всем ячейкам в блоке 7 производится стирание ранее записанной информации в нулевой ячейке и запись в нее вновь поступившей информации и т.д. по всем ячейкам памяти, таким образом производится циклическое обновление информации.

При наличии в исследуемом сигнале синхронизирующего импульса (Спайка) компаратор 2 вырабатывает импульс, который устанавливает триггер 43 в 1, на выходе 30 блока 5 появляется потенциал, разрешающий работу счетчика 14 и прохождение сигнала через элемент И 17 на вход счетчика 18. По цепи 29 вырабатывается сигнал, по которому в счетчик 14 заносится код адреса, находящийся в счетчике 6 в момент появления им

пульса Спайка и продолжается запись дискретных отсчетов в блок 7, при этом после каждой записи в счетчик 18 добавляется единица и осущекода; заданного на входе 20 и подсчитанного счетчиком 18, т.е. осуществляется контроль длительности записываемой реализации после им35 пульса Спайка.

При совпадении кодов компаратор 16 вырабатывает потенциал, по которому запрещается прохождение информации на вход счетчика 18 через элемент И 17

40 прекращается циклическая запись дискретных отчетов от АЦП- 1 в блок 7 и разрешается блоку 5 вьфабатывать командные сигналы для сдвига инфорЙ - ции по ячейкам блока 7 памяти. Сдвиг

45 информации осуществляется для расположения в начальных ячейках памяти участка реализации необходимой длительности до появления спайки и в последующих ячейках реализации

50 участка после импульса Спайка.

Сдвиг информации производится на число ячеек, равных разности кодов, записанных в счетчике 14 и на входе 19.

55 Для режима сдвига информации по ячейкам блока 7 памяти для нулевой ячейки блок 5 вначале вырабатывает команду приема информации в ре3

гистр 10 по цепи 26, при этом считанная информация заносится в регистр 1 и по команде, поступающей по цепи 27 переписывается в регистр 9, а в счетчик 6 по цепи 31 добавляется единица, в результате выбирается следующий адрес (ячейка блока 7). По команде, поступающей по цепи 26, содержимое первой ячейки блока 7 переписывается в регистр 10 и по тому же адресу в ячейку записывается содержимо нулевого адреса с регистра 9 по команде 28 и блокируется одна из команд приема в регистр 10 путем установки триггера 63 в нулевое положение (фиг. 2). Далее по команде 27 содержимое первой ячейки из регистра 10 переписывается в регистр 9, добавляется единица в счетчик 6, содержимое второй ячейки блока 7 переписывается в регистр 10, а содержимо первой ячейки с регистра 9 записывается во вторую ячейку и т.д.

После сдвига всей информации блока .7 на один адрес на выходе счетчика 6 появляется сигнал, который заносится в счетчик 14. Компаратхэр 15 троизводит сравнение кодов, зафиксированных в счетчике 14 и входе 19, при несовпадении кодов повторяется сдвиг всей информации еще на один адрес и т.д. Признаком окончания сдвига информации служит сигнал сравнения на выходе компаратора 15. Этот сигнал разрещает прием сигналов в счетчик 4, считывание (запись) в блок 8 и формируется программа сложения блоком 5.

Из блока 8 (по нулевой ячейке) считывается информация на один из входов сумматора 3 на другие входы сумматора поступает считанная информация из блока 7 (по нулевой ячейке). с выхода регистра 10 по команде 26. Результат суммирования поступает в регистр 11 и по команде 25 фиксируется в регистре 11, затем по команде 28 записывается в нулевую ячейку блока 8, а в счетчике 6 добавляется единица. Аналогичным образом производится перепись со сложением содержимого первой ячейки блока 7 в первую ячейку блока 8 и т.д. UocSie переписи со сложением последней ячейки на выходе счетчика 6 появляется импульс, который заносится в счетчики 4 и 14, в результате на выходе компаратора 15 появляется сигнал, запрещающий режим

49536 -

сложения, и счетчик 18 сбрасывается в нулевое положение. На этом один полньй цикл накопления заканчивается. При установке в счетчик 4 числа

5 циклов больше, чем один, производится накопление информации в блоке 8 аналогичным образом до достижения заданного числа циклов накопления. После достижения заданного числа цикto лов накопления на выходе счетчика 4 появляется сигнал, который сбрасывает триггер 43 в О (фиг. 2), запрещает прохождение сигналов от компаратора -2 на вход триггера 42 для заJ5 пуска. На зтом полный цикл работы накопителя заканчивается.

В результате накопления в блоке 8 будет зафиксирована кривая в первых 2Q каналах с предисторией, а в последующих, каналах - информация после импульса Спайка.

Формула изобретения

25 Цифровой фильтр, содержащий первый, второй и третий регистры, первый блок памяти, выход которого через второй регистр подключен к первому

- входу сумматора, выход которого прд30

ключен к информационному входу третьего регистра, выход первого регистра подключен к информационному входу первого блока памяти, адресный вход крторого подключен к информационному выходу счетчика адреса, выход

переноса которого подключен к счетному входу первого счетчика, 1бло1Гуправ- ления, первый вход входного компаратора соединен с информационным входом аналого-цифрового преобразователя и

является информационным входом

фильтра, а второй вход входного компаратора является входом опорного напряжения фильтра, отличающий с я тем, что, с целью повыше кия достоверности, в него введены второй блок памяти блок элементов 2И-2Ш1И, элемент НЕ, второй и третий счетчики, первый и второй компараторы, элемент И, выход которого

50

подключен к счетному входу второго

счетчика, информационный выход которого подключен к первому входу первого компаратора, выход которого подключен к первому входу элемента И, 55.входу элемента НЕ и первому входу блока элемента 2И-2ИЛИ, выход которого подключен к информационному входу первого регистра, информационный

выход третьего регистра подключен к информационному входу второго блока памяти, выход которого подключен к второму входу сумматора, выход вто- рого регистра подключен к второму входу блока элементов , третий и четвертый входы которого подключены соответственно к выходу элемента НЕ и выходу аналого-цифрового преобразователя, информационный вход счетчика адреса подключен к адресному входу второго .блока памяти и уста- новочному входу третьего счетчика, информационный выход которого подклю- чен к первому входу второго компара- тора, выход которого подключен к входу управления второго блока памяти и установочному входу первого счетчика, счетный вход третьего счетчика подключен к выходу переноса счетчика адреса, а вторые входы первого и второго компараторов являются входами задания соответственно длины реализации и начальной зоны фильтра, при этом блок управления содержит четыре триггера, пять элементов И, элемент И-НЕ, двенадцать элементов задержки, четыре элемента ИЛИ, элемент НЕ,, первьм и второй делители частоты и генератор тактовых импульсов, выход которого подключен к входам первого и второго делителей частоты, выход первого делителя частоты подключен к первому входу перво го элемента И и первому входу второго элемента И, выход которого подключен к входу первого элемента задержки, выход которого подключен к первому входу первого элемента ИЛИ и входу второго элемента задержки, выход которого подключен к входу третьего элемента задержки, выход которого подключен к входу четвертого элемента задержки, выход которого подключен к первому входу второго элемента ИЛИ и входу пятого элемента задержки, выход которого подключен к первому входу третьего элемента ИЛИ, второй вход которого соедине с входом шестого элемента задержки тактовым входом первого триггера, первым входом третьего элемента И и подключен к выходу четвертого элемента И, первый вход которого под- к.шочен к выходу второго делителя частоты, выход первого элемента И подключен к первому входу пятого элемента И и входу седьмого элемента задержки, выход которого подключен к первому входу четвертого элемента ИЛИ и входу восьмого элемента Задержки, выход которого подключен к третьему входу третьего элемента ИЛИ и входу девятого элемента задержки, выход которого подключен к второму вхеду первого элемента ИЛИ и входу десятого элемента задержки, выход которого подключен к второму входу второго элемента ИЛИ и R-входу второго триггера, выход которого подключен к второму входу пятого элемента И, выход которого подключен к третьему входу первого элемента ИЛИ выход шестого элемента задержки подключен к второму входу четвертого элемента ИЛИ и второму входу одиннадцатого элемента задержки, выход которого подключен к третьему входу второго элемента ИЛИ, выход элемента И-НЕ подключен к S-входу второго триггера, прямой выход которого подключен к D-входу первого триггера, прямой выход которого подключен к второму входу третьего элемента И, выход которого подключен к входу „двенадцатого элемента задержки, выход котерого подключен к R-входу первого триггера и Н.-входу третьего триггера инверсный выход которого подключен к S-входу четвертого триггера, выход входного компаратора подключен к первому входу элемента И-НЕ блока управления, R-вход.четвертого триггера и второй вход элемента И-НЕ которого соединены и подключены к выходу переноса первого счетчика, выход четвертого элемента И, выхоД четвертого элемента задержки, выход первого элемента ИЛИ и выход четвертого элемента ИЛИ блока управления подключены к тактовым входам соответственно аналого-цифрового преобразователя, третьего, второго и первого регистров, входы управления записью первого и второго блоков памяти подключены к выходу второго элемента ИЛИ блока управления, выход третьего элемента ИЛИ которого подключен к счетному входу счетчика адреса и второму входу элемента И, третий вход которого соединен с входом разрешения считывания третьего счетчика и подключен к прямому выходу четвертого триггера блока управления, вьжод третьего

элемента И которого подключен к входу разрешения записи третьего счетчика, выход элемента НЕ и выход первого компаратора подтшючены соответственно к первому входу четвертого элемента И и второму входу первого элемента И блока управления, второй вход элемента И которого подключен к выходу элемента И блока управления, третий вход первого элемента И и элемента НЕ которого соединены и подключены к выходу второго компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Устройство для приема и передачи информации | 1991 |

|

SU1833871A1 |

| Логический анализатор | 1981 |

|

SU1032457A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для отображения информации | 1986 |

|

SU1319072A1 |

| Устройство для информационного поиска | 1988 |

|

SU1587543A2 |

.Изобретение относится к электроизмерительной технике и предназначено для вьделения повторяющихся сигналов из шума, моменты появления которых распределены во времени случай- лым образом. Цель изобретения - повышение достоверности диагностических оценок исследуемых сигналов на фоне шумов, моменты появления которых распределены случайнь образом. Цифровой фильтр содержит аналого-цифровой преобразователь, компараторы, сумматор, счетчики, блоки памяти, регистры, блок элементов 2И-2ИЛИ, элемент НЕ, элемент И, блок управления. 2 ил. Q S л

фив.2

| Труды института инженеров по электронике и рг диотехнике, 1977, т.65, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Приборы и системы вычислительной техники для регистрации и обработки информации в биологии и медицине | |||

| Ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1986-08-07—Публикация

1983-12-30—Подача