Изобретение относится к измерительной технике и приборостроению и предназначено для измерения скорости в системах контроля управления.

Цель изобретения - уменьшение погрешности измерения скорости за счет снижения методической погрешности, обусловленной несинхронностью .импульсов датчика и генератора, а также за счет уменьшения запаздывания в канале обратной связи по скорости.

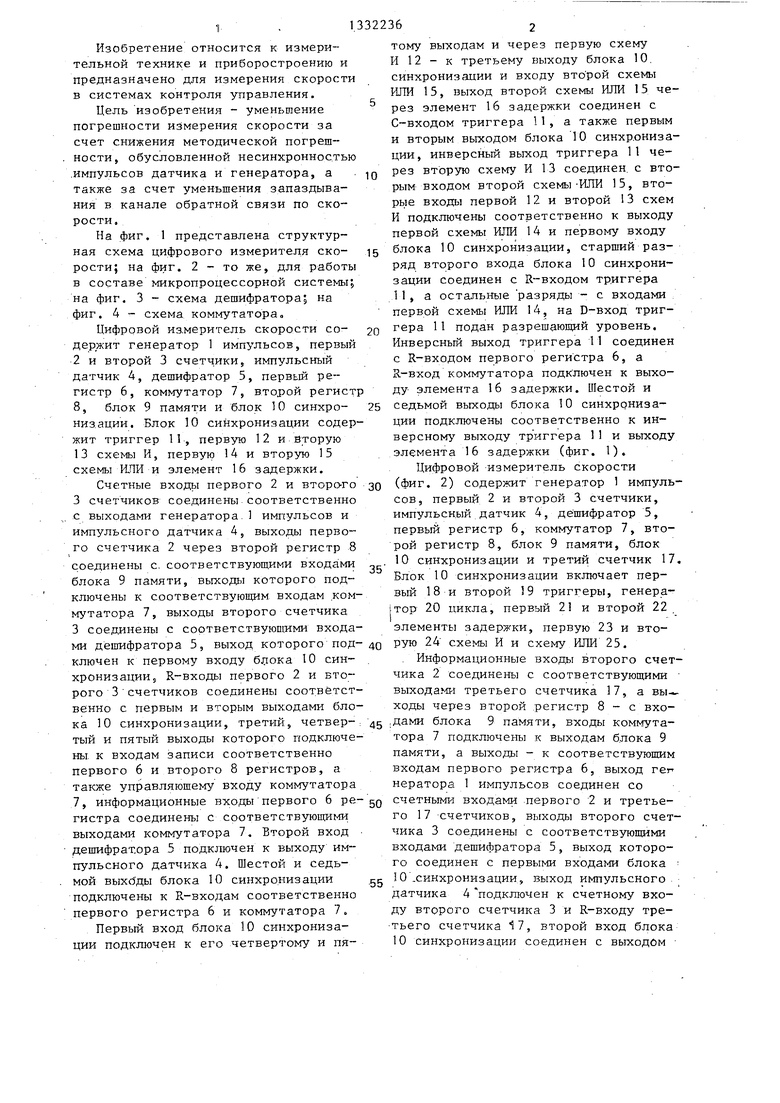

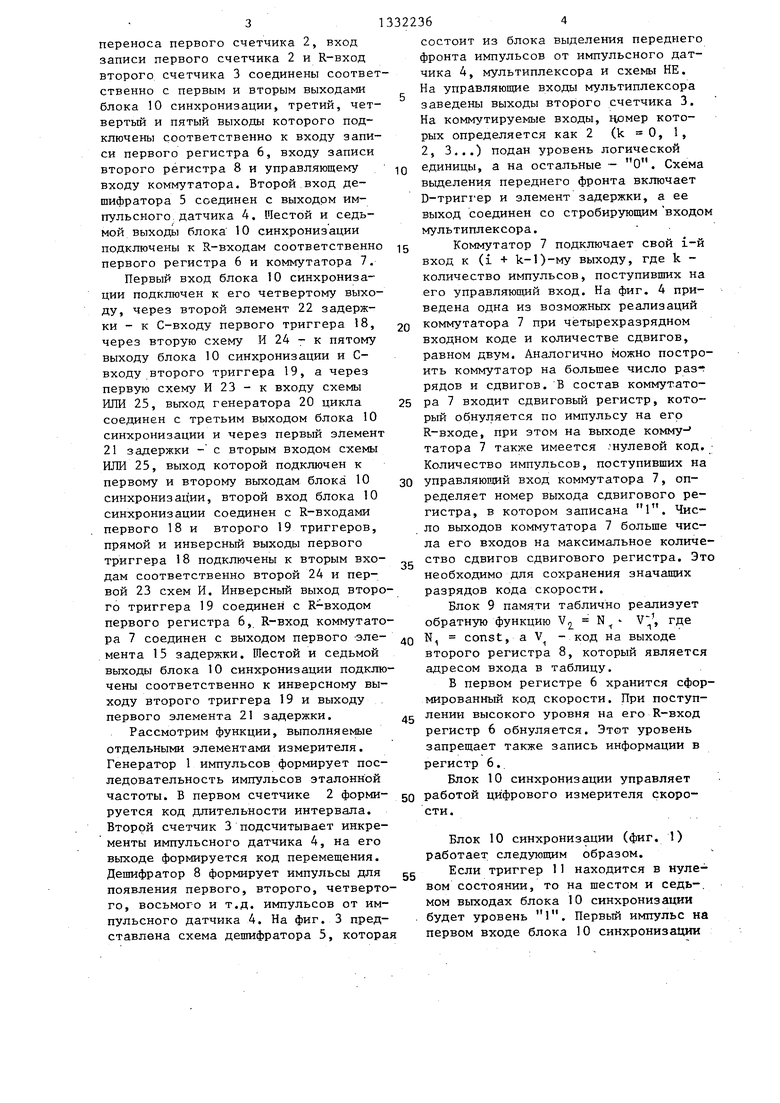

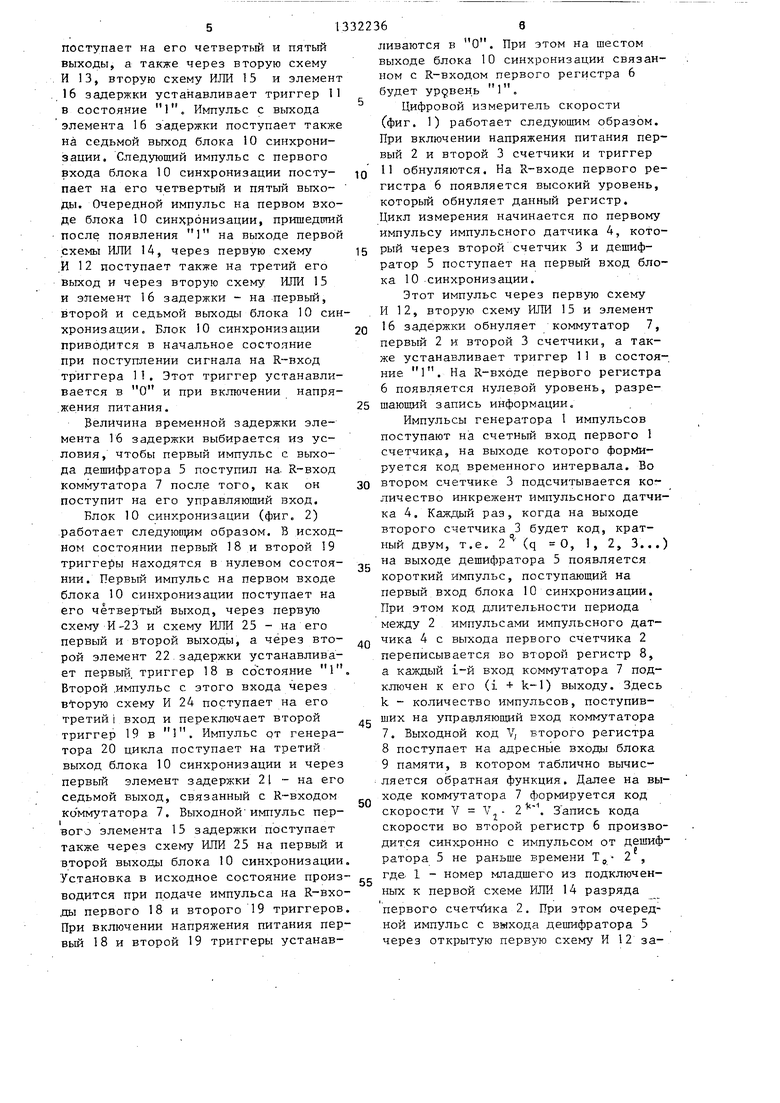

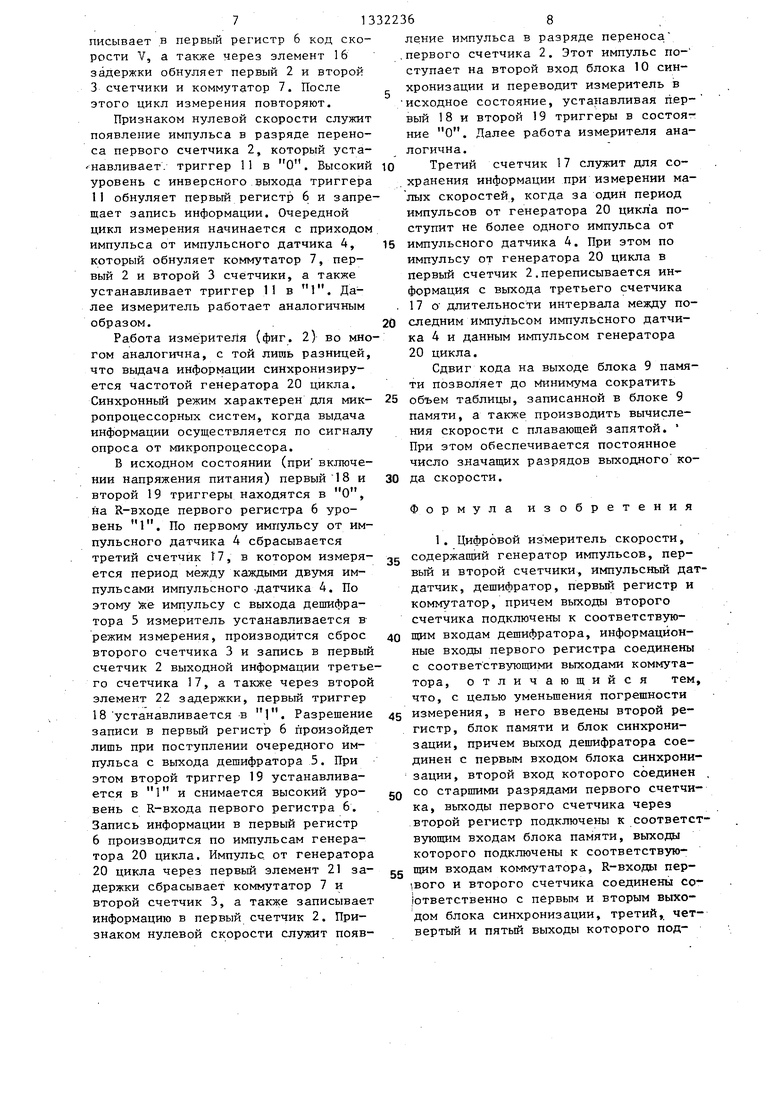

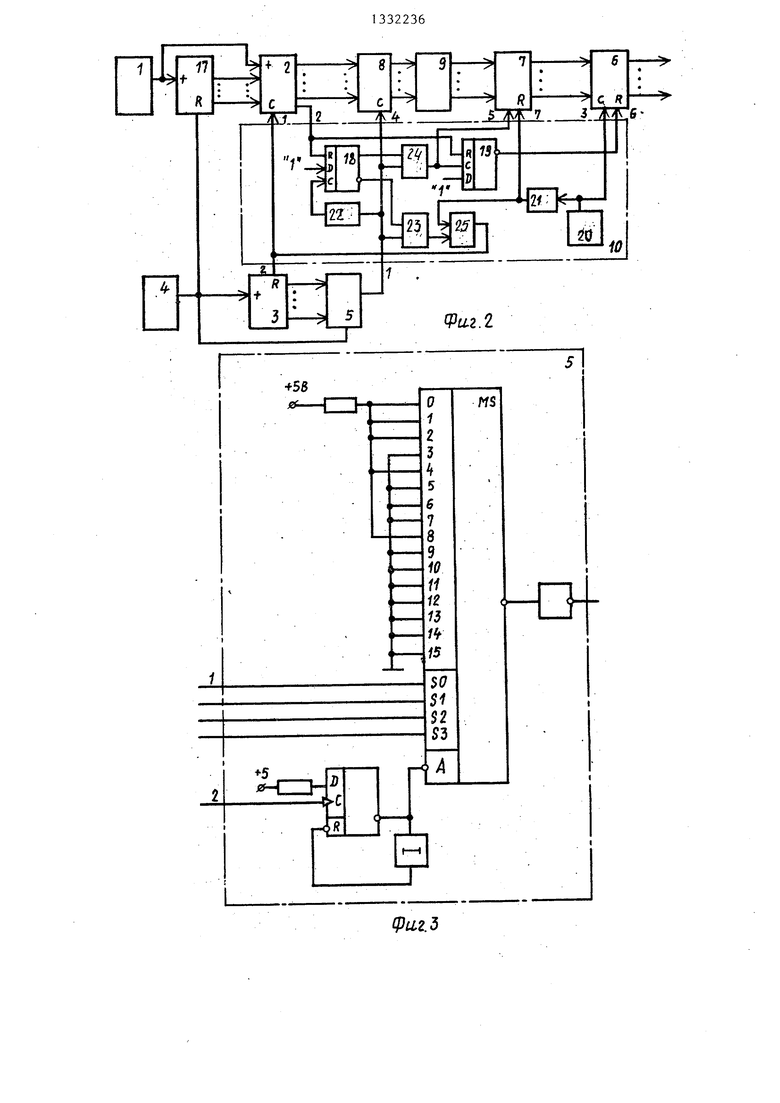

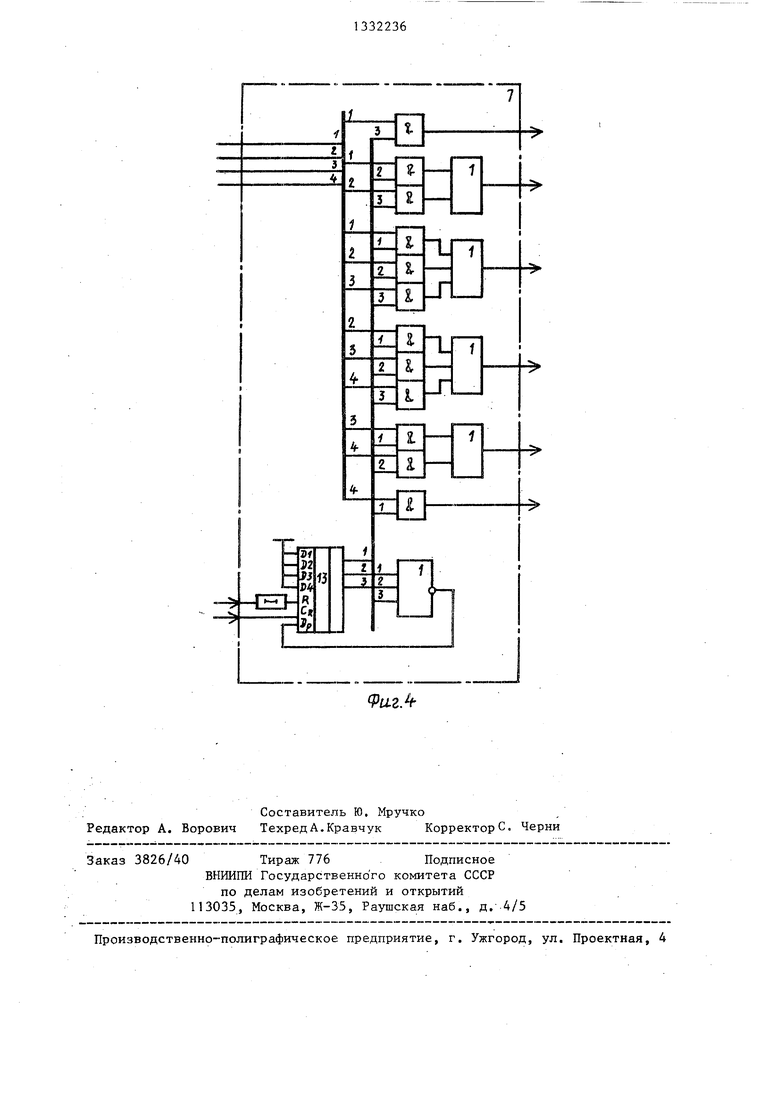

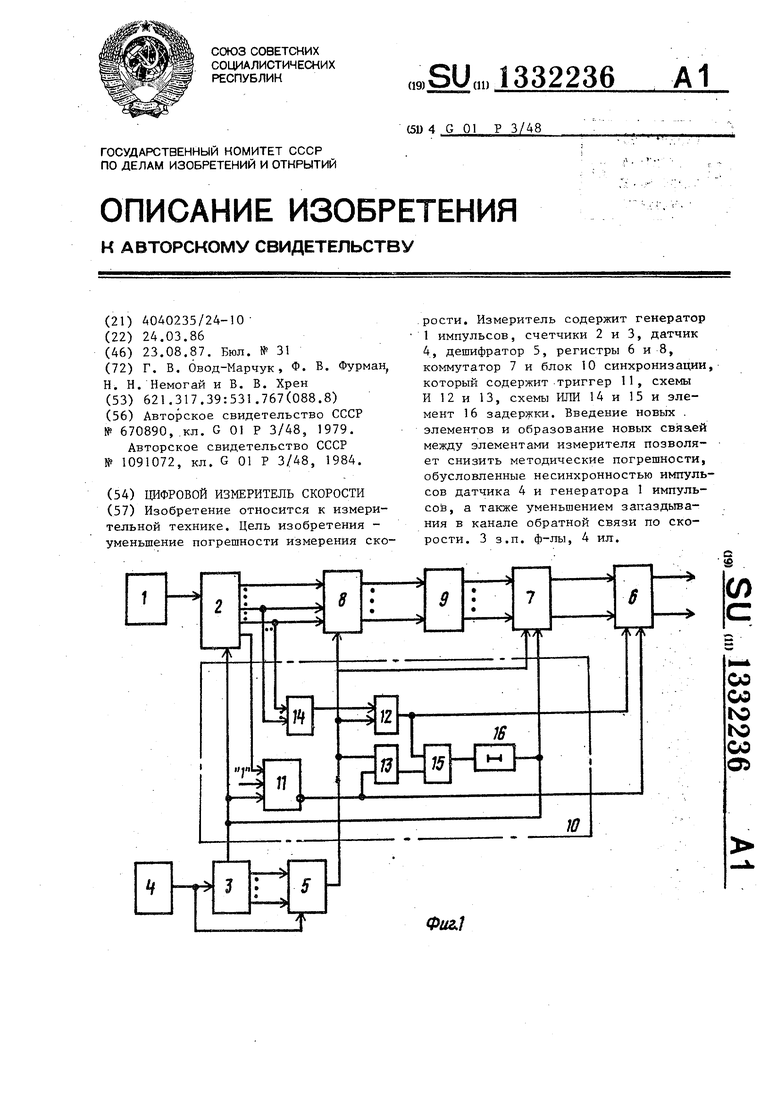

На фиг. 1 представлена структурная схема цифрового измерителя скорости; на фиг. 2 - то же, для работы в составе микропроцессорной системьц на фиг. 3 - схема дешифратора на фиг. 4 - схема комг утатора

ЦИФРОВОЙ из.меритель скорости содержит генератор 1 импульсов, первый

2и второй 3 счетчики, импульсный датчик 4, дешифратор 5, первый регистр 6, коммутатор 7, второй регист 8, блок 9 памяти и блок 10 синхро- низации. Блок 10 синхронизации содержит триггер 11, первую 12 и вторую

13 схемы И, первую 14 и вторую 15 схемы ИЛИ и элемент 16 задержки.

Счетные входы первого 2 и второго

3счетчиков соединены соответственно с выходами генератора.1 импульсов и импульсного датчика 4, выходы первого счетчика 2 через второй регистр 8 соединены с. соответствующими входа ми блока 9 памяти, выходы которого подключены к cooтвeтcтвyюшJ м входам коммутатора 7, выходы второго счетчика

3 соединены с соответствующими входа

ми дешифратора 5, выход которого под- 40 РУЮ 24 схемы И и схему ИЛИ 25.

ключен к первому входу 6jioKa 10 синхронизации, R-входы первого 2 и второго 3 счетчиков соединены соот;вётст- венно с первым и вторым выходами блока 10 синхронизации, третий, четвертый и пятый выходы которого подключены, к входам записи соответственно первого 6 и второго 8 регистров, а также управляющему входу коммутатора 7, информационные входы первого 6 ре- гистра соединены с соответствующими выходами коммутатора 7. Второй вход дешифратора 5 подключен к выходу импульсного датчика 4. Шестой и седьмой выхбды блока 10 синхронизации подключены к R.-входам соответственно первого регистра 6 и коммутатора 7. Первый вход блока 10 синхронизации подключен к его четвертому и пя

5

0

5

0

5

тому выходам и через первую схему И 12 - к третьему выходу блока Ю, синхронизации и входу второй схемы ИЛИ 15, выход второй схемы ИЛИ 15 через элемент 16 задержки соединен с С-входом триггера 11, а также первым и вторым выходом блока 10 синхр.ониза- ции, инверсный выход триггера П через вторую схему И 13 соединен, с вторым входом второй схемы-ИЛИ 15, вторые входы первой 12 и второй 13 схем И подключены соответственно к выходу первой схемы ИЛИ 14 и первому входу блока 10 синхронизации, старший разряд второго входа блока 10 синхронизации соединен с R-входом триггера 11, а остальные разряды - с входами первой схемы ИЛИ 14, на D-вход триггера 11 подан разрешаюшз1й уровень. Инверсный выход триггера 11 соединен с R-входом первого регистра 6, а R-вход коммутатора подключен к выходу элемента 16 задержки. Шестой и седьмой выходы блока 10 синхронизации подключены соответственно к инверсному выходу триггера 11 и выходу элемента 16 задержки (фиг. 1).

Цифровой измеритель скорости (фиг. 2) содержит генератор 1 импульсов, первый 2 и второй 3 счетчики, импульсный датчик 4, дешифратор 5, первый регистр 6, коммутатор 7, второй регистр 8, блок 9 памяти, блок 10 синхронизации и третий счетчик 17. Блок 10 синхронизации включает первый 18 и второй 19 триггеры, генера- |тор 20 цикла, первый 21 и второй 22 . элементы задержки, первую 23 и вто5

Q

. Информационные входы второго счетчика 2 соединены с соответствующими выходами третьего счетчика 17, а вы- ходы через второй .регистр 8 - с входами блока 9 памяти, входы коммутатора 7 подключены к выходам б.лока 9 памяти, а выходы - к соответствующим входам первого регистра 6, выход гег- нератора 1 импульсов соединен со счетными входами .первого 2 и третьего 17 счетчиков, выходы второго счетчика 3 соединены с соответствующими входами дешифратора 5, выход которого соединен с первыми входами блока ; g 10 .синхронизации, выход импульсного датчика 4 подключен к счетному входу второго счетчика 3 и R-входу тре- -тьего счетчика 17, второй вход блока 10 синхрониза.ции соединен с выходом

переноса первого счетчика 2, вход записи первого счетчика 2 и R-вход второго счетчика 3 соединены соответственно с первым и вторым выходами блока 10 синхронизации, третий, четвертый и пятый выходы которого под- кпючены соответственно к входу записи первого регистра 6, входу записи второго регистра 8 и управляющему входу коммутатора. Второй вход дешифратора 5 соединен с выходом импульсного датчика 4. Шестой и седьмой выходы блока 10 синхронизации подключены к R-входам соответственно первого регистра 6 и коммутатора 7.

Первый вход блока 10 синхронизации подключен к его четвертому выходу, через второй элемент 22 задержки - к С-входу первого триггера 18, через вторую схему И 24 - к пятому выходу блока 10 синхронизации и С- входу второго триггера 19, а через первую схему И 23 - к входу схемы ИЛИ 25, выход генератора 20 цикла соединен с третьим выходом блока 10 синхронизации и через первый элемент 21 задержки - с вторым входом схемы ИЛИ 25, выход которой подключен к первому и второму выходам блока 10 синхронизации, второй вход блока 10 синхронизации соединен с R-входами первого 18 и второго 19 триггеров, прямой и инверсный выходы первого триггера 18 подключены к вторым входам соответственно второй 24 и первой 23 схем И. Инверсный выход второго триггера 19 соединен с R-входом первого регистра 6, R-вход коммутатора 7 соединен с выходом первого -элемента 15 задержки. Шестой и седьмой выходы блока 10 синхронизации подключены соответственно к инверсному выходу второго триггера 19 и выходу первого элемента 21 задержки.

Рассмотрим функции, выполняемые отдельными элементами измерителя. Генератор 1 импульсов формирует последовательность импульсов эталонной частоты. В первом счетчике 2 формируется код длительности интервала. Второй счетчик 3 подсчитывает инкременты импульсного датчика 4, на его выходе формируется код перемещения. Дешифратор 8 формирует импульсы для появления первого, второго, четвертого, восьмого и т.д. импульсов от импульсного датчика 4. На фиг. 3 представлена схема депгафратора 5, котора

10

15

20

3322364

состоит из блока выделения переднего фронта импульсов от импульсного датчика 4, мультиплексора и схемы НЕ. На управляющие входы мультиплексора заведены выходы второго счетчика 3. На коммутируемые входы, номер которых определяется как 2 (k О, 1, 2, 3...) подан уровень логической единицы, а на остальные - О. Схема вьщеления переднего фронта включает D-триггер и элемент задержки, а ее выход соединен со стробирующим входом мультиплексора.

Коммутатор 7 подключает свой i-й вход к (i + k-l)-My выходу, где k - количество импульсов, поступивших на его управляющий вход. На фиг. 4 приведена одна из возможных реализаций коммутатора 7 при четырехразрядном входном коде и количестве сдвигов, равном двум. Аналогично можно построить коммутатор на большее число раз г рядов и сдвигов. В состав коммутато-

25 ра 7 входит сдвиговый регистр, который обнуляется по импульсу на его R-входе, при этом на выходе комму- татора 7 также имеется .-нулевой код. Количество импульсов, поступивших на управляющий вход коммутатора 7, определяет номер выхода сдвигового регистра, в котором записана 1. Число выходов коммутатора 7 больше числа его входов на максимальное количество сдвигов сдвигового регистра. Это необходимо для сохранения значащих разрядов кода скорости.

Блок 9 памяти таблично реализует обратную функцию V N , где N const, а V - код на выходе второго регистра 8, который является адресом входа в таблицу.

В первом регистре 6 хранится сформированный код скорости. При поступ4g лении высокого уровня на его R-вход регистр 6 обнуляется. Этот уровень запрещает также запись информации в регистр 6.

Блок 10 синхронизации управляет

50 работой цифрового измерителя скорости.

30

35

40

Блок 10 синхронизации (фиг. 1) работает следующим образом.

Если триггер 11 находится в нулевом состоянии, то на шестом и седь-, мом выходах блока 10 синхронизации будет уровень 1. Первый импульс на первом входе блока 10 синхронизации

поступает на его четвертый и пятый выходы, а также через вторую схему И 13, вторую схему ИЛИ 15 и элемент 16 задержки устанавливает триггер 11 в состояние 1. Импульс с выхода элемента 16 задержки поступает также на седьмой выход блока 10 синхронизации. Следующий импульс с первого входа блока 10 синхронизации поступает на его четвертый и пятый выхо- ды. Очередной импульс на первом входе блока 10 синхронизации, пришедший после появления 1 на выходе первой схемы ИЛИ 14, через первую схему .И 12 поступает также на третий его выход и через вторую схему ИЛИ 15 и элемент 16 задержки - на первый, второй и седьмой выходы блока 10 синхронизации. Блок 10 синхронизации приводится в начальное состояние при поступлении сигнала на R-вход триггера 11. Этот триггер устанавливается в О и при включении напряжения питания.

Величина временной задержки элемента 16 задержки выбирается из условия, чтобы первый импульс с выхода дешифратора 5 поступил на R-вход коммутатора 7 после того, как он поступит на его управляющий вход. Блок 10 синхронизации (фиг. 2) работает следуюпщм образом. В исходном состоянии первый 18 и второй 19 триггеры находятся в нулевом состоянии. Первый импульс на первом входе блока 10 синхронизации поступает на его четвертый выход, через первую cxBNTy И-23 и схему ИЛИ 25 - на его первый и второй выходы, а через второй элемент 22.задержки устанавливает первый, триггер 18 в со стояние , Второй .импульс с этого входа через в горую схему И 24 поступает на его третий i вход и переключает второй триггер 19 в 1. Импульс от генератора 20 цикла поступает на третий выход блока 10 синхронизации и через первый элемент задержки 21 - на его седьмой выход, связанный с R-входом ко ммутатора 7. Выходной импульс перого элемента 15 задержки поступает также через схему ИЛИ 25 на первый и второй выходы блока 10 синхронизации. становка в исходное состояние производится при подаче импульса на R-BXO- ы первого 18 и второго 19 триггеров. ри включении напряжения питания цер- ый 18 и второй 19 триггеры устанав0

5

0

5

0

5

0

5

0

5

ливаются в О. При этом на шестом выходе блока 10 синхронизации связанном с R-входом первого регистра 6 будет уровень 1.

Цифровой измеритель скорости (фиг. 1) работает следующим образом. При включении напряжения питания первый 2 и второй 3 счетчики и триггер 11 обнуляются. На R-входе первого регистра 6 появляется высокий уровень, который обнуляет данный регистр. Цикл измерения начинается по первому импульсу импульсного датчика 4, который через второй счетчик 3 и дешифратор 5 поступает на первьш вход блока 10 синхронизации.

Этот импульс через первую схему И 12, вторую схему ИЛИ 15 и элемент 16 задержки обнуляет коммутатор 7, первый 2 и второй 3 счетчики, а также устанавливает триггер 11 в состояние 1. На R-входе первого регистра 6 появляется нулевой уровень, разре- щающий запись информации„

Импульсы генератора I импульсов поступают на счетный вход первого 1 счетчика, на выходе которого формируется код временного интервала. Во втором счетчик€ 3 подсчитывается ко-- личество инкрежент импульсного датчика 4. Каждый раз, когда на выходе второго счетчика 3 будет код, кратный двум, т.е. 2 (q О, 1, 2, 3...) на выходе дешифратора 5 появляется короткий импульс, поступающий на первый вход блока 10 синхронизации. При этом код длительности периода между 2 импульсами импульсного датчика 4 с выхода первого счетчика 2 переписывается во второй регистр 8, а каждый г-й вход коммутатора 7 подключен к его (i + k-l) выходу. Здесь k - количество импульсов, поступивших на управляющий вход коммутатора 7. Выходной код V, второго регистра

8поступает на адресные входы блока

9памяти, в котором таблично вычисляется обратная функция. Далее на выходе коммутатора 7 формируется код скорости V V.- 2 Запись кода скорости во второй регистр 6 производится синхронно с импульсом от дешифратора 5 не раньше времени 2 , где. 1 - номер младшего из подключенных к первой схеме ИЛИ 14 разряда первого счетч ика 2. При этом очередной импульс с выхода дешифратора 5 через открытую первую схему И 12 записывает в первый регистр 6 код скорости V, а также через элемент 16 задержки обнуляет первый 2 и второй 3 счетчики и коммутатор 7. После этого цикл измерения повторяют.

Признаком нулевой скорости служит появление импульса в разряде переноса первого счетчика 2, который уста- навливает. триггер 11 в О. Высокий уровень с инверсного выхода триггера 11 обнуляет первый регистр 6 и запрещает запись информации. Очередной цикл измерения начинается с приходом импульса от импульсного датчика 4, который обнуляет коммутатор 7, первый 2 и второй 3 счётчики, а также устанавливает триггер 11 в 1. Далее измеритель работает аналогичным образом.

Работа измерителя (фиг. 2) во многом аналогична, с той лишь разницей, что выдача информации синхронизируется частотой генератора 20 цикла. Синхронный режим характерен для микропроцессорных систем, когда выдача информации осуществляется по сигналу опроса от микропроцессора.

В исходном состоянии (при включении напряжения питания) первый 18 и второй 19 триггеры находятся в О, на R-входе первого регистра 6 уровень 1. По первому импульсу от импульсного датчика 4 сбрасывается третий счетчик ТУ, в котором измеряется период между каждыми двумя импульсами импульсного .датчика 4. По этому же импульсу с выхода дешифратора 5 измеритель устанавливается в режим измерения, производится сброс второго счетчика 3 и запись в первый счетчик 2 выходной информации третьего счетчика 17, а также через второй элемент 22 задержки, первый триггер 18 устанавливается в |. Разрешение записи в первый регистр 6 произойдет лишь при поступлении очередного импульса с выхода дешифратора 5. При этом второй триггер 19 устанавливается в 1 и снимается высокий уровень с R-входа первого регистра 6. Запись информации в первый регистр 6 производится по импульсам генератора 20 цикла. Импульс от генератора 20 цикла через первый элемент 21 задержки сбрасывает коммутатор 7 и второй счетчик 3, а также записывает информацию в первый счетчик 2. Признаком нулевой скорости служит появление импульса в разряде переноса .первого счетчика 2. Этот импульс по- ступает на второй вход блока 10 синхронизации и переводит измеритель в исходное состояние, устанавливая пер- вый 18 и второй 19 триггеры в состояг ние О. Далее работа измерителя аналогична.

0 Третий счетчик 17 служит для сохранения информации при измерении малых скоростей, когда за один период импульсов от генератора 20 цикл а поступит не более одного импульса от

5 импульсного датчика 4. При этом по импульсу от генератора 20 цикла в первый счетчик 2 .переписывается ин- формация с выхода третьего счетчика . 17 О длительности интервала между по0 следним импульсом импульсного датчика 4 и данным импульсом генератора 20 цикла.

Сдвиг кода на выходе блока 9 памяти позволяет до минимума сократить

5 объем таблицы, записанной в блоке 9 памяти, а также производить вычисления скорости с плавающей запятой. При этом обеспечивается постоянное число значащих разрядов выходного ко0 да скорости.

Формула изобретения

1. Цифровой измеритель скорости,

g содержащий генератор импульсов, первый и второй счетчики, импульсный дат- датчик, дешифратор, первый регистр и коммутатор, причем выходы второго счетчика подключены к соответствую0 Щим входам дешифратора, информационные входы первого регистра соединены с соответствующими выходами коммутатора, отличающийся тем, что, с целью уменьшения погрешности

5 измерения, в него введены второй регистр, блок памяти и блок синхронизации, причем выход дешифратора соединен с первым входом блока синхронизации, второй вход которого соединен ,

Q со старшими разрядами первого счетчика, выходы первого счетчика через второй регистр подключены к соответствующим входам блока памяти, выхода которого подключены к соответствуюg ЩИМ входам коммутатора, R-входы перового и второго счетчика соединены со- |ответственно с первым и вторым выходом блока синхронизации, третий, четвертый и пятый выходы которого под9

ключены к входам записи соответственно первого и второго регистров и управляющему входу коммутатора, счет- ные входы первого и второго счетчиков соединены соответственно с выходами генератора импульсов и импульсного датчика.

2.Измеритель по п. 1, отличающийся тем, что блок синхронизации содержит триггер, первую и вторую схемы И, первую и вторую схему ИЛИ и элемент задержки, причем первый вход блока синхронизации подключен к его четвертому и пятому выходам и через первую схему И - к третьему выходу блока синхронизации и входу второй схемы ИЛИ, выход второй схемы ИЛИ через элемент задержки соединен с С-входом триггера, а также первым и вторым выходами блока синхронизации, инверсный выход триггера через вторую схему И соединен с вторым входом второй схемы ИЛИ, вторые входы первой и второй схем И подключены соответственно к выходу первой схемы ИЛИ и первому входу блока синхронизации, старший разряд второго входа блока синхронизации соединен с R-входом триггера, а остальные разряды - с входами первой схемы ИЛИ.

3.Измеритель по п. 1, отличающийся тем, что, с целью обеспечения сопряжения с микропроцессорными потребителями, в него дополнительно введен третий счетчик, причем выход дешифратора соединен с первым входом блока синхронизации, выход переноса первого счетчика подключен к второму входу блока синхронизации,, а информационные выходы через второй регистр - к соответствуюим входам блока памяти, выход генеатора импульсов соединен со счетныи входами первого и третьего счетчиов, информационные входы первого

133

10

подключены к соответствующим

0

5

0

5

0

5

0

5

писи - к первому выходу блока синхронизации, выходы блока памяти соединены с соответствующими входами коммутатора, управляющий вход которого подключен к пятому выходу блока синхронизации, выход импульсного датчика соединен со счетным входом второго счетчика и R-входом третьего счетчика, второй, третий и четвертый выхог ды блока синхронизации подключены соответственно к Н-входу второго счетчика, входам записи первого и второго регистров.

4. Измеритель по п. 3, -отличающийся тем, что блок синхронизации содержит первый и второй триггеры, генератор цикла, первый и второй элементы задержки, первую и

вторую схемы И и схему ИЛИ, причем

I

первый.вход блока синхронизации подключен к его четвертому выходу, через второй элемент задержки - к С- входу первого триггера, через вторую схему И - к пятому выходу блока синхронизации и С-входу второго триггера, вход первой схемы И соединен с первым входом блока синхронизации, а выход - с входом схемы ИЛИ, выход генератора цикла соединен с третьим выходом блока синхронизации и через первый элемент задержки - с вторым входом схемы ИЛИ, выход которой подключен к первому и второму выходам . блока синхронизации, второй вход блока синхронизации соединен с R- входами первого и второго триггеров, прямой и инверсный выходы первого триггера подключены к вторым входам соответственно второй и первой схем И, инверсный выход второго триггера и выход первого -элемента задержки соединены с R-входами соответственно первого регистра и коммутатора

Фаг.З

Составитель Ю, Мручко Редактор А. Ворович Техред А. Кравчук Корректоре. Черни

Заказ 3826/40 Тираж 776Подписное

ВНИИПИ Государственно го комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ФагЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель скорости для микропроцессорных систем | 1985 |

|

SU1307339A1 |

| Автоматический измеритель импульсной мощности СВЧ радиосигналов | 1985 |

|

SU1287025A1 |

| Устройство для программного управления | 1981 |

|

SU1003020A1 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090840C1 |

| Программируемый контроллер | 1984 |

|

SU1453404A1 |

| Устройство для определения абсолютного положения вала исполнительного механизма | 1988 |

|

SU1781822A1 |

| СПОСОБ ДИСКРЕТНОГО КОНТРОЛЯ РАССТОЯНИЙ ДО ИСТОЧНИКА КОЛЕБАНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2028579C1 |

| Система автоматического пожаротушения | 1987 |

|

SU1461486A1 |

| Система для контроля и управления | 1985 |

|

SU1273932A1 |

| Система адаптивного числового программного управления металлорежущим станком | 1980 |

|

SU954945A1 |

Изобретение относится к измерительной технике. Цель изобретения - уменьшение погрешности измерения скорости. Измеритель содержит генератор 1 импульсов, счетчики 2 и 3, датчик 4, дешифратор 5, регистры 6 и 8, коммутатор 7 и блок 10 синхронизации, который содержит -триггер 11, схемы И 12 и 13, схемы ИЛИ 14 и 15 и элемент 16 задержки. Введение новых . элементов и образование новых свяаей между элементами измерителя позволяет снизить методические погрешности, обусловленные несинхронностью импульсов датчика 4 и генератора 1 импульсов, а также уменьшением запаздьгоа- ния в канале обратной связи по скорости. 3 з.п. ф-лы, 4 ил. (Л с со со к ю оо О5

| Устройство для измерения угловой скорости | 1978 |

|

SU670890A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения угловой скорости | 1982 |

|

SU1091072A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-08-23—Публикация

1986-03-24—Подача