3

с целью повьшения надежности, в него введены второй блок памяти управляющих программ, второй элемент ИЛИ, счетчик, дешифратор, второй триггер и три элемента И, причем выход признака считывания операционного блока подключен .к счетному входу счетчика, вход установки в ноль, первый и второй выходы которого подключены соответственно к выходу формирователя сброса, к первому и второму входам первого элемента И, выход которого подключен к входу установки в единицу второго триггера, вход установки в ноль и выход которого подключены соответственно к выходу формирователя сброса и к первому входу второго элемента И, выход которого подключен к входу считыв анрш первого блока памяти управляющих программ, инверсньш выход второго триггера подключен к первому входу третьего элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход ко торого подключен к входу считывания второго блока памяти управляющих программ, адресньм вход которого подключен через шину адреса к выходу коммутатора и к выходу младших разрядов адреса операдионного блока и соединен с входом дешифратора, выход второго блока памяти управляющих программ подключен, через вторую шину данных к информационному входу операционного блока, первый выход дешифратора подключе: к вторым входам третьего и четвертого элементов И, второй выход дешифратора подключен к второму входу второго элемента ИЖ третий и четвертый выходы дешифратор подключены соответственно к входам выборки блока памяти состояний и блока памяти рабочей программы

2„ Программируемьй контролер по Hoi, отличающийся т€;м, что блок обработки логических условий содержит регистр, пять триггеров четыре дешифратора, формирователь им .пульсов, три одновибратора, мультиплексор, узел двунаправленной передачи данных, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ два элемента И-НЕ,, элемент ИЛИ-НЕ,

двадцать пять элементов И, восемь элементов ИЛИ, две группы элементов И-НЕ, причем первый вход-выход блокз. через шину подключен к ннформациок- ному входу-выходу узла двунаправленной передачи данных, информадионньй

0

5

0

5

0

5

0

5

0

5

выход которого, информационные входы мультиплексора, первые входы элементов И-НЕ первой группы, информацион- НЕлй вход регистра, информационный вход первого дешифратора, входы первого элемента И через шину соединены с вторым входом-выходом блока, выход первого триггера подключен к строби- рующему входу второго дешифратора, К-е выходы третьего и четвертого дешифраторов подключены соответственно к второму входу К-го элемента И-НЕ первой группы и к первому входу К-го элемента И-НЕ второй группы (,..о, М, где М - разрядность шины данных), второй вход и выход которого подключены соответственно к выходу К-го элемента И-НЕ первой группы и к информационному входу К-го разряда узла двунаправленной передачи данных, вход режима записи которого подключен к первому выходу регистра, второй выход которого подключен к первому входу второго элемента И, выходы первого и второго элементов И подключены соответственно к информационному и стробирующему входам первого дешифратора, первый вход блока подключен к тактовому входу формирователя импульсов, второй вход блока подключен к инверсному входу первого элемента И-НЕ, третий вход блока подключен к входам установки в ноль регистра и первого триггера и к первому входу первого элемента ИЛИ, чет- вертьш вход блока подключен к первому входу элемента ИЛИ-НЕ, входу режима чтения узла двунаправленной передачи данных, второму входу второго элемента И, первому входу третьего элемента И, пятый вход блока подключен к второму входу элемента ИЛИ-НЕ, первому входу четвертого элемента И, первому входу пятого элемента И,шестой вход блока подключен к второму входу первого элемента И-НЕ, выход второго дешифратора подключен к первому входу шестого элемента И, седьмой вход блока подключен к информационному входу второго дешифратора, к остальным входам шестого элемента И, информационным входам третьего и четвертого дешифравторов, к второму информационному входу мультиплексора и к третьему входу второго элемента И, четвертый вход блока подключен к первому входу седьмого элемента И, первый выхо;.; блока подключен к выходу первого одновибратора, второй выход блока подключен к выходу второго элемента ИЛИ, третий выход блока подключен к выходу первого элемента И-НЕ и соединен с синхровходом регистра и входом установки в единицу первого триггера, выход второго одновибратора через третий одновибратор подключен к четвертому выходу блока и второму входу четвертого элемента И, третий вход которого подключен к выходу второго одновибратора, выход шестого элемента И подключен к входу второго одновибратора, к пятому выходу блока, четвертому входу четвертого и второго входу седьмого элемен- тов И, выходы которых подключены соответственно к шестому и седьмому выходам блока, выход второго триггера подключен к первым входам элементов И с восьмого по тринадцатый, информационному входу третьего триггера и первому входу третьего элемента ИЛИ, выход которого подключен к информационному входу четвертого триггера, выходы элементов И с восьмого по десятый подключены соответственно к входам четвертого элемента ИЛИ, выход которого подключен к стробирую- щему входу четвертого дешифратора, выходы элементов И с одиннадцатого по тринадцатый подключены к входам пятого элемента ИЛИ, выход которого подключён к стробирующему входу третьего дешифратора, выход шестого элемента ИЛИ подключен к входу пер- вого одновибратора и к входу запуска формирователя импульсов, первый выход которого подключен к первым входам четырнадцатого и пятнадцатого элементов И, второй выход формирователя импульсов подключен к первым входам шестнадцатого и семнадцатого элементов И, выходы которых подключены соответственно к первым входам второго элемента И-НЕ и восемнадцатого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, выход которого подключен к входам установки в ноль третьего, четвертого и пятого триггеров и первому входу установки в единицу второго триггера, второй вход установки в единицу, вход установки в ноль, информационный вход и синхровход которого подключены соответственно к выходам элементов И с девятнадцатого по двадцать второй, выходы элементов

10

20

25

и с двадцать третьего по двадцать пятый подключены соответственно к второму входу установки в ноль н сннхро- входу третьего триггера, к синхровхо- ду четвертого триггера, выход седьмого элемента ИЛИ подключен к второму входу третьего элемента Инк первому входу второго элемента ИЛИ, выход восьмого элемента ИЛИ подключен к второму входу второго элемента ИЛИ и к второму входу jiHToro элемента И, выход которого подключен к первому входу шестого элемента ИЖ и к второму входу семнадцатого элемента И, выход третьего элемента.И подключен к второму входу шестого элемента ИШ и к второму входу пятнадцатого элемента И, выход которого подключен к первому входу двадцатого элемента И, второй вход которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первьй и второй входы которого подключены соответственно к выходу мультиплексора и к первому выходу второго дешифратора, выходы с первого по шестой которого подключены соответственно к первому и второму входам седьмого и к входам с первого по четвертый восьмого элементов ИЛИ, третий выход второго дешифратора подключен к вторым входам девятого и тринадцатого элементов И, четвертый выход второго дешифратора подключен к вторым входам десятого и двенадцатого элементов И, пятый и шестой выходы второго дешифратора подключены соответственно к вторым входам восьмого и одиннадцатого элементов И, выход первого элемента ИЛИ-НЕ подключен к синхровходу первого триггера, информационный вход которого подключен к входу логического нуля контроллера, выход второго элемента И подключен к вторым входам четырнадцатого и шестнадцатого элементов И, выходы с первого по третий первого дешифратора подключены соответственно к входам с третьего по пятый шестого элемента ИЛИ, второй выход первого дешифратора подключен к второму входу второго элемента И-НЕ и к первым входам двадцать первого, двадцать второго, двадцать четвертого и двадцать пятого элементов И, вторые входы которых подключены соответственно к выходу третьего триггера, выходу шестнадцатого элемента И, прямому и инверсному выходам пятого триггера, третий выход

30

35

40

45

55

п,ервого дешифратора подключен к первым входам двадцать третьего и девятнадцатого элементов И, выход четырнадцатого элемента И подключен к третьим входам двадцать четвертого и двадцать пятого элементов И и. к второму входу девятнадцатого элемента .И, третий вход которого подключен к выходу четвертого триггера и соединен с вторым входом третьего элемента ИЛИ, второй вход двадцать третьего элемента И подключен к выходу

шестнадцатого элемента И, выход второго элемента И-НЕ подключен к синх- ровходу пятого триггера, прямой выход которого подключен к третьему входу двадцать второго элемента И, ин- версньй выход пятого триггера подключен к информационному входу пятого триггера и к второму входу восемнадцатого элемента И, выход которого подключен к второму входу первого элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

| Однобитовый процессор программируемого контроллера | 1986 |

|

SU1476464A1 |

| Программируемый контроллер | 1987 |

|

SU1537016A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Устройство для сопряжения вычислительной машины с внешними объектами | 1986 |

|

SU1543411A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для обмена информацией | 1982 |

|

SU1084776A1 |

Изобретение относится к вычислительной технике и предназначено для построения программируемых контролеров (ПК).

Целью изобретения является повышение надежности работы ПК.

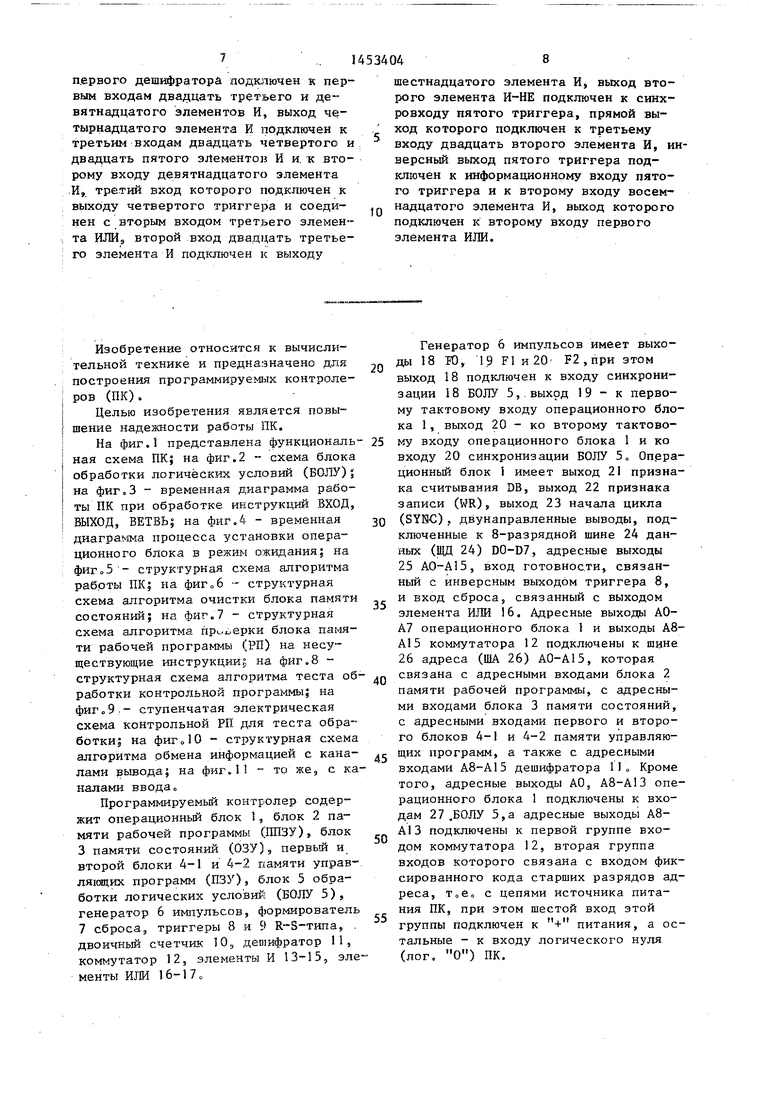

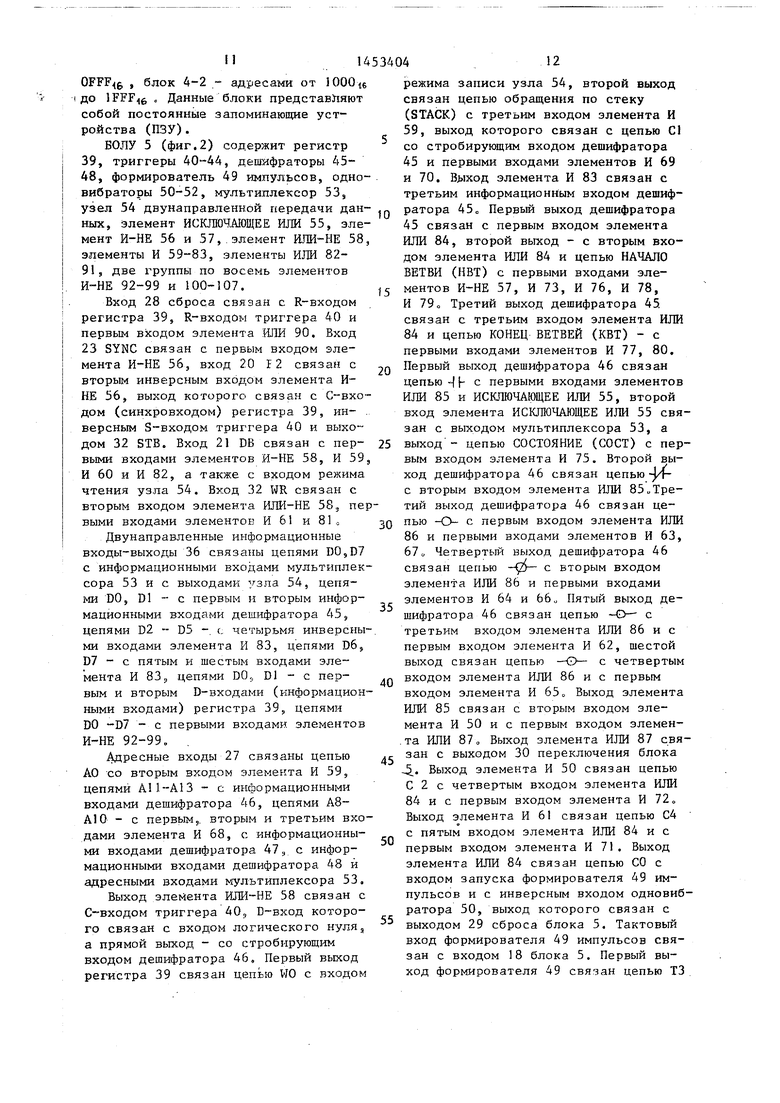

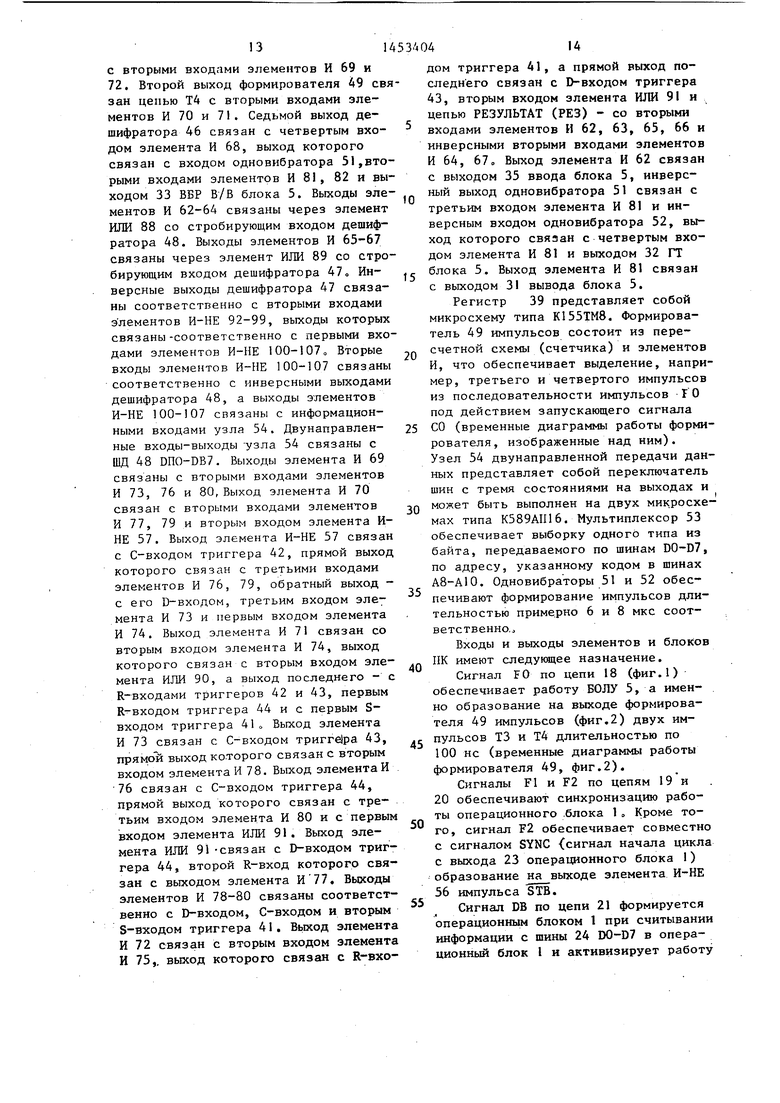

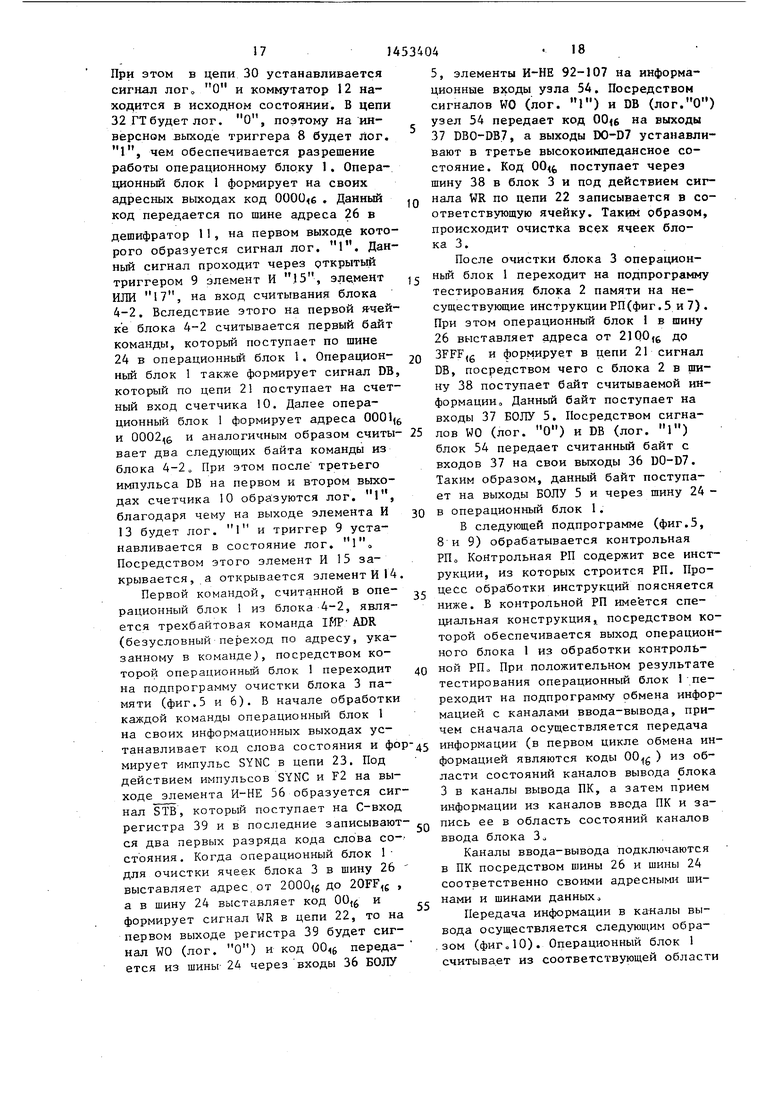

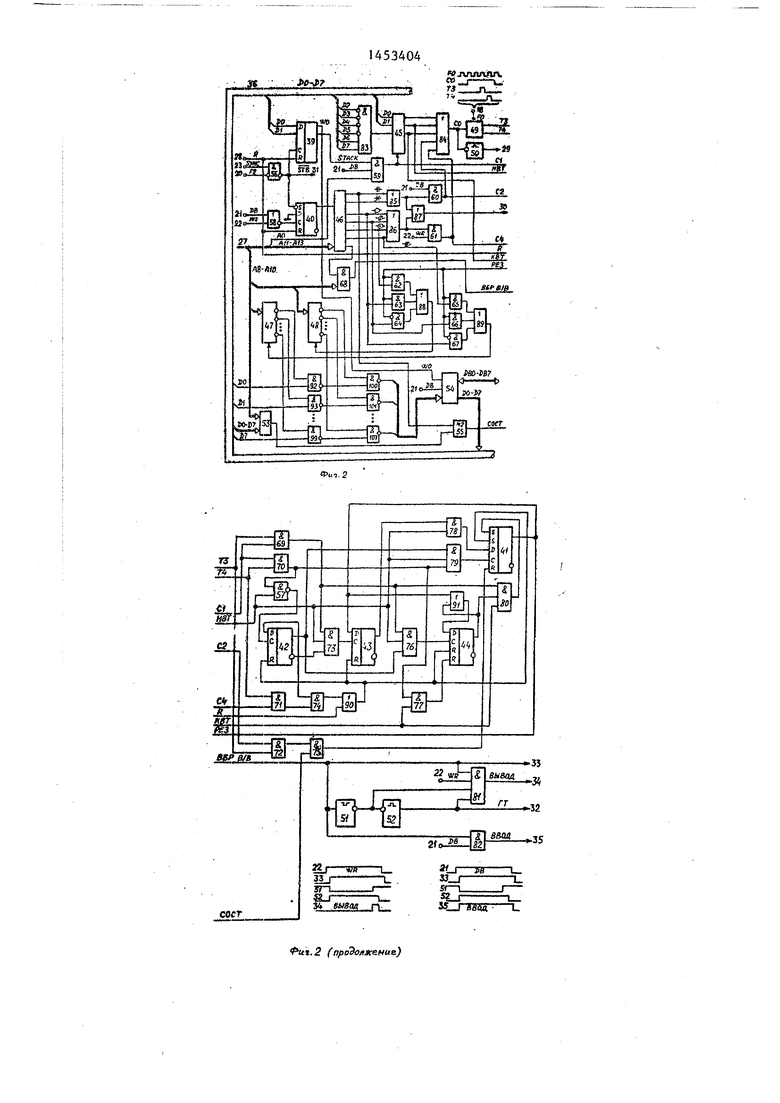

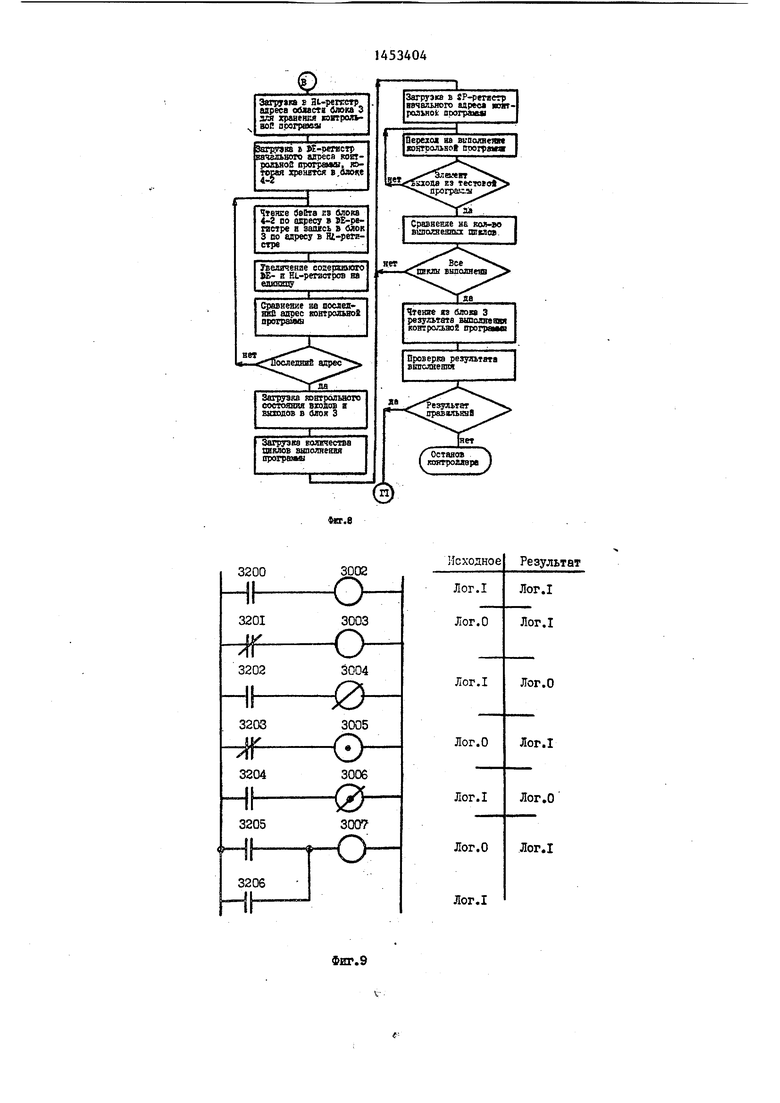

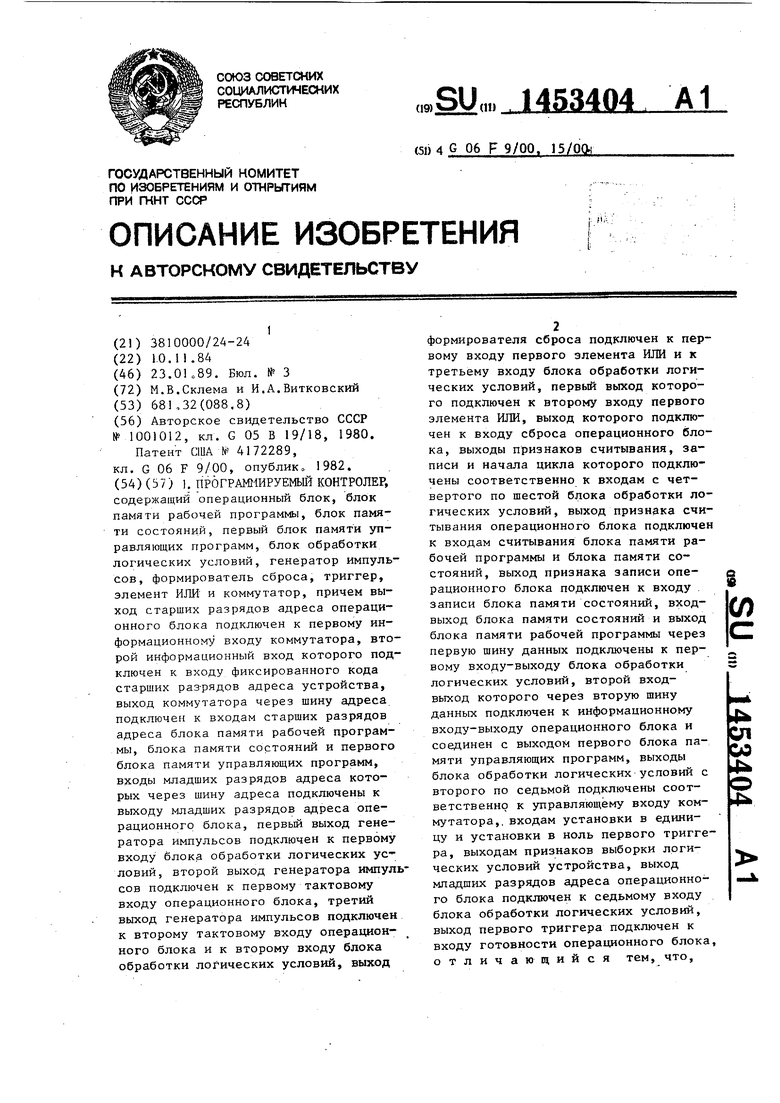

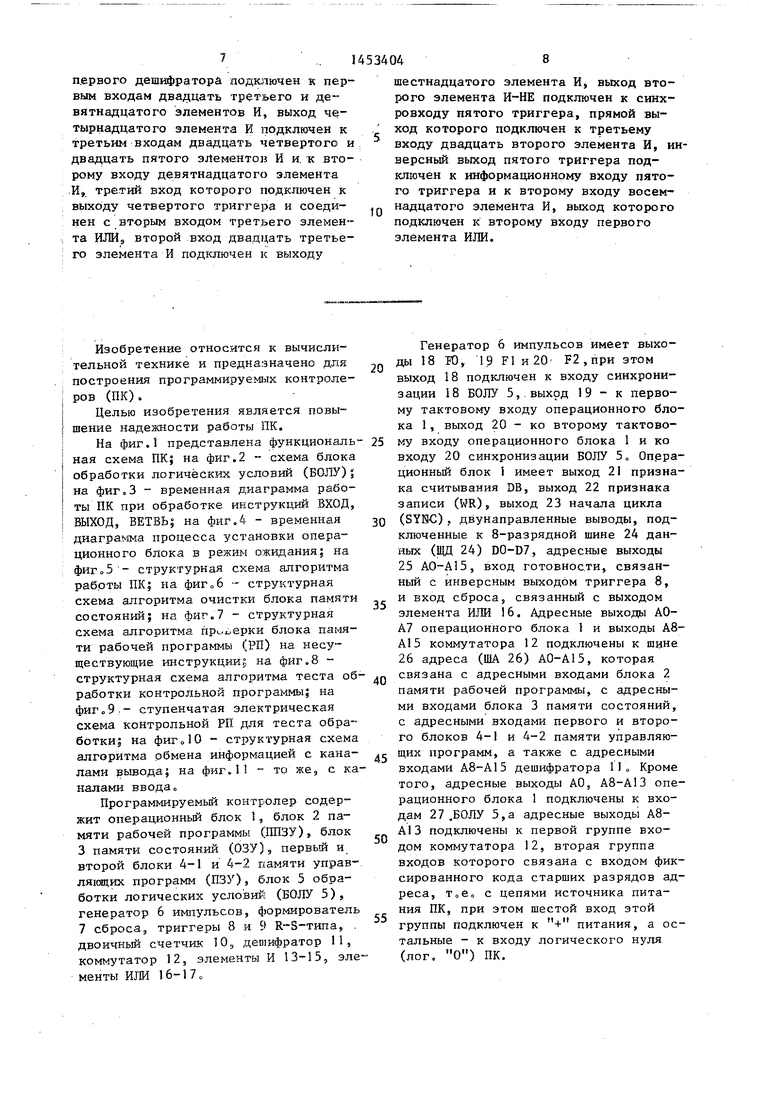

На фиг.1 представлена функциональная схема ПК; на фиг.2 - схема блока обработки логических условий (БОЛУ)| на фиГоЗ - временная диаграмма работы ПК при обработке инструкций ВХОД, ВЫХОД, ВЕТВЬ| на фиг.4 - временная диагра ша процесса установки операционного блока в режим ожидания| на фиго5 - структурная схема алгоритма работы ПК| на фиг о 6 - структурная схема алгоритма очистки блока памяти состояний; на фиг.7 - структурная схема алгоритма при..1:.ерки блока памяти рабочей программы (РП) на несуществующие инструкции; на фиг.8 - структурная схема алгоритма теста обработки контрольной программы; на фиг о 9.- ступенчатая электрическая схема контрольной РП для теста обработки; на фиг,10 - структурная схема алгоритма обмена информацией с каналами вывода; на фиг.11 то же, с каналами ввода.

Программируемый контролер содержит операционный блок 1, блок 2 памяти рабочей программы (Ш13У), блок 3 памяти состояний (ОЗУ), первый и второй блоки 4-1 и 4-2 памяти управ- ЛЯ1СЩИХ программ (ПЗУ), блок 5 обработки логических ycno swi (БОЛУ 5), генератор 6 импульсов, формирователь 7 сброса, триггеры 8 и 9 R-S-типа, . двоичньш счетчик 10,, дешифратор И, коммутатор 12, элементы И 13-15, элементы ИЛИ 16-17„

0

5

0

5

0

5

0

5

Генератор 6 импульсов имеет выходы 18 БО, 19 F1 и 20 Р2,при этом выход 18 подключен к входу синхронизации 18 БОЛУ 5,.выход 19 - к первому тактовому входу операционного блока 1, выход 20 - ко второму тактовому входу операционного блока 1 и ко входу 20 синхронизации БОЛУ 5о Оп.ера- ционный блок 1 имеет выход 21 признака считывания DB, выход 22 признака записи (WR), выход 23 начала цикла (SYNC) .. двунаправленные выводы, подключенные к 8-разрядной шине 24 данных (ЩД 24) DO-D7, адресные выходы

25АО-А15, вход готовности, связанный с инверсным выходом триггера 8, и вход сброса, связанный с выходом элемента ИЛИ 16. Адресные выходы АО- А7 операционного блока 1 и выходы А8- А15 коммутатора 12 подключены к шине

26адреса (ША 26) АО-А15, которая связана с адресными входами блока 2 памяти рабочей программы, с адресными входами блока 3 памяти состояний, с адресными входами первого и второго блоков 4-1 и 4-2 памяти управляющих программ, а также с адресными входами А8-А15 дешифратора По Кроме того, адресные выходы АО, А8-А13 операционного блока 1 подключены к входам 27 .БОЛУ 5,а адресные выходы А8- А13 подключены к первой группе входом коммутатора 12, вторая группа входов которого связана с входом фиксированного кода старших разрядов адреса, т„е„ с цепями источника питания ПК, при этом шестой вход этой группы подключен к + питания, а остальные - к входу логического нуля (лог, о) ПК.

Выход 21 DB операционного блока 1 подключен к счетному входу счётчика 10, входам считывания блоков 2 и 3 и входу 21 БОЛУ 5. Выход 22 WR операционного блока 1 подключен к входу записи блока 3 и к входу 22 БОЛУ 5, Выход 23 SYNC операционного блока 1 подключен к входу 23 БОЛУ 5.

Выход R формирователя 7 сброса подключен к первому входу элемента ИЛИ 16, к входу 28 сброса БОЛУ 5, к входу 28 сброса счетчика 10 и к R- входу триггера 9. Второй вход элемента ИЛИ 16 подключен к выходу 29 сброса БОЛУ 5..

БОЛУ 5 имеет выход 30 переключения, связанный с управляющим входом коммутатора 12, инверсный выход 31 . стробирования (STB), связанный с S- входом триггера 8, выход 32 готовности (ГТ), связанный с R-входом триггера 8, выходы 33 выборки свода-вывода (ВБР В/В), 34 вывода и 35 ввода

БОЛУ 5 имеет двунаправленные входы-выходы 36, связанные с ЩД 24, и двунаправленные входы-выходы 37,связанные с шиной 38 данных (ШД 38)D BO-D В7. При этом шина 24 связана с информационными вы5содами блоков 4-1 и 4-2, а шина 38 - с информационными входами-выходами блока 3 и информационными выходами блока 2.

Первый и второй выходы двоичного счетчика Ю связаны через элемент И 12 с S-входом триггера 9, прямой выход которого связан с первым входом элемента И 14, а инверсный выход - с первым входом элемента И 15„ Вторые входы элементов И 14 и 15 .подключены к первому выходу дешифратора I1, второй выход которого связан с первым входом элемента ИЛИ 17о Второй вход

10

15

20

25

30

35

40

Коммутатор 12 представляет собой два шинных формирователя, например, на микросхемах типа К589ИР12.

Генератор импульсов состоит из кварцевого генератора и делителя частоты и обеспечивает формирование импульсов F О частотой 5 МГц и длительностью 100 НС и импульсов FI и F2 частотой 1 МГц и сдвинутых относительно друг друга.

Формирователь 7 сброса представляет собой одновибратор, формирующий импульс R при включении питания.

Двоичный счетчик 10 имеет инверсный счетный вход, поэтому информация на его выходах появляется по заднему фронту счетного импульса.

Дешифратор 11 имеет четыре выхода, при этом на выходах образуются сигналы, когда на шине 26 появляются следующие адреса:

0000 - OFFF,g - для первого выхода; 1000 - 1FFF,6 - для -второго выхода; 2000 - 20FF, - для третьего выхода; 2100 - 3FFF,6 - для четвертого выход а ,

В блоке 2 памяти хранятся инструкции РП, последовательность которых воспроизводит ступенчатую электрическую схему управляемого объекта. Каждая инструкция занимает объем два байта в блоке 2, Блок 2 представляет собой перепрограммируемое постоянное запоминающее устройство (ЛПЗУ) и содержит ряд микросхем памяти типа К573РФ5. Рабочая программа в микросхемы памяти записывается с помощью отдельных средств, .которые не входят в ПК. Блок 2 адресуется операционным блоком 1, когда на шине 26 формируется адрес от 2100(6 до 3FFF(6 .

В блоке 3 памяти имеется область, в которой хранятся биты состояний

входим злемеп i «а rjjirj i / о .-т. im -

элемента ИЛИ 17 связан с выходом эле- 45 каналов вывода, другая область, в ко fiu-rt-T г пгтпач н кана-

мента И 15. Выход элемента И 14 подключен к входу считывания блока 4-1, выход элемента ИЛИ 17 - к входу считывания блока 4-2. Третий выход дешифратора 11 связан с входом выборки блока 3, а четвертый выход - с входом выборки блока 2.

Операционный блок 1 представляет собой микропроцессор и может быть выполнен на микросхеме КР580ИК80А, которая имеет двунаправленную 8-разрядную шину данных и 16-разрядную шину адреса, - .

50

55

торой хранятся биты состояний каналов ввода, и третья область, которая используется операционным блоком 1 для своих нужд, например для хранения результатов диагностики и тестирования ПКо Блок 2 представляет собой оперативное запоминающее устройство (ОЗУ) и адресуется операционным блоком 1, когда на шине 26 формируется адрес от 2000,6 до 20FF,6

В блоках 4-1 и 4-2 памяти хранятся команды операционного блока 1, образующие алгоритм работы ПК. Блок 4-1 выбирается адресами от 0000 до

5

0

5

0

5

0

Коммутатор 12 представляет собой два шинных формирователя, например, на микросхемах типа К589ИР12.

Генератор импульсов состоит из кварцевого генератора и делителя частоты и обеспечивает формирование импульсов F О частотой 5 МГц и длительностью 100 НС и импульсов FI и F2 частотой 1 МГц и сдвинутых относительно друг друга.

Формирователь 7 сброса представляет собой одновибратор, формирующий импульс R при включении питания.

Двоичный счетчик 10 имеет инверсный счетный вход, поэтому информация на его выходах появляется по заднему фронту счетного импульса.

Дешифратор 11 имеет четыре выхода, при этом на выходах образуются сигналы, когда на шине 26 появляются следующие адреса:

0000 - OFFF,g - для первого выхода; 1000 - 1FFF,6 - для -второго выхода; 2000 - 20FF, - для третьего выхода; 2100 - 3FFF,6 - для четвертого выход а ,

В блоке 2 памяти хранятся инструкции РП, последовательность которых воспроизводит ступенчатую электрическую схему управляемого объекта. Каждая инструкция занимает объем два байта в блоке 2, Блок 2 представляет собой перепрограммируемое постоянное запоминающее устройство (ЛПЗУ) и содержит ряд микросхем памяти типа К573РФ5. Рабочая программа в микросхемы памяти записывается с помощью отдельных средств, .которые не входят в ПК. Блок 2 адресуется операционным блоком 1, когда на шине 26 формируется адрес от 2100(6 до 3FFF(6 .

В блоке 3 памяти имеется область, в которой хранятся биты состояний

-.-т. im -

каналов вывода, другая область, в ко fiu-rt-T г пгтпач н кана-

торой хранятся биты состояний каналов ввода, и третья область, которая используется операционным блоком 1 для своих нужд, например для хранения результатов диагностики и тестирования ПКо Блок 2 представляет собой оперативное запоминающее устройство (ОЗУ) и адресуется операционным блоком 1, когда на шине 26 формируется адрес от 2000,6 до 20FF,6

В блоках 4-1 и 4-2 памяти хранятся команды операционного блока 1, образующие алгоритм работы ПК. Блок 4-1 выбирается адресами от 0000 до

10

15

20

25

, блок 4-2 адресами от ЮООчб до « Данные блоки представляют собой постоянные запоминающие устройства (ПЗУ).

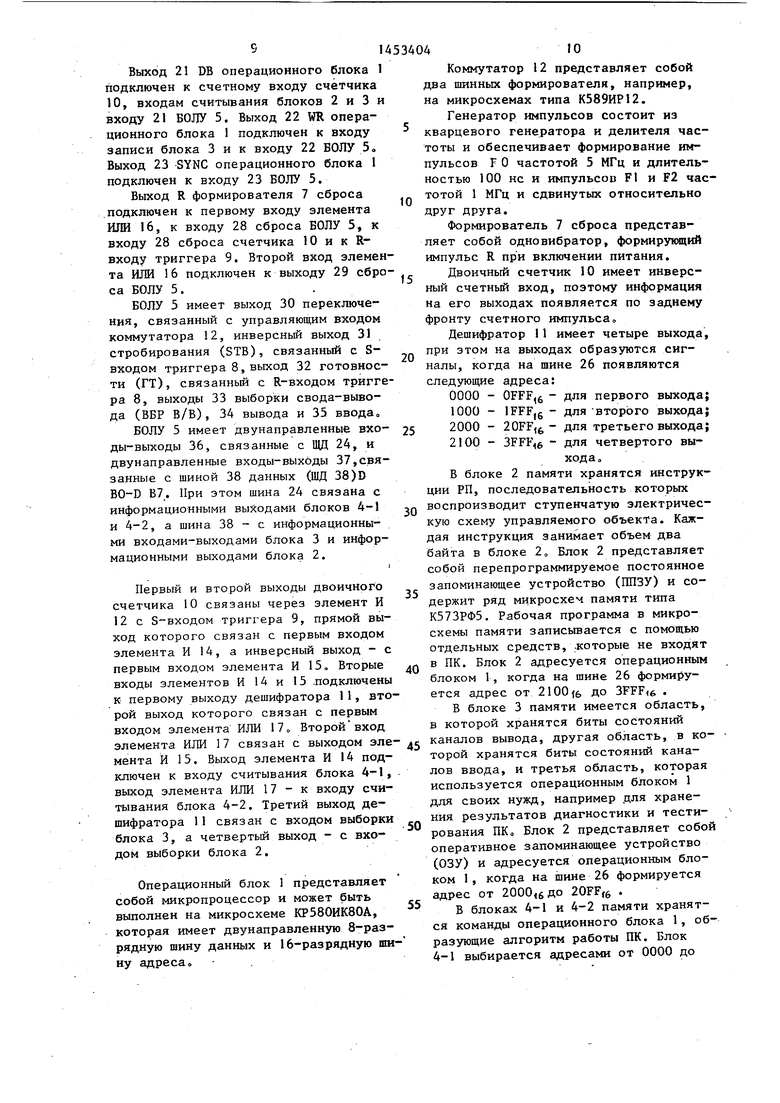

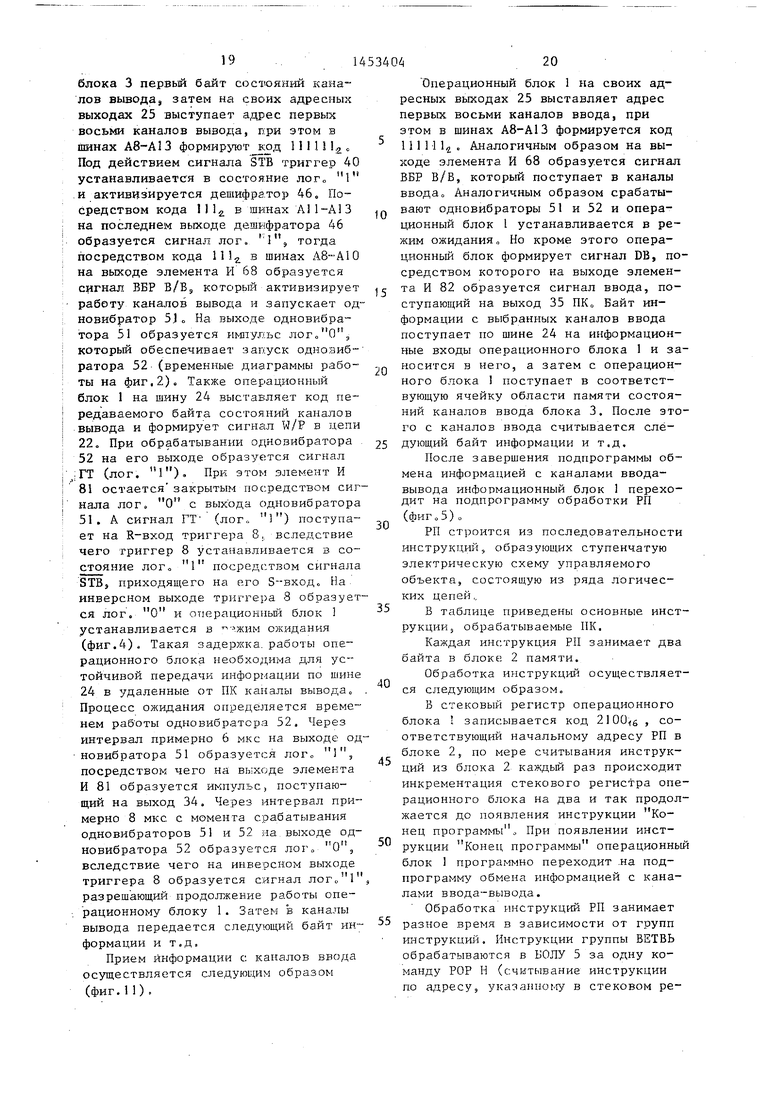

БОЛУ 5 (фиг.2) содержит регистр 39, триггеры 40-44, дешифраторы 45- 48, формирователь 49 импульсов, одно- вибраторы 50-52, мультиплексор 53, узел 54 двунаправленной передачи данных, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 55, элемент И-НЕ 56 и 57, элемент ИЛИ-НЕ 58, элементы И 59-83, элементы ИЛИ 82- 91, две группы по восемь элементов И-НЕ 92-99 и 100-107.

Вход 28 сброса связан с R-входом регистра 39, R-входом триггера 40 и первым входом элемента ИЛИ 90. Вход 23 SYNC связан с первым входом элемента И-НЕ 56, вход 20 Г 2 связан с вторым инверсным входом элемента И- НЕ 56, выход которого связан с С-вхо- дом (синхровходом) регистра 39, ин- . версным S-входом триггера 40 и выходом 32 STB. Вход 21 DB связан с первыми входами элементов И-НЕ 58, И 39, И 60 и И 82, а также с входом режима чтения узла 54. Вход 32 WR связан с вторым входом элемента ИЛИ-НЕ 58, первыми входами элементов И 61 и 81 о зо

Двунаправленные информационные входы-выходы 36 связаны цепями 1)0,D7 с информационными входами мультиплексора 53 и с выходами узпа 54, цепями DO, D1 - с первым и вторым информационными входами дешифратора 45, цепями D2 - D5 -. с. четырьмя инверсными входами элемента И 83, цепями D6, D7 - с пятым и шестым входами элемента И 83,, цепями DO., D1 - с первым и вторым D-входами (информационными входами) регистра 39, цепями DO -D7 - с первыми входами элементов И-НЕ 92-99. .

Адресные входы 27 связаны цепью АО СО вторым входом элемента И 59, цепями А11-А13 - с информационными входами дешифратора 46, цепями А8- А10 - с первым,, вторым и третьим входами элемента И 68, с информационными входами дешифратора 47, с информационными входами дешифратора 48 и адресными входами мультиплексора 53.

Выход элемента ИЛИ-НЕ 58 связан с е-входом триггера 40, D-вход которого связан с входом логического нуля, а прямой выход - со стробирующим входом дешифратора 46, Первый в)1ход регистра 39 связан цепью WO с входом

35

40

45

50

55

режима записи узла 54, второй выход связан цепью обращения по стеку (STACK) с третьим входом элемента И 59, выход которого связан с цепью С1 со стробирующим входом дешифратора 45 и первыми входами элементов И 69 и 70. элемента И 83 связан с третьим информационным входом дешифратора 45с Первый выход дешифратора 45 связан с первым входом элемента ИЛИ 84, второй выход - с вторым входом элемента ИЛИ 84 и цепью НАЧАЛО ВЕТВИ (НВТ) с первыми входами элементов И-НЕ 57, И 73, И 76, И 78, И 79о Третий выход дешифратора 45. связан с третьим входом элемента ИЛИ 84 и цепью КОНЕП ВЕТВЕЙ (КВТ) - с первыми входами элементов И 77, 80. Первый выход дешифратора 46 связан цепью -| h с первыми входами элементов ИЛИ 85 и ИСКЛЮЧАЮЩЕЕ ИЛИ 55, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 55 связан с выходом мультиплексора 53, а выход - цепью СОСТОЯНИЕ (СОСТ) с первым входом элемента И 75. Второй выход дешифратора 46 связан цепью -j/r- с вторым входом элемента ИЛИ 85„Третий выход дешифратора 46 связан цепью -О- с первым входом элемента ИЛИ 86 и первыми входами элементов И 63, 67„ Четвертый выход дешифратора 46 связан цепью с вторым входом элемента ИЛИ 86 и первыми входами элементов И 64 и 66„ Пятый выход дешифратора 46 связан цепью -О- с третьим входом элемента ИЖ 86 и с первым входом элемента И 62, шестой выход связан цепью -О- с четвертым входом элемента ИЛИ 86 и с первым входом элемента И 65„ Выход элемента ИЛИ 85 связан с вторым входом элемента И 50 и с первым входом элемен- .та ИЛИ 87 о Выход элемента ИЛИ 87 связан с выходом 30 переключения блока Д. Выход элемента И 50 связан цепью С 2 с четвертым входом элемента ИЖ 84 и с первым входом элемента И 72 Выход элемента И 61 связан цепью С4 с пятым входом элемента ИЛИ 84 и с первым входом элемента И 71. Выход элемента ИЛИ 84 связан цепью СО с входом запуска формирователя 49 импульсов и с инверсным входом одновиб- ратора 50, выход которого связан с выходом 29 сброса блока 5. Тактовый вход формирователя 49 импульсов связан с входом 18 блока 5. Первый выход формирователя 49 связан цепью ТЗ

1314

с вторыми входами элементов И 69 и 72, Второй выход формирователя 49 связан цепью Т4 с вторыми входами элементов И 70 и 71. Седьмой выход дешифратора 46 связан с четвертым входом элемента И 68, выход которого связан с входом одновибратора 51,вторыми входами элементов И 81, 82 и выходом 33 ВБР В/В блока 5. Выходы эле

ментов И 62-64 связаны через элемент ИЛИ 88 со стробирующим входом дешифратора 48. Выходы элементов И 65-67 связаны через элемент ИЛИ 89 со стробирующим входом дешифратора 47 Ин- версные выходы дешифратора 47 связаны соответственно с вторыми входами элементов И-НЕ 92-99, выходы которых связаны-соответственно с первыми входами элементов И-НЕ 100-107 Вторые входы элементов И-НЕ 100-107 связаны соответственно с инверсными выходами дешифратора 48, а выходы элементов И-НЕ 100-107 связаны с информационными входами узла 54. Двунаправлен- ные входы-выходы -узла 54 связаны с ШД 48 Dno-DB7. Выходы элемента И 69 связаны с вторыми входами элементов И 73, 76 и 80,Выход элемента И 70 связан с вторыми входами элементов И 77, 79 и вторым входом элемента И- НЕ 57. Выход элемента И-НЕ 57 связан с С-входом триггера 42, прямой выход которого связан с третьими входами элементов И 76, 79, обратный выход - с его D-ВХОДОМ, третьим входом элемента И 73 и первым входом элемента И 74. Выход элемента И 71 связан со вторым входом элемента И 74, выход которого связан с вторым входом эле- мента ИЛИ 90, а выход последнего - с R-входами триггеров 42 и 43, первым R-входом триггера 44 и с первым S- входом триггера 41 Выход элемента И 73 связан с С-входом тригге|ра 43, прямой выход которого связан с вторым входом элемента И 78. Выход элемента И 76 связан с С-входом триггера 44, прямой выход которого связан с третьим входом элемента И 80 и с первым входом элемента ИЛИ 91. Выход элемента ИЛИ 91-связан с D-входом триггера 44, второй R-вход которого связан с выходом элемента И 77, Выходы элементов И 78-80 связаны соответственно с D-входом, С-входом и вторым S-входом триггера 41. Вь1ход элемента И 72 связан с вторым входом элемента И 75,, выход которого связан с R-BXO

0 5 0 Q д

5

50

55

0414

дом триггера 41, а прямой выход последнего связан с D-входом триггера 43, вторым входом элемента ИЛИ 91 и цепью РЕЗУЛЬТАТ (РЕЗ) - со вторыми входами элементов И 62, 63, 65, 66 и инверсными вторыми входами элементов И 64, 67 о Выход элемента И 62 связан с выходом 35 ввода блока 5, инверсный выход одновибратора 51 связан с третьим входом элемента И 81 и инверсным входом одновибратора 52, выход которого связан с четвертым входом элемента И 81 и выходом 32 ГТ блока 5. Выход элемента И 81 связан с выходом 31 вывода блока 5.

Регистр 39 представляет собой микросхему типа К155ТМ8. Формирователь 49 импульсов состоит из пересчетной схемы (счетчика) и элементов И, что обеспечивает выделение, например, третьего и четвертого импульсов из последовательности импуЛьсов Г О под действием запускающего сигнала СО (временные диаграммы работы формирователя , изображенные над ним). Узел 54 двунаправленной передачи данных представляет собой переключатель шин с тремя состояниями на выходах и может быть выполнен на двух мик.росхе- мах типа К589АП16. Мультиплексор 53 обеспечивает выборку одного типа из байта, передаваемого по шинам DO-D7, по адресу, указанному кодом в шинах А8-А10. Одновибраторы 51 и 52 обеспечивают формирование импульсов длительностью примерно 6 и 8 МКС соот- ветственно.о

Входы и выходы элементов и блоков ПК имеют следукицее назначение.

Сигнал FO по цепи 18 (фиг.1) обеспечивает работу БОЛУ 5, а именно образование на выходе формирователя 49 импульсов (фиг.2) двух импульсов 13 и Т4 длительностью по 100 НС (временные диаграммы работы формирователя 49, фиг.2).

Сигналы F1 и F2 по цепям 19 и 20 обеспечивают синхронизацию работы операционного .блока 1 о Кроме того, сигнал F2 обеспечивает совместно с сигналом SYNC {сигнал начала цикла с выхода 23 операциоиного блока 1) образование на выходе элемента И-НЕ 56 импульса STB.

Сигнал DB по цепи 21 формируется операционным блоком 1 при считывании информации с шины 24 DO-D7 в операционный блок 1 и активизирует работу

-5 .

узлов ПК для вьщачи информации в опрационный блок.

Сигнал WE по цепи 22 формируется операционным блоком 1 при выдаче информации с операционного блока 1 в шину 24 и активизирует работу узлов ПК. .

Сигнал SYNC по цепи 23 формируется операционным блоком 1 всякий раз когда начинается машинный цикл обработки команды в операционном блоке (фиг.З). Сигнал SYNC обеспечивает синхронную работу БОЛУ 5 с выполнением команд в операционном блоке 1 ,

Сигнал R по цепи 28 формируется при включении питания ПК и обеспечивает установку узлов ПК в исходное состояние.

Сигнал сброса операционного блок 1 по цепи 29 образуется и БОЛУ 5 по завершении обработки инструкции ВХО ВЫХОД, ВЕТВЬ. Данньш сигнал обеспечивает ускоренный переход операционного блока 1 на обработку следующей инструкции РП, минуя выход из обработки через подпрограмму перехода.

На выходе 30 БОЛУ 5 формируется сигнал переключения коммутатора 12, чем обеспечивается адресация операционного блока 1 к блоку 3 памяти, если сигнал имеет состояние лог, 1 или адресация к блоку 2, или 4-2 памяти,, если сигнал имеет состояние лог. О.

Сигнал STB ПО цепи 31 синхронизирует начало работы БОЛУ 5, а также процесс установки операционного блока 1 в режим ожиданизг и ззыход из него.

Сигнал ГТ по цепи 32 формируется БОЛУ 5 для установки операционного блока 1 в режим ожидания, что осуществляется при передаче информации с блока 3 памяти в кана.л) вывода ПК и при приеме информации с каналов ввода в блок 3 памяти,

Сигнал ВБР/В/В на выходе 33 формируется при обращении ПК к каналам ввода-вывода и активизирует их ра-. боту.

Сигнал вывода на выходе 34 формируется при вьщаче информации с ПК в каналы вывода и обеспе чивает запись информации, например, в регистры моделей вывода.

Сигнал ввода на Бых.оде 35 форми руется при приеме байта информации

16

0

5

0

5

0

5

5

в ПК с каналов ввода и обеспечивает синхронизацию их работы.

Сигналы WO и STACK, образующиеся на выходах регистра 39, являются сигналами слова состояния операционного блока j. Сигнал WO обусловливает работу операционного блока 1 по выводу информации из него и активизирует работу узла 54 двунаправленной передачи данных. Сигнал STACK обусловливает считывание информации в операционньй блок по адресу, ука- за нному в его внутреннем стековом регистре, и обеспечивает формирование управляющего сигнала с дешифратора 45 при выполнении операционным блоком 1 первой команды POP Н обработки инструкции РП.

Сигнал С1 с выхода элемента И 59 обеспечивает работу узлов БОЛУ 5 при обработке инструкции группы ВЕТВЬ.

Сигнал С2 с выхода элемента И 60 обеспечивает работу узлов БОЛУ 5 при обработке инструкции группы БХОДо

.Сигнал С4 с выхода элемента И 61 обеспечивает работу узлов БОЛУ 5 при обработке инструкции группы ВЫХОД.

Импульсы ТЗ и Т4 с выходов формирователя 49 импульсов обеспечивают последовательность срабатьшания отдельных элементов БОЛУ 5.

Сигнал РЕЗ с выхода триггера 41 обусловливает-результат обработки последовательности инструкции РН,образующих одну логическую цепь.

Сигнал СОСТ с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЖ 55 обусловливает результат обработки инструкции ВХОД.

Сигнал, образующийся на выходе мультиплексора 53, обусловливает состояние анализируемого канала ввода и называется битом состояния канала ввода

Сигнал, образующийся на выходе элемента ИЛИ 88, обеспечивает установку в состояние лог„ 1 обрабатываемого канала вывода А сигнал, образующийся на выходе элемента ИЛИ 89, обеспечивает установку обрабатываемого канала вывода в состояние лого О.

Работает ПК следующим образом

После включения питания одновиб- ратор 7 формирует импульс R устанавливающий триггеры 9, 44, 40 и 42, счетчик 10, регистр 39 и операционный блок 1 в состояние лог О, а триггер 41 - в состояние лог. I.

17J4

При этом в цепи 30 устанавливается сигнал лого О и коммутатор 12 находится в исходном состоянии. В цепи 32 ГТбудет лог. О, поэтому на инверсном выходе триггера 8 будет лог. 1, чем обеспечивается разрешение работы операционному блоку 1, Опера- ционньй блок 1 формирует на своих адресных выходах код . Данный код передается по шине адреса 26 в дешифратор 11, на первом выходе которого образуется сигнал лог. 1 . Дан- ньй сигнал проходит через открытый триггером 9 элемент И )5, элемент ИЛИ 17, на вход считывания блока 4-2. Вследствие этого на первой я-чей- ке блока 4-2 считывается первый байт команды, который поступает по шине 24 в операционный блок 1. Операцион- ный блок 1 также формирует сигнал DB, который по цепи 2 поступает на счетный вход счетчика 10. Далее операционный блок 1 формирует адреса OOOl и 0002,6 и аналогичным образом считы- вает два следующих байта команды из блока 4-2« При этом после третьего импульса DB на первом и втором выходах счетчика 10 образуются лог. , благодаря чему на выходе элемента И 13 будет лог. I

и триггер 9 устанавливается в состояние лог. 1 Посредством этого элемент И 15 закрывается, а открывается элемент И 14

Первой командой, считанной в one- рационный блок 1 из блока 4-2, является трехбайтовая команда 1ЙР ADR (безусловный переход по адресу, указанному в команде), посредством которой операционный блок 1 переходит на подпрограмму очистки блока 3 памяти (фиг.5 и 6). В начале обработки каждой команды операционный блок 1 на своих информационных выходах устанавливает код слова состояния и фо мирует импульс SYNC в цепи 23. Под действием импульсов SYNC и F2 на выходе элемента И-НЕ 56 образуется сигнал Sra, который поступает на С-вход регистра 39 и в последние записывают ся два первых разряда кода слова состояния. Когда операционный блок 1 для очистки ячеек блока 3 в шину 26 выставляет адрес от 2000,6 до 20FF,g , а в шину 24 выставляет код 00, и формирует сигнал WR в цепи 22, то на первом выходе регистра 39 будет сигнал WO (лог. О) и код 00,6 переда- ется из шины 24 через входы 36 БОЛУ

18

5, элементы И-НЕ 92-107 на информационные входы узла 54. Посредством сигналов WO (лог. 1) и DB (лог.О) узел 54 передает код на выходы 37 DBO-DB7, а выходы DO-D7 устанавливают в третье высокоикшедансное состояние. Код OOifc поступает через шину 38 в блок 3 и под действием сигнала WR по цепи 22 записывается в соответствующую ячейку. Таким образом, происходит очистка всех ячеек блока 3..

После очистки блока 3 операционный блок 1 переходит на подпрограмму тестирования блока 2 памяти на несуществующие инструкции РП(фиг. 5 и 7) . При этом операционный блок 1 в шину 26 выставляет адреса от 21QO, до 3FFF,g и формирует в цепи 21 сигнал DB, посредством чего с блока 2 в шину 38 поступает байт считываемой информации Данный байт поступает на входы 37 БОЛУ 5. Посредством сигналов WO (лог. О) и DB (лог. 1) блок 54 передает считанный байт с входов 37 на свои выходы 36 DO-D7. Таким образом, данный байт поступает на выходы БОЛУ 5 и через шину 24 - в операционный блок 1.

В следующей подпрограмме (фиг.5, 8 и 9) обрабатывается контрольная РПо Контрольная РП содержит все инструкции, из которых строится РП. Процесс обработки инструкций поясняется ниже. В контрольной РП нме ется специальная конструкция, посредством которой обеспечивается выход операционного блока 1 из обработки контрольной РПо При положительном результате тестирования операционный блок 1 переходит на подпрограмму обмена информацией с каналами ввода-вывода, причем сначала осуществляется передача информации (в первом цикле обмена информацией являются коды ) из области состояний каналов вывода блока 3 в каналы вывода ПК, а затем прием информации из каналов ввода ПК и запись ее в область состояний каналов ввода блока 3

Каналы ввода-вывода подключаются в ПК посредством шины 26 и шины 24 соответственно своими адресными шинами и шинами данныхо

Передача информации в каналы вывода осуществляется следующим образом (фиго 10). Операционный блок 1 считывает из соответствующей области

блока 3 первьй байт состояний каналов вывода, затем на своих адресных выходах 25 выступает адрес первых восьми каналов вывода, при этом в шинах А8-А13 формир тот код 11 ПП Под действием cигнaJ a STB триггер 40 устанавливается в состояние лого 1 ,и активизируется дешифратор 46. Посредством кода 1)1 в шинах А11-А13 на последнем выходе дешифратора 46 образуется сигнал лог I, тогда

посредством кода 11 1. в шинах А8--А10 на выходе элемента И 68 образуется сигнал ВБР В/Б, который активизирует

работу канагтов вывода и запускает од- новибратор 5J о На выходе одновибра- тора 51 образуется импуяъс который обеспечивает запуск одноаиб- ратора 52-(временные диаграммы работы на фиг,2). Также операционный блок 1 на шину 24 выставляет код передаваемого байта состояний каналов вывода и формирует сигнал W/P в цепи 22 При обрабатывании одновибратора 52 на его выходе образуется сигнал

;ГТ (лог. 1), При этом элемент И 81 остается закрытым по (средством сигнала лог. О с выхода одновибратора 51. А сигнал ГТ (лог,. )) поступает на R-вход триггера 8,, вследствие чего триггер 8 устанавливается в состояние лог о 1 посредством сигнала STB, приходящего на его 3--вход« На. инверсном выходе триггера 8 образуется лог. О и операционньй блок 1 устанавливается в ожидания (фиг.4). Такая задержка, работы опе- радионного блока необходима для устойчивой передачи информации по шине 24 в удаленные от ПК каналы вывода . Процесс ожидания oпpeдёJтяeтcя временем работы одновибратора 52, Через интервал примерно 6 мкс на выходе од- новибратора 51 образуется лог о , посредством чего на выходе элемента И 81 образуется импульс, поступающий на выход 34. Через интервал примерно 8 МКС с момента срабатывания одновибраторов 51 и 52 на выходе одновибратора 52 образуется лог о О , вследствие чего на инверсном выходе триггера 8 образуется сигнал лог 1 j разрешающий продолжение работы опе- . рационному блоку 1. Затем в каналы вывода передается следующий байт ин-- формадии и т.д.

Прием информации с каналов ввода осуществляется следующим образом (фиг.11).

0

5

0

5

0

5

0

5

Операционный блок 1 на своих адресных выходах 25 выставляет адрес первых восьми каналов ввода, при зтом в шинах А8-А13 формируется код 111111. Аналогичным образом на выходе элемента И 68 образуется сигнал ВБР В/В, которьш поступает в каналы ввода,, Аналогичным образом срабатывают одновибраторы 51 и 52 и операционный блок 1 устанавливается в режим ожидания. Но кроме этого операционньй блок формирует сигнал DB, посредством которого на выходе элемента И 82 образуется сигнал ввода, поступающий на выход 35 ПК Байт информации с выбранных каналов ввода поступает по шине 24 на информационные входы операционного блока 1 и заносится в него, а затем с операционного блока поступает в соответствующую ячейку области памяти состояний каналов ввода блока 3. После этого с каналов ввода считывается следующий байт информации и т.д.

После завершения подпрограммы обмена информацией с каналами ввода- вывода информационный блок 1 переходит на подпрограмму обработки РП

(фиго5)о

РП строится из последовательности инструкций, образующих ступенчатую электрическую схему управляемого объекта, состоящую из ряда логических цепей,,

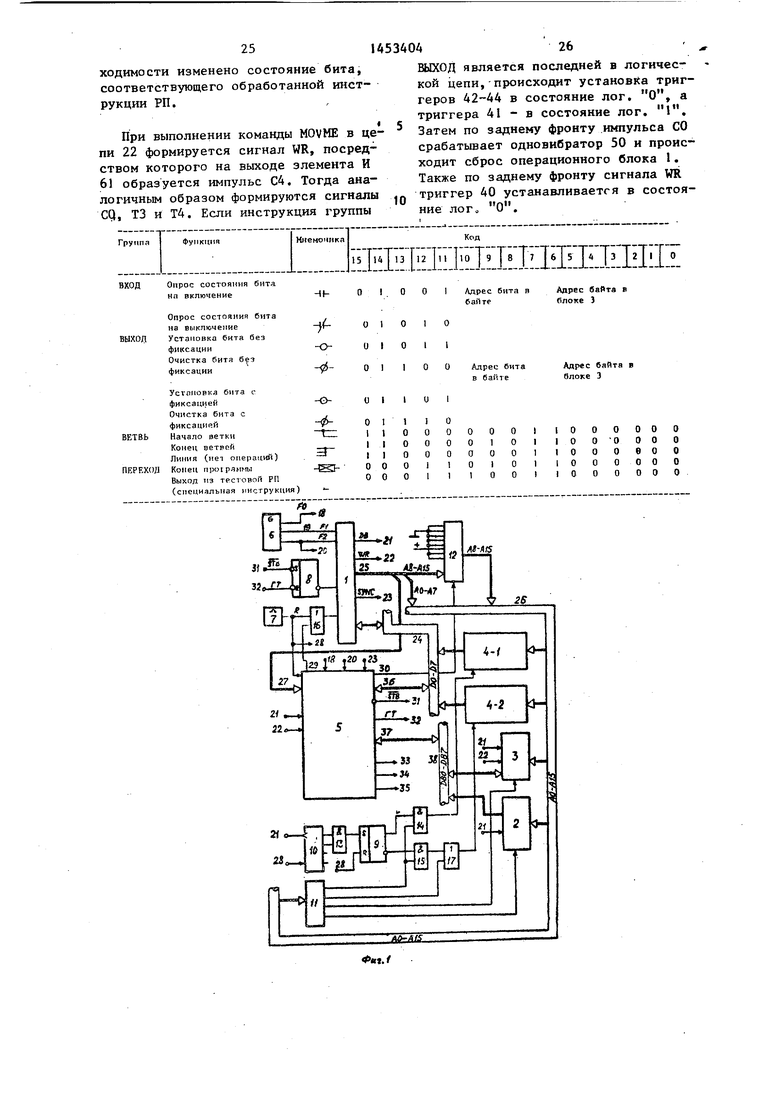

В таблице приведены основные инструкции, обрабатываемые ПК.

Каждая инструкция РП занимает два байта в блоке 2 памяти.

Обработка инструкций осуществляется следующим образом.

В стековый регистр операционного блока записывается код , соответствующий начальному адресу РП в блоке 2, по мере считывания инструкций из блока 2 каждьй раз происходит инкрементация стекового регистра операционного блока на два и так продолжается до появления инструкции Конец программы о При появлении инструкции Конец программы операционньй блок 1 программно переходит .на подпрограмму обмена информацией с каналами ввода-вывода.

Обработка инструкций РП занимает разное время в зависимости от групп инструкций. Инструкции группы ВЕТВЬ обрабатываются в БОЛУ 5 за одну команду POP Н (считывание инструкции по а,цресу5 указанному в стековом ре10

15

20

21I453A04

истре, и загрузка ее во внутренние , L-регистры операционного блока). оманда POP Н хранится в первых ячейах блока 4-1 и выбирается адресом

000,6 .

Считываемая из блока 2 инструкция руппы ВЕТВЬ поступает по шине 38 на ходы 37 БОЛУ 5 о Так как в цикле Ьчи- ывания формируются сигналы WO (лоГо О) и DB (лого 1), то узел 54 пеедает считанный байт в шину 24/DO- 7. Таким образом, первьш байт (младий байт) инструкции поступит в операционный блок 1 При считывании ладшего байта инструкции при выполнении команды POP Н в регистр 39 записывается слово состояния операционного блока 1, в котором присутствует сигнал STACK. Также под действием сигнала STB триггер 40 устанавливается в состояние лог„ I, Однако остальные узлы БОЛУ 5 не срабатывают.

При считывании старшего байта инструкции группы ВЕТВЬ под действием сигналов STACK, DB и АО - лог. 1 на выходе элемента И 59 образуется сигнал С1 (лог. 1), который разрешает работу дешифратору 45 Тогда на одном из выходов последнего образуется сигнал НВТ, КВТ или ЛИНИЯ,вследствие чего на выходе элемента ИЛИ 84 образуется сигнал СО, который поступает на вход запуска формирователя 49 импульсов. Формирователь 49 сформирует импульсы ТЗ и Т4. Также по заднему фронту сигнала СО сработает одновибратор 50 и на его выходе 29 образуется импульс сброса, который поступает через элемент ИТМ 16 на вход сброса операционного блока 1 о При этом операционный блок 1 устанавливается в состояние лог. О ,затем устанавливает на своих адресных выходах код 0000, и происходит снова обращение к первым ячейкам блока 4-, в которых записана команда POP Н, т.е. происходит переход на считывание следующей инструкции РП. Сигналы С1, КВТ (НВТ), ТЗ, Т4 обеспечивают срабатывание триггеров 4144„

Если считанная инструкция относится к группе ВХОД или ВЫХОД, то аналогичным образом на выходе элемента И 59 образуется импульс С1 и разрешается работа дешифратору 45, однако на его выходах сигналы не образуются. Поэтому при выполнении комами

ос ци ты ук гр оп пр ци ад пр мл ко ке ст ст де ил ст та 25 пр зу м в м п н с 35 н ш б

30

40

50

5

0

A04

22

манды POP П импульсы ТЗ и Т4 не формируются .

Обработка инструкции группы ВХОД осуществляется на две команды операционного блока: POP Ни МО V ЕМ (считывание байта из блока 3 по адресу, указанному в Н, L-регистрах, и за- грузка байта во внутренний А-регистр операционного блока). Таким образом, при выполнении команды MOVEM операционный блок 1 выставляет на своих адресных выходах код инструкции РП, при этом в шины АО-А7 поступает код младшего байта инструкции РП, Тов, код, определяющий адрес байта в блоке 3, а в шины А8-А15 поступает код старшего байта инструкции РП. Посредством кода в шинах А11-А13 на выходах дешифратора 46 образуется сигнал-t I- или -| 1- соответствующий мнемонике инструкции РП Тогда на выходе элемента ИЛИ 85 образуется сигнал лог, 1. Так как выполнение команды MOVEM со- 5 провождается формированием сигнала DB, то на выходе элемента И 60 образуется сигнал С2, которьй через элемент ИЛИ 84 запускает формирователь 49 и задним фронтом запускает одно- вибратор 50. Кроме того, с выхода элемента ИЛИ 85 сигнал лог. 1 поступает через элемент ИЛИ 87 по цепи 30 на управляющий вход коммутатора 12, благодаря чему последний подключает свои вторые входы к цепям А8-А15 ши- 5 ны 26, Таким образом, в шину 26 поступает код 20 , где NN - код в шинах АО-А7. Значит происходит обращение к блоку 3. Считанный из блока 3 байт информации содержит бит состояния необходимого канала ввода данной обрабатываемой инструкции РП. Байт информации поступает через входы DO-D7 узла 54 на информационные входы мультиплексора 53, на адресные входы которого поступает с шин А8- А10 код, соответствующий номеру бита в байте состояний каналов ввода оТогда на выходе мультиплексора 53 выделяется бит информации, код которого соответствует состоянию канала ввода. Этот код поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 55, на выходе которого образуется сигнал лог о О или лог о 1 в зависимости от типа обра- батываемой инструкции группы ВХОД и в зависимости от состояния канала ввода. При этом на выходе .элемента 55 будет состояние лог, О, если обра0

0

50

23

батывается инструкция типа Ч |- и состояние канала ввода равно лоГо 1 или, если обрабатывается инструкция типа -j/f- и состояние канала ввода равно лог о О. На выходе элемента 55 образуется лог 1, если обрабатывается инструкция типа Ч I- и состояние канала ввода равно лог. О или, если обрабатывается -инструкция типа -У}- и состояние канала ввода равно ЛОГо Г о

Сигнал СОСТ с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 55 поступает на первый вход элемента И 75. Таким образом, если сигнал СОСТ равен , то под такты С2 и ТЗ через элементы И 72 и 75 триггер 41 устанавливается в состояние лог

По завершении выполнения команды МОУЕМ по заднему фронту сигнала DB на выходе элемента ИЛИ-НЕ 58 образуется сигнал ЛОГо 1 и триггер 40 устанавливается в состояние лог,О, дешифратор 46 закрывается и на выходе элемента ИЛИ 87 образуется сигнал; ЛОГо О, вследствие чего коммутатор 12 переключается в исходное состояние

На выходе одновибратора 50 формируется импульс сброса операционного блока 1, таким образом, обработка инструкции группы ВХОД завершается,.

Обработка инструкции группы ВЫХОД осзпцествляется за три команды операционного блока 1: POP Н, MOVEM и MOVME (запись банта з блок 3 по адресу, указанному в h, 1,-регистрах) Аналогичным образом из блока 2 считывается инструкция, из блока 3 считывается байт, содержащий бит состояния канала вывода, соответствующего инструкции, при этом формирование сигналов С2 и С1 не происходит, А далее при выполнении команд МОУМЕ ранее считанный опефационным блоком 1 байт состояния яересылается из опе .рационного блока 1 через шину 24, БОЛУ 5, шину 38 обратно в блок 3. При этом под действием сигнала ;эТВ триггер 40 устанавливается в состояние лог. 1 и разрешает работу дешифратору 46. На адресные входы дешифратора 46-поступает код из L-pe- гистра операционного блока 1, которым является код ста-ршего байта обрабатываемой инструкции РП. Таким образом, на втором, третьем, четвертом или пятом выходах дешифратора 46

1

10

20

25

45340424

образуется сигнал -Q- , , -О- или -0- в зависимости от типа обрабатываемой инструкции группы ВЫХОД. Тогда посредством элементов ИЛИ 86 и 83 в цепи 30 образуется сигнал, обеспечивающий коммутатору 12 подключение к цепям А8-А15 шины 26 своей второй группы входом, чем достигается адресация к блоку 3. Сигналы, .соответствующие -О- , , -О- или , с выходов дешифратора 46 поступают на две комбинационные схе №1, одна из которых состоит из эле- )5 ментов И 62-64 и элемента ИЛИ 88, а другая - из элементов И 65-67 и элемента ИЛИ 89. В зависимости от типа обрабатываемой инструкции группы ВЫХОД и результата обработки логической цепи (состояния триггера 41) образуется сигнал лог. 1 на выходе элемента ИЛИ 88 или на выходе элемента ИЛИ 89. Например, результат обработки логической цепи равно лог. 1, тогда сигнал лог„ 1 образуется на выходе элемента ИЛИ 88 для сигналов, соответствующих -Q- и -О- . Этот сигнал разрешает работу дешифратору .48, на адресные входы А8-А10 которого поступает код, который при выполнении команды MOVME соответствует адресу бита в передаваемом байте состояния в блок 3. Таким образом, на соответствующем выходе дешифратора 48 образуется сигнал лог. О, а на остальных выходах дешифратора 48 и на всех выходах дешифратора 47 будут сигналы лог. 1, Передаваемый байт поступает на выходы DBO-DB7 узла 54, при этом проходит через группы элементов И-НЕ 92-107. Так как на входе одного из элементов И-НЕ 100-107 с выхода дешифратора 48 поступает сигнал лог. О, то соответствующий бит в передаваемом байте состояния устанавливается в лог. 1, а остальные биты информации не изменяют своего состояния. Если результат обработки логической цепи равен лог. О, то сигнал лог. 1 образуется на выходе элемента ИЛИ 89 для сигналов, соответствующих -О- и -О-, и на определенном выходе дешифратора 47 будет сигнал лог. О. Тогда в передаваемом байте информации происходит установка соответствующего бита в состояние ЛОГо О. Таким образом, в блок 3 записывается байт состояния каналов вывода, в котором при необ30

35

40

45

50

55

ходимости изменено состояние бита, соответствующего обработанной инструкции РП..

I

При выполнении команды MOVME в цепи 22 формируется сигнал WR, посредством которого на выходе элемента И 61 образуется импульс С4. Тогда аналогичным образом формируются сигналы CQ, ТЗ и Т4. Если инструкция группы

ВЫХОД является последней в логической цепи, происходит установка триггеров 42-44 в состояние лог. О, а триггера 41 - в состояние лог. 1 . Затем по заднему фронту импульса СО срабатывает одновибратор 50 и происходит сброс операционного блока 1. Также по заднему фронту сигнала WR триггер 40 устанавливается в состояние лог о О.

JS L .ff-ф

.2 (.ние.)

«лллллл

со

.35

еол L

Считывание ufctry ytfunu из ППЗУ2

«t.J

, jULJl-JlJUtJLJl-A-n

wnruTX

Siom3

jnr

--TT- LT

( В|лвЖ1)

10-1

Очвотке блока 3

Тес ва провеску бло- да а Н8 весувНтвуо- вве Енструкциг

I Тест ва обработку 1коЕтрольной програиш

Е

Обмен с выводом и вволом

Обработке инструкций раоочей програи.ш

Фш .5

,

iJarpysKB в HL-per0c7 p начального адреса I рабочей программы (5лока г

I Чтение из блока 2 по I алресу в Ш.-регистре I

Т

I Оаределение четного г I или нечетного адреса I

Срганеяие считанного раита на несутаестаую- vyv инструкйш

1 Ti, 1 дД««М11ма Ддаааидаа 5аи

Увеличеняе солервимо roHtrpeructpa яа еяшш

ЗагруакЕ в Hl-реглсгр начального адреса олояа 3

Очистка акку.удягора микропроцессора

Запись солеояимого аккумулятора в йлок 3 00 адресу в Ш..регяст.

иг. 6

Увеличение содерин- мого Ш.-оегистра на едЕшщу

Останов контроллера /

Загрузка вК -регястр адреса области вывода блока 3

Загрузка в ВС-регистр начального адреса каналов вывода

Чтение из блока 3 по адресу в 5Б-регистре

Передача байта в каналы вывода ко адресу в ВС-регистре

Сравнение на последили адрес области вывода С5лока 3

Увеличение содержимох о Ш- и БС регистров на единицу

ФшгЛО

Загрузка в ЬЕ-регистр адреса области ввсда блока 3

Загрузка в ВС-оегист начального адреса каналов ввода

Прием байта из каналов ввода по адресу в ВС-регистре

±

Запись состояния входов в блок 3 до адресу в 3)Е-регистре

Сравнение на последний адрес области ввода блока 3

нет

Увеличение содерзкимо- го ВС- и КЕ-регистров на единицу

Фиг.II

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США № 4172289, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-23—Публикация

1984-11-10—Подача