Изобретение относится F вычислительной технике и может быть использовано в.многопроцессорных вычислительных системах для реализации межзадачного взаимодействия.

Цель изобретения расширение области применения за счет адаптивной коммутации процессоров при выполнени моногозадачных программ. .

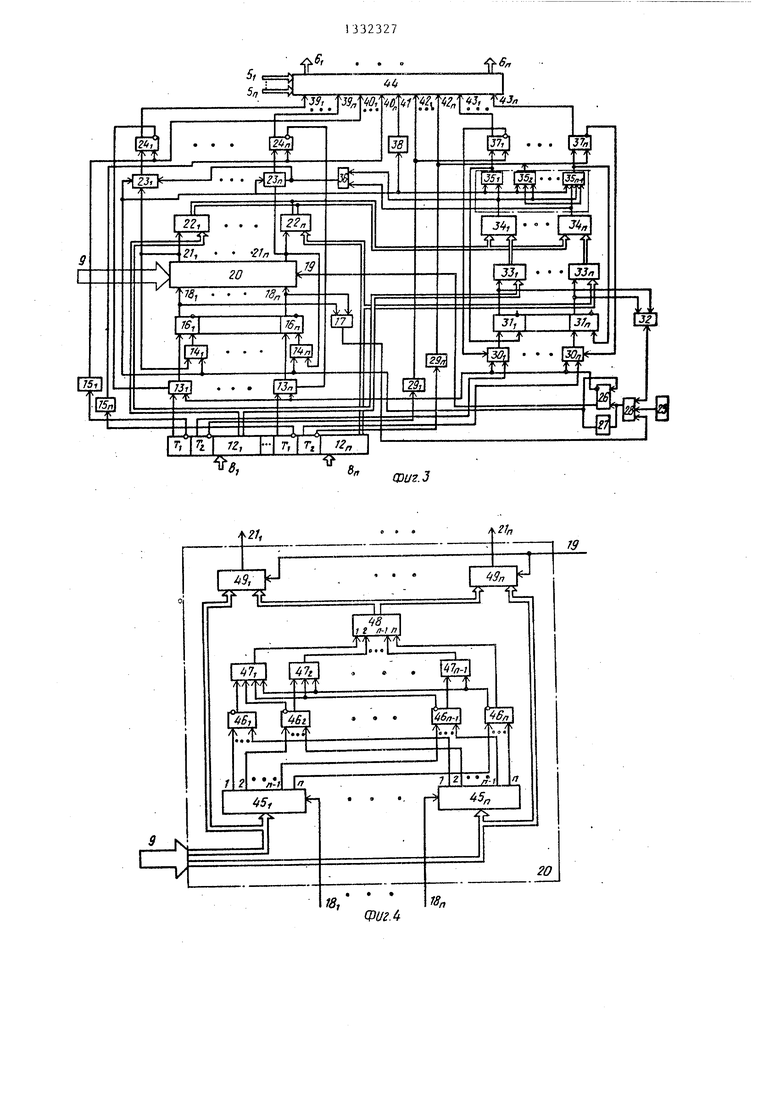

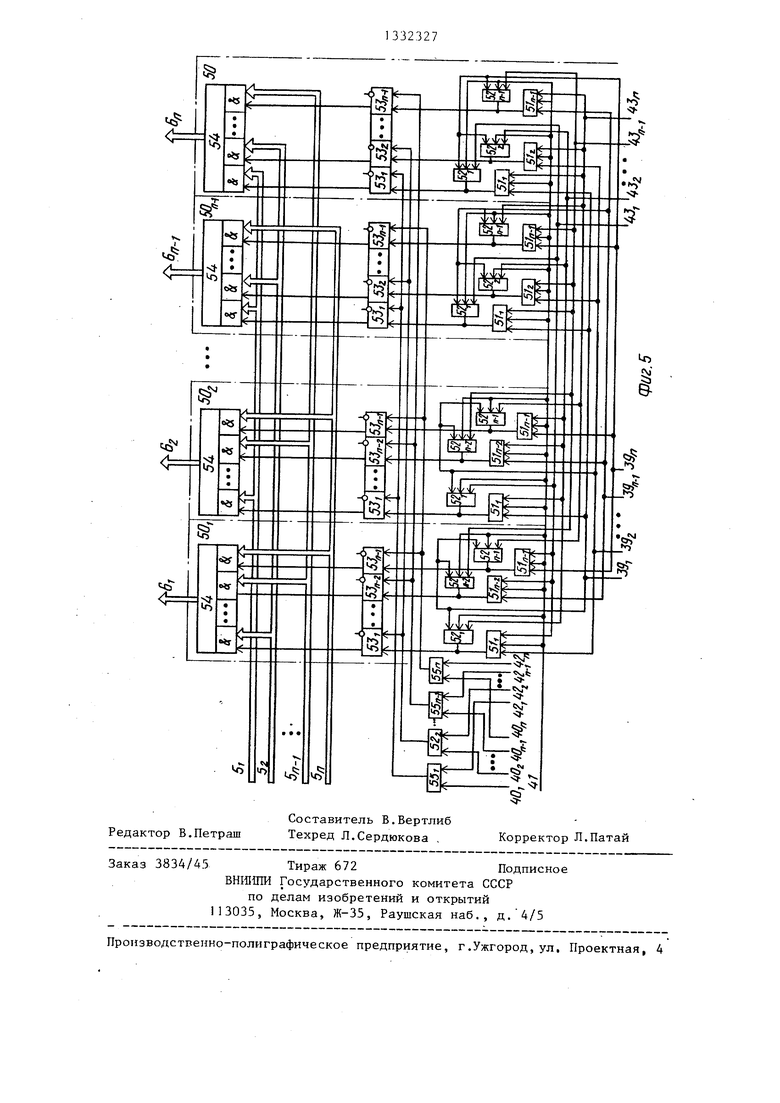

На фиг.1 представлена блок-схема устройства; на фиг.2 - 5 - функциональные схемы блока регистров приори тета, блока установления соединения, узла приоритетов процессов и узла ком- мутации соответственно.

Устройство (фиг.О содержит шины 1 стандартного интерфейса связи, ин- терфейсные блоки 2 усилителей, узел 3 комутации соединения, блок 4 ре- гистров приоритета, шины 5 передачи, шины 6 приема, линии 7 запросов, шины 8,запросов, шины 9 группы выходов блока 4 регистров приоритета.

Блок 4 регистров приоритета (фиг.2) содержит коммутатор Ю и группу регистров 11 приоритета.

Узел 3 коммутации соединения (фиг.З) содерлшт группу управляюш;их регистров 12, первую группу элемен- тов И 13, вторую группу элементов И 14, первую группу формирователей 15 импульса (дифференцирующих элементов), буферный регистр 16 запросов , первый элемент ИЛИ 17, группу выходов 18 регистра 16, управляющий вход 19 узла 20 приоритетов процессов, выходы 21 узла 20, первую группу блоков 22 элементов И, третью группу элементов И 23, первую группу управляющих триггеров 24, генератор 25 импульсов, триггер 26 управления, первый элемент 27 задержки, элемент И 28, вторую группу формирователей 2 импульса.(дифференцирующих элемен- тов), четвертую группу элементов И 30, буферный регистр 31 готовности , второй элемент ИЛИ 32, вторую группу блоков 33 элементов И, группу схем 34 сравнения, узел 35 приорите- та активного процесса, третий элемен ИЛИ 36, вторую группу управляющих триггеров 37 , второй элемент 38 задержки, выходы 39 триггеров 24, группу выходов 40 формирователей 15, вы- ход 41 элемента 38 задержки, группу выходов 42 формирователей 29, группу выходов 43 триггеров 37, бло1 44 коммутации .

Узел 20 приоритетов процессов (фиг.4) содержит группу дешифраторов 45, группу элементов ИЛИ 46, группу элементов И 47, шифратор 48 и группу схем -49 сравнения.

Узел 44 коммутации (фиг.5) содержит каналы 50, каждый из которых включает в себя первую 51 и вторую 52 группы элементов И, регистр 53 и коммутатор 54, группу элементов ИЛИ 55.

Устройство работает следующим образом.

При организации процессов в вычислительной системе каждому из них вьщеляется необходимое число процессоров, один из которых является центральным (активным), и определяется приоритет процесса при установлении межпроцессорного обмена.

Приоритет процесса задается приоритетными двоичными кодами натурального ряда чисел, причем наивысшим приоритетом обладает процесс с меньшим приоритетным кодом. Каждый процесс реализуется одним или несколькими процессорами, которым на этапе планирования вычислений устанавливаются одинаковые номера. Это дает 1

возможность при организации обменов запросы сопровождать номером процесса. В каждом процессе активный процессор формирует сигна.пы запросов, а остальные его процессоры (пассивные) - сигналы готовности. Таким образом, если вычислительная система содержит п процессоров и в ней организуется р процессов (), то р процессорам разрешается формировать сигналы запросов, а (п-р) процессорам - сигналы готовности. Сигналы запросов и готовности сопровождаются номером процесса и фиксируются в соответствующем управляющем регистре 12 (фиг.З),

Каждый управляющий регистр 12 содержит два триггера, хранящих сигналы запроса Т и готовности Т, и регистр для хранения, двоичного кода номера процесса. .

Функцию присвоения приоритетов мбжет взять на себя любой из процессоров, входяш11х в вычислительную систему, который в данный момент является центральным. При этом блок 4 рассматривается как абонент для процессора, присваивающего приоритеты. Процессор вьщает код приоритета, который через соответствующий интерфейсный блок 2 поступает по шинам 5 на вход коммутатора 10 (фиг.1 и 2) и далее в соответствующий регистр I 1 по управляющему сигналу на линиях 7

Межпроцессорный обмен начинается с фазы установления связи между процессорами, выделенными процессу. Установление связи происходит в соответствии с присвоенными приоритетами процессорам. Выбор приоритетного процесса -происходит следующим образом.

Исходное состояние устройства характеризуется тем, что триггер 26, регистры 16 и 31, триггеры 24 и 37 (фиг.З) и регистры 53 каналов 50 (фиг.З) установлены в состояние О (цепи установки не показаны).

При необходимости установления связи активными процессорами по пш- нам 8 в регистры 12 заносятся сигналы запросов в триггеры Т и коды номеров процессов, а пассивными процессорами по шинам 8 - сигналы готовности в триггеры 12 и коды номеров процессов.

Так как триггеры 26, 24 и 37 находятся в нулевом состоянии, то в ре- гистрах 16 и 31 с помощью открытвгх элементов И 13 и 30 производится отслеживание состояния триггеров Т и Tj регистров 12. При наличии в регистрах 16 и 31 единичных сигналов через соответствующие элементы РШИ 1 и 32 открывается элемент И 28 и первым импульсом генератора 25 триггер 26 устанавливается в состояние 1. При этом элементы И 13 и 30 закрываются , чем фиксируются сигналы в регистрах 16 и 31 на момент выбора приоритетного процесса.

Единичные сигналы с выходов регистра 16 и триггера 26.по входам 18 и 19 соответственно подаются в узел 20, по входам 9 которого поступают приоритетные коды из блока 4. В узле 20 (фиг.4) коды приоритетов посредством открытых по соответствующим входам 18 дешифраторов 45 преобразуются в позиционные. Одноименные выходы дешифраторов 45 объединяются одноименными элементами ИЛИ 46. С помощью элементов И 47, включенных с выходами элементов ИЛИ 46 по приоритетной схеме, производится выделение приоритетной младшей единицы и формирование кода на выходах

шифратора 48. Посредством схем 49 сравнения определяется приоритетный источник запроса, т.е. приоритетный процесс, Сигнал от соответствующей схемы 49 сравнения формируется на соответствующем выходе 21. Этим сигналом открываются элементы И блоков 22J и на объединенных выходах блоков

22 формируется двоичный код номера приоритетного процесса. Этот код поступает на входы схем 34 сравнения. На другие входы схем 34 сравнения через соответствующие открытые сигнаg лами готовности регистра 31 блоки 33 поступают коды номеров процессов, пассивные процессоры которых выставили сигналы готовности к обмену. При этом возможны два случая:

Q сигналы готовности приняты в ре - гистр 31 от пассивных процессоров, не относящихся к выделенному приоритетному процессу;

в регистре 31 зафиксированы один

5 или более сигналов готовности пассивных процессоров, ОТНОСЯ1ЦИХСЯ к выделенному приоритетному процессу.

В первом случае через некоторое время, определяемое элементом 27 заQ держки, устанавливается в состояние о триггер 26. По единичному сигналу с нулевого выхода триггера 26 в регистры 16 и 31 принимаются сигналы запросов и готовности из регистров 12. По следующему сигналу генератора 25 делается очередная попытка установления связи.

Во втором случае единичным сигналом с выхода-элемента ИЛИ 36 открыQ ваются элементы И 23. Одновременно

при наличии нескольких единичных сигналов на выходах схем 34 сравнения с помощью узла 35 выделяется крайняя левая единица из позиционноg го кода выходных сигналов схем 34 сравнения.

Задержанным сигналом с выхода элемента 27 задержки устанавливаются в состояние 1 соответствующие триг0 геры 24 и 37 и в состояние О - через соответствующий элемент И 14 разряд регистра 16, соответствующий триггер регистра 31 и триггер 26. Единичными сигнапами с нулевых выхо5 дов триггеров 24 и 37 закрываются соответствующие элементы И 14 и 30, чем блокируется прием в них единичных сигналов из регистра 13 в нулевом состоянии триггера 26.

5

Выходные сигналы триггеров 24 и 37 используются для коммутации входов и выходов активного и пассивного процессов в узле 44 комьгутации.

Пусть в единичное состояние установлены триггеры 24 и 37 . Это означает, что по сигналу запроса выходы первого процессора должны быть скоммутированы с входами п-го процессора, выходы которого, в свою очередь, должны быть подключены к входам 1-го процессора. Эта задача выполняется блоком 44 следующим образом. Единичным сигналом с входа 39 (фиг,5) открыты элементы И 52 в канале 50, и элемент И 51 в канале . Единичным сигналом с входа 43п открыт элемент И 52., в канале 50у и элементы И 51 в канале ,.

Через время задержки, определяемое элементом 38 (фиг.З), триггеры 53 п.t в канале 50, и 53 в канале 50п устанавливаются в состояние Ь. При этом шины 5., первого процессора коммутатором 54 подключаются к минам 6, шины 5 коммутатором 54 подключаются к шинам 6, чем обеспечивается двухсторонняя связь первого процессора с п -м. Период псвторекия импульсод генератора 25 выбирается с учетом параметров элементов 27 и 38 задержки.

Одновременно с установкой в состояние 1 одного из триггеров 24 задержанным сигналом с выхода элемента 27 задержки сбрасывается в О соответствующие разряды регистров 16 и 31 через одноименные элементы И 14 и 30 и триггер 26.

В дальнейшем по единичному сигналу с нулевого выхода триггера 26 разрешается прием сигналов готовности из регистра 12 в соответствующие

разряды регистра 16, не заблокирован- g группы элементов И, узел приоритета

ные по единичному входу элементами И 13, закрытые нулевыми сигналами с нулевых выходов соответствующих триггеров 24. Аналогично блокируется прием сигналов готовности в разряды регистра 31.

По очередному импульсу генератора 25 при нгличии сигналов в регистрах 16 и 31 устанавливается в 1 триггер 26, определяя следующий цикл по обслуживанию приоритетного процесса.

По окончании обмена сигналы запросов и готовности снимаются. При

этом соответствуюище триггеры регистра 12 устанавливаются в состояние о. Перепады потенциалов на нулевых выходах дифференцируются соответствующими элементами 15 и 29, положительными сигналами с выходов которых устанавливаются в состояние о соответствующие триггеры 24 и 37 и в узле 44 триггеры 53 соответствующих каналов через элементы ИЛИ 55.

Формула изобретения

Устройство для сопряжения процессоров в вычислительной системе,содержащее группу интерфейсных блоков усилителей, входы-выходы которых являются группой входов-выходов устройства для подключения к входам-выходам соответствующих процессоров вычисли-, тельной системы, блок регистров приоритета, группа информационных и группа синхровходов которого соединены соответственно с информационными выходами и выходом сигнала запроса интерфейсных блоков усилителей группы, узел коммутации соединения, включающяй блок коммутации, группы информационных входов и выходов которого подключены соответственно к информационным выходам и входам интерфейсных блоков усилителей группы, и узел

приоритетов процессов, группа инфор- мационных входов которого соединена с группой выходов блока регистров приоритета, отличающееся тем, что, с целью расширения области применения устройства за счет адаптивной коммутации процессов при выполнении шогозадачных программ, в узел коммутации соединения введены группа управляющих регистров, четыре

активного процесса, две группы формирователей импульса, буферный регистр запросов, буферный регистр готовности, две группы блоков элементов И,

gQ две группы управляющих триггеров, группа схем сравнения, два элемента задержки, три элемента ИЛИ, элемент И, триггер управления и генератор, импульсов, причем информационные

gg входы управляющих регистров группы соединены с входами-выходами соответствующих интерфейсных блоков усилителей, первый и второй адресные входы узла коммутации подключены со

ответственно к единичным выходам триггеров первой и второй групп, нулевые входы которых соединены соответственно с первым и вторым входами сброса узла коммутации и через соответствующие формирователи импульса первой и второй групп к инверсным выходам разрядов запроса и готовности управляющих регистров групп, прямые выходы разрядов запросов которых подключены к первым входам элементов И первой группы, а выходы разрядов кода номера задачи - к информационным входам блоков элементов И первой и второй групп, выходы которых подключены соответственно к первым и вторым входам схем сравнения группы, управляющие входы блоков элементов И первой группы подключены к группе выходов узла приоритетов процессов и первым входам элементов И второй и первой групп, вторые входы которых соединены с нулевым входом триггера управления, выходом первого элемента задержки и через второй элемент задержки с входом стробирования узла коммутации, выходы элементов И третьей и второй груп подключены соответственно к единич- ным входам управляющих триггеров первой группы и группе нулевых входов буферного регистра запросов, группа единичных входов и группа выходов которого соединены соответственно с выходами элементов И первой группы, с группой входов первого элемента ИЛИ и группой разрешающих

5

5 О

0

5

входов узла приоритета процессов, синхронизирующим входом соединенного с единичным выходом триггера управления, единичный вход которого под- .ключен к входу первого элемента задержки и выходу элемента И, первый, второй и третий входы которого соединены соответственно с выходами генератора импульсов, первого и второго элементов ИЛИ, группа входов которого соединена с управляющими входами блоков элементов И второй группы и группой выходов буферного регистра готовности, группа единичных входов которого соединена с выходами элементов И четвертой группы, первые входы которых подключены к единичным разрядам готовности управляющих регистров группы, нулевые выходы управляющих триггеров первой и второй групп соединены соответственно с вторыми входами элементов И первой и четвертой групп, третьими входами подключенных к нулевому выходу триггера управления, третьи входы элементов И третьей группы соединены с выходом третьего элемента ИЛИ, группа входов которого подключена к выходам схем сравнения группы и группе запросных входов узла приоритета активного процесса, синхронизирующий вход которого соединен с выходом первого элемента задержки, а группа выходов - с единичными входами управляющих триггеров второй группы и группой нулевых входов буферного регис тра готовности.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для связи процессоров в вычислительной системе | 1988 |

|

SU1515170A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для распределения групповых заявок по процессорам | 1985 |

|

SU1254485A1 |

| Устройство приоритета для выбора групповых заявок | 1985 |

|

SU1319030A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для распределения заявок по процессорам | 1982 |

|

SU1121671A1 |

| Устройство для сопряжения | 1978 |

|

SU813401A2 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорньк вычислительных системах для реализации межзадачного взаимодействия. Цель изобретения - расширение области применения за счет адаптивной коммутации процессоров при выполнении многозадачных программ. Устройство содержит группу интерфейсных блоков 2 . усилителей, узел 3 коммутации соединения, блок 4 регистров приоритета, включающий узел коммутации и группу регистров приоритета. Новым в устройстве является введение в узел 3 группы управляющих регистров, четырех групп элементов И, двух групп формирователей импульса (дифференцирующих элементов), буферного регистра запросов, буферного регистра готовности, двух групп блоков элементов И, двух групп управляющих триггеров, группы схем сравнения, двух элементов задержки, трех элементов ИЛИ, элемента И, триггера управления, генератора импульсов и узла приоритетов активных процессов. 5 ил. i СЛ М ОР ю к

| Устройство для сопряжения вычислительныхМАшиН | 1978 |

|

SU840867A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения вычислительных машин | 1983 |

|

SU1130855A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-23—Публикация

1985-08-06—Подача