Изобретение относится к области определения характеристик узкополосных случайных процессов, предназначено для оперативной оценки модуля и аргумента междупериодного коэффициента корреляции флюктуирующих периодических сигналов, в том числе при появлении в выборке аномальных сигналов (импульсных помех 5 и может использоваться в системах измерительной техники, связи и автоматического управления.

Цель изобретения - повышение точности .

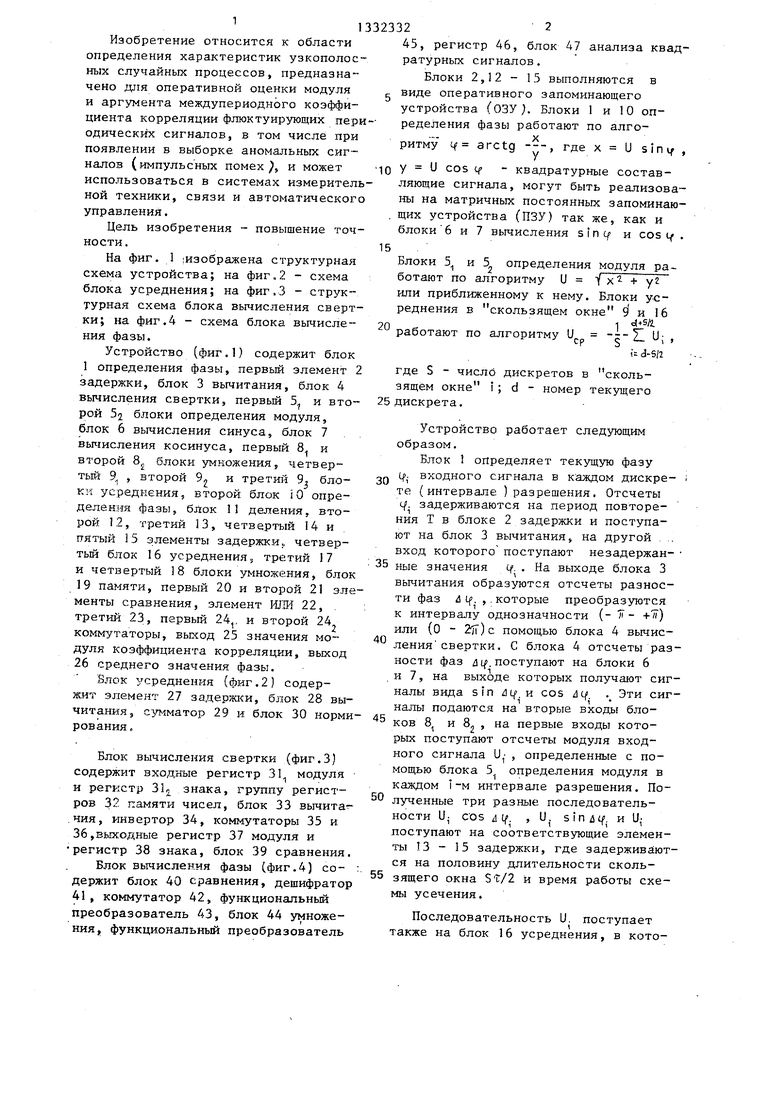

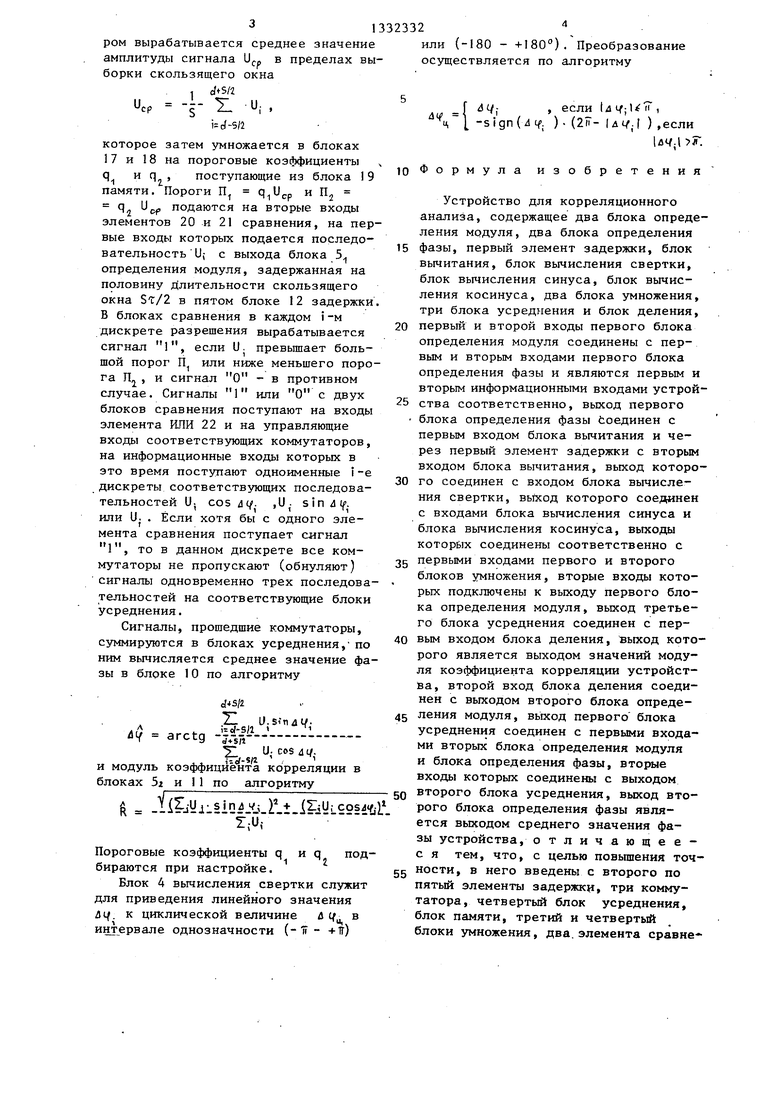

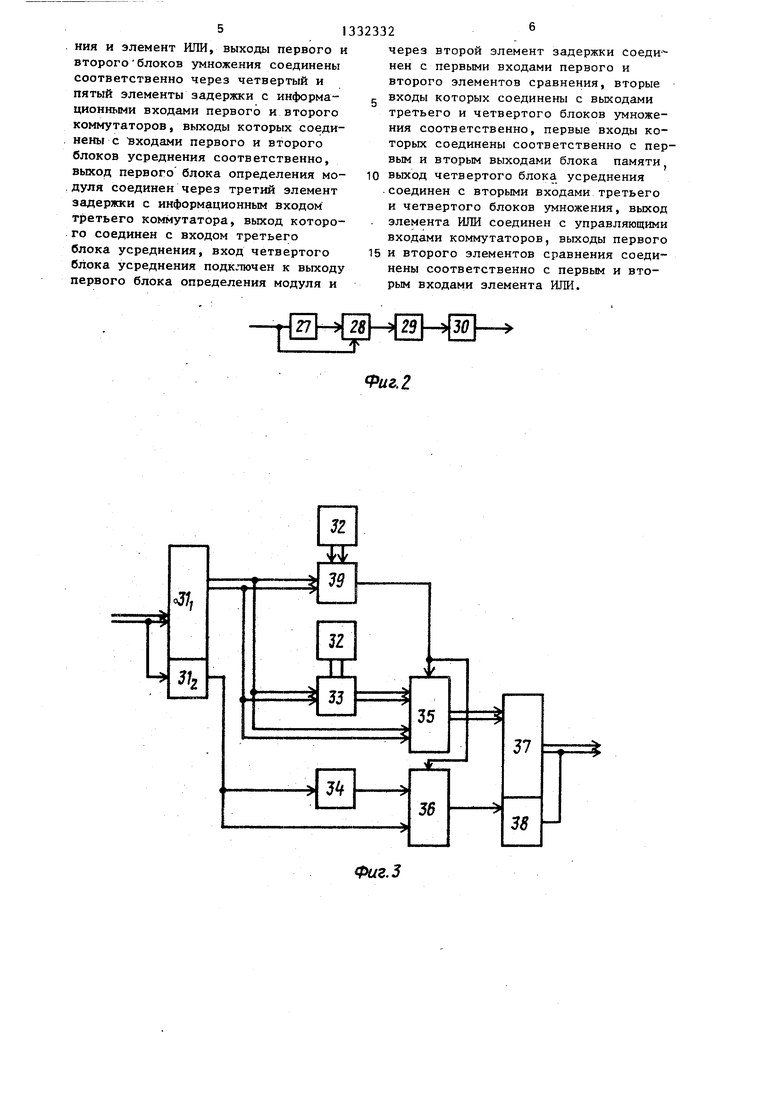

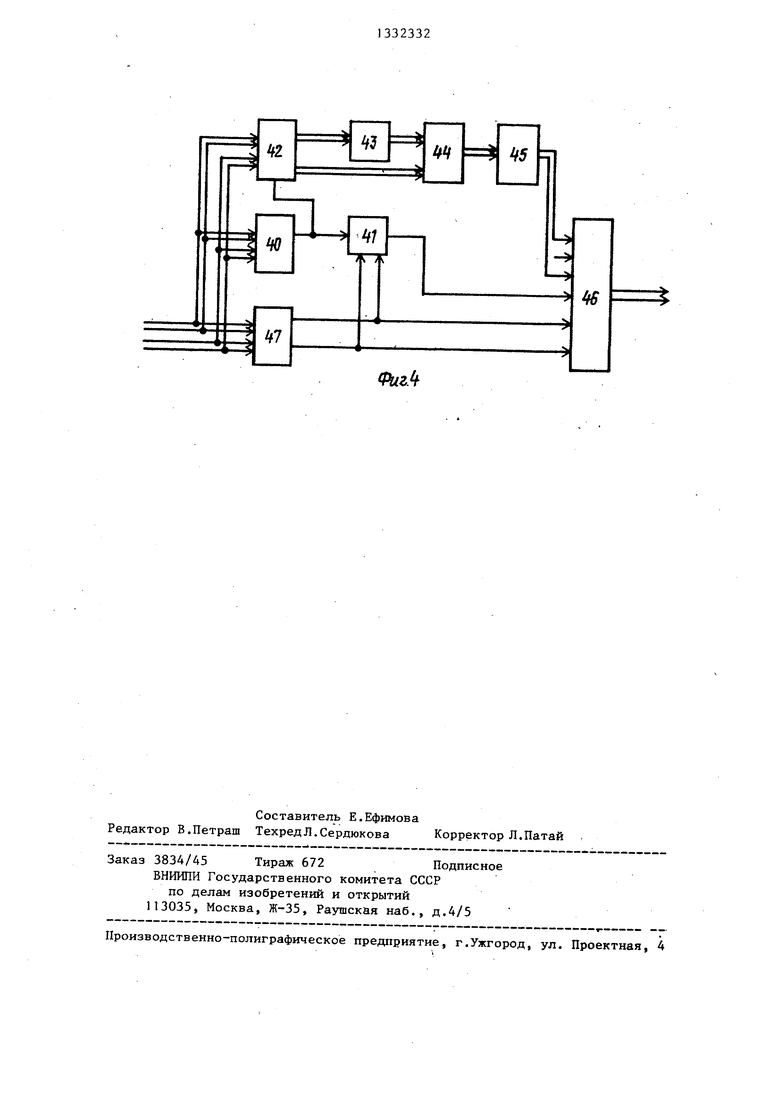

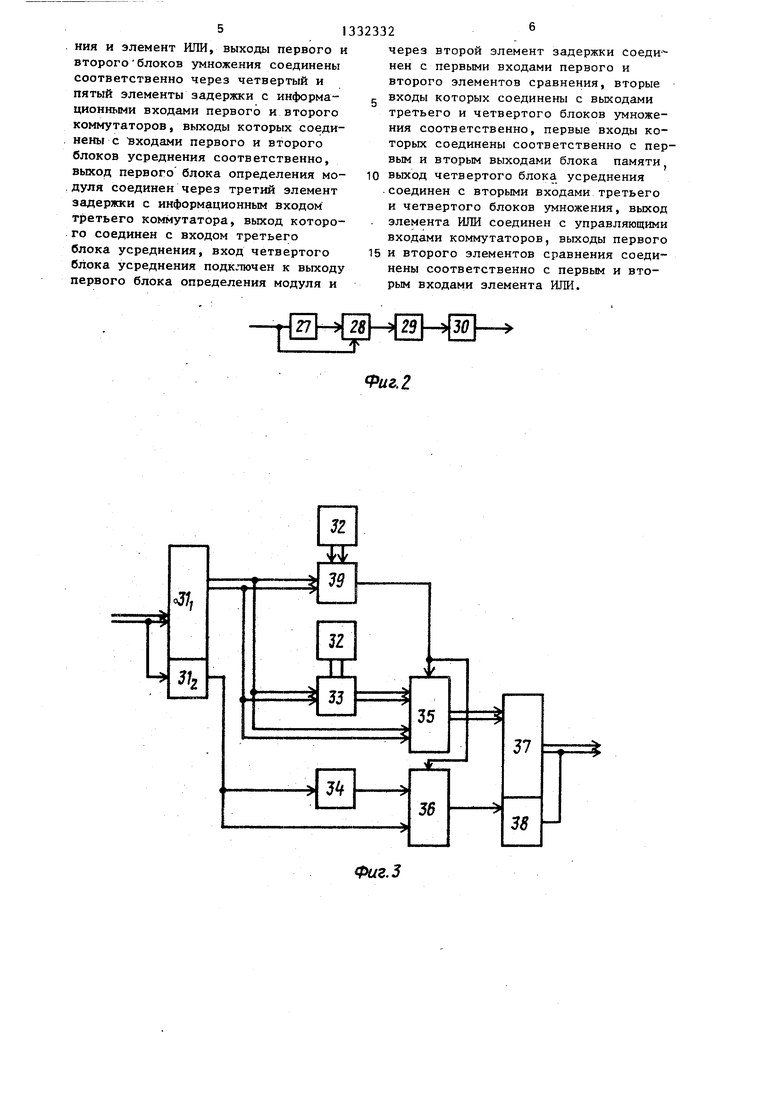

На фиг. 1 ;изображена структурная схема устройства; на фиг,2 - схема блока усреднения; на фиг.З - структурная схема блока вычисления свертки; на фиг.4 - схема блока вычисления фазы.

Устройство (фиг.1) содержит блок I определения фазы, первый элемент 2 задержки, блок 3 вычитания, блок 4 вычисления свертки, первый 5 и второй Sj блоки определения модуля, блок 6 вычисления синуса, блок 7 вычисления косинуса, первый 8 и

10

45, регистр 46, блок 47 анализа квадратурных сигналов.

Блоки 2,12 - 15 выполняются в виде оперативного запоминающего устройства (ОЗУ. Блоки 1 и 10 определения фазы работают по алго-.X

ритму tf arctg -, где х U sinif ,

у и cos If - квадратурные составляющие сигнала, могут быть реализованы на матричных постоянных запоминающих устройства (ПЗУ) так же, как и блоки 6 и 7 вычисления sine/ и cos ( .

15

Блоки 5 и 5 ботают по алгоритму

определения модуля ра

и

If х + уг или приближенному к нему. Блоки усреднения в скользящем окне 9 и 16

п1

работают по алгоритму U U; ,

; d-s/2

где S - число дискретов в скользящем окне 25 дискрета.

d номер текущего

второй 8 блоки умножения 5 четвертый 9, , второй 9„ и третий 9, блоки усреднения, второй блок iO определения фазы, блок 11 деления, второй 1.2, третий 13, четвертый 14 и . пятый 15 элементы задержки,, четвер- тьм блок 16 усреднения, третий 17 и четвертый 18 блоки умножения, блок 19 памяти, первый 20 и второй 21 эле менты сравнения, элемент ЮШ 22, . третий 23, первый 24,, и второй 24 коммутаторы, выход 25 значения модуля коэффициента корреляции, выход 26 среднего значения фазы.

Блок усреднения (фиг.2) содержит элемент 27 задержки, блок 28 вычитания, сумматор 29 и блок 30 рования,

30

Блок вычисления свертки (фиг.З) содержит входш 1е регистр 31 модуля и регистр 31j знака, группу регистров 32 памяти чисел, блок 33 вьгчита

.чия, инвертор 34, коммутаторы 35 и 36,выходные регистр 37 модуля и

регистр 38 знака, блок 39 сравнения. Блок вычисления фазы (фиг.4) содержит блок 40 сравнения, дешифратор 41, коммутатор 42, функциональньй преобразователь 43, блок 44 умножения, функциональный преобразователь

Устройство работает следующим образом.

Блок 1 определяет текущую фазу Lf. входного сигнала в каждом дискре- те (интервале ) разрешения. Отсчеты с/, задерживаются на период повторения Т в блоке 2 задержки и поступают на блок 3 вычитания, на другой . .. вход которого поступают незадержан- 35 ные значения t. , На выходе блока 3 вычитания образуются отсчеты разности фаз If. ,. которые преобразуются к интервалу однозначности (- Т - ) или (о - 25Г)с помощью блока 4 вычисления свертки. С блока 4 отсчеты разности фаз л 1. поступают на блоки 6 и 7, на выходе которых получают сигналы вида sin JY. и cos л с/. . Эти сигналы подаются на вторые входы бло- норми- 45 ков 8 и 8. , на первые входы которых поступают отсчеты модуля входного сигнала U-, определенные с по40

50

55

мощью блока 5 определения модуля в каждом i-м интервале разрешения. Полученные три разные последовательности и cos л If. , и. . и U; поступают на соответствующие элементы 13 - 15 задержки, где задерживаются на половину длительности скользящего окна ST/2 и время работы схемы усечения.

Последовательность U. поступает также на блок 16 усреднения, в кото

45, регистр 46, блок 47 анализа квадратурных сигналов.

Блоки 2,12 - 15 выполняются в виде оперативного запоминающего устройства (ОЗУ. Блоки 1 и 10 определения фазы работают по алго-.X

ритму tf arctg -, где х U sinif ,

у и cos If - квадратурные составляющие сигнала, могут быть реализованы на матричных постоянных запоминающих устройства (ПЗУ) так же, как и блоки 6 и 7 вычисления sine/ и cos ( .

Блоки 5 и 5 ботают по алгоритму

определения модуля ра

и

If х + уг или приближенному к нему. Блоки усреднения в скользящем окне 9 и 16

п1

работают по алгоритму U U; ,

; d-s/2

где S - число дискретов в скользящем окне 25 дискрета.

d номер текущего

50

55

мощью блока 5 определения модуля в каждом i-м интервале разрешения. Полученные три разные последовательности и cos л If. , и. . и U; поступают на соответствующие элементы 13 - 15 задержки, где задерживаются на половину длительности скользящего окна ST/2 и время работы схемы усечения.

Последовательность U. поступает также на блок 16 усреднения, в котором вырабатывается среднее значение амплитуды сигнала 1). в пределах выборки скользящего окна

1

c/tS/2

-S-- Т.

i c/-S/2

и.

которое затем умножается в блоках 17 и 18 на пороговые коэффициенты

q и q

г

поступающие из блока 19

памяти. Пороги П ..

и П2

q Upp подаются на вторые входы элементов 20 и 21 сравнения, на первые входы которых подается последовательность U; с выхода блока 5 определения модуля, задержанная на половину длительности скользящего окна 5т/2 в пятом блоке 12 задержки В блоках сравнения в каждом i-м дискрете разрешения вырабатывается сигнал 1, если U. превьшает большой порог П или ниже меньшего порога Л , и сигнал О - в противном случае. Сигналы 1 или О с двух блоков сравнения поступают на входы элемента ИЛИ 22 и на управляющие входы соответствующих коммутаторов, на информационные входы которых в это время поступают одноименные i-е дискреты соответствующих последовательностей U; cos Л(/. ,(i sin , или и. . Если хотя бы с одного элемента сравнения поступает сигнал 1, то в данном дискрете все коммутаторы не пропускают (обнуляют) сигналы одновременно трех последовательностей на соответствующие блоки усреднения.

Сигналы, прошедшие коммутаторы, суммируются в блоках усреднения, по ним вычисляется среднее значение фазы в блоке 10 по алгоритму

21 U.Si ndt/.

jr d-Bn

.cosdt/.

и модуль коэффициента корреляции в блоках 5z и 11 по алгоритму

й({ arctg

40 вым входом блока деления, выход которого является выходом значений модуля коэффициента корреляции устройства, второй вход блока деления соединен с выходом второго блока опреде45 ления модуля, выход первого блока усреднения соединен с первыми входами вторых блока определения модуля и блока определения фазы, вторые входы которых соединены с выходом

,50 второго блока усреднения, выход втой 11 лУл151 0 1 1 11-::У159§1 {)1- рого блока определения фазы являи q под.-и,Пороговые коэффициенты q бираются при настройке.

Блок 4 вычисления свертки служит для приведения линейного значения й. к циклической величине d („ в интервале однозначности ( - +t)

ется выходом среднего значения фазы устройства, отличающее- с я тем, что, с целью повышения точ- 55 кости, в него введены с второго по пятый элементы задержку, три коммутатора, четвертый блок усреднения, блок памяти, третий и четвертый блоки умножения, два.элемента сравне

или (-180 - +180°), Преобразование осуществляется по алгоритму

й(

Г 4i/,- , если {u - it i , -signC tf. ) (2F- |д1/.| ) ,если

.

Формула изобретения

Устройство для корреляционного анализа, содержащее два блока определения модуля, два блока определения

фазы, первый элемент задержки, блок вычитания, блок вычисления свертки, блок вычисления синуса, блок вычисления косинуса, два блока умножения, три блока усреднения и блок деления,

первый и второй входы первого блока определения модуля соединены с первым и вторым входами первого блока определения фазы и являются первьм и вторым информационными входами устройства соответственно, выход первого блока определения фазы йоединен с первым входом блока вычитания и через первый элемент задержки с вторым входом блока вычитания, выход которого соединен с входом блока вычисления свертки, вьйсод которого соединен с входами блока вычисления синуса и блока вычисления косинуса, выходы которых соединены соответственно с

первыми входами первого и второго блоков умножения, вторые входы которых подключены к выходу первого блока определения модуля, выход третьего блока усреднения соединен с первым входом блока деления, выход которого является выходом значений модуля коэффициента корреляции устройства, второй вход блока деления соединен с выходом второго блока определения модуля, выход первого блока усреднения соединен с первыми входами вторых блока определения модуля и блока определения фазы, вторые входы которых соединены с выходом

ется выходом среднего значения фазы устройства, отличающее- с я тем, что, с целью повышения точ- 55 кости, в него введены с второго по пятый элементы задержку, три коммутатора, четвертый блок усреднения, блок памяти, третий и четвертый блоки умножения, два.элемента сравне

5I

ния и элемент ИЛИ, выходы первого и второго блоков умножения соединены соответственно через четвертый и пятый элементы задержки с информационными входами первого и второго коммутаторов, выходы которых соединены с входами первого и второго блоков усреднения соответственно, выход первого блока определения модуля соединен через третий элемент задержки с информационным входом третьего коммутатора, выход которого соединен с входом третьего блока усреднения, вход четвертого блока усреднения подключен к выходу первого блока определения модуля и

32332

через второй элемент задержки соеди- нен с первыми входами первого и второго элементов сравнения, вторые

g входы которых соединены с выходами третьего и четвертого блоков умноже- иия соответственно, первые входы ко- торьк соединены соответственно с первым и вторым выходами блока памяти 10 выход четвертого блока усреднения .соединен с вторыми входами третьего и четвертого блоков умножения, выход

. элемента ИЛИ соединен с управляющими входами коммутаторов, выходы первого

15 и второго элементов сравнения соединены соответственно с первым и вторым входами элемента ИЛИ.

Ф«г.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для корреляционного анализа (его варианты) | 1982 |

|

SU1038949A1 |

| Фазометр среднего значения набега фазы | 1977 |

|

SU737860A1 |

| Устройство для определения корреляционных функций | 1983 |

|

SU1101847A1 |

| Цифровой анализатор | 1979 |

|

SU834581A1 |

| Устройство для автоматизированной градуировки датчика силы | 1988 |

|

SU1606889A1 |

| Способ компенсации импульсных помех при обнаружении протяженных сигналов и устройство для его осуществления | 2017 |

|

RU2679010C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ СИГНАЛОВ С ДВУХКРАТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 1991 |

|

RU2007886C1 |

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Устройство для градуировки датчиков силы | 1989 |

|

SU1682845A1 |

| Фазометр доплеровского набега фазы радиоимпульсных сигналов | 1990 |

|

SU1748086A1 |

J/,

9

31,

33

35

56

38

Фиг.З

Фиг.

Авторы

Даты

1987-08-23—Публикация

1985-09-05—Подача