Изобретение относится к вычислиельной технике, а именно к исследоаниям графов, представляющих схемы ифровых блоков, проводимым для проерки логической правильности схем процессе их разработки и оценки ачества тестов , применяемых при роизводственном и эксплуатационом контроле цифровых блоков. .

Цель изобретения - повьшенйе быстродействия и точности.

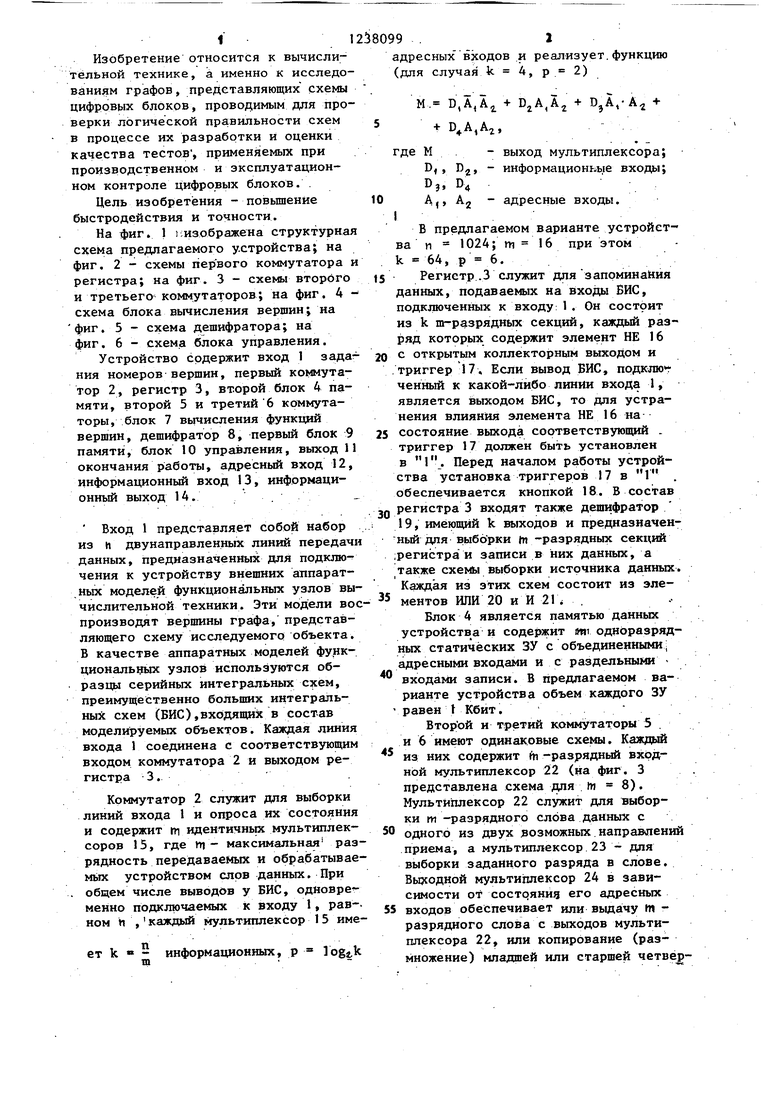

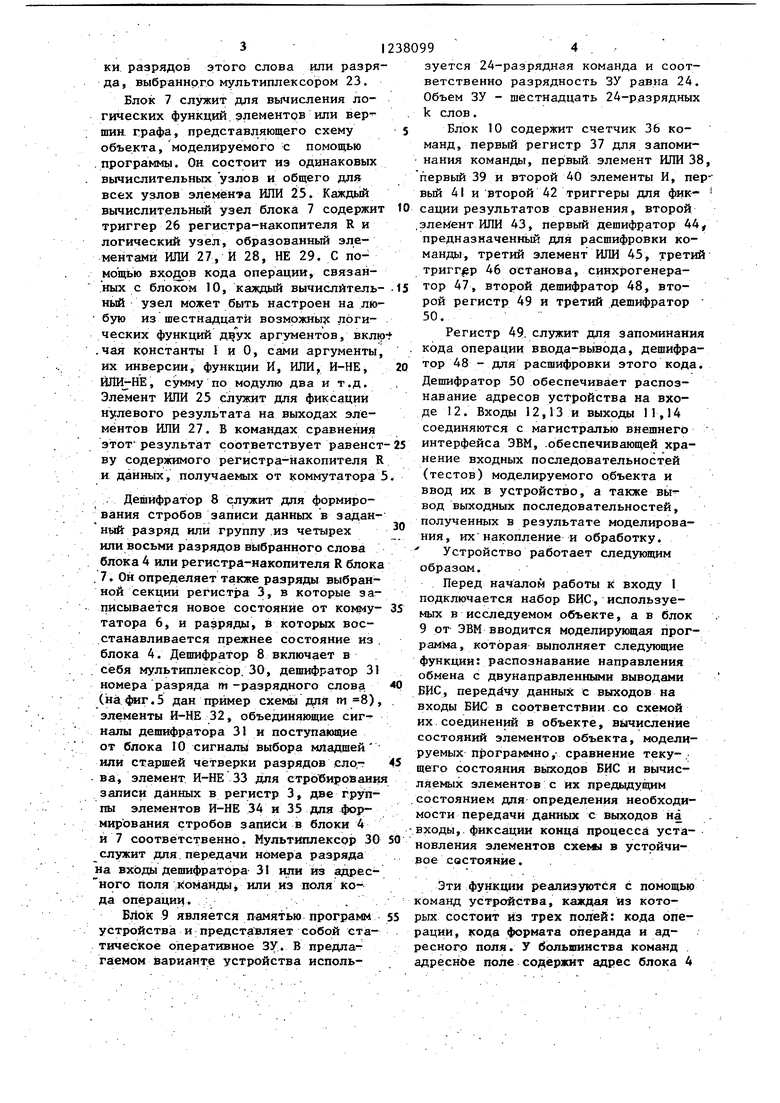

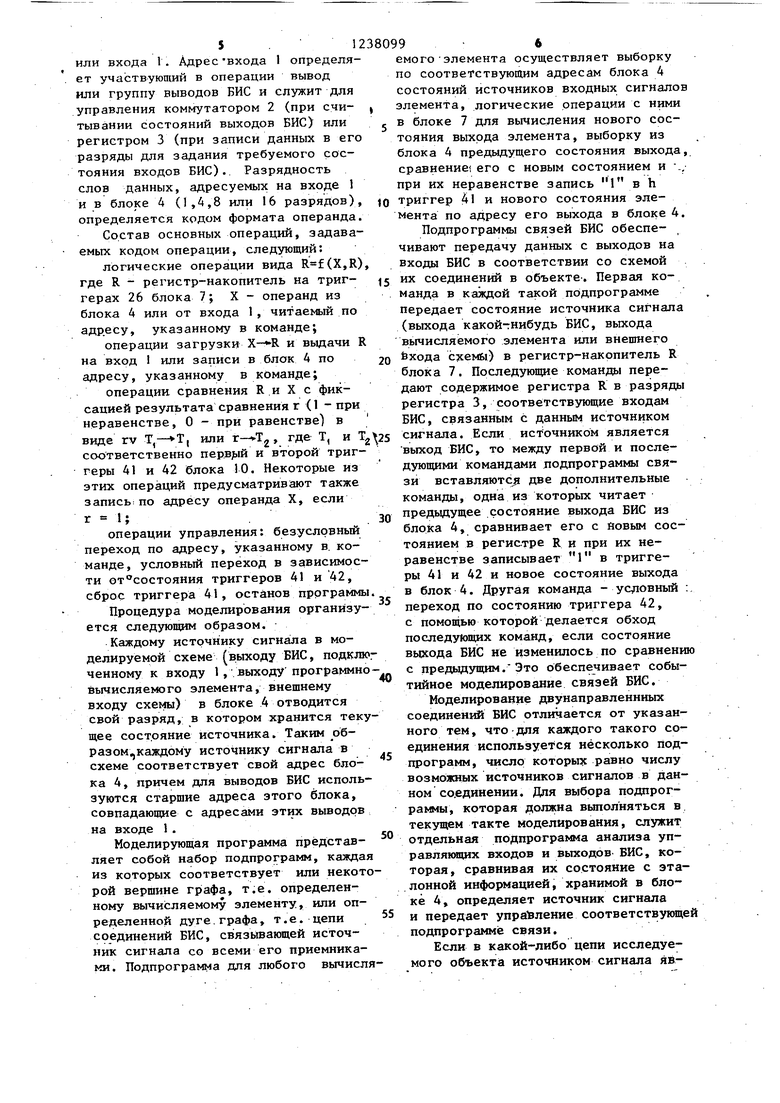

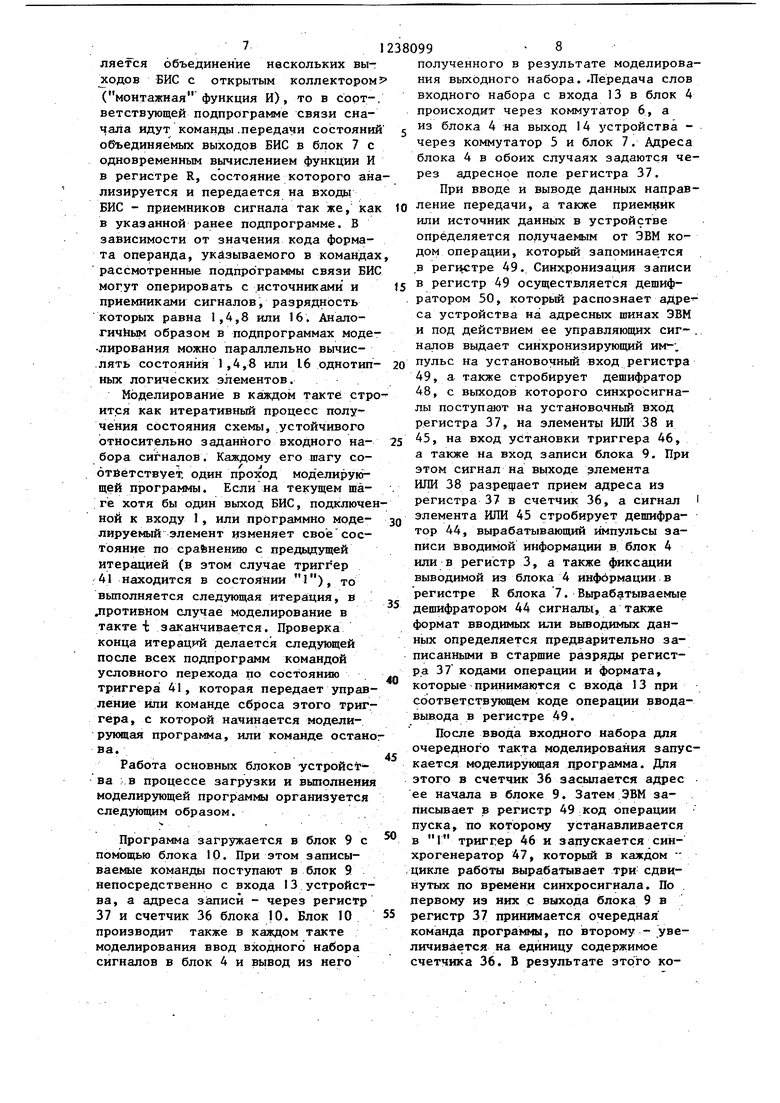

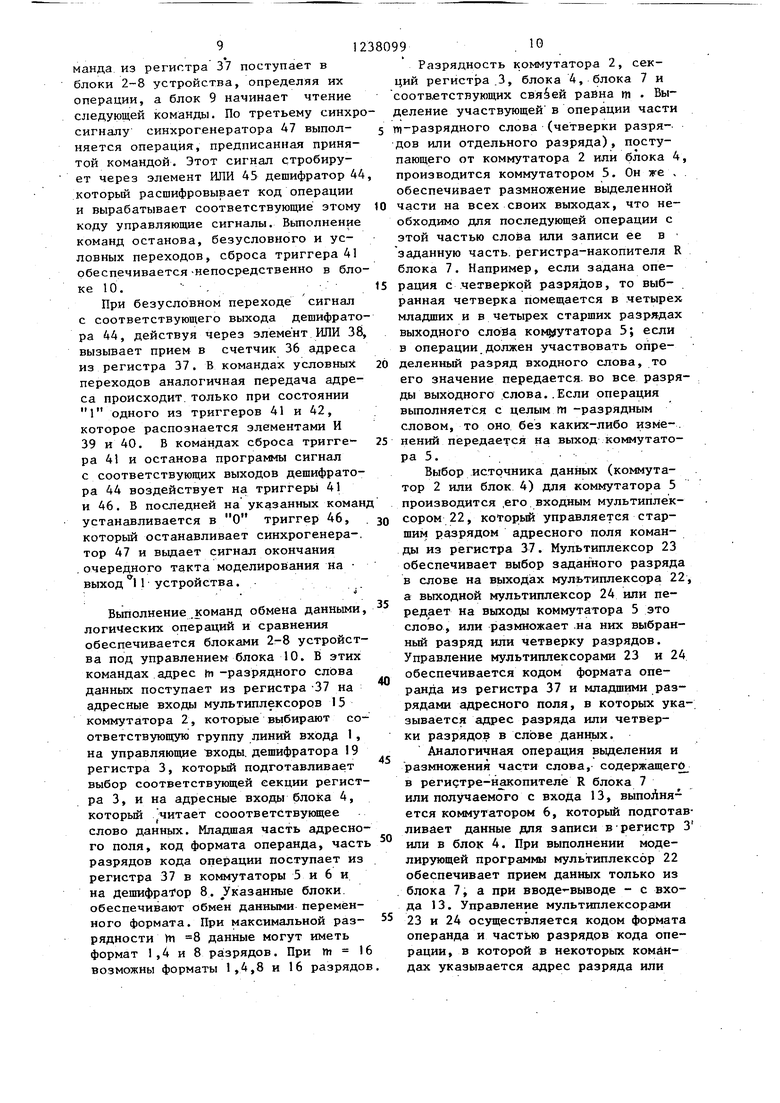

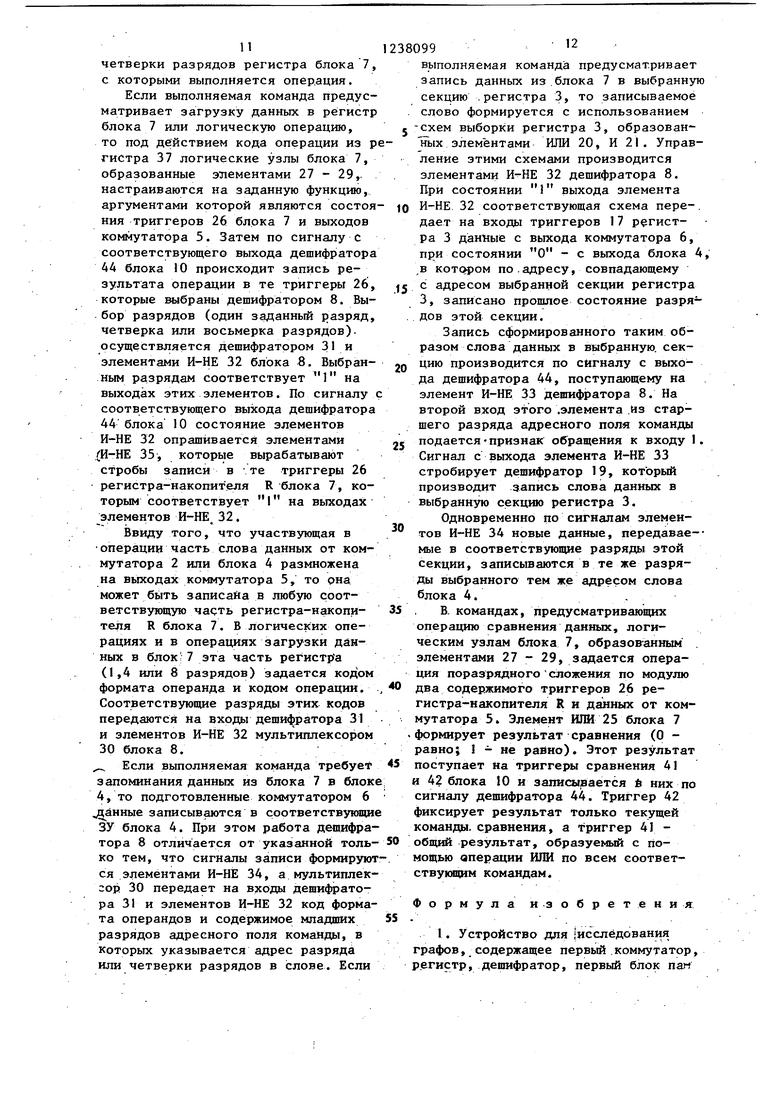

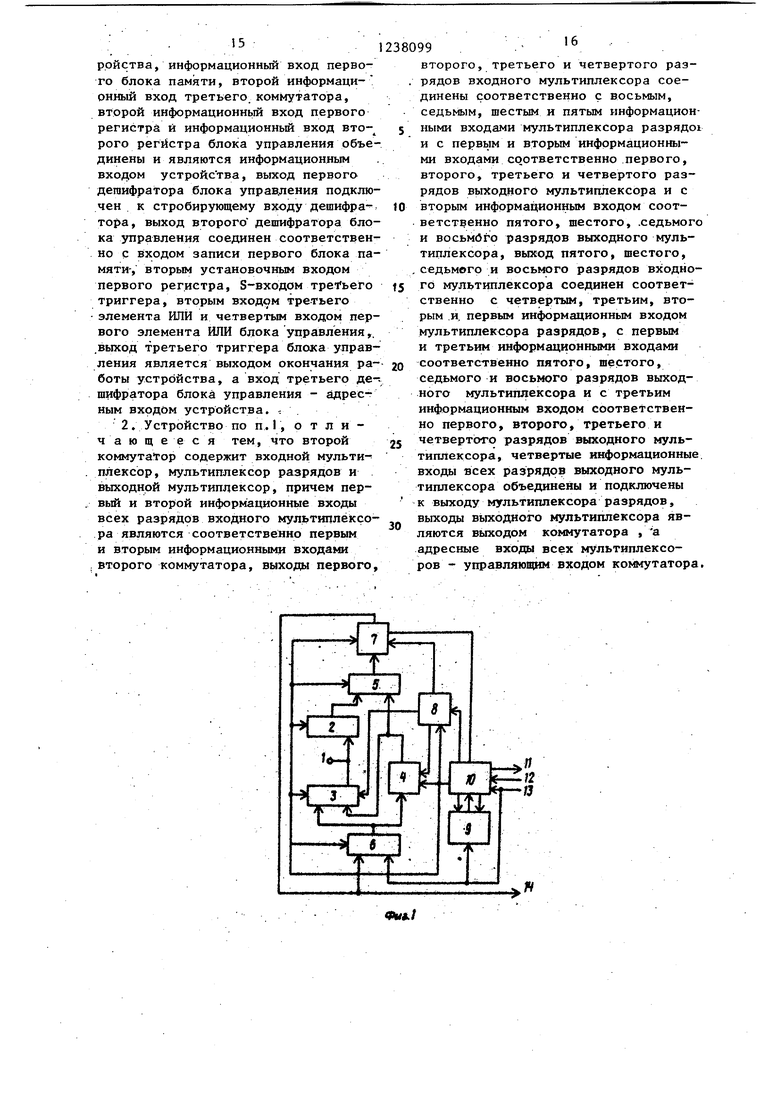

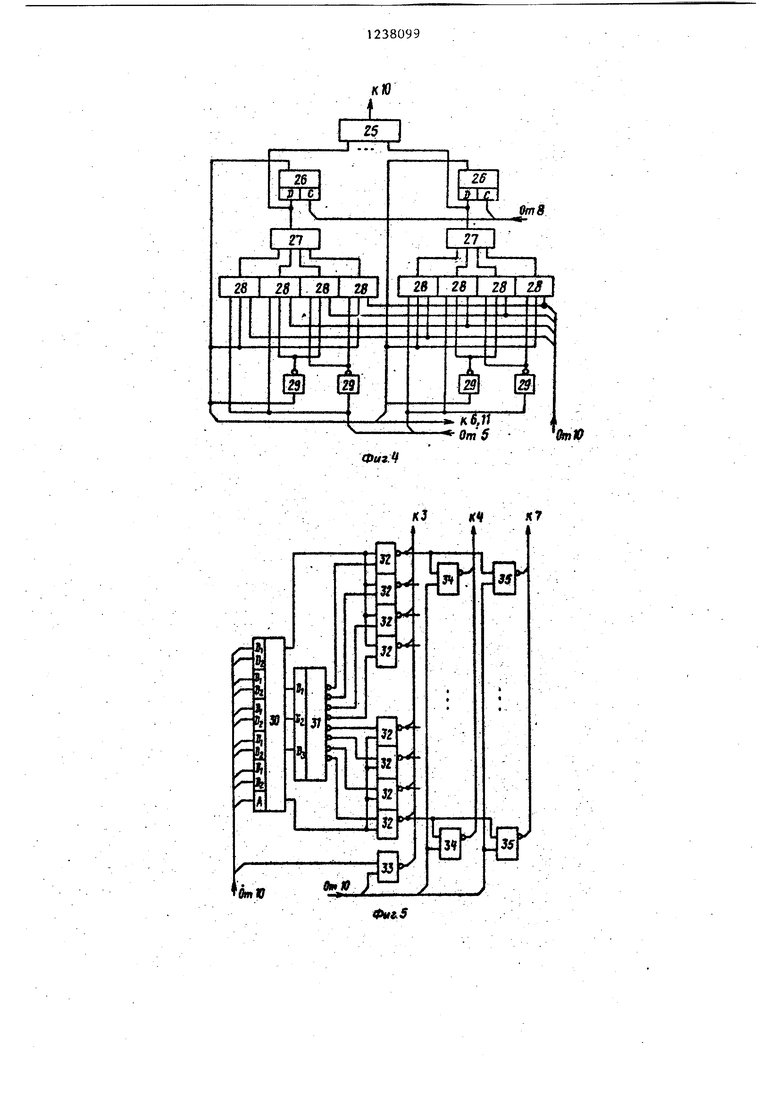

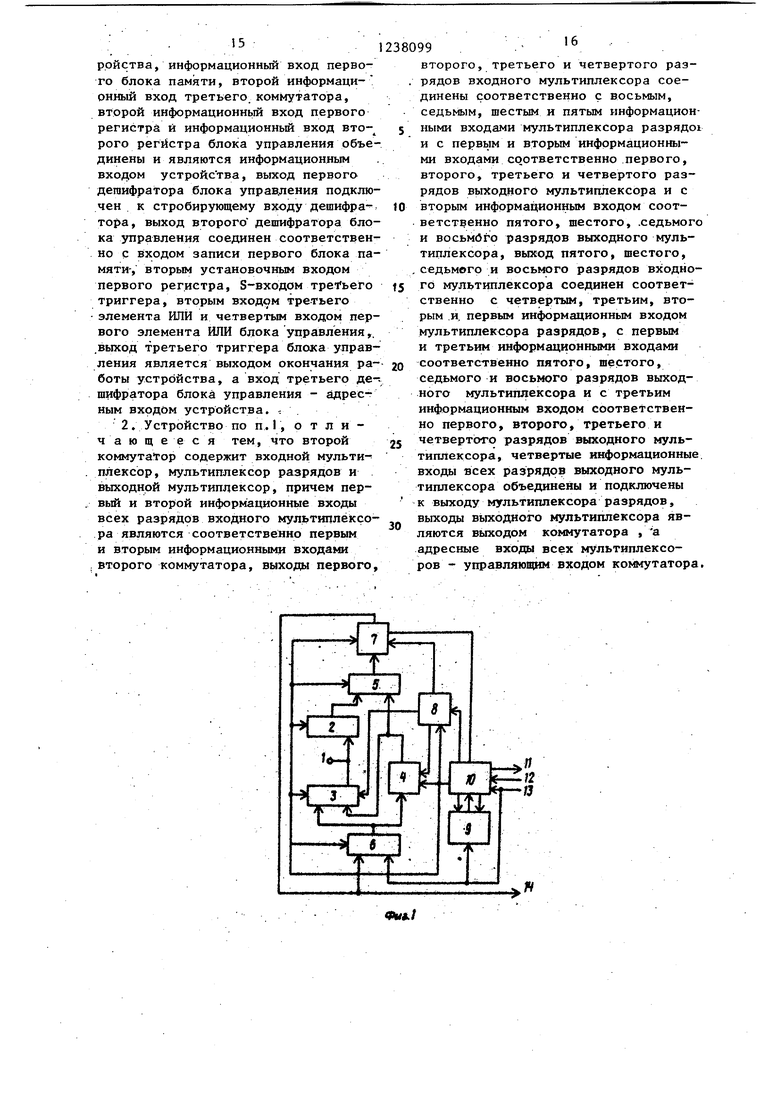

На фиг. 1 1;изображена структурная схема предлагаемого устройства} на фиг. 2 - схемы первого коммутатора и регистра; на фиг. 3 - схемы второго и третьего коммутаторов; на фиг. 4 - схема блока вычисления вершин; на фиг. 5 - схема дешифратора; на фиг. 6 - схема блока управления.

Устройство содержит вход 1 задания номеров вершин, первый коммутатор 2, регистр 3, второй блок 4 памяти, второй 5 и третий 6 коммутаторы, блок 7 вьгчисления функций вершин, дешифратор 8, первый блок 9 памяти, блок 10 управления, выход 11 окончания работы, адресный вход 12, информационный вход 13, информационный выход 14.

Вход 1 представляет собой набор из и двунаправленных линий передачи данных, предназначенных для подклю-г чения к устройству внешних аппаратных моделей функциональных узлов вычислительной техники. Эти модели воспроизводят вершины графа, представляющего схему исследуемого объекта. В качестве аппаратных моделей функ- циональщ 1х узлов используются образцы серийньпс интегральных схем, преимущественно больших интегральных схем (БИС),входящих в состав моделируемых объектов. Каждая линия входа 1 соединена с соответствующим входом коммутатора 2 и выходом регистра 3.

Коммутатор 2 служит для выборки линий входа 1 и опроса их состояния и содержит m идентичньрс мультиплексоров 15, где щ - максимальная разрядность передаваемых и обра(5атывае- мьпс устройством слов данных. При обцем числе выводов у БИС, одновре - менно подключаемых к входу 1, рав-- ном И , каждый мультиплексор 15 имеет k - информационных, р log.k m

адресных входов и реализует, функцию (для случая k 4, р 2)

М.

D,A,A +

D,A,A,

D,A,-A,

D,A,A

г

где M

выход мультиплексора;

I

« 2 информационьые Dj, D

А,, АЗ - адресные входы.

0

5

0

В предлагаемом варианте устройства и 1024; m 16 при этом k 64, р 6.

Регистр .3 служит для запоминания данных, подаваемых на выходы БИС, подключенных к входу:1. Он состоит из k ш-разрядных секций, каждый разряд которых содержит элемент НЕ 16 с открытым коллекторным выходом и .триггер 17. Если вывод БИС, подклю :- ченный к какой-либо линии входа 1, является выходом БИС, то для устранения влияния элемента НЕ 16 на состояние выхода соответствуюпщй . триггер 17 должен быть установлен в 1. Перед началом работы устройства установка триггеров 17 в Г обеспечивается кнопкой 18. В состав регистра 3 входят также дешифратор 19, имеющий k выходов и предназначенный для выборки (т -разрядных секций ;регистра и записи в них данных, а также схемы выборки источника данных. Каждая из этих схем состоит из элементов ИЛИ 20 и И 21; .

Блок 4 является памятью данных устройства и содержит ляг одноразрядных статических ЗУ с объединенными; адресными входами и с раздельными входа ш записи. В предлагаемом варианте устройства объем каждого ЗУ равен Кбит.

ВторЪй и третий коммутаторы 5 . и 6 имеют одинаковые схемы. Каждый из них содержит iti -разрядный входной мультиплексор 22 (на фиг. 3 представлена схема для m 8). Мультиплексор 22 служит для выборки m -разрядного слова данных с одного из двух возможных направлений приема, а мультиплексор 23 - для выборки заданного разряда в слове. Вьрсодной мультиплексор 24 в зависимости от состояние его адресных 5 входов обеспечивает или tn - разрядного слова с выходов мультиплексора 22, или копирование (размножение) младшей или старшей четвёр5

0

5

0

10

ки разрядов этого слова или разряда, выбранного мультиплексором 23.

Блок 7 служит для вычисления логических функций элементрв или вер- пган графа, представляющего схему объекта, моделируемого с помощью

программь. Он состоит из одинаковых вычислительных узлов и общего для всех узлов элемента ИЛИ 25. Каждый вычислительный узел блока 7 содержит триггер 26 регистра-накопителя R и логический узел, образованный элементами ИЛИ 27, И 28, НЕ 29. С помощью входов кода операции, связанных с блоком 10, каждый вычислитель- ный узел может быть настроен на любую из шестнадцати возможных логических функций двух аргументов, вклю-

чая константы 1 и О, сами аргументы, их инверсии, функции И, ИЛИ, И-НЕ, , сумму по модулю два и т.д. Элемент ИЛИ 25 служит для фиксации нулевого результата на выходах элементов ИЛИ 27. В командах сравнения этот результант соответствует равенст- 25 ву содержимого регистра-накопителя R и данных, получаемых от коммутатора 5.

15

20

Дешифратор 8 служит для формирования стробов записи данных в заданный разряд или группу .из четырех или восьми разрядов выбранного слова блока 4 или регистра-накопителя R блока

7. Он определяет также разряды выбранной секции регистра 3, в которые записывается новое состояние от коммутатора 6, и разряды, в которых восстанавливается прежнее состояние из . блока 4. Дешифратор 8 включает в

себя мультиплексор. 30, дешифратор 31 номера разряда m -разрядного Слова (на фиг.5 дан пример схемь для т В), элементы И-НЕ 32, объединяющие налы дешифратора 31 и поступающие от блока 10 сигналы выбора мпадшей или старшей четверки разрядов .слова, элемент И-НЕ 33 для стробирования

записи данных в регистр 3, две группы элементов И-НЕ 34 и 35 для формирования стробов записи в блоки 4 и 7 соответственно. Мультиплексор 30 50 служит для.передачи номера разряда а входы дешифратора 31 или из адрес- ного поля командыj или из поля кода операции;.

Блок 9 является памятью программ 55 устройства и представляет собой статическое оперативное ЗУ. В предла raieMOM варианте устройства исполь10

25 .

15

20

50

2380994 ,

зуется 24-разрядная команда и соответственно разрядность ЗУ равна 24. Объем ЗУ - шестнадцать 24-р.азрядных k слов.

Блок 10 содержит счетчик 36 команд, первый регистр 37 для запоминания команды, первый элемент ИЛИ 38, первый 39 и второй 40 элементы И, первый 41 и второй 42 триггеры для фик- сации результатов сравнения, второй .элемент ИЛИ 43, первый дешифратор 44/ предназначенный для расшифровки команды, третий элемент ИЛИ 45, третий триггер 46 останова, синхрогенера- тор 47, второй дешифратор 48, второй регистр 49 и третий дешифратор 50.

Регистр 49. служит для запоминания кода операции внода-вывода, дешифратор 48 - для расшифровки этого кода. Дешифратор 50 обеспечивает распознавание адресов устройства на входе 12. Входы 12,13 и выходы 11,14 соединяются с магистралью внешнего интерфейса ЭВМ, .обеспечивающей хранение входных последовательностей (тестов) моделируемого объекта и ввод их в устройство, а также вы вод выходных последовательностей, полученных в результате моделирования, их накопление и обработку. Устройство работает следующим образом.

Перед началом работы к входу 1 подключается набор БИС, используемых в исследуемом объекте, а в блок 9 от ЭВМ вводится моделирующая программа, которая выполняет следующие функции: распознавание направления обмена с двунаправленными выводами БИС, передачу данных с выходов на входы БИС в соответствии со схемой их соединений в объекте, вычисление состояний элементов объекта, моделируемых программно,- сравнение теку-, щего состояния выходов БИС и вычисляемых элементов:с их предьщущим состоянием для определения необходимости передачи данных с выходов на входы,, фиксации конца процесса установления элементов схеьш в устойчивое состояние. .

30

35

40

45

Эти функции реализуются с помощью команд устройства, каждая из которых состоит из трех полей: кода операции, кода формата операнда и адресного поля. У большинства команд адресное поле содержит адрес блока 4

или входа 1. Адрес входа 1 определя- ет участвующий в операции вывод или группу выводов БИС и служит для управления коммутатором 2 (при счи- тывании состояний выходов БИС) или регистром 3 (при записи данных в его разряды для задания требуемого состояния входов БИС).. Разрядность слов данных, адресуемых на входе 1 и в блоке 4 (1,4,8 или 16 разрядов), определяется кодом формата операнда. Состав основных операций, задаваемых кодом операции, следующий:

логические операции вида (X,R), где R - регистр-накопитель на триггерах 26 блока 7; X - операнд из блока 4 или от входа 1, читаемый по адр.есу, указанному в команде;

операции загрузки и выдачи R на вход 1 или записи в блок А по адресу, указанному в команде;

операции сравнения R и X с фиксацией результата сравнения г (1 - при неравенстве, О - при равенстве) в виде rv Т,, или , где Т, и соответственно и второй триггеры 41 и 42 блока 10. Некоторые из этих операций предусматривают также запись-по адресу операнда X, если г 1;

операции управления: безусловный переход по адресу, указанному в. команде, условньш переход в зависимости от°состояния триггеров 41 и 42, сброс триггера 41, останов программы. Процедура моделирования организуется следующим образом.

Каждому источнику сигнала в моделируемой схеме (выходу БИС, подклю: ченному к входу 1, выходу программно- вьмисляемого элемента, внешнему входу схеьял) в блоке 4 отводится свой разряд, в котором хранится текущее состояние источника. Таким образ ом,, каждому источнику сигнала в схеме соответствует свой адрес блока 4, причем для выводов ВИС используются старшие адреса этого блока, совпадающие с адресами этих выводов на входе 1.

Моделирующая программа представляет собой набор подпрограмм, каждая из которых соответствует или некоторой вершине , т.е. определенному вычисляемому элементу, или определенной дуге.графа т.е. цепи срединений БИС, связывающей источник сигнала со всеми его приемниками. Подпрограмма для любого вычисля

20

5

емого элемента осуществляет выборку по соответствующим адресам блока 4 состояний источников входных сигналов элемента, логические операции с ними J в блоке 7 для вычисления нового состояния выхода элемента, выборку из блока 4 предыдущего состояния выхода, сравнение1 его с новым состоянием и , при их неравенстве запись 1 в h

JO триггер 4l и нового состояния элемента по адресу его выхода в блоке 4.

Подпрограммы связей БИС обеспечивают передачу данных с выходов на входы БИС в соответствии со схемой

J5 их соединений в объекте. Первая команда в каждой такой подпрограмме передает состояние источника сигнала (выхода какой-нибудь БИС, выхода вычисляемого элемента или внешнего Ьхода схемы) в регистр-накопитель R блока 7. Последующие команды передают содержимое регистра R в разряды регистра 3, соответствующие входам БИС, связанным с данным источником сигнала. Если источником является выход БИС, то мезкду первой и последующими командами подпрограммы связи вставляются две дополнительные команды, одна из которых читает предыдущее состояние выхода БИС из блока 4, сравнивает его с йовым состоянием в регистре R и при их неравенстве записывает 1 в триггеры 41 и 42 и новое состояние выхода в блок 4. Другая команда - условный : переход по состоянию триггера 42, с помощью которой делается обход последующих команд, если состояние выхода БИС не изменилось по сравнению с предыдущим. Это обеспечивает событийное моделирование связей БИС.

Моделирование двунаправленнных соединений БИС отличается от указанного тем, что для каждого такого соединения используется несколько подпрограмм, число которых равно числу возможных источников сигналов в данном соединении. Для выбора подпрограммы, которая должна выполняться в текущем такте моделирования, служит отдельная подпрограмма анализа управляющих входов и выходов БИС, которая, сравнивая их состояние с эталонной информацией, хранимой в блоке 4, определяет источник сигнала 5 и передает упраТвление соответствующей подпрограмме связи.

Если в какой-либо цепи исследуемого объекта источником сигнала яв0

5

0

5

0

ляется объединение нескольких выходов БИС с открытым коллектором (монтажная функция И), то в соот-, ветствующей подпрограмме связи сначала идут команды.передачи состояний объединяемых выходов БИС в блок 7 с одновременным вычислением функции И в регистре R, состояние которого анализируется и передается на входы БИС - приемников сигнала так же, как в указанной ранее подпрограмме. В зависимости от значения кода формата операнда, указываемого в командах рассмотренные подпрограммы связи БИС могут оперировать с источниками и приемниками сигналов, разрядность которых равна 1,4,8 или 16. Анало- гичйым образом в подпрограммах моде- лирования можно параллельно вычислять состояния 1,4,8 или 16 однотипных логических элементов.

Моделирование в каждом такте стро ится как итеративный процесс получения состояния схемы, устойчивого относительно заданного входного набора сигналов. Каждому его шагу со- отйётствует, один проход мод елирую- щей программы. Если на текущем шаге хотя бы один выход БИС, подключенной к входу 1, или программно моделируемый элемент изменяет свое состояние по сравнению с предьщущей итерацией (в этом случае триггер 41 находится в состоянии 1), то вьтолняется следующая итера ция, в ПРОТИВНОМ случае моделирование в такте-fc заканчивается. Проверка конца итераций делается следующей после всех подпрограмм командой условного перехода по состоянию триггера 41, которая передает управление или команде сброса этого триггера, с которой начинается модели- рукхцая программа, или команде останова..

Работа основных блоков устройства : в процессе загрузки и выполнения моделирующей программы организуется следующим образом.

Программа загружается в блок 9с пог«)щью блока 10. При этом записываемые команды поступают в блок 9 непосредственно с входа I3 устройства, а адреса записи - через регистр 37 и счетчик 36 блока 10. Блок 10 производит также в каждом такте моделирования ввод входного набора сигналов в блок 4 и вывод из него

полученного в результате моделирования выходного набора. .Передача слов входного набора с входа 13 в блок 4 происходит через коммутатор 6, а из блока 4 на выход 14 устройства - через коммутатор 5 и блок 7. Адреса блока 4 в обоих случаях задаются через адресное поле регистра 37.

При вводе и выводе данных направJQ ление передачи, а также приемник или источник данных в устройстве определяется получаемым от ЭВМ кодом операции, который запоминается в регистре 49. Синхронизация записи

J5 в регистр 49 осуществляется дешиф- . ратором 50, который распознает адре- са устройства на адресных шинах ЭВМ и под действием ее управляющих сиг- . налов выдает синхронизирующий им- ,

20 пульс на установочный вход регистра 49, а также стробирует дешифратор 48, с выходов которого синхросигналы поступают на установочный вход регистра 37, на элементы ИЛИ 38 и

5 45, на вход установки триггера 46, а также на вход записи блока 9, При этом сигнал на выходе элемента ИЛИ 38 разрещает прием адреса из регистра 37 в счетчик 36, а сигнал I элемента ИЛИ 45 стробирует дешифратор 44, вырабатывающий импульсы записи вводимой информации в блок 4 или в регистр 3, а также фиксации выводимой из блока 4 информации в регистре R блока 7. Вырабатываемые дешифратором 44 сигналы, а также формат вводимых или выводимых данных определяется предварительно записанными в старшие разряды регистра 37 кодами операции и формата, которые принимаются с входа 13 при соответствующем коде операции ввода- вывода в регистре 49.

После ввода входного набора для очередного такта моделирования запускается моделирующая программа. Для этого в счетчик 36 засылается адрес ее начала в блоке 9. Затем ЭВМ записывает в регистр 49 код операции пуска, по которому устанавливается

0

5

0

5

в 1 триггер 46 и запускается син- хрогенератор 47, который в каждом - .цикле работы вырабатывает три сдвинутых по времени синхросигнала. По первому из них с выхода блока 9 в регистр 37 принимается очередная команда программы, по второму - увеличивается на единицу содержимое счетчика 36. В результате зтрго команда из регистра 37 поступает в блоки 2-8 устройства, определяя их операции, а блок 9 начинает чтение следующей команды. По третьему синхросигналу синхрогенератора 47 выпол- няется операция, предписанная принятой командой. Этот сигнал стробиру- ет через элемент ИЛИ 45 дешифратор 44 который расшифровывает код операции и вырабатывает соответствующие этому коду управляющие сигналы. Вьтолнение команд останова, безусловного и условных переходов, сброса триггера 41 обеспечивается-непосредственно в блоке 10. .

При безусловном переходе сигнал с соответствующего выхода дешифратора 44, действуя через элемент ИЛИ 38, вызывает прием в счетчик 36 адреса из регистра 37. В командах условных переходов аналогичная передача адреса происходит только при состоянии 1 одного из триггеров 41 и 42, которое распознается элементами И 39 и 40. В командах сброса тригге - ра 41 и останова программы сигнал с соответствующих выходов дешифратора 44 воздействует на триггеры 41 и 46. В последней на указанных коман устанавливается в О триггер 46, который останавливает синхрогенера-. тор 47 и вьщает сигнал окончания .очередного такта моделирования на выход l 1 устройства.

. .

Выполнение.команд обмена данными, логических операций и сравнения обеспечивается блоками 2-8 устройства под управлением блока 10. В этих командах адрес tn -разрядного слова данных поступает из регистра -37 на адресные входы мультиплексоров 15 коммутатора 2, которые выбирают соответствующую группу линий входэ 1, на управляющие входы, дешифратора 19 регистра 3, который подготавливает выбор соответствующей секции регистра 3, и на адресные входы блока 4, который читает сооответствукяцее слово данных. Младшая часть адресного поля, код формата операнда, часть разрядов кода операции поступает из регистра 37 в коммутаторы 5 и 6 и на дешифратор 8. Указанные блоки, обеспечивают обмен данными переменного формата. При максимальной раз- рядности п 8 данные могут иметь формат 1,4 и 8 ра:зрядов. При m 16 возможны форматы 1,4,8 и 16 разрядов

5 0 5

0 5 0

5

5

0

Разрядность коммутатора 2, секций регистра.3, блока 4, блока 7 и соответствующих связей раина т Выделение участвующей в операции части г 1-разрядного слова (четверки разря-- дов или отдельного разряда), поступающего от коммутатора 2 или блока 4, производится коммутатором 5. Он же , обеспечивает размножение вьщеленной части на всех своих выходах, что необходимо дпя последующей операции с этой частью снова или записи ее в заданную часть, регистра-накопителя R блока 7. Например, если задана операция с четверкой разрядов, то выбранная четверка помещается в четырех младших и в четырех старших разрядах выходного слова коммутатора 5; если в операции должен участвовать определенный разряд входного слова, то его значение передается во все разряды выходного слова..ЕСли операция выполняется с целым m -разрядным словом, то оно без каких-либо изме-. нений передается на выход коммутатора 5 .

Выбор источника данных (коммутатор 2 или блок 4) для коммутатора 5 производится ,его входным мультиплексором 22, который управляется старшим радрядом адресного поля команды из регистра 37. Мультиплексор 23 обеспечивает выбор заданного разряда в слове на выходах мультиплексора 22, а выходной мультиплексор 24 или передает на выходы коммутатора 5 это слово, или размножает .на них выбранный разряд или четверку разрядов. Управление мультиплексорами 23 и 24 обеспечивается кодом формата операнда из регистра 37 и младшими разрядами адресного поля, в которых ука-. зывается адрес разряда или ки разрядов в слове данных.

Аналогичная операция выделения и размножения части слова, содержащего в регистре-накопителе R блока 7 или получаемого с входа 13, выпоЛня- ется коммутатором 6, который подготавливает данные дпя записи в-регистр 3 или в блок 4. При выполнении моделирующей программы мультиплексор 22 обеспечивает прием данных только из .блока 7, а при вводб -выводе - с входа 13. Управление мультиплексорами 23 и 24 осуществляется кодом формата операнда и частью разрядов кода операции, в которой в некоторых командах указывается адрес разряда или

.1

четверки разрядов регистра блока 7, с которыми выполняется операция.

Если выполняемая команда предусматривает загрузку данных в регистр блока 7 или логическую операцию, то под действием кода операции из регистра 37 логические узлы блока 7, образованные элементами 27-29, настраиваются на заданную функцию, аргументами которой являются состояния триггеров 26 блока 7 и выходов коммутатора 5. Затем по сигналу с соответствующего выхода дешифратора 44 блока 10 происходит запись результата операции в те триггеры 26, которые выбраны дешифратором 8. Выбор разрядов (один заданный разряд, четверка или восьмерка разрядов), осуществляется дешифратором 3 и элементами И-НЕ 32 блока 8. Выбранным разрядам соответствует 1 на выходах этих элементов. По сигналу с соответствующего выхода дешифратора 44 блока 10 состояние элементов И-НЕ 32 опрашивается элементами

И-НЕ 35, которые вырабатывают стробы записи в те триггеры 26

регистра-накопителя R блока 7, которым соответствует I на выходах элементов .

Ввиду того, что участвующая в

операции часть слова данных от коммутатора 2 или блока 4 размножена на выходах коммутатора 5, то она может быть записана в любую соответствующую часть регистра-накопителя R блока 7. В Логических операциях и в операциях загрузки данных в блок: 7 эта часть регистр а (1,4 или 8 разрядов) задается кодом формата операнда и кодом операции. , Соответствующие разряды этих кодов передаются На входы деши(1 ратора 31 и элементов И-НЕ 32 мультиплексором 30 блока 8.

Если выполняемая команда требует- апоминания данных из блока 7 в блоке , то подготовленные коммутатором 6

анные записываются в соответствующие 5у блока 4. При этом работа дешифратора 8 отлич ается от указанной толь- 50 ко тем, что сигналы записи формируют-, ся элементами И-НЕ 34, а мультиплексор 30 передает на входы дешифратора 31 и элементов И-НЕ 32 код формата операндов и содержимое младших разрядов адресного поля команды, в которых указывается адрес разряда или четверки разрядов в слове. Если

30

35

40

45

55

.15

25

0

10

20

30

5

0

5

5

выполняемая команда предусматривает запись данных из.блока 7 в выбранную секцию .регистра 3, то записываемое . слово формируется с использованием с Схем выборки регистра 3, образован- ТГых элементами ИЛИ 20, И 21. Управление этими схемами производится элементами И-НЕ 32 дешифратора 8. При состоянии 1 выхода элемента И-НЕ 32 соответствующая схема пере-. дает на входы триггеров 17 регистра 3 данные с выхода коммутатора 6, при состоянии О - с выхода блока 4, в котсн ом по .адресу, совпадающему с адресом выбранной секции регистра 3, записано прошлое состояние раэря дов этой секции.

Запись сформированного таким образом слова данных в выбранную, секцию производится по Сигналу с выхода дешифратора 44, поступающему на элемент И-НЕ 33 дешифратора 8. На второй вход этого .элемента .из старшего разряда адресного поля команды подается Признак обращения к входу 1. Сигнал с выхода элемента И-НЕ 33 стробирует дешифратор 19, который производит запись слова данных в выбранную секцию регистра 3.

Одновременно цо сигналам элементов И-НЕ 34 новые данные, передавае-- мые в соответствующие разряды этой секции, записываются в те же разряды выбранного тем же адресом слова блока 4..

В. командах, предусматривающих операцию сравнения данных, логическим узлам блока 7, образов-анным элементами 27 - 29, задается операция поразрядного сложения по модулю два содержимого триггеров 26 регистра-накопителя R и данных от коммутатора 5. Элемент ИЛИ 25 блока 7 .формирует результат сравнения (О - равно; 1 - не раано). Этот результат поступает На триггеры сравнения 41 и 42 блока 10 и записы вается 6 них по сигналу дешифратора 44. Триггер 42 фиксирует результат только текущей команды, сравнения, а триггер 41 - общий результат, образуемый с помощью операции ИЛИ по всем соответствующим командам.

Формула и.3 обретения.

I. Устройство для исследования графов, содержащее первый коммутатор, регистр, дешифратор, первый блок пам

мяти и блок управления, состоящий из первого регистра, счетчика, первого и второго триггеров и синхрогенера- тора, первый и второй выходы которого соединены соответственно с первым установочным входом первого регистра и счетным входом счетчика, первый установочный вход регистра соединен с первым выходом дешифратора, вь1ход первого регистра блока управления подключен к информационному входу дешифратора и управляющему входу первого коммутатора, выход .счетчика блока управления - с адресным входом первого блока памяти, выход которого по/хключен к первому информационному входу первого регистра блока управления, а информационный вход первого коммутатора является входом задания номеров вершин устройства, о т л и ч а ю щ е, е- с я тем, что, с целью повышения быстродействия и точности, в устройство введены второй блок памяти, второй и третий коммутаторы, блок вычисления функций вершин, состоя1ций из элемента-ИЛИ и группы вычислительных узлов, каждый из которых состоит из триггера, элемента ИЛИ, первого, второго, третьего и четвертого элементов И, первого и второго элементов НЕ, в блок управления введены первый, второй и третий дешифраторы, второй регистр, третий триггер, первый, втдрой и третий элементы ИЛИ, первый и второй элементы И, в блоке управления информационный и стробиру ющий входы первого дешифратора соединены соответственно с выходом первого регистра и выходом третьего элемента ИЛИ, первый вход которого подключен к третьему выходу синхро- генератора, установочный вход счетчика соединен с выходом первого элемента ИЛИ, первый и второй входы которого подключены к вьпсодам первого и второго элементов И, выход первого триггера соединен с первым входом первого элемента И и первым входом второго элемента ИЛИ, выход которого соединен с D-входом первого триггера, выходы второго и третьего триггеров подключены соответственно к первому входу второго .элемента И и входу останова синхрогенератора, первый, второй, третий, четвертый, пятый, шестой я седьмой выходы первого дешифратора соединены соответственно с С-входом и R-входом первого

триггера, С-входом второго триггера; R-входом третьего триггера, вторым входом первого элемента И, вторым входом второго элемента И и третьим входом первого элемента ИЛИ, а информационный вход счетчика подключен к выходу первого регистра, выхбд второго регистра подключен к информационному входу второго дешифратора, выход третьего дешифратора подключен к установочному входу второго регистра и стробирующему входу вто- . рого дешифратора, в блоке вычисления функций вершин в каждом вычислительном узле D-вход триггера соединен с выходом элемента ИЛИ, входы которого подключены к выходам элементов И, выход триггера соединен с первыми входами первого и четвертого элементов И, а через первый элемент НЕ - с первыми входами второго и третьего элементов И, к вторым входам третьего и четвертого элементов И. подключен выход второго элемента НЕ, вход которого объединен с вторыми входами первого и второго элементов. И, к входам элемента ИЛИ подключены вь1- ходы элементов ИЛИ выч.ислительных узлов, выход второго блока памяти соединен с первыми информационными входами: второго коммутатора и регистра, выход которого подключен к информационному входу первого коммутатора, выход которого соединен с вторым информационным входом второго коммутатора, выход которого подключен к входам вторых элементов НЕ вычислительных узлов, выход третьего коммутатора соединен с вторым информационным входом регистра и информационным входом второго блока памяти, вход записи которого подключен к второму выходу дешифратора, третий выход которого соединен с G-входами триггеров вычислительных узлов, выход элемента ИЛИ которого подключен к второму входу второго элемента ИЛИ и D-входу второго триггера блока управления, выход первого регистра . блока управления соединен с адресным входом второго блока памяти, вторым установочнь1м входом регистра, управляющими входами второго и третье- гр коммутаторов и третьими входами элементов И вычислительных узлов, выхода) триггеров вычислительных узлов подключены к первому информационному входу третьего коммутатора и являются информационным вьпсодом уст15

ройства, информационный вход первого блока памяти, второй информаци- онный вход третьего, коммутатора, второй информациоиньгй вход первого регистра и информационньй вход вто- рого регистра блока управления объединены и являются информационным входом устройства, выход первого дешифратора блока управления подключен к стробирующему входу дешифра-. тора, выход второго дешифратора блока управления соединен соответственно с входом записи первого блока памяти-, вторым установочным входом первого регистра, S-входом третьего триггера, вторым входом третьего

элемента ИЛИ и четвертым входом первого элемента ИЛИ блока управления,. выход третьего триггера блока управления является выходом окончания работы устройства, а вход третьего де- шифратора блока управления - адресным входом устройства. -. .

2. Устройство по п. Г, о т л и - ча ю щ ее ся тем, что второй коммутатор содержит входной мульти- плексор, мультиплексор разрядов и выходной мультиплексор, причем первый и второй информационные входы всех разрядов входного мультиплексора являются соответственно первым и вторым информационными входами

второго коммутатора, выходы первого.

to

15

38099 . .

второго, третьего и четвертого раэ- . рядов входного мультиплексора соединены соответственно с восьмым, седьмым, шестым и пятым информацион- 5 ными входами мультиплексора разрядо и с первым и вторым информационными входами соответственно первого, второго, третьего и четвертого разрядов выходного мультиплексора и с вторым информационным входом соответственно пятого, шестого, .седьмого и восьмого разрядов выходного мультиплексора, выход пятого, шестого, седьмого и восьмого разрядов входного мультиплексора соединен соответственно с четвертым, третьим, вторым и, первым информационным входом мультиплексора разрядов, с первым и третьим информационными входами соответственно пятого, шестого, седьмого и восьмого разрядов выходного мультиплексора и с третьим информационным входом соответственно пер во го, второго, третье го и четвертого разрядов выходного мультиплексора, четвертые информационные, входы всех разрядов выходного мультиплексора объединены и подключены к выходу мультиплексора разрядов, выходы выходного мультиплексора являются выходом коммутатора , а адресные входы всех мультиплексоров - управляющим входом коммутатора.

20

5

0

OmS - Omf- ftnV

I г5П

KJ

кц

К7

Редактор С.Лисина

Составитель А.Шеренков

Техред Н.Бонкало Корректор Л.Пилипенко

Заказ 3294/51 , Тираж 671 Подписное ВНИИПИ Государствеиного комитета СССР

по дел1ам изобретений и открытий 113035, Москва, Ж-35, Раутпская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

f

W 12

;j

Фиг. 6

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Процессор | 1977 |

|

SU691858A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

Изобретение относится к области вычислительной техники и может быть использовано при решении на графах задач проверки логической правильности схем цифровых блоков в процессе разработки и оценки качества тестов, применяемых при их контроле. Цель изобретения состоит в повышении быстродействия и точности. Устройство содержит вход задания вершин, первый коммутатор, регистр, второй блок памяти, второй и третий коммутаторы, блок вычисления вершин и дешифратор, первый блок памяти, блок управления, выход окончания работы, адресный вход, информационный вход. Коммутатор содержит,мультиплексоры, регистр содержит :элёменты НЕ, триггеры, кнопку дешифратор, элементы Ш1И, элементы И. В состав второго (третьего) коммутатора входят Мультиплексоры. Блок вычисления вершин содержит триггеры, элементы ИЛИ, элементы И, элементы НЕ. В состав дешифратора входят мультиплексор, дешифратор, элементы И-НЕ. Блок управления содержит счетчик, первый регистр, первый элемент ШШ, первый и второй элементы И, первый и второй триггеры, второй элемент JlTffl, первый дешифратор, третий элемент ИЛИ, третий триЕгер, синхрогенератор, второй дешифратор, второй регистр, третий дешифратор. Повышение, быстродействия и точности достигается liy- тем сочетания методов программного И аппаратного моделирования и параллельной событийной организации : обмена даннътми между аппаратными моделями функциональных узлов исследуемой схемы. 1 з.п. , 6 ил.

| Устройство для электрофореза на вертикальной пластине геля | 1980 |

|

SU989438A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования цифровых объектов | 1976 |

|

SU610114A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-04-29—Подача