помехи на ЭВМ. Устройство содержит блок 2 регулирования напряжения, источник 3 номинального напряжения, источник 4 добавочного напряжения, составной эмиттерный повторитель 5, фильтр 6 нижних частот, цифроанало- говый преобразователь 7 и цифровой генератор 8 случайных сигналов. Введение мультиплексора 9, блока 10 защиты, блока 11 датчиков, блока 12 допускового контроля, блока 13 пре- рьшаний, блока 14 регистров состояА

ния, блока 15 регистров параметров, ЭВМ 16, магистральной шины 17, дешифратора 18 адреса, блока 19 счетчиков и блока 20 управления позволяет повысить надежность формирования сигнала помехи, а следовательно, и правильность определения помехоустойчивости испытуемых радиоэлектронных приборов, а также расширяет класс испытуемых приборов за счет расширения частотного диапазона помехового сигнала. 2 з.п. ф-лы, 9 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода в электронную вычислительную машину величин измеряемых параметров быстропеременных и пульсирующих потоков жидкости и газа | 1982 |

|

SU1054824A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1287170A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

Изобретекие может быть использовано при испытаниях различных радиоэлектронных приборов на помехоустойчивость по цепям электропитания. Цель изобретения - повышение надежности и расширение функциональных возможностей за счет моделирования сигнала

1

Изобретение относится к радиоэлектронике и может быть использовано при испытании радиоаппаратуры по цепям электропитания.

Цель изобретения - повьш1ение на- дежности и расширение функциональных возможностей за счет моделирования сигнала помехи на ЭВМ.

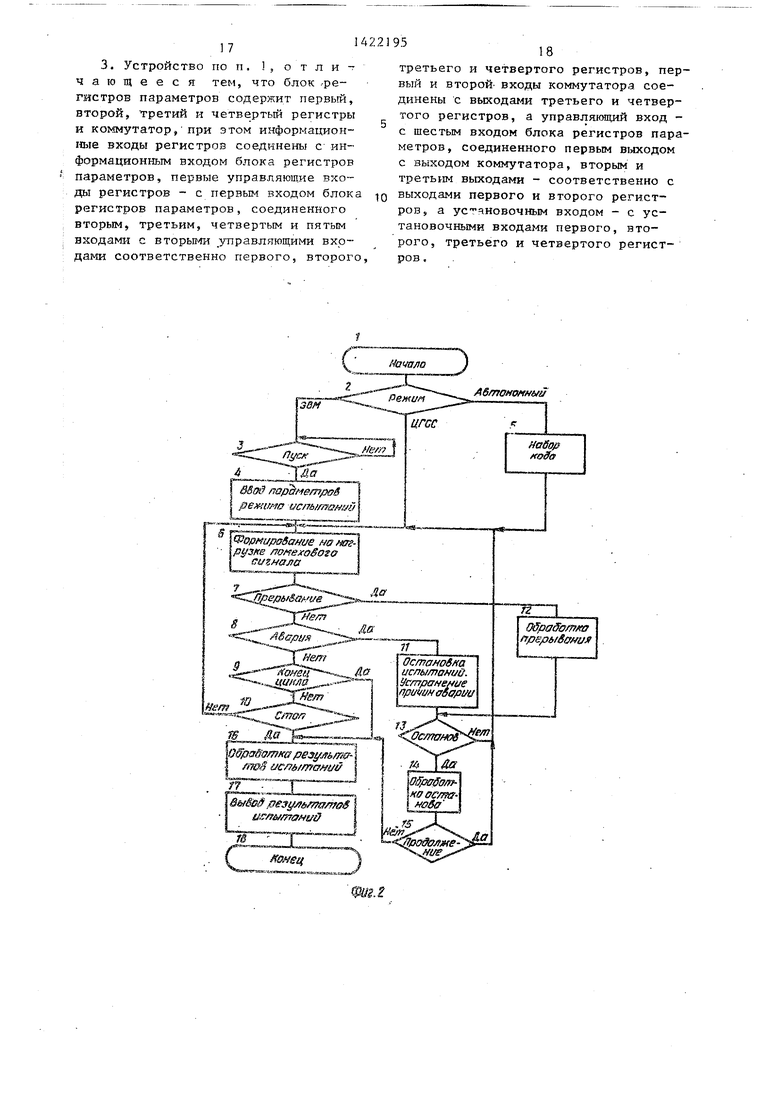

На фиг. 1 приведена электрическая схема предлагаемого устройства; на фиг. 2 - алгоритм работы устройства; ,/на фиг. 3 - схема блока регистров состояния; на фиг. 4 - схема блока регистров параметров; на фиг. 5 - структурная схема ЭВМ; на фиг. 6 - схема блока счетчиков; на фиг, 7 - схем блока управления; на фиг. 8 - схема блока регулирования напряжения,- на фиг. 9 - временная диаграмма испытательного помехового сигнала.

Устройство содержит нагрузку 1 (испытуемый прибор), блок 2 регулирования напряжения, источники номинального напряжения 3 и добавочного напряжения 4, составной эмиттерный повторитель 5, фильтр 6 нижних частот, цифроаналоговый преобразо- ватель 7, цифровой генератор 8 случайных сигналов, мультиплексор 9, блоки защиты 10, датчиков 1I, допус- кового контроля 12, прерьгоаний 13, регистров состояния 14, регистров параметров 15, ЭВМ 16, магистральную шину 17, дешифратор 18 адреса, блоки счетчиков 19 и управления 20,

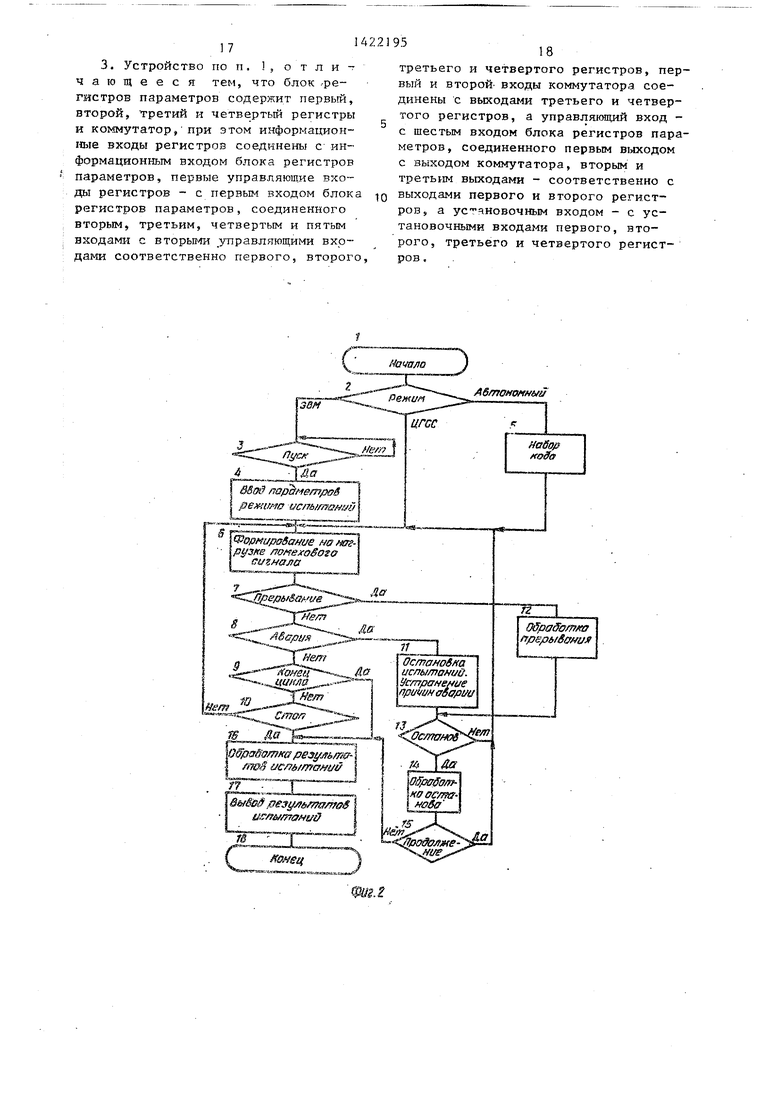

Блок 14 регистров состояния содержит первый 21 (состояния), второй 22 (маски), третий 23 (ошибок), четвер

0 5 0

0 5

5

тый 24 (адреса) регистры, коммутатор 25, логическую схему И 26 и формирователь 27 сигнала преры)зания.

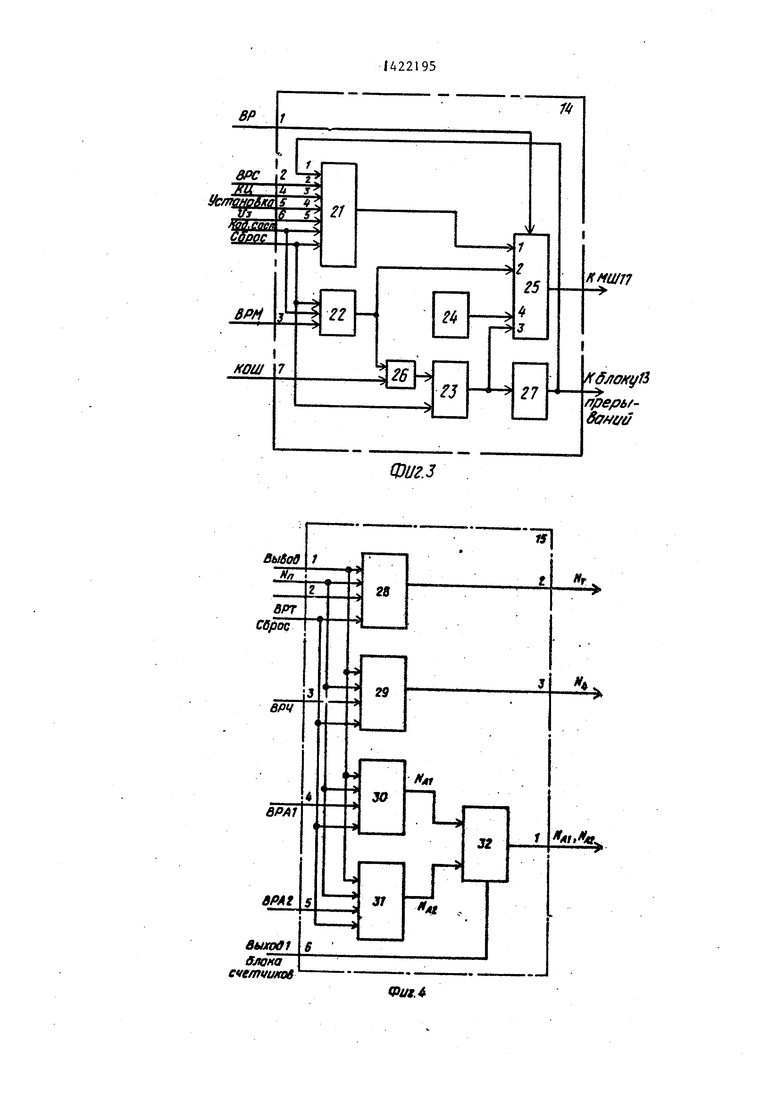

Блок 15 регистров параметров содержит первый 28 (времени), второй 29 (частоты), третий 30 (бросков напряжения), четвертый 31 (просадок напряжения) регистры и коммутатор 32.

ЭВМ 16 содержит процессор 33, оперативное запоминающее устройство 34,, постоянное запоминающее.устройство 35, устройство 36 ввода, устройство 37 вывода и шину 38 управляющих сигналов.

Блок 19 счетчиков содержит первый 39 и второй 40 генераторы, счетчики 41 и 42 и логические схемы И 43 и 44.

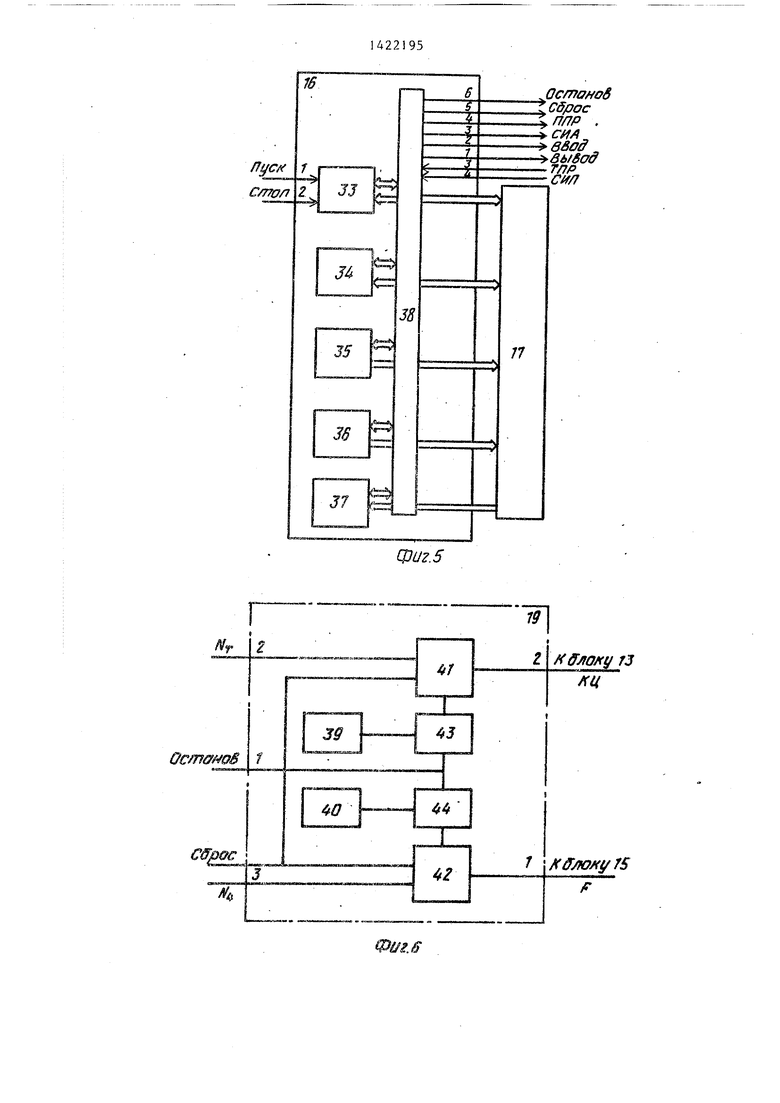

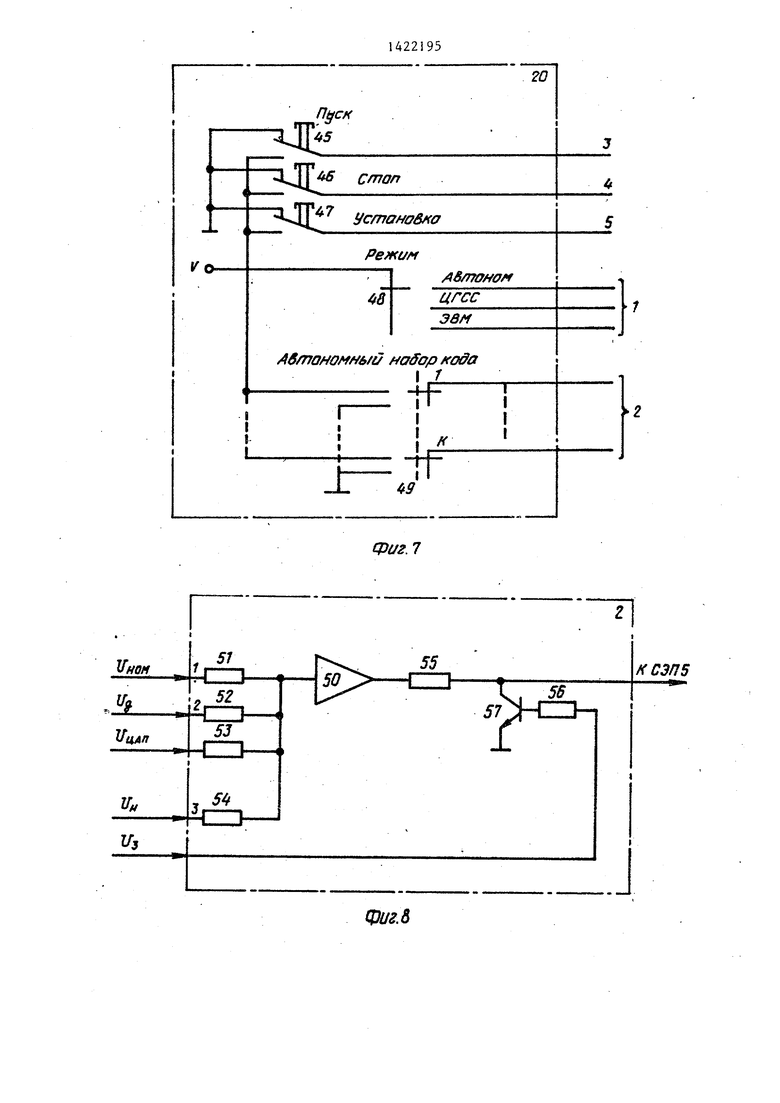

Блок 20 управления содержит первую 45, вторую 46 и третью 47 кнопки, первый 48 и второй 49 переключатели.

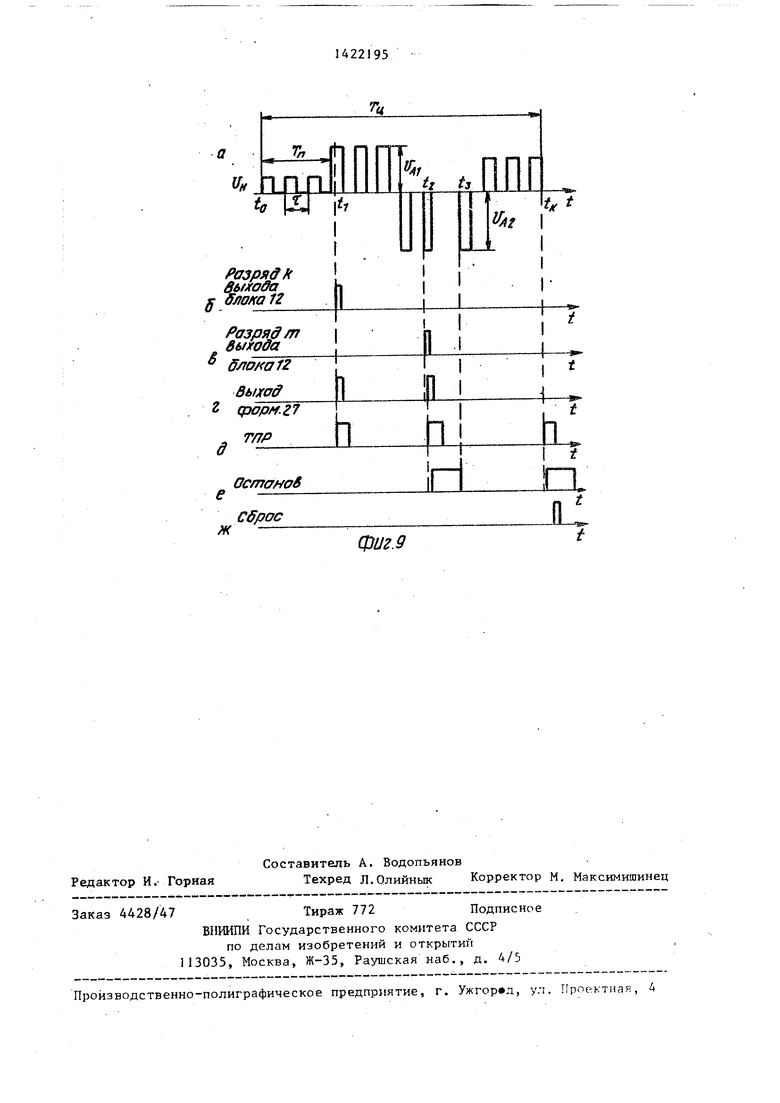

Блок 2 регулирования напряжения содержит усилитель 50 постоянного тока, входные первый 51 второй 52 и третий 53 резисторы, резистор 54 обратной связи, четвертый 55 и пятый 56 резисторы и транзистор 57 защиты.

Источники 3 и 4 соединены последовательно, один выход источника 3 номинального напряжения соединен с первым входом блока 2 регулирования напряжения, другой выход - с общей шиной питания нагрузки 1. Выход источника 4 соединен с входом составного эмиттерного повторителя 5 и вторым входом блока 2, выход составного эмиттерного повторителя 5 соединен с вторым входом блока 10 защиты, одной клеммой нагрузки 1 и чеез фильтр 6 нижних частот с входом братной связи блока 2 регулирования апряжения, управляющий вход которого оединен с выходом блока 10 защиты, естым входом блока 14 и третьим входом блока 13-прерываний, выход ультиплексора 9 соединен с входом цифроаналогового преобразователя 7, выход которого соединен с третьим входом блока 2, первый вход мультиплексора 9 - с выходом цифрового генератора 8 случайных сигналов, второй вход - с первым выходом блока 15 регистров параметров,третий вход - с вторым выходом блока 20 управления, а первый управляющий вход - с первым выходом блока 20. ЭВМ 16 соединена с магистральной шиной 17, а также соединена первым и вторым управляющими входами с третьим и четвертым выходами блока 20 управления, третьим управляющим входом - с выходом блока 13 прерываний, четвертым управляющим входом - с управляющим выходом ешифратора 18 адреса, первый выход ЭВМ 16 соединен с первыми входами блока 15 и дешифратора 8 адреса, второй и третий выходы - с вторым и . третьим входами дешифратора 18 .адреса, четвертый выход - с управляющим входом блока 13 прерываний, пятьш выход - с установочными входами блоа 14 регистров состояния, блока 15 регистров параметров и блока 19 счетчиков, шестой выход - с первым входом блока 19 и вторым управляющим входом мультиплексора 9, блок 14 регистров

о

состояния первыми тремя входами соединен с одноименньми выходам дешифратора 18, четвертым входом - с вторым выходом блока 19 и первым входом блока 13 прерьгааний, пятым входом - с пятым выходом блока 20 управления и первым входом блока 10 защиты, а седьмым входом - с выходом блока 12 допускового контроля, входы которого соединены с выходами блока 11 датчиков, информационный вход и информационный выход блока 14 соединены с магистральной шиной 17, а выход блока 14 - с вторым входом блока 13 прерьшаний, блок 15 регистров параметров вторым,- третьим, четвертьм и пятым входами соединен с четвертым, пятым, шестым и седьмым выходами дешифратора 18 адреса, а щестым входом - с первым выходом блока 19 счетчиков , информационный вход блока 15

соединен с магистарльной шиной 17, второй и третий выходы - с вторьпч и третьим входами блока 19 счетчиков, информационные выходы нагрузки 1 соединены с входом блока II датчиков.

В блоке 14 регистров состояния первый вход коммутатора 25 соединен

с выходом первого регистра 21, второй вход - с выходом второго регистра 22, третий вход - с выходом третьего регистра 23 и входом форми- ро вателя 27 сигнала прерывания, четвертый вход - с выходом четвертого регистра 24, а выход - с информа- ционны выходом блока 14, первый регистр 21 первым входом соединен с выходом формирователя 27 и выходом

блока 14, вторым, третьим, четвертым и пятым входами - с вторьм, четвертым, пятым и шесть М входами блока 14, информационным входом - с информационным входом блока 14 и информационньгм входом второго регистра 22, установочным входом - с установочным входом блока 14 и установочными входами второго 22 и третьего 23 регистров, управляющий вход

второго регистра 22 соединен с третьим входом блока 14, один вход логической схемы И 26 соединен с выходом регистра 22, а другой вход - с седьмым входом блока 14, выход логической схемы И 26 соединен с информационным входом третьего регистра 23, управляющий вход коммутатора 25 соединен с первым входом блока 14.

В блоке 15 регистров параметров

информацион ные входы регистров 28- 31 соединены с информационным входом блока 15, а установочные входы этих регистров - с установочмзм входом блока 15,.первые управляющие входы регистров 28-31 соединены с первым входом блока 15, вторые управляющие входы этиЬ регистров соединены соответственно с вторым, треть- liM, четвертым и пятым входами блока 15, выходы регистров 28 и 29 соеди- нены соответственно с вторым и третьим выходами блока 15, а выходы регистров 30 и 31 - соответственно с первым и вторым входами коммутатора 32, управляющий вход которого соединен с шестым входом блока 15, а выход - с первым выходом блока 15.

Устройство работает следующим образом.

Для формирования помеховых сигналов, действующих по цепи питания нагрузки 1 используются два источника - источник 3 номинального напряжения и источник 4 добавочного напряжения. Для адекватной имитации реальных условий эксплуатации нагрузки 1 источники 3 и 4 должны иметь эквивалентные нагрузочные характеристики. На нагрузке 1 формируется напряжение U, равное

UH и

HOW

Un,

где - Номинальное напряжение

источника 3;

Uf, , - случайная составляющая, моделирующая воздействие помех.

Источник 4 добавочного напряжения обеспечивает броски питающего напряжения UH на нагрузке 1 по отнощению

к-и

НОАЛ

В системе осуществляется

автоматическая стабилизация номинального уровня постоянного напряжения на выходе независимо от влияния нагрузки 1. Для этого служит цепь обратной связи состоящая из составного эмиттерного повторителя 5, филь- ра 6 нижних час-гот, резистора 54 обратной связи и операционного усилителя 50 в блоке 2 регулирования на- прягження,

В исходном состоянии на выходе 4yльтиплeкcopa 9 присутствует нулевой код N5, и на третий вход блока 2 поступает напряжение Ut, с выхода цифроаналогового преобразователя 7. Операционный усилитель 50 блока 2 управляет составным эмиттерным повторителем 5 так, что выполняется соотношение

.,и

51 нем

де Ug - 51 Ду1 Y

Y.,(UH,M+

51

Uj) - UH

Uo

(0

напряжение источника 4;

53

проводимости резисторов 51, 52 и 53, - проводимость последовательно соединенных фильтра 6 и резистора 54 обратной связи. При условии

(2)

S1

-)- Yr, YO и YcoU. Y.U,

53Uo

получается

UH - UKOM

т.е. обеспечивается инвариантность напряжения UK относительно изменений нагрузки 1.

При моделировании помехового сигнала с выхода мультиплексора 9 поступает код NO + Np , преобразуемьй циф- роаналоговым преобразователем в напряжение Uo - Up, и согласно (1) и (2), и согласно (1) и (2)выполняется соотнэщение

UK,M +

Y.jUn

YoUn.

При дополнительном условии Ug напряжение на нагрузке 1 равно

5

0

0

0

5

и„ и„

+ kN.

где

н How k - коэффициент преобразования

цифроаналогового преобразователя 7.

Формирование испытательного поме- хового сигнала в устройстве производится в одном из трех режимов. Режимы выбираются установкой соответствующего положения переключателя 48 в блоке 20 управления (фиг. 7),

Режим автономного набора кода. В блоке 20 переключатель в положении

АВтоном.Управляющий сигнал на пер- Ь

вом выходе блока 20 подключает выход

мультиплексора 9 к его третьему входу, на который со второго выхода блока 20 поступает код, набираемый на переключателе 49. В этом режиме проводятся наладочные работы с устройством, проверка функционирования его блоков, а также испытания радиозлек- TPOHHLIX приборов воздействием различных уровней постоянного напряже5 ния с длительностью выдержки до 25 ч. I

Режим работы цифрового генератора

случайных сигналов. В блоке 20 управления переключатель 48 в положении

0 ЦГСС. На выходе мультиплексора 9 проходит код с выхода цифрового генератора 8. Этот режим используется для формирования случайных помеховых сигналов, частота которых выше,

5 чем предельная частота изменения сиг. налов под управлением ЭВМ 16. Гене- , ратор 8 работает автономно и может воспроизводить сигналы, моделирующие процессы дрейфа и старения.

Режим работы под управлением ЭВМ. В блоке 20 переключатель 48 в положении ЭВМ . ЭВМ 16 на основе программно заданного закона распределения формирует случайный помеховый сигнал с помощью блока 4 регистров,, блока 15 регистров параметров, блока i 9 счетчиков и дешифратора 18 адреса. Управляющий код с первого выхода блока 15 поступает на второй

вход мультиплексора 9. ЭВМ-16 связана с внешними блоками 14 и 15 и дешифратором 18 с помощью магистральной шины I7 адреса и данных шины 38 управляющих сигналов. Структура ЭВМ 16 и способ связи аналогичен ЭВМ Электроника-60. При передаче информации по шине 17 сперва поступает адрес внешнего устройст- ва, который дешифрируется в дешифраторе 18 адреса, а затем поступают данные на ЭВМ в выбранное внешнее устройство или наоборот.

В качестве адресуемых внешних устройств используются регистры 21- 24 в блоке 14 регистров состояния и регистры 28-31 в блоке 15 регистров параметров.

Для дешифрации адреса на первые три входа дешифратора 18 поступают управляющие сигналы Вывод, Ввод и сил, после, передачи данных дешифратор 18 вырабатьшает ответный сигнал сип на четвертый управляю- щий вход ЭВМ 16. Для управления записью данных в регистры 28-31 используется сигнал Выво/ь.

Сброс регистров блоков 14 и 15 производится сигналом Сброс на пя- том выходе ЭВМ J6.

Разрешение прерывания подтверждается сигналом ВПР на четвертом выходе ЭВМ 16, а сигнал требования прерывания ТИР от блока 13 принимаетс на третий управляющий вход 16. Для остановки процесса испытаний и фиксации состояния помехового сигнала на шестом выходе ЭВМ 16 вы°рабаты- вается сигнал Останов, поступаю- ющий на цифровой генератор 8 случай- сигналов и на блок 19 счетчиков. После снятия этого сигнала процесс испытаний может продолжаться.

Оператор управляет началом процесса и остановкой с помощью кнопок Пуск 45 и Стоп 46 в блоке 20 управления, запуская или останавливая ЭВМ 16.

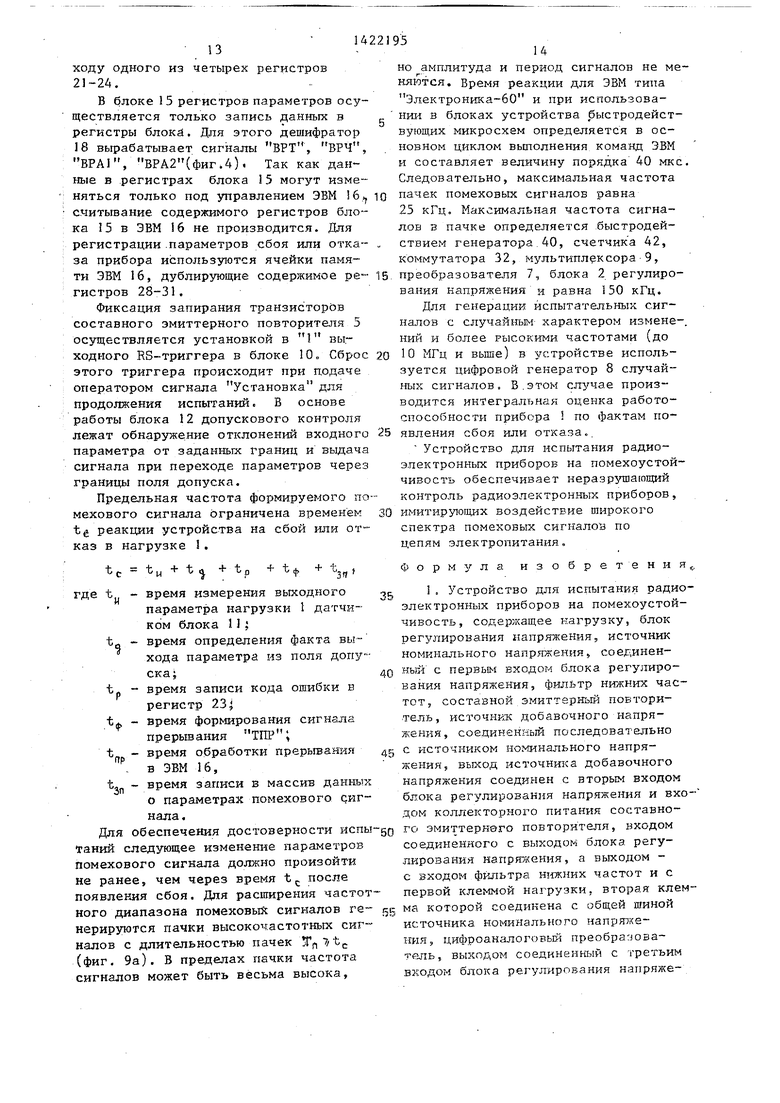

Общий алгоритм работы устройства представлен на фиг, 2.

В начале испытаний выбирается режим работы. По сигналу Пуск запускется ЭВМ 16 и через устройство 36 ввода (фиг. 5) вводится в оперативное запоминающее ycтpoйqтвo 34 программа испытаний. Управление передается на начало программы испытаний и

под ее управлением вводятся параметры режима испытаний.

В качестве этих параметров выступают амплитуда и частота помехового сигнала, параметры случайного закона распределения, длительность- цикла испытания прибора.

В течение всех подготовительных операций на вход цифроаналогового преобразователя 7 поступает нулевой код NO, на нагрузке присутствует напряжение питания .

Это обеспечивается подачей в данный период времени,сигнала Останов с шестого выхода ЭВМ 16 на второй управляющий вход мультиплексора 9. В результате выход последнего подключается к своему внутреннему регистру хранящему нулевой код Np.

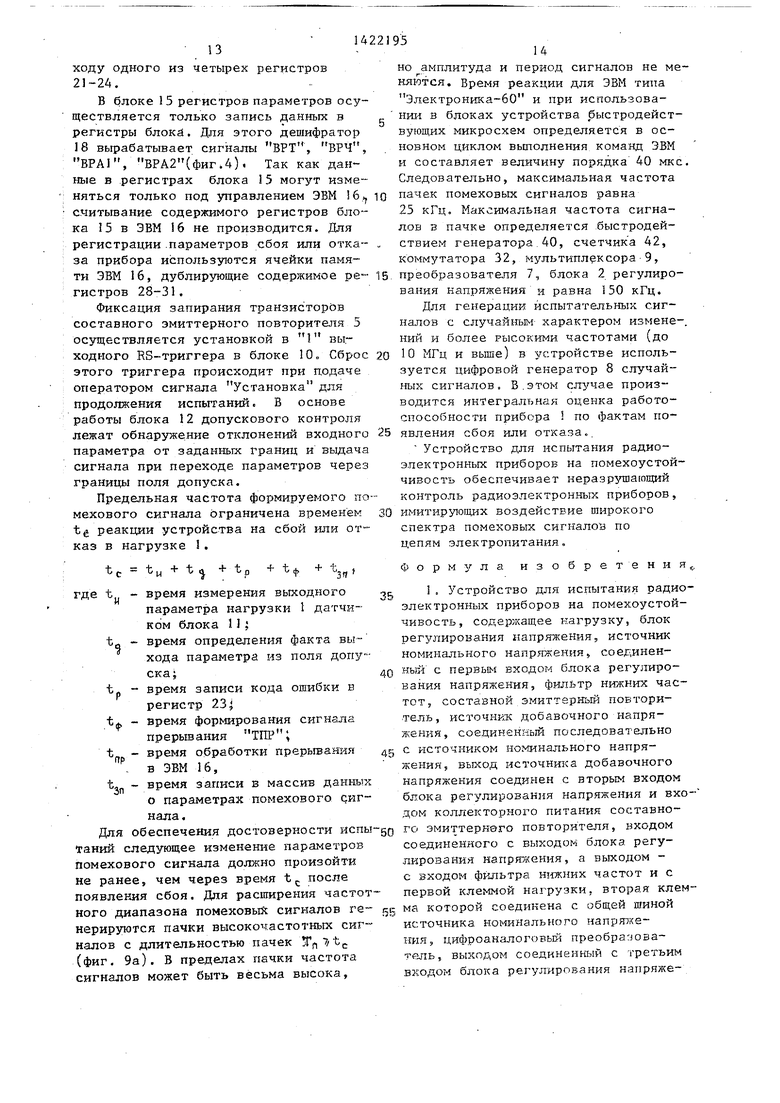

Затем сигнал Останов снимается, и начинает работать программа формирования на нагрузке помехов ого сигнала (фиг.2,блок 6).На фиг.9,как пример, приведена временная диаграмма помехового сигнала, представляющего собой последовательность пачек прямоугольных импульсов (коммутационные помехи) с постоянной частотой И амплитудой, распределенной по случайному закону. Параметрами помехового сигнала являются длительность TQ цикла испытаний прибора данным видом помехи, частота

1

f - изменения амплитуды, значе/

ния амплитуд бросков U и просадок UKо напряжения и длительность пачек импульсов Т г,.

В начале формирования помехового сигнала ЭВМ 16 записьгаает в регистр 28 времени код U длительности цикла испытаний, затем в регистр 29 частоты - код N.. частоты изменения сигнала. Эти коды с выходов регистров 28 и 29 поступают на второй и третий входы блока 19 счетчиков. В последнем (фиг. 6) программируемый счетчик 41 определяет длительность Тц, а программируе й1й счетчик 42 - часто ту f изменения сигнала. Для этого синхроимпульсы с выхода генератора 39 через схему И 43 поступают на сченый вход счетчика 41, а импульсы генратора 40 - через схему И 44 на счетный вход счетчика 42. Коэффициенты пересчета счетчиков 41 и 42 определяются кодами N и N у , поступающими на их управляющие входы.

В результате сигнал F с выхода счетчика 42 поступает на шестой вход блока 15 регистров параметров и управляет в нем, коммутатором 32 (фиг.4 В одном периоде пересчета импульсов в счетчике 42 сигнал F коммутатор 32 подключает к первому выходу блока 15 выход регистра 30 бросков напряжения. ,

Во втором периоде пересчета сигнал F I j, и к первому выходз блока 15 Подключается выход регистра 31 просадок напряжения,„

Этим обеспечивается изменение по- мехового сигнала U с заданной частотой f.

При формировании сигнала (фиг. 9) для положительньпс импульсов в регистр 30 записывается код N, амплитз ды, а в регистр 31 - нулевой код N(,. Для формирования отрицательных мпульсов в регистр 30 записывается код NO, а в регистр 31 код амплитуды Nд. После заполнения счетчика 4 сигнал.пе- реполнения КЦ свидетельствует о конце, цикла испытаний прибора. Этот сигнал поступает в регистр 21 состояния и на блок 13 прерываний, кото; - рый вырабатывает сигнал- ХПР требо- вання прерывания (фиг. 2, блок 9),. ЭВМ 16 прерывает работу подпрограммы формирования и считывает из регистра 24 адрес вектора прерывания, после чего переходит к обработке резуль- татов испытаний и выводу их через устройство 37 вывода (фиг. 2, блоки 4 и 15).

В устройстве производятся фикса- :ция и обработка сбоев и нарушений функционирова 1ия испытуемого радиоэлектронного прибора (нагрузки J}; ,(1пя этого анализируются сигналы на некотором множестве выходов нагрузки Г. Каждый выход подк.гаочается к входу блока 1I датчиков 1I, который ||юрмирует унифшдарованные измерительные сигналы и передает их на . входы блока 2 допускового контро- лл. В последнем каждому выходному сигналу соответству,ет канал допус-- кового контроля, в котором определяется находится ли данный выходной сигнал нагрузки 1 в заданных границах допуска. При выходе сигна- ла из поля допуска на соответствующем „заряде выходного сигнала блока 12 появляется единичный импульс. Выходной сигнал блока 12 допускового

контроля представляет собой параллельный код кош, который поступает на один из входов логической схемы И 26, на другой вход которой подается код с выхода регистра 22 маски Выходной сигнал схемы И 26 равен

, п, «оа. л п,Д - 1Д. где К - число разрядов кода КОШ.

Следовательно, в регистр 23 ошибок заносятся единиць только в те разряды, которые не замаскированы кодом маски. Это позволяет, программно изменяя код маски, управлять реакцией устройства на сбои по различ- iuiiM выходам нагрузки ,

Формирователь 27 сигнала прерываний вырабатывает ш-1 пульс ОШ, если хотя бы в одном разряде регистра 24 появляется единица. Этот импул} с поступает в регистр 21 состояния и одновременно на второй вход блока 13 прерываний5 вызьшая прерывание ЭВН16

Регистр 2 состояния блока S3 определяет режимы работы устройства и содержит информацию о состоянии процесса испытаний. Во все разряды регистра 21 информация может быть занесена программно по магнстральной шине 17 через информационный вход блока 14 По сигналу Сброс все разряды регистра 21 обнуляются.

На фиг. 9 показана обработка прерываний при воздействии помехового сигнала. В момент t возникает сбой в нагрузке I , и в разряде вьосодного кода кош блока 3 появляется единица (фиг. 96). На выходе формировтеля 27 появляется импульс (фиг.9г),, который устанавливает в 7-3и разряд регистра 21 и вызывает появление сигнала ТПР (фиг, 9д) в том случае, если имеется единичный уровень сигнала предоставления прерывания НИР, полз. чаемого от ЭВМ 16. Происходят прерьюания (фиг.2; блок 7) и переход к подпрогрги зме обработки пре- рьшания по ошибке (фиг,, 2, блок 12). При этом фиксир тотся и запоминаются в оперативном запон1 на1ощем устройстве 34 параметры помехового сигнала., вызывающего сбой в нагрузке 1, Для этого в устройстве 34 в соответствующих ячейках все время дублируются параметры Т, f , UA. и U д занесенные в регистры 28--3 ,

Такш- образом, в памяти IBM 16 формируется массив значений параметров помеховых сигналов, вызьтаю- щих сбой нагрузки 1. -Далее производится анализ: необходима для остановки процесса испытания (фиг. 2, блок 13), Останов ка имеет место в случаях, если сбой в нагрузке 1 приводит к выходу ее из строя и если необходимо более детально исследовать состояние нагрузки в данный момент и после этого принять решение о продолжении испытаний.

Если достаточно только зарегистрировать факт сбоя и значения параВ устройстве предусмотрена защи составного эмиттерного повторителя и нагрузки 1 при превышении током нагрузки заданного порога. Для это в блоке 10 защиты измеряется ток, текающий через нагрузку 1 . При прев шении порога срабатьгеает устройств типа триггера Шмидта и устанавлива в единичное состояние выходной три гер блока 10 защиты. Единичный уро вець выходного сигнала Uj. из блока

.метров сигналов, процесс испытаний не is Ю поступает на третий вход блока

прерывается, т.е. на нагрузку продолжает действовать помеховый сигнал, хотя .в ЭВМ 16 прерывание происходит. В случае остановки ЭВМ 16 вырабатывает сигнал Останов, ко- торьм запрещает прохождение синхроимпульсов через логические схемы И 43 и 44, к коды в счетчиках 41 и 42 не изменяются. Кроме того, сигнал Останов подключает к выходу мультиплексора 9 внутренний регистр кода NP и на нагрузку 1 действует только номинальное напряжение и рщ;На фиг. 9 сигнал прерывания по k-му разряду КОШ не вызывает остановки. В момент t происходит .сбой в нагрузке 1 и в т-м разряде кода кош появляется единица (фиг.9в) Формируется прерьшание, и подпрограма обработки этого прерывания вызывает сигнал Останов (фиг.9е) В период t, t производится обработка остановки(фиг. 2, блок 14), а затем процесс испытаний продолжается. В момент tk счетчик 4,1 вырабатывает сигнал КЦ, который йы

зывает сигнал ТПР (фиг.. 9д). ЭВМ 16 вьфабатьгаает сигнал Останов, а затем сигнал Сброс, устанавливающий в нулевое состояние регистры 21-23, 28-31 и счетчики 41 и 42. На нагрузку 1 теперь действует только напряжение и,, .

После этого начинает работать подпрограмма обработки результатов испы- таний. В,функции этой подпрограммы входят: построение области работоспособности прибора в зависимости от параметров испытательного помехового сигнала, статическая обработка, принятие решения о годности испыту; мо- го (фиг. 2, ЭВМ 16). Вьшод результатов испытаний производится либо в виде твердой копии, либо на экране дисп

лея устройства 37 вывода (фиг.2, шина 17).

В устройстве предусмотрена защита составного эмиттерного повторителя 5 и нагрузки 1 при превышении током нагрузки заданного порога. Для этого в блоке 10 защиты измеряется ток, протекающий через нагрузку 1 . При превышении порога срабатьгеает устройство типа триггера Шмидта и устанавливает в единичное состояние выходной триггер блока 10 защиты. Единичный уро- вець выходного сигнала Uj. из блока

Ю поступает на третий вход блока

5

Q

13, вызывая прерьшание по аварии, на шестой вход блока 14, устанавливая в 1 первый разряд регистра 21, и на управляющий вход блока 2 регулиро0 вания напряжения. В последнем сигнал открывает транзистор 57 (фиг.8), и выходное напряжение блока 2 становится равным нулю, запирая транзисторы составного эмиттерного повторите5 ля 5. Ток через нагрузку 1 прекращается . ЭВМ 16 вырабатывает сигнал Останов и производятся анализ и устранение причин аварийного превышения тока нагрузки 1 (фиг. 2, блок 11).

0 Для продолжения процесса испытаний необходимо нажать кнопку 47 в блоке 20 управления. Вырабатьгеается сигнал Установка, который переводит в нуль 1-й разряд регистра 21 состояния и

g сбрасывает выходной триггер блока 10 защиты, разрешая работу блока 2 регулирования напряжения.

Оператор в любой момент может остано вить испытания нажатием кнопки Стоп

0 46 в блоке 20 управления и вьгоести результаты испытаний (фиг. 2, блок 10),

Обмен информацией в системе между ЭВМ 16 и внешними регистрами осуществляется следующим образом.

По магистральной шине 17 данные могут быть переданы в регистры 21 и 22 блока 14 регистров состояния. Запись кода в регистр 23 ошибок производится при поступлении кода ошибки (КОШ) с выхода блока 12 допуско- вого контроля. В регистре 24 постоянно записан адрес вектора прерьшания. Для считывания данньрс из регистров блока 14 дешифратор 18 адреса вырабатывает

С сигнал ВР, управляющий коммутато- .ром 25. Сигнал ВР представляет собой двухразрядный параллельный код, в зависимости от которого коммутатор 25 подключает свой выход к выходу одного из четырех регистров 21-24.

В блоке 5 регистров параметров осуществляется только запись данных в регистры блоки. Для этого дешифратор 18 вырабатывает сигналы ВРТ, ВРЧ, ВРАГ , ВРА2(фиг.4), Так как данные в регистрах блока 15 могут изменяться только под управлением ЭВМ 16,, считывание содержимого регистров блока 15 в ЭВМ 16 не производится. Для регистрации .параметров сбоя или отка- за прибора используются ячейки памяти ЭВМ 16, дублирующие содержимое ре- гистров 28-31.

Фиксация запирания транзисторов составного эмиттерного повторителя 5 осуществляется установкой в 1 выходного RS-триггера в блоке 10. Сброс этого триггера происходит при подаче оператором сигнала Установка для продолжения испьгганий, В основе работы блока 12 допускового контроля лежат обнаруже.ние отклонений входного параметра от заданных границ и вьщача сигнала при переходе параметров через границы поля допуска.

Предельная частота формируемого по мехового сигнала ограничена временем tg реакции устройства на сбой или отказ в нагрузке I.

tc ty + t + tp + t

+

где t - время измерения выходного

параметра нагрузки 1 датчиком блока 11;

tq - время определения факта выхода параметра из поля допуска j tp - время записи кода ошибки в

регистр 23 t - время формирования сигнала

прерьшания t - время обработки прерывания

. в ЭВМ 16,

t.j - время записи в массив данных о параметрах помехового сигнала.

Для обеспечения достоверности испы Таний следующее изменение параметров помехового сигнала должно произойти не ранее, чем через время t,.. после появления сбоя. Для расширения частотного диапазона помеховых сигналов генерируются пачки высокочастотных сигналов с длительностью пачек (фиг. 9а). В пределах пачки частота сигналов может быть весьма высока.

HO амплитуда и период сигналов не меняются. Время реакции для ЭВМ типа Электроника-60 и при использовании в блоках устройства быстродействующих микросхем определяется в основном ЦИКЛОМ вьтолнения команд ЭВМ и составляет величину порядка 40 мкс Следовательно, максимальная частота пачек помеховых сигналов равна 25 кГц. Максимальная частота сигналов в пачке определяется .быстродействием генератора . 40, счетчик а 42, коммутатора 32, мультиплексора9, преобразователя 7, блока 2 регулиро- ва.ния напряжения и равна i 50 кГц.

Для генерации испытательных сиг- нгшов с случайные характером изменеНИИ и более рысокими частотами (до 10 МГц и вьше) в устройстве используется цифровой генератор 8 случайных сигналов. В.этом случае производится интегральная оценка работоспособности прибора 1 по фактам появления сбоя или отказа.

Устройство для испытания радиоэлектронных приборов на помехоустойчивость обеспечивает неразрзтпающий контроль радиоэлектронных приборов, имитирующих воздействие широкого спектра помеховых сигналов по цепям электропитания.

Формула изобретения

ц 1. Устройство для испытания радиоэлектронных приборов на помехоустойчивость, содержащее нагрузку, блок регзширования напряжения, источник номинального напряжения, соединен40 Hbsi с первым входог блока регулирования напряжения, фильтр нижних частот, составной эмиттерный повторитель, источнк-к добавочного напряжения, соединенный последовательно

4Р; с источником номинального напряжения, выход источншса добавочного напряжения соединен с вторым входом блока регулирования напряжения и вхо дом коллекторного питания составно- -gp го эмиттернэго повторителя, входом соединенного с выходом блока регулирования напряжения, а выходом - с входом фильтра ш-шних частот и с первой клеммой нагрузки, вторая клемкр ма которой соединена с общей шиной источника номинального иапршхе- 1ВДЯ, цифроаналоговый npeo6pa:joBa- тель, выходом соединенный с третьим входом блока регулирования напряжения, вход обратной связи которого соединен с выходом фильтра нижних частот, и цифровой генератор случайных сигналов, отличающее- с я тем, что, с целью Ьоньшения на- дежности и расширения функциональных ,возможностей, в него введены ЭВМ, блок управления, магистральная шина, соединенная с ЭВМ, мультиплексор, блок регистров параметров, блок регистров состояния, дешифратор адреса, блок счетчиков, блок прерьтаний, блок защиты, блок датчиков и блок допускового контроля, при этом пер- вый выход блока управления соединен с первьм управляющим входом мультиплексора, первый, вход которого соединен с выходом цифрового генератора случайных сигналов, второй вход - с первым -выходом блока регистров параметров, третий вход - с вторым выходом блока управления, а выход мультиплексора соединен с входом цифроаналогового преобразователя третий и четвертьй выходы блока управления соединены с первым и вторым управляющими входами ЭВМ, первый выход которой соединен с первыми входами блока регистров параметров и деши ратора адреса, второй и третий выходы - с одноименными входами дешифратора адреса, четвертый выход - с управляющим входом блока прерываний, птый выход - с установочньпчи входами блока регистров параметров, блока ре гистров состояния и блока счетчиков, а шестой выход - с вторым управляющш. входом мультиплексора и первым входо блока счетчиков, выход блока прерыва .НИИ соединен с третьим управляющим ЭВМ, соединенной четвертым управляющим входом с управляющим выходом дешифратора адреса, магистральная шина соединена с информационны- ми входами блока регистров состояния блока регистров параметров и дешифратора адреса и информационным выходом блока регистров состояния, первыми тремя входами соедиенного с од- ноименными выходами дешифратора адреса, соединенного четвертым, пятым j шестым и седьмым выходами соответственно с вторым, третьим, четвертым и пятым входами блока регист- ров параметров, второй и третий входы блока счетчиков соединены с одноименными выходами блока регистров параметров, соединенного шестым входом с первым выходом блока счетчиков, соединенного вторым выходом с первым входом блока прерываний и четвертым входом блока регистров состояния, соединенного пятым входом с пятым выходом блока управления и первым входом блока защиты, второй вход блока прерываний соединен с управляющим выходом блока регистров состояния, соединенного шестым входом с третьим входом блока прерываний, управляющим входом блока регулирования напряжения и выходом блока защиты, второй вход которого соединен с выходом составного эмиттерного повторителя, информационные выходы нагрузки соединены с входами блока датчиков, соединенного выходами с входами блока допускового контроля, соединенного выходом с седьмым входом блока регистров состояния.

2, Устройство по п. 1, отличающееся тем, что блок регистров состояния содержит первый, второй, третий и четвертьй регистры, логическую схему И, формирователь сиг кала прерывания и коммутатор, первым входом соединенный с выходом первого регистра, а управляющим входом - с первым входом блока регистров состояния , а выходом - с информационным выходом блока, первый вход первого регистра соединен с выходом формирователя сигнала прерывания и выходом блока регистров состояния, соединенного вторым, четвертым, пятым и шестым входами с вторым, третьим, четвертым и пятым входами первого регистра, а информационным входом - с информационными входами первого и второго регистров, выход второго регистра соединен с вторьм входом коммутатора и первым входом логической схемы И, вторым входом соединенной с седьмым входом блока регистров состояния , а выходом - с информационным входом, третьего регистра, выходом соединенного с третьим входом коммутатора и с входом формирователя сигнала прерывания, управляющий вход второго регистра соединен с третьим входом блока регистров состояния, соединенного установочным входом с установочными входами первого, второго и третьего регистров, выход четвертого регистра соединен с четвертым входом коммутатора.

S

eSiK nap MemflftS I ee tifHp испытаний

.-даи.ц.ци.а:Ц.яа:.,.1.,.ш .„д

opMi/paSaffi/s as рузке /70f exoSozo сигнала

С тмец

«tusiC E- raat.-us

третьего и четвертого регистров, первый и второй входы коммутатора соединены с выходами третьего и четвертого регистров, а управляющий вход - с шестым входом блока регистров параметров, соединенного первым В лходом с выходом коммутатора, вторым и третьим выходами - соответственно с выходами первого и второго регистров, а установочным входом - с ус- тановочнь ми входами первого, второго, третьего и четвертого регистров ,

-JT

Фиг.з

Cpuz.S

Ф1/г.&

Фиг Л

Фиг.&

| Устройство для контроля интегральных схем | 1981 |

|

SU966628A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Источник помеховых сигналов | 1984 |

|

SU1188680A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-09-07—Публикация

1987-01-14—Подача