I

Изобретвгае относится к области автоматикв и вычислительной техники и быть использовано в полупровоцни- . ковых ЗУ.

Известны ЗУ на биполярных и многоемнттерных транзисторах с матричной организацией запоминающих элементов Однако эти устройства характеризуЬэтся большой потребляемой мощностью.

Наиболее близким техническим решением к изобретению является ЗУ, содержвшее адресный регистр, выходы которого соединены с входами дешифраторов, соответствующий вход одного из которых соединен с одним из входов элемента ИЛИ выход которого подключен к одним из

входов адресного регистра и другого дешифратора, информационные, адресные шины, шины записи и считывания. Выходы одного из дешифраторов соединены с одними из входов накопителя 2j|.

Однако в таком устройстве сложна аппаратурная реализация управления адреоиыми шинами накопителя и недостаточно использована возмоншость снижения пот2

ребляемой мощности за счет уменьшения входных токов адресных шин накопителя. Одними из основных потребителей тока в полупроводниковых запоминающих элементах на биполярных многоэмиттерных транзисторах являются адресные входы, например, для элементов К 155 РУ1 один невыбранный адресный вход потребляет 11 ма. В режиме хранения информации, все адресные входы запоминающего элемента оказываются невыбранными (потенциал логического О), вследствие чего токи, потребляемые по этим входам максимальны.,

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что предложенное устройство содержит коммутатор, дополнительные элементы ИЛИ и элемент НЕ вход которого соединен с выходом элемента ИЛИ, а выходс первыми входами дополнительных элементов ИЛИ, вторые входы которых соединены с выходами одного из дешифраторов. Выходы дополнительных элементо

ИЛИ соединены с соответствующими входами накопителя, выходы которого соединены с входами коммутатора, управляющий вход которого подключен к одному из выходов адресного регистра.

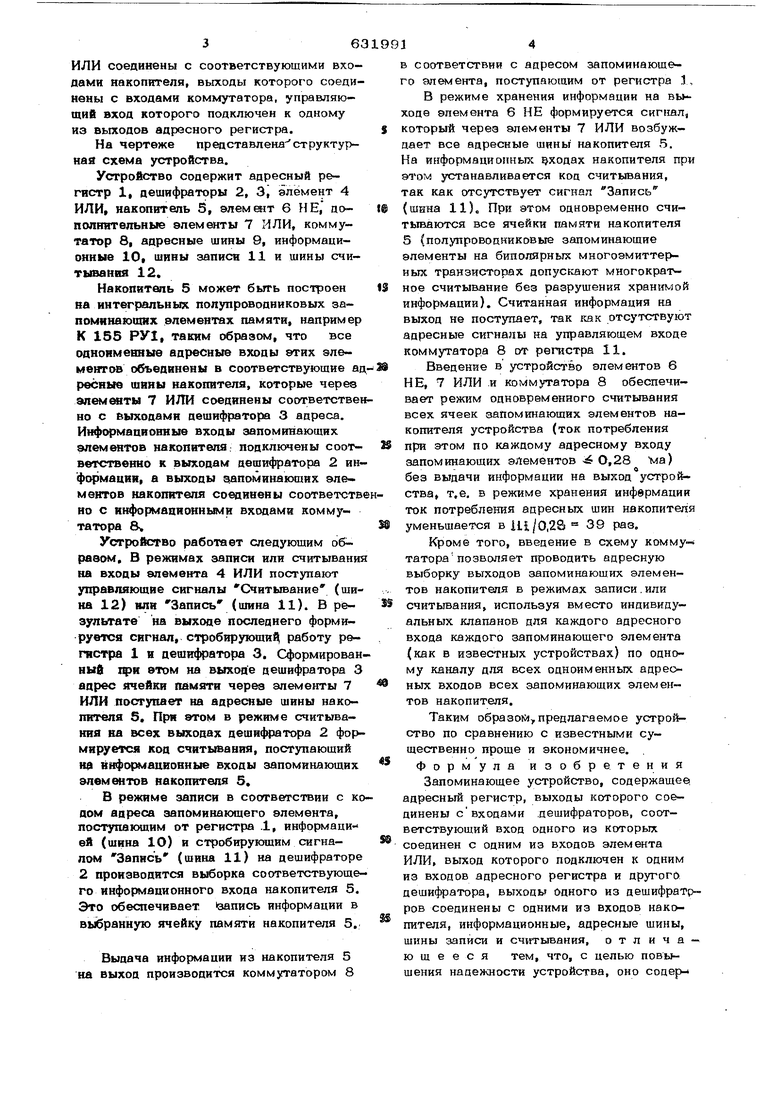

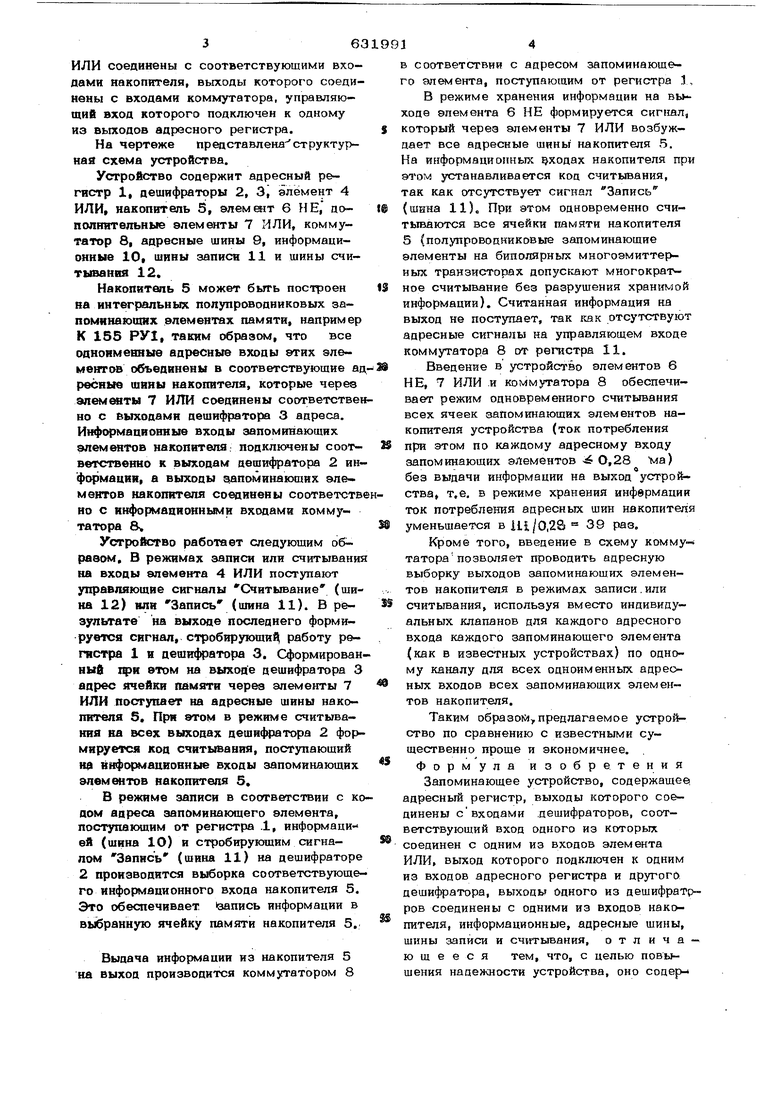

На чертеже пред ставленаструктурная схема устройства.

Устройство Содержит ацресный регистр 1, дешифраторы 2, 3, элемент 4 ИЛИ, накопитель 5, &пем&1Г 6 НЕ, дополнительные элементы 7 ИЛИ, коммутатор 8, адресные шины 9, информационные 10, шины записи 11 и шины считывания 12.

Накопитепь 5 может быть построен на интегральных полупроводниковых запоминающих элементах памяти, например К 155 РУ1, таким образом, что все оононменяью адресные входы этих злементов объединены в соответствующие ад ресные шины накопителя, которые через 7 ИЛИ соединены соответственно с выходами дешифратор 3 адреса. Информадионные входы запоминающих элементов накопителя подключены соответственно к выходам дешифратора 2 информации, а выходы упоминающих элементов накопителя соединены соответствно с информационными входами коммутатора

УстроЛ гво работает следующим обравом, В режимах записи или считывания на входы элемента 4 ИЛИ поступают управляющие сигналы Считывание (шина 12) вли Запись (шина 11). В результате на выходе последнего формируется сигнал, стробируюши работу регистра 1 и дешифратора 3. Сформированный 1ФИ этом на выходе дешифратора 3 адрес ячейки памяти через элементы 7 ИЛИ поступает на адресные шины накопителя 5. При этом в режиме считывания на всех выходах дешифратора 2 формируется код считывания, поступающий И9 информационные входы запоминающих элемттов накопителя 5.

В режиме записи в соответствии с кодом адреса запоминающего элемента, поступающим от регистра .1, информацией (шина 1О) и стробируюшим сигналом Запись (шина 11) на дешифраторе 2 производится выборка соответствующего информационного входа накопителя 5. Это обеспечивает запись информации в выбранную ячейку памяти накопителя 5,

Выдача информации из накопителя 5 на выход производится коммутатором 8

в соответствии с адресом запоминающего элемента, поступающим от регистра 1

В режиме хранения информации на вььходе элемента 6 НЕ формируется сигнал, который через элементы 7 ИЛИ возбуждает все адресные шины накопителя 5. На информационных уходах накопителя при этом устанавливается коц считывания, так как отсутствует сигнал Запись (шина 11). При этом одновременно считываются все ячейки памяти накопителя 5 (полупровоцниковые запоминающие элементы на биполярных многоэмиттерных транзисторах дoпyc caют многократное считывание без разрушения хранимой информации). Считанная информация на выход не поступает, так как отсутствуют ацресные сигналы на управляющем входе коммутатора 8 от решстра 11.

Введение в устройство элементов 6 НЕ, 7 ИЛИ .и коммутатора 8 обеспечивает режим одновременного считывания всех ячеек запоминающих элементов накопителя устройства (ток потребления при этом по каждому адресному входу запоминающих элементов - 0,28 va) без выдачи информации на выход устройства, т.е. в режиме хранения инфврмации ток потребления адресных шин накопителя уменьшается Bili/0,2S 39 раз.

Кроме того, введение в схему коммутаторапозволяет проводить адресную выборку выходов запоминающих элементов накопителя в режимах записи. или считывания, используя вместо индивидуальных клапанов для каждого адресного входа каждого запоминающего элемента (как в известных устройствах) по одному каналу для всех одноименных адресных входов всех запоминающих элементов накопителя.

Таким образом,предлагаемое устройство по сравнению с известными существенно проще и экономичнее. Формула изобретения

Запоминающее устройство, содержащее. адресный регистр, выходы которого соединены с входами дешифраторов, соответствующий вход одного из которых соединен с одним из входов элемента ИЛИ, выход которого подключен к одним из входов адресного регистра и другого дешифратора, выходы одного из дешифратрров соединены с одними из входов накопителя, информационные, адресные шины, шины записи и сч1ггывания, о т л и ч а - ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит коммутатор, дополнительные элем ей- ты ИЛИ и элемент НЕ, вход которого соединен с выходом элемента ИЛИ, а вьтхоп с первыми входами дополнительных элеме тов ИЛИ, вторые входы которых соединены с выходами одного из дешифраторов; выходы

дополнительных элементов ИЛИ соединены с соответствующими входами накопителя,

выходы которого соединены с входами коммутатора, управляющий вход которого подключей к одному из выходов адресного регистра.

Источники информации, принятые RO внимание при экспертизе:

1.Шебанин В. В. Интегральные функциональные узлы для запоминающих уст ройств, Советское рацио , 1976,

с. 12-24, 40-42,

2.Авторское свидетельство СССР № 522523, кл. Q 11 С 11/34, 18.10.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1979 |

|

SU847377A1 |

| Многоканальное устройство для формирования временных интервалов | 1980 |

|

SU932603A1 |

| Устройство для записи информации в накопитель | 1976 |

|

SU568079A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Программируемый контроллер | 1991 |

|

SU1833870A1 |

| Устройство для реализации логических функций | 1977 |

|

SU732878A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Многоканальное устройство для форми-РОВАНия ВРЕМЕННыХ иНТЕРВАлОВ | 1979 |

|

SU815875A1 |

| Запоминающее устройство | 1978 |

|

SU696543A1 |

Авторы

Даты

1978-11-05—Публикация

1977-04-11—Подача