Изобретение относится к измерению в технике цифровой связи и может быт использовано для контроля качества цифрового сигнала, а именно для контроля амплитуды, действующего значения шумов и оценки вероятности ошибок в тракте цифрового регенератора.

Целью изобретения является повышение точности контроля качества цифрового сигнала путем обеспечения раздельного измерения амплитуды сигнала и действующего значения шумов в каналах связи и их отношения сигнал/шум.

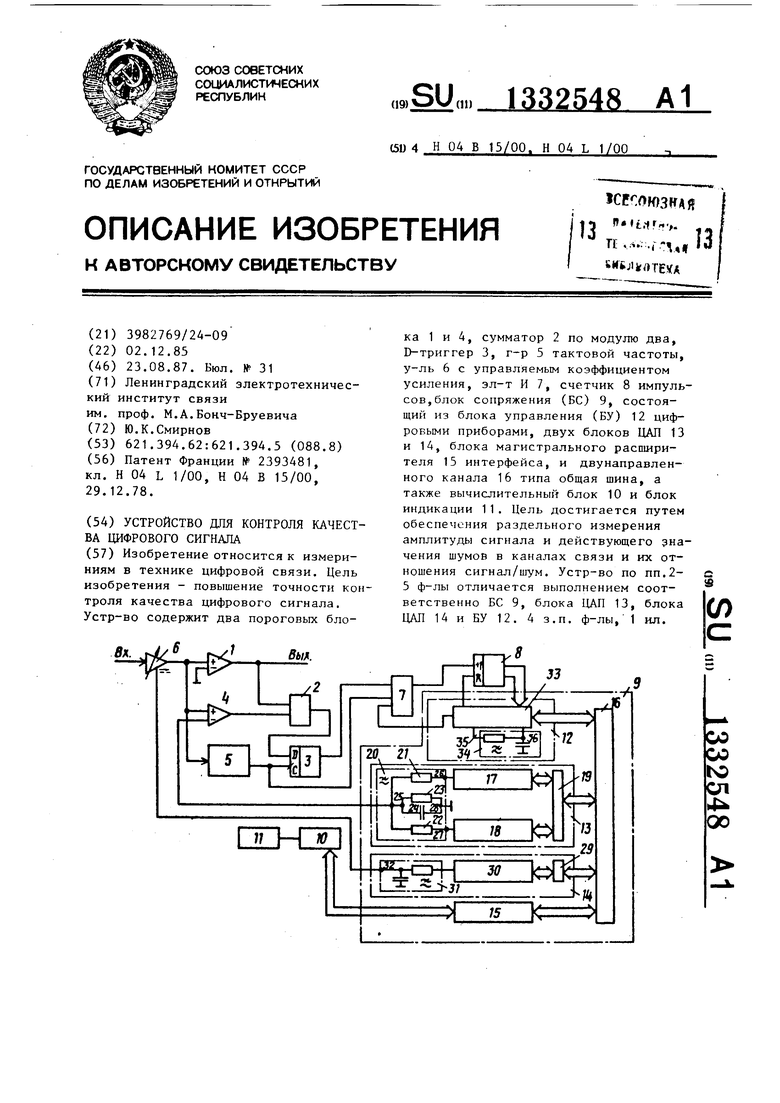

На чертеже представлена блок-схема устройства для контроля качества цифрового сигнала.

Устройство для контроля качества цифрового сигнала содержит первый пороговый блок 1, сумматор 2 по модулю два, D-триггер 3, второй пороговый блок 4, генератор 5 тактовой частоты, усилитель 6 с управляемым коэффициентом усиления, элемент-И 7, счетчик 8 импульсов, блок 9 сопряжения, вычислительный блок 10, блок 11 индикации. Блок 9 сопряжения содержит блок 12 управления цифровыми при40

,первый блок 13 цифроаналогового о ность ошибки на выходе порогового преобразования, второй блок 14 цифро- аналогового преобразования, блок 15 магистрального расширителя интерфейса, двунаправленный канал 16 типа общая шина. В свою очередь первый блок 13 цифроаналогового преобразования содержит первый 17 и второй 18 цифро- аналоговые преобразователи, блок 19 коммутации и управления, фильтр 20 нижних частот, причем последний содержит три резистора 21, 22 и 23 соответственно, конденсатор 24, первые полюсы всех резисторов и конденсаторов соединены с выходом 25 фильтра 20 нижних частот, вторые полюсы первого и второго резисторов являются входами 26 и 27 фильтра 20 нижних частот, а вторые полюсы третьего резистора 23 и конденсатора 24 соединены с общей клеммой 28.

Второй блок 14 цифроаналогового преобразования содержит блок 29 управления, цифроаналоговый преобразователь 30, фильтр 31 нижних частот, выход 32 которого является выходом второго блока 14 цифроаналогового преобразования. В качестве фильтра 31 нижних частот используется RC-фильтр нижних частот. Блок 12 управления

блока 1. На второй вход второго по рогового блока 4 поступает напряже ние порога с выхода 25 фильтра 20 нижних частот первого блока 13 циф аналогового преобразования. Сигнал с выходов первого 1 и второго А по роговых блоков поступают на входы сумматора 2 по модулю два, на выхо образуются импульсы псевдоошибок, возникающие в те моменты времени, когда напряжение на выходе усилите 6 находится между оптимальным напр жением порога, поступающим на втор вход порогового блока 1, и неоптим ным напряжением порога, поступающи на второй вход второго порогового блока 4. Вероятность псевдоошибок на выходе сумматора 2 по модулю дв стремится в процессе переходного п цесса к постоянному уровню, что до стигается автоматическим изменение указанного неоптимального порога в процессе работы устройства.

Сигнал с выхода усилителя ,6 пос пает также на генератор 5 тактовой 55 частоты, который выделяет из сигна напряжение тактовой частоты. D-три гер 3 привязывает импульсы псевдоо бок к фазе напряжения тактовой 4ас

45

50

цифровыми приборами содержит блок 33 управления и блок 34 задержки, выполненный в виде RC-фильтра нижних частот. Вход 35 блока 34 задержки является пусковым выходом блока 33 управления, а выход 36 блока 34 задержки является пусковым входом блока 33 управления. Блок 34 задержки выполнен в виде RC-фильтра нижних частот.

Устройство для контроля качества цифрового сигнала работает следующим образом.

Цифровой бинарный сигнал, несущи

информацию, поступает на вход усилителя 6 с коэффициентом усиления, управляемым напряжением с выхода 32 фильтра 31 нижних частот, подключенного своим входом к выходу цифроаналогового преобразователя 30, На выходе усилителя 6 благодаря управляющему напряжению поддерживается определенное значение амплитуды сигнала, небходимого для работы первого 1 и

второго 4 пороговых блоков. На второй вход первого порогового блока 1 поступает напряжение, соответствующее оптимальному значению порога, обеспечивающему минимальную вероят0

о ность ошибки на выходе порогового

блока 1. На второй вход второго порогового блока 4 поступает напряжение порога с выхода 25 фильтра 20 нижних частот первого блока 13 цифро- аналогового преобразования. Сигналы с выходов первого 1 и второго А пороговых блоков поступают на входы сумматора 2 по модулю два, на выхоДе образуются импульсы псевдоошибок, возникающие в те моменты времени, когда напряжение на выходе усилителя 6 находится между оптимальным напряжением порога, поступающим на второй вход порогового блока 1, и неоптимальным напряжением порога, поступающим на второй вход второго порогового блока 4. Вероятность псевдоошибок на выходе сумматора 2 по модулю два стремится в процессе переходного процесса к постоянному уровню, что достигается автоматическим изменением указанного неоптимального порога в процессе работы устройства.

Сигнал с выхода усилителя ,6 поступает также на генератор 5 тактовой 5 частоты, который выделяет из сигнала напряжение тактовой частоты. D-триггер 3 привязывает импульсы псевдооши- бок к фазе напряжения тактовой 4асто5

0

ты, что обеспечивает выполнение фазовых соотношений при стробировании импульсов псевдоошибок напряжением тактовой частоты элемента И 7, позволяя разделять пачки импульсов псев доошибок на отдельные импульсы длительностью полпериода тактовой частоты, подсчитываемые в дальнейшем счетчиком 8 импульсов.

В процессе первого цикла работы на выходе 25 фильтра 20 нижних частот первого блока 13 цифроаналогово- го преобразования формируется пороговое напряжение л и , поступающее на второй вход порогового блока 4. При этом частота импульсов псевдоошибок устанавливается в процессе переходного процесса на уровне р равном, например, 0,1.

В процессе второго цикла работы устройства на выходе 25 фильтра 20 формируется пороговое напряжение ли,, также поступающее на второй вход второго порогового блока 4. При этом частота импульсов псевдоошибок устанавливается в процессе переходного процесса на уровне р РОЩ например р может быть равным 0,01.

on 7

Величины связаны уравнениями

1 («)

-2

Ib)

J.

(1)

и -ди: ъб.

и.

СГ

-амплитуда цифрового сигнала,

-действующее значение шумов в канале

СВЯЗИ,

А1),ли Ь) значение порогов, поступающих в виде напряжений с первого аналогового выхода блока 9 сопряжени на второй вход второго порогового блока 4,

Вычислительный блок 10 на основании величин ди|° и AU вычисляет амплитуду сигнала

,/Ь) (а)

О ли a-aUi b

Zг I

аг-Ъ

(2)

действующее значение

.„(ь) )

ди, -ли.

а-Ь

отношение сигнал/шум

(Ь) IQ)

Up, ди a-AU , b

- :

,

(4)

Кроме того, по величине отношения сигнал/шум путем обращения распределения смеси сигнала с шумом (например, нормального распределения) може быть вычислена вероятность ошибок при передаче информационных сигналов Указанные результаты измерений отображаются на блоке 11 индикации.

Если измеренное значение амплиту- ды сигнала U , соответствующее регулирующему напряжению , не находится в оптимальном диапазоне, необходимом для работы пороговых блоков 1 и 4, то вычислительный блок 10 производит вычисление регулирующего напряжения , необходимого для обеспечения требуемого значения амплитуды сигнала на первых входных пороговых блоков 1 и 4. Это вычисление проводится на основании известной формулы характеристики АРУ

(U,,, ),

где К - коэффициент усиления усилителя 6,

а также известных текущей и требуемой амплитуд сигнала U и U путем решения управления

35

F(U.rvo )

F(u,,).

Код напряжения из канала ввода-вывода вычислительного блоха

10 поступает через блок 15 магистрального расширителя, канал 16 типа общая шина, блок 29 управления, циф- роаналоговый преобразователь 30 и фильтр 31 нижних частот на выход 32 фильтра 31 нижних частот, являющийся выходом второго блока 14 цифроанало- гового преобразования, и далее на вход управления коэффициентом усиления усилителя 6 с управляемым коэф-- фициентом усиления.

Рассмотрим процесс формирования пороговых напряжений и /.U в предлагаемом устройстве.

Вычислительный блок 10 через блок

15 магистрального расширителя, канал 16 типа общая шина и блок 12 управления передает сигнал сброса счетчика 8. На первый 17 и второй 18 цифро- аналоговые преобразователи через

51

блок 15 магистрального расширителя, канал 16 типа общая шина, блок 19 коммутации и управления поступает и вычислительного блока 10 первоначално код нулевого напряжения, приводящий к подаче на второй вход второго порогового блока 4 нулевого пороговго напряжения. В регистре состояния блока 33 управления вычислительный блок 10 устанавливает разрешающий потенциал, поступающий на выход разрешения счета блока 9 сопряжения. Этот потенциал через элемент И 7 рарешает счетчику 8 подсчет импульсов псевдоошибок. Вычислительный блок 10 в течение ряда временных дискретов осуществляет ввод в память количества импульсов со счетчика 8 импульсов. При этом одновременно провдится в каждом временном дискрете вычитание из содержимого счетчика 8 числа, соответствунлцего числу импул

сов с опорной частотой р ,2

от которые могли бы появиться в

временного дискрета, и суммирование полученных разностей в оперативной памяти вычислительного блока, а также передача в первый блок 13 цифро- аналогового преобразования полученной суммы. Код этой суммы поступает из вычислительного блока 10 через магистральный расширитель 15, канал 16 типа общая шина, блок 19 коммутации и управления на первый 17 и второй 18 цифроаналоговые преобразователи. Напряжения, полученные на выходах 26 и 27 цифроаналоговых преобразователей 17 и 18 суммируются с соответствующими весами в фильтре 20 нижних частот, где одновременно благодаря наличию конденсатора 24 производится сглаживание коммутационных помех цифроаналоговых преобразователей. Суммирование с весами напряжений от двух цифроаналоговых преобразователей 17 и 18 обеспечивает уменьшение дискретности напряжения на выходе 25 и, следовательно, увеличение точности измерений по сравнению со случаем использования одного циф- роаналогового преобразователя имеющего недостаточное число разрядов преобразуемого кода (в данном примере это число разрядов равно 10). По мере увеличения количества временных дискретов напряжение лЦ (илидС,) на вьЕходе 25 стремится к установившемуся значению. Время переходного

8

б

процесса при различных параметрах устройства может быть вычислено заранее. Следовательно, его зависимость от параметров устройства известна. Поэтому после установления напряжений AU| и эквивалентные им двоичные коды могут быть запомнены и использованы для вьшисления измеряемых параметров по формулам (2.) - (4).

Величины и ли определяются соответственно значениями опорных вероятностей р , р , а точность

-or. 1

их измерений - коэффициентами преоб разования цифроаналоговых преобразователей (фактически максимальным количеством импульсов псевдоошибок, накапливаемых в оперативной памяти устройства в течение цикла измерения). В формулах (1) - (4) параметры а и b для шумов с нормальным распределением равны взятым с обратными знаками квантилям нормального распределения уровня 2р и 2р соответственОЬ 1 Oh. о

но.

Таким образом, предлагаемое устройство для контроля качества цифрового сигнала позволяет оценить вероятность ошибок в канале связи.

Формула изобретения

1. Устройство для контроля качества цифрового сигнала, содержащее последовательно соединенные первый пороговый блок, первый вход которого соединен с первым входом второго порогового блока, сумматор по модулю два, к второму входу которого подключен выход второго порогового блока, и D-триггер, к входу синхронизации которого подключен выход генератора тактовой частоты, отличающееся тем, что с целью повышения точности контроля путем обеспе-

чения раздельного измерения амплитуды сигнала и действующего значения шумов в каналах связи и их отношения сигнал/шум, введен усилитель, выход которого подключен к первому входу первого порогового блока и входу генератора тактовой частоты, а также последовательно соединенные элемент И, счетчик импульсов и блок сопряжения, подключенный к последовательно соединенным вычислительному блоку и блоку индикации, причем второй аналоговый выход блока сопряжения подключен к входу управления козффициентом усилителя, первый аналоговый выход - к вТорому входу второго порогового блока, выход разрешения счета - к первому входу элемента И, к второму и третьему входам которого подключены соответственно выход генератора тактовой частоты и выход D-триггера, а выход сброса блока сопряжения подключен к второму входу счетчика импульсов.

2,Устройство по П.1, о т л и - чающееся тем, что блок сопряжения содержит блок управления цифровыми приборами, первьй и второй блоки цифроаналогового преобразования, блок магистрального расширителя интерфейса, информационные, управляющие входы и выходы и входы контроля состояния которых подключены к соответствующим линиям двунаправленного канала, при этом аналоговые выходы первого и второго блоков цифроаналогового преобразования являются первым и вторым аналоговыми выходами блока сопряжения, информационными входами которого являются информационные входы блока управления цифровыми приборами, выходы разрешения счета и сброса которого являются выходами разрешения счета и сброса блока сопряжения, входом разрешения счета которого является вход разрешения счета блока магистрального расширителя интерфейса.

3.Устройство по п.2, отличающееся тем, что первый блок цифроаналогового преобразования со;держит первый и второй цифроаналого- вые преобразователи, информационные управляющие входы и выходы контроля состояния которых подключены соответ

ор Л.Лангазо 3850/56

Составитель Л.Тимошина Техред Л. Сердюкова

Корре Подпи

Тираж 638 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

ственно к информационным, управляющим выходам и входам приема состояния блока коммутации и управления, информационные, управляющие входы и выходы контроля состояния которых являются входами и выходами первого блока цифроаналогового преобразования, а аналоговые выходы первого и второго цифроаналоговых преобразователей подключены к входам фильтра нижних частот, выход которого является аналоговым выходом первого блока цифроаналогового преобразования.

4.Устройство по п.2, отличающееся тем, что второй блок цифроаналогово преобразования содержит последовательно соединенные блок управления, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является аналоговым выходом второго блока цифроаналогового преобразования, а информационные, управляющие входы и выходы контроля состояния блока управления являются входами и выходами второго блока ци- фроаналогового преобразования.

5.Устройство по п.2, о т л и ч а- ю щ е е с я тем, что блок управления цифровьми приборами содержит блок управления, пусковой выход которого подключен к входу блока задержки, выход которого подключен к пусковому входу блока управления, выход разрешения счета и выход сбрбса которого являются выходом разрешения счета и выходом сброса блока управления цифровыми приборами, информационные управляющие входы и выходы

и вькоды контроля состояния которого являются информационными, управляющими входами и выходами и вькодами контроля состояния блока управления.

Корректор А, Тяско Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля качества цифрового сигнала | 1988 |

|

SU1555882A2 |

| Устройство для контроля качества цифрового сигнала | 1986 |

|

SU1506571A2 |

| СПОСОБ АКУСТИКО-ЭМИССИОННОГО КОНТРОЛЯ КАЧЕСТВА СВАРНОГО ШВА В ПРОЦЕССЕ СВАРКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2008 |

|

RU2379677C1 |

| МНОГОКАНАЛЬНАЯ АКУСТИКО-ЭМИССИОННАЯ СИСТЕМА ДИАГНОСТИКИ КОНСТРУКЦИЙ | 2017 |

|

RU2664795C1 |

| СПОСОБ ОБНАРУЖЕНИЯ В ПРОЦЕССЕ СВАРКИ ДЕФЕКТОВ В СВАРНЫХ ШВАХ И ОПРЕДЕЛЕНИЯ ИХ МЕСТОПОЛОЖЕНИЯ ПО АКУСТИЧЕСКИМ СИГНАЛАМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2424510C2 |

| Устройство для контроля цифрового канала связи | 2019 |

|

RU2731678C1 |

| Способ акустико-эмиссионного контроля металлических объектов и устройство для его осуществления | 2020 |

|

RU2736175C1 |

| Устройство для контроля цифрового канала связи | 1985 |

|

SU1358099A1 |

| МНОГОКАНАЛЬНОЕ АКУСТИКО-ЭМИССИОННОЕ УСТРОЙСТВО | 2019 |

|

RU2726278C1 |

| СПОСОБ АКУСТИКО-ЭМИССИОННОГО КОНТРОЛЯ КАЧЕСТВА СВАРНОГО ШВА В ПРОЦЕССЕ СВАРКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2442155C2 |

Изобретение относится к измери- ниям в технике цифровой связи. Цель изобретения - повышение точности контроля качества цифрового сигнала. Устр-во содержит два пороговых блока 1 и 4, сумматор 2 по модулю два, D-триггер 3, г-р 5 тактовой частоты, у-ль 6 с управляемым коэффициентом усиления, эл-т И 7, счетчик 8 импульсов, блок сопряжения (БС) 9, состоящий из блока управления (БУ) 12 цифровыми приборами, двух блоков ЦАП 13 и 14, блока магистрального расширителя 15 интерфейса, и двунаправленного канала 16 типа общая шина, а также вычислительный блок 10 и блок индикации 11. Цель достигается путем обеспечения раздельного измерения амплитуды сигнала и действующего значения шумов в каналах связи и их отношения сигнал/шум. Устр-во по пп.2- 5 ф-лы отличается выполнением соответственно БС 9, блока ЦАП 13, блока ЦАЛ 14 и БУ 12. 4 з.п. ф-лы, 1 ил. с (Л f aq-c:: I JL -W V.J1 75

| СПОСОБ ПОДАВЛЕНИЯ ИММУННЫХ РЕАКЦИЙ | 2008 |

|

RU2393481C1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-08-23—Публикация

1985-12-02—Подача