Изобретение относится к вычислительной технике и может быть использовано для построения прецизионных цифроаналоговых преобразователей.

Цель изобретения - повьшения точности с одновременным упрощением устройства.

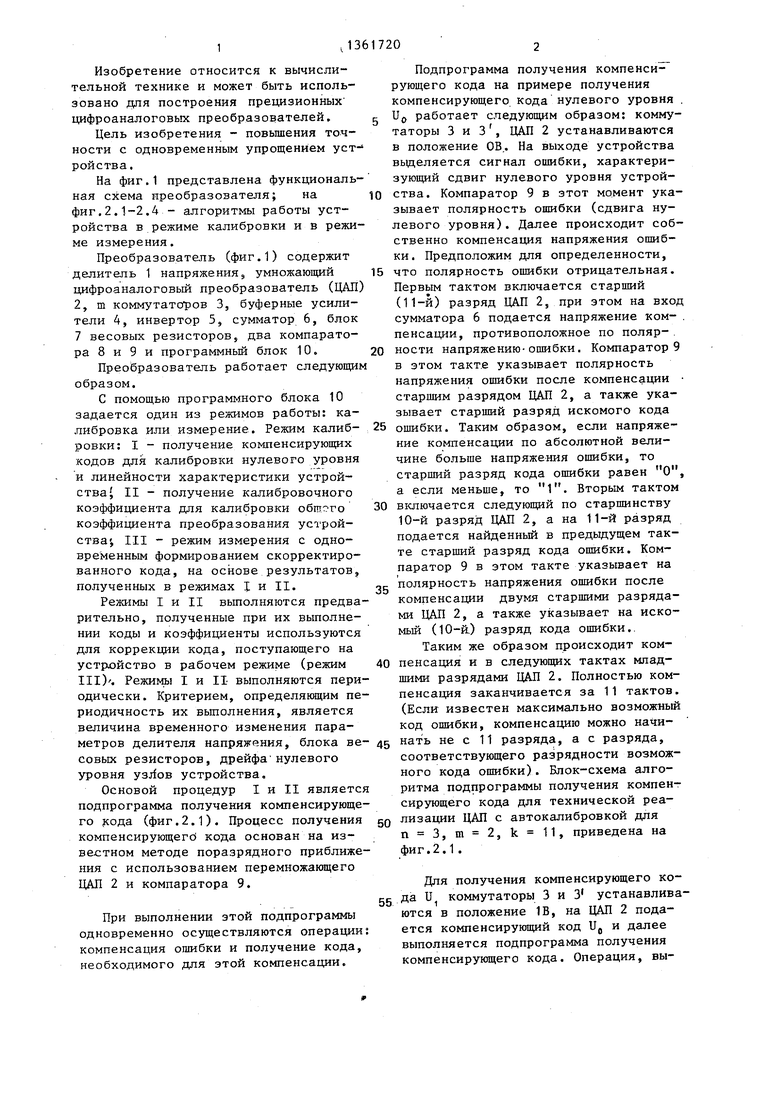

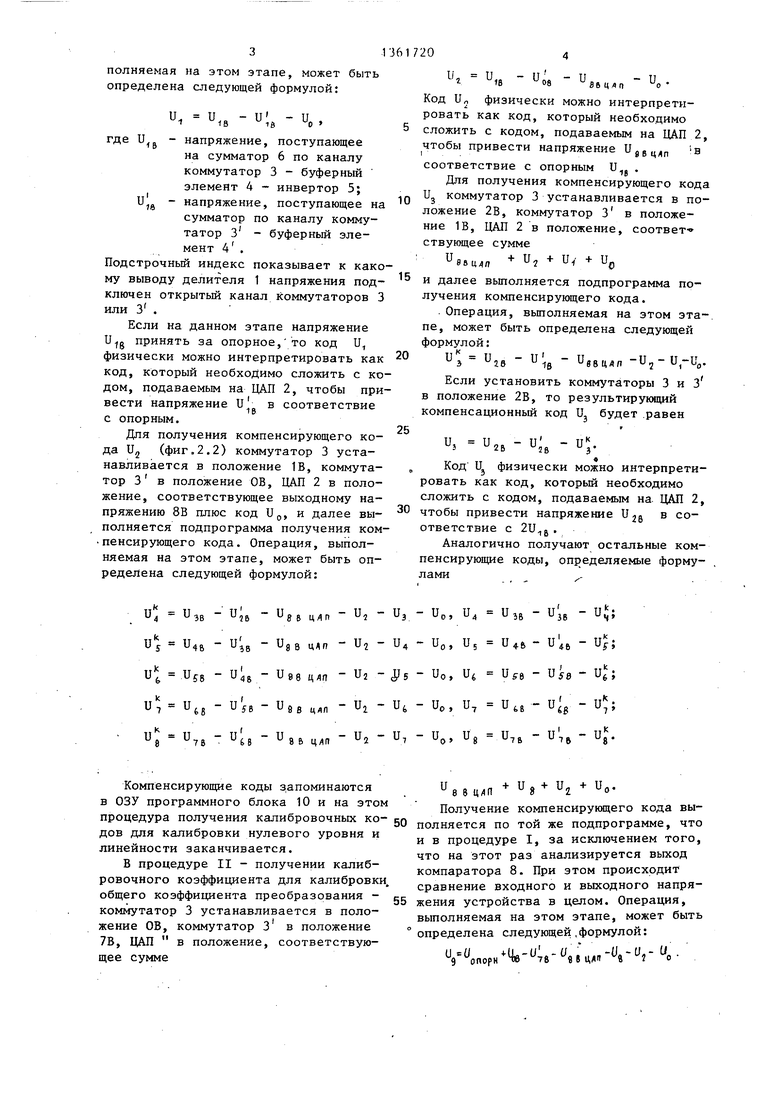

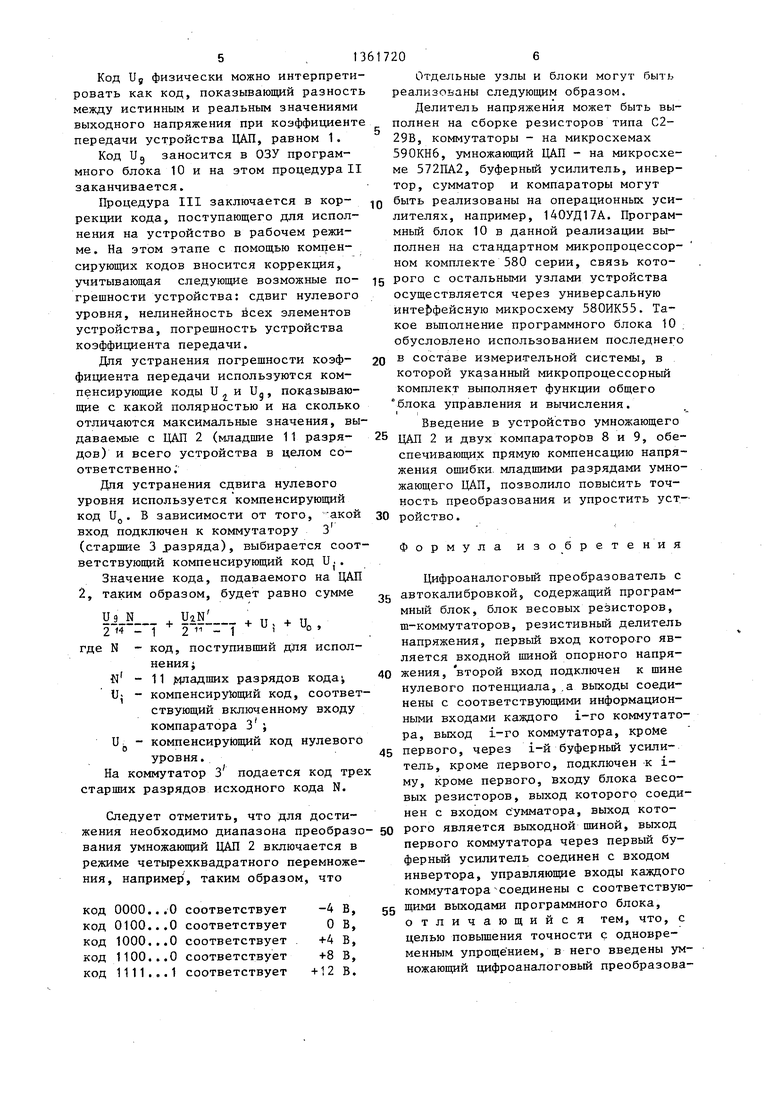

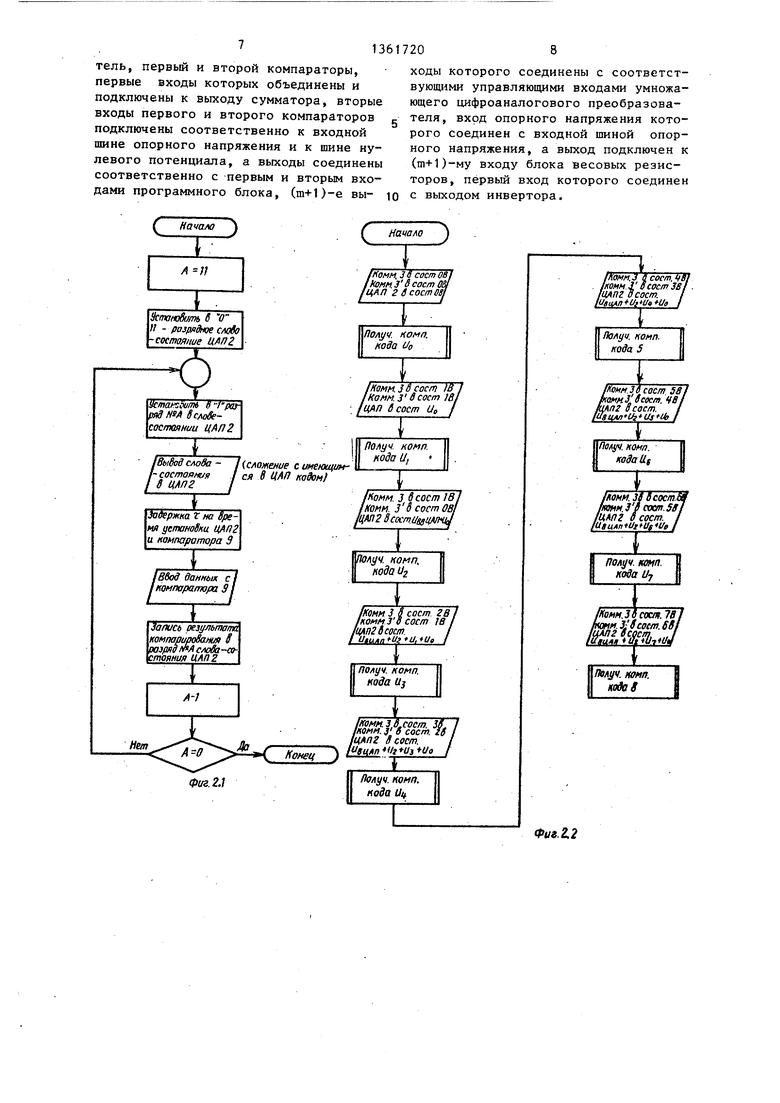

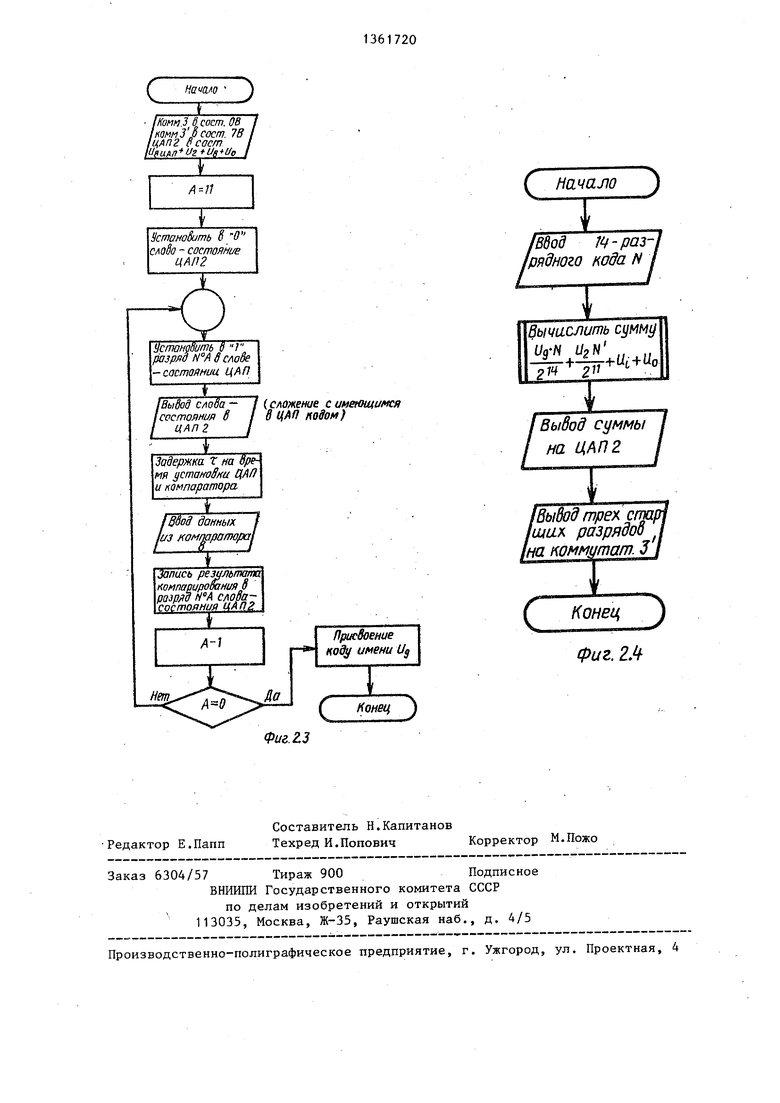

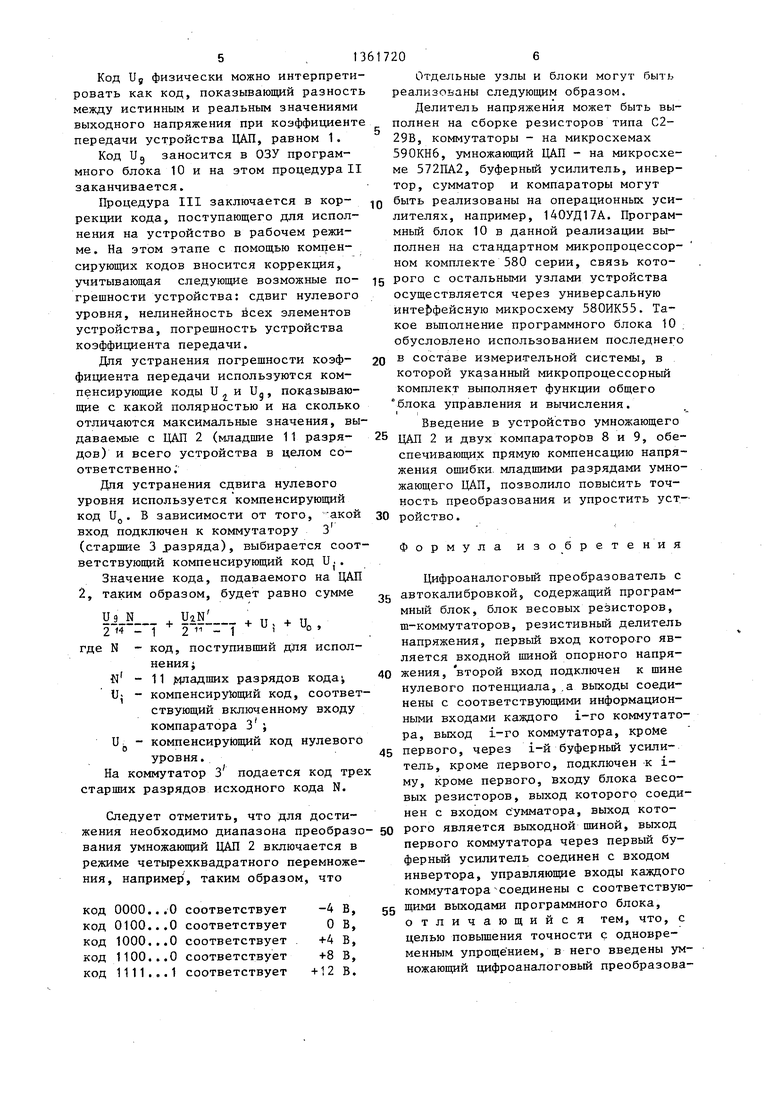

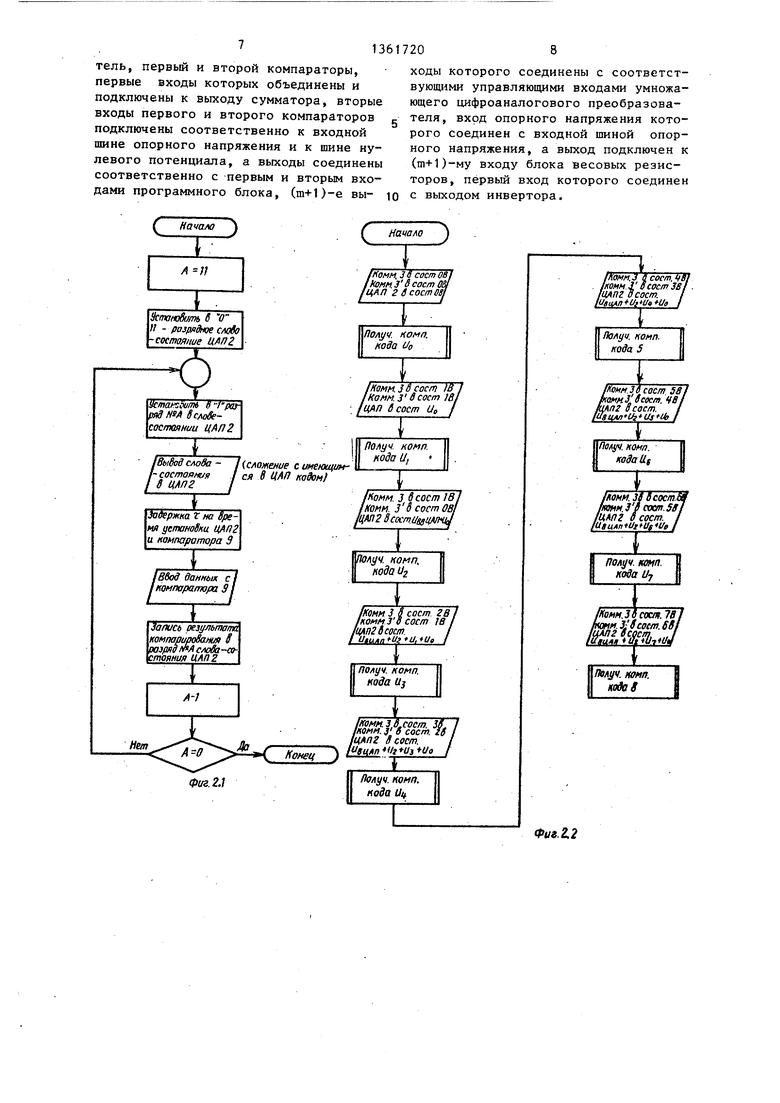

На фиг.1 представлена функциональная схема преобразователя; на фиг.2.1-2.4 - алгоритмы работы устройства в режиме калибровки и в режиме измерения.

Преобразователь (фиг.1) содержит делитель 1 напряжения, умножающий цифроаналоговый преобразователь (ЦАП) 2, m коммутаторов 3, буферные усилители 4, инвертор 5, сумматор 6, блок 7 весовых резисторовS два компаратора 8 и 9 и программный блок 10.

Преобразователь работает следующим образом.

С помощью программного блока 10 задается один из режимов работы: калибровка или измерение. Режим калиб- ровки: I - получение компенсирующих кодов для калибровки нулевого уровня и линейности характеристики устройства J II - получение калибровочного коэффициента для калибровки обшого коэффициента преобразования усп рой- ства , III - режим измерения с одновременным формированием скорректированного кода, на основе результатов, полученных в режимах I и II.

Режимы I и II выполняются предварительно, полученные при их выполнении коды и коэффициенты используются для коррекции кода, поступающего на устройство в рабочем режиме (режим III). I и II выполняются периодически. Критерием, определяющим периодичность их вьтолнения, является величина временного изменения параметров делителя напряжения, блока ве- совых резисторов, дрейфа нулевого уровня узЛов устройства.

Основой процедур I и II является подпрограмма получения компенсирующего сода (фиг .2.1). Процесс получения компенсирующегс) кода основан на известном методе поразрядного приближения с использованием перемножающего ЦДЛ 2 и компаратора 9.

При выполнении этой подпрограммы

одновременно осуществляются операции компенсация ошибки и получение кода, необходимого для этой компенсации.

Подпрограмма получения компенсирующего кода на примере получения компенсирующего кода нулевого уровня Ujj работает следующим образом: коммутаторы 3 и 3, ЦАП 2 устанавливаются в положение ОБ,. На выходе устройства выделяется сигнал ошибки, характери- зуюпщй сдвиг нулевого уровня устройства. Компаратор 9 в этот момент указывает полярность ошибки (сдвига нулевого уровня). Далее происходит собственно компенсация напряжения ошибки. Предположим для определенности, что полярность ошибки отрицательная. Первым тактом включается старший (11-й) разряд ЦАП 2, при этом на вхо сумматора 6 подается напряжение ком- пенсации, противоположное по поляр-, ности напряжению-ошибки. Компаратор 9 в этом такт.е указывает полярность напряжения ошибки после компенсации старшим разрядом ЦАП 2, а также указывает старший разряд искомого кода ошибки. Таким образом, если напряжение компенсации по абсолютной величине больше напряжения ошибки, то старший разряд кода ошибки равен О а если меньше, то 1. Вторым тактом включается следуюш 1й по старшинству 10-й разряд ЦАП 2, а на 11-й разряд подается найденный в предьщущем такте старший разряд кода ошибки. Компаратор 9 в этом такте указывает на полярность напряжения ошибки после компенсации двумя старшими разрядами ЦАП 2, а также указывает на искомый (10-й.) разряд кода ошибки..

Таким же образом происходит компенсация и в следуюш;их тактах младшими разрядами ЦАП 2. Полностью компенсация заканчивается за 11 тактов. (Если известен максимально возможный код ошибки, компенсацию можно начинать не с 11 разряда, а с разряда, соответствующего разрядности возможного кода ошибки). Блок-схема алгоритма подпрограммы получения компенсирующего кода для технической реализации ЦАП с автокалибровкой для , , , приведена на фиг.2.1.

Для получения компенсирующего кода и коммутаторы 3 и 3 устанавливаются в положение 1Б, на ЦАП 2 подается компенсирующий код Uj и далее выполняется подпрограмма получения компенсирующего кода. Операция, выполняемая на этом этапе, может быть определена следующей формулой:

и.

и.

- UL - и«.

где - напряжение, поступающее на сумматор 6 по каналу коммутатор 3 - буферный элемент 4 - инвертор 5; - напряжение, поступающее на сумматор по каналу коммутатор З - буферный элемент 4 .

Подстрочньш индекс показывает к какому выводу делителя 1 напряжения подключен открытый канал коммутаторов 3 или 3 .

Если на данном этапе напряжение

и

16

принять за опорное, то код U,

физически можно интерпретировать как код, который необходимо сложить с кодом, подаваемым на ЦАП 2, чтобы привести напряжение и„ в соответствие с опорным.

Для получения компенсирующего кода Uj (фиг.2.2) коммутатор 3 устанавливается в положение 1В, коммутатор 3 в положение ОБ, ЦАП 2 в положение, соответствующее выходному напряжению 8В плюс код Up, и далее выполняется подпрограмма получения ком- пенсирующего кода. Операция, выполняемая на этом этапе, может быть определена следующей формулой:

УЗВ - и;в - Uj5 ц/(п - и, - из - и„,и,

U4B - и; - UjB цлп - и - U4 - Uo,Us

Ujg - Uljg - Use ЦЛП - Us - ils - Uo,Ui

- UjB - USB ц,л - Uj - U - Uo,U

u,g - - Ug, ,„ - V, и, - и,, Uj

Компенсирующие коды запоминаются в ОЗУ программного блока 10 и на этом процедура получения калибровочных кодов для калибровки нулевого уровня и линейности заканчивается.

В процедуре II - получении калибровочного коэффициента для калибровки, общего коэффициента преобразования - коммутатор 3 устанавливается в положение ОБ, коммутатор З в положение 7В, ЦАП в положение, соответствующее сумме

и.

16 - Uo8 - ,,,,„ - и„.

Код Uo физически можно интерпретировать как код, который необходимо сложить с кодом, подаваемым на ЦАП 2, чтобы привести напряжение Ujg в соответствие с опорным U,. .

Для получения компенсирующего кода Uj коммутатор 3 устанавливается в положение 2В, коммутатор З в положение 1В, ЦАП 2 в положение, соответ- ствующее сумме и,,„ - и, -ь и, + и

и далее выполняется подпрограмма получения компенсирующего кода.

Операция, вьшолняемая на этом эта-, пе, может быть определена следующей формулой:

20

з Uje - u ie - ееМП -и,-и,-и„.

, о

Если установить коммутаторы 3 и З в положение 2В, то результирующий компенсационный код Uj будет .равен

з и, - и; - и.

Код Uj физически можно интерпретировать как код, который необходимо сложить с кодом, подаваемым на ЦАП 2, чтобы привести напряжение в соответствие с 2U.,j .

Аналогично получают остальные компенсирующие коды, определяемые формулами , , - u:;; u ,e - - -

u -,5 - Ug

Уевц.п U, U -b U,.

Получение компенсирунмцего кода вы- полняется по той же подпрограмме, что и в процедуре I, за исключением того, что на этот раз анализируется выход компаратора 8. При этом происходит сравнение входного и выходного напря- жения устройства в целом. Операция,

вьшолняемая на этом этапе, может быть определена следующей .формулой:

9 опорн

-и,-и,- и„.

5

Код Uy физически можно интерпретировать как код, показывающий разност между истинным и реальным значениями выходного напряжения при коэффициент передачи устройства ЦАП, равном 1,

Код и а заносится в ОЗУ программного блока 10 и на этом процедура II заканчивается.

Процедура III заключается в коррекции кода, поступающего для исполнения на устройство в рабочем режиме. На этом этапе с помощью компенсирующих кодов вносится коррекция, учитывающая следующие возможные погрешности устройства: сдвиг нулевого уровня, нелинейность йсех элементов устройства, погрешность устройства коэффициента передачи.

Для устранения погрешности коэффициента передачи используются компенсирующие коды и . и и., показывающие с какой полярностью и на сколько отличаются максимальные значения, выдаваемые с ЦАП 2 (младшие 11 разрядов) и всего устройства в целом соответственно.

Для устранения сдвига нулевого уровня используется компенсирующий код и. В зависимости от того, акой вход подключен к коммутатору З (старшие 3 разряда), выбирается соответствующий компенсирующий код U..

Значение кода, подаваемого на ЦАП 2, таким образом, будет равно сумме

УЭ N UaN 2 2

N - код, поступивший для исполнения i

11 младших разрядов кода , компенсируйщий код, соответствующий включенному входу компаратора 3 ; компенсирующий код нулевого уровня.

На коммутатор З подается код тре старших разрядов исходного кода N.

Следует отметить, что для достижения необходимо диапазона преобразования умножающий ЦАП 2 включается в режиме четьфехквадратного перемножения, например , таким образом, что

+ U; + и„

где

w и- и 0000...о соответствует-4 В,

0100...О соответствуетО В,

1000...О соответствует .+4 В,

1100...О соответствует+8 В,

1111...1 соответствует+12 В.

Отдельные узлы и блоки могут быть реализованы следующим образом.

Делитель напряжения может быть выполнен на сборке резисторов типа С2- 29В, коммутаторы - на микросхемах 590КН6, умножающий ЦАП - на микросхеме 572ПА2, буферньм усилитель, инвертор, сумматор и компараторы могут

быть реализованы на операционных усилителях, например, 140УД17А. Программный блок 10 в данной реализации выполнен на стандартном микропроцессор- ном комплекте 580 серии, связь которого с остальными узлами устройства осуществляется через универсальную интерфейсную микросхему 580ИК55. Такое выполнение программного блока 10 обусловлено использованием последнего

в составе измерительной системы, в которой указанный микропроцессорный комплект выполняет функции общего блока управления и вычисления.

Введение в устройство умножающего

ЦАП 2 и двух компараторов 8 и 9, обеспечивающих прямую компенсацию напряжения ошибки, мпадшими разрядами умножающего ЦАП, позволило повысить точность преобразования и упростить уст-

ройство.

Формула изобретения

Цифроаналоговьй преобразователь с

автокалибровкой, содержащий программный блок, блок весовых резисторов, т-коммутаторов, резистивный делитель напряжения, первый вход которого является входной шиной опорного напряжения, второй вход подключен к шине нулевого потенциала,,а выходы соединены с соответствующими информационными входами каждого i-ro коммутатора, выход i-ro коммутатора, кроме

первого, через i-й буферный усилитель, кроме первого, подключен -к i- му, кроме первого, входу блока весовых резисторов, выход которого соединен с входом с умматора, выход которого является выходной шиной, выход первого коммутатора через первый буферный усилитель соединен с входом инвертора, управляющие входы каждого коммутатора соединены с соответствующими выходами программного блока, отличающийся тем, что, с целью повышения точности с одновременным упрощением, в него введены умножающий цифроаналоговый преобразователь, первый и второй компараторы, первые входы которых объединены и подключены к выходу сумматора, вторые входы первого и второго компараторов подключены соответственно к входной шине опорного напряжения и к шине нулевого потенциала, а выходы соединены соответственно с -первым и вторьм входами программного блока, (т+1)-е вы- ю

ходы которого соединены с соответствующими управляющими входами умножающего цифроаналогового преобразователя, вход опорного напряжения которого соединен с входной шиной опорного напряжения, а выход подключен к (т+1)-му входу блока весовых резисторов, первый вход которого соединен с выходом инвертора.

С

.o

X

D

lKoM.3 Scocm.OB IxoMfi J o сост. ff 1цАП2 6cacm muKn- Uz Us Uo

A n

ScmamSumb 8 0 сло8о - состояние Ц АЛ 2

Фиг.гз

Редактор Е.Папп

Составитель Н.Капитанов

Техред И.Попович Корректор М.Пожо

Заказ 6304/57 Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

начало

/

i

Wod Щ-paz- рядного кода N

Bbi числить сумму

Ug N UgN ,. „ .U,-bUo

/

1

Вывод суммы на ал/72

i

Выбод трех cfmf IOILLK разрядов j /на коммипшгп-З

i

( КОНЕЦ J фиг. 2Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой феррозондовый измеритель азимута | 1987 |

|

SU1498913A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Способ калибровки линейности умножающего цифроаналогового преобразователя | 1985 |

|

SU1317657A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1427564A1 |

| СВЧ-амплифазометр | 1986 |

|

SU1350627A1 |

| Устройство для измерения времени установления выходного сигнала цифро-аналоговых преобразователей | 1985 |

|

SU1298916A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Устройство для измерения уровней сигнала изображения | 1987 |

|

SU1520672A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения прецизионных цифроаналоговых преобразователей. Цель изобретения - повышение точности с одновременным упрощением устройства. Устройство содержит делитель 1 напряжения, умножающий цифроаналого- вый преобразователь 2, m коммутаторов 3, -буферные усилители 4 инвертор 5, сумматор 6, блок 7 весовых резисторов, два компаратор,а 8, 9 и про- 1граммный блок 10. Введение в устройство умножающего цифроаналогового преобразователя 2 и двух компараторов 8, 9, обеспечивающих прямую компенсацию напряжения ошибки младшими разрядами умножающего цифроаналогового преобразователя, позволяет повысить точность преобразования и упростить устройство. 2 ил. с € (Л Bxpff опорного напряжения Вмод ОО о: o uzJ

| Балашов Е.П | |||

| и др | |||

| Микро- и ми- ниЭВМ.- Л.: Энергоатомиздат, 1984 | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-12-23—Публикация

1986-07-14—Подача