Изобретение относится к вычислительной технике и может быть использовано автономно или в комплексе с проблемно ориентированными вычислительными системами для решения дифференциальных уравнений.

Цель изобретения - увеличение быстродействия.

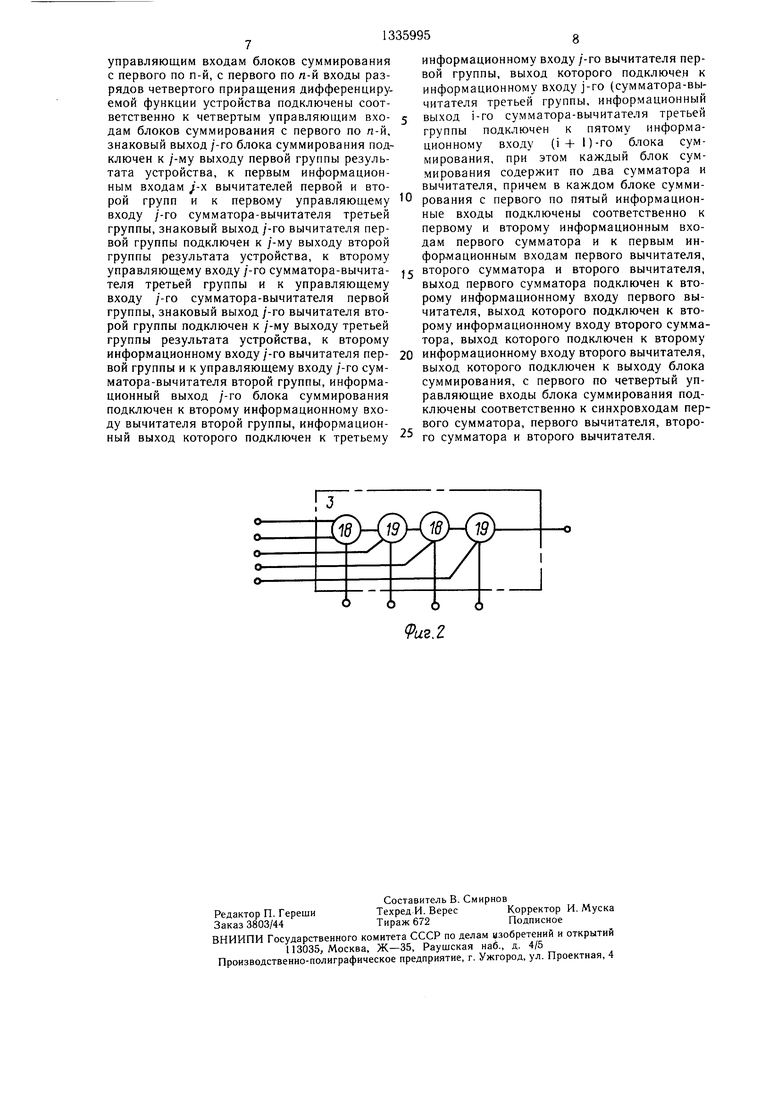

На фиг. 1 представлена схема устройства для п 4; на фиг. 2 - схема блока суммирования.

Устройство содержит п сумматоров 1, две группы из п сумматоров-БЫчитателей 2, п бло ков 3 суммирования, первую и вторую группы по п вычитателей 4 и 5, третуью группу из п сумматоров-вычитателей 6, с первого по четвертый входы 7-10 коэффициентов аппро ксимации дифференцируемой функции, входы 11 -14 разрядов с первого по четвертое приращение дифференцируемой функции, группа входов 15 коэффициентов аппроксимации дифференцируемой функции, входы 16 приращения аргументов дифференцируемой функции, выходы 17 результата.

Блок 3 суммирования содержит два сумматора 18 и два вычитателя 19.

Работа устройства при дифференцировании функций y (Xj) на основе формулы повышенной точности вида

Ах

кие Дх, у (х;);

yJ,y i)yM,y(i),.i) АХ, АХ,...,На основании выражения (3) значение

- разрядные векторы, пред- первого разряда y(x,)yi{x,)+у 2(х/) не- ставляющие собой раз- известного у (х;) определяется рядное изображение У(х,-), АХ.

fl,

,(х,-) 2-5,-|,, 2li 2- ВАУ1,

1--1,,

I, Г О -.,) 2-22д v, 2-з2«1д ,, (x,)Bj, lO, S,0(4)

У (х,-) (12ЛХ)- (25ЛУ,-23Лу-1 + + 13ду,2-ЗЛу,-з),(1)

которая в общем случае записывается так у (х;) (аЛх)(ЬоЛу,-biAy,i)4- + Ь2Лу,-2- ЬзАу,-з),(2)

осуществляется следующим образом. Запишем выражение (2) в виде

ЬоЛу/- biAyi-i+ Ь2Лу,-г аЛху (х,-) и представим его в разрядной форме

(х,) +

2 2- вАу,. (xOAxt il,

(3)

15

20

ОV V V V .

где Ь I bobib2b3l- матрица бинарных элементов, каждый столбец которой является разрядным вектором вида

i Ъi

Ь(г bft. Б, Ok,..,bt,

представляющим собой разрядное изображение числа bft, К О, 1,2, 3;

ду/ (Л у/,

ЛУ(-1, Лу.-а)

вектор, формируемый из

-х разрядов Лу,..-,Лу,-з соответственно;

ч

1,е о,0 2- §(,(x,-)S,, о,+ ((х,-)|-2- ,,,

у2(х,)

1о,ео,а 2-- а 1 2- ау2(х,)|, у(х,) , (х,) + у2(х,).

4I

Значение второго разряда у(х.,) yi (х,+ +У2(х,) формируется следующим образом

fl,

У|(Х.)ео2 2-25 2-Ь2- §), ,+ ,

LO, ео2 0,

1,

.,(5)

Г I, е о2 О 2-V,fU 2-3 +2-5а , (х,)е У2(х,.) ,е о2+ )yS(x,.)b-2- a fix е

10, ,.)|2; (х,.) , (х,) + (х,).

.Каждое, j-e значение разряда у{х/) 1 (х,-)+У2(х,-) формируется следующим образом

1о Г п - - , Vi-2-§Ay,.

jJt Оо; и

Г 1, , 2 -С + )) 2-( + аО-|;+ 2-2 5Ах,

l-l,S,0, eo -2 + a WAx + -g,.2((x,)e,,(6)

2-0 %aj 2-C/+2)0-i)+ 2-(, (X,) |., l,, e;+2-( -+0 aWy2(x,-)gy-2-f + a7)A + x |.

У2(х,-)

2-f/+ g(,J (;-i) 2-«2 +l | 2(x,)|, L0,e;, (x,)J.,(x,) + 2(x,).

Устройство работает следующим образом.которые поступают соответственно на третьи

В исходном состоянии на входы 7-1040 входы сумматора-вычитателя 6 и вычитателя

подаются значения бо, 6i, 1э2, бз на выходы5 и со сдвигом на первые входы сумматоров-вычитателей 6 и вычитателя 5 и со сдви11 -14, , и. подаются значения j-x раз-гом на первые входы сумматоров-вычитатерядов Ау„ , , Ау,-э исходныхлей 2 своих групп. На выходе первого блока 3

«VIп выражению (4) образуется значение

векторов Ay,-,...,Ayi, ,.-. , которое поступает на первый вход выAyi-i; АУ;-1 ,..., Ayi-2; Ау/-з читателя 4 на выходе которого сформируется

величина ЕОЬ поступающая на первый вход

Ayi-3, АУ|-з. На В.ХОД 15 подается зна-вычитателя 5, в котором вычисляется значечение а, а на вход Ji6 - значение j-x разря-ние еоь поступающее на первый вход сумма- дов АХ вектора АХ АХ,..., А После этогоу тора-вычитателя 6, в котором вычисляется в схеме устройства протекает переходнойзначение еш и подается на пятый вход вто- процесс, по окончанию которого на выходахрого блока 3. первого сумматора 1 в соответствии с (4) об-,. , разуется значение 2-2§О), которое подаетсяН а знаковых выходах блоков 3 и вычитана входы вычитателей 4 и 5 сумматора-вычи- 4 и 5 по выражению (5) образуются тателя 6 и со сдвигом 2- на первый вход55 f ° у,(х,), второго сумматора 1.У2(х,) первого разряда искомого результата,

На выходах первых сумматоров-вычита-которые поступают на выходы 17о, 17:, 172.

тедей 2 первой и второй групп по выраже-Аналогично на выходах вторых сумматора

нию (I) образуются значения ,1 и сумматоров-вычитателей 2 первой и второй групп по выражению (5) сформируются значения 2 а , которые поступают на соответствующие входы вычи- тателей 4 и 5 и второго сумматора-вычи- тателя 6. На выходах второго блока 3 и вторых вычитателей 4 и 5 по выражению (5) образуются значения , 02- 02- На выходе второго сумматора-вычитателя 6 образуется значение к, которое подается на пятый вход третьего блока. На знаковых выходах блоков 3 и вычитателей 4 и 5 образуются знак 2 и величины yi(Xi), У2(х,) второго разряда, поступающие на

112

ВЫХОДЫ 17(), 17i, 172.

В каждых J-X сумматоре 1 и суммато- рах-вычитателях 2 первой и второй групп по выражению (6) образуются значения

2Ч S.iJ ), 2f +-Vi 2-« + §o(j), поступающие на соответствующие входы jx вычитателей 4 и 5 и сумматора-вычитателя 6. На выходах j-ro блока 3, J-X вычитателей 4 и 5 сумматора- вычитателя 6 по ,выпажени о (6) образуются величины ,, eoj, &о/, е/, а на выходах знаковых разрядов блока 3, вычитателей 4 и 5 - соответственно, знак |/ и величины У|(Х,), У2(х,) j-ro разряда искомого век-гора у(х;), поступающие на j-й выходы 17о,

17,, .

На выходах последних сумматора 1 и сум- маторов-вычитателей 2 сформируются зна- чения 2- +4Т на выходах последних блока 3, вычитателей 4 и 5 и сумматора-вычитателя 6 остатков -

значения 2 S, iee , ti, , „, а на выходах знаковых разрядов блока 3 и вычитателей 4 и 5 -- знак j и ве;1ичины yi(xi), yz(Xi) последнего разряда искомого вектора y(xi), поступающие на выходы 17,, и, 1 .

Таким образом, за время, равное задержке сигнала между входом и выходом элементов схемы, на выходах устройства

i i -с

17о, 17ь 172 образуется искомый вектор вида

V((yi(X,) + 2(xO),...,|n(ynX,-)+y2{X,))

Формула изобретения

Устройство для дифференцирования функций, х;одержащее три сумматора, отличающееся тем, что, с целью увеличения быстродействия, в него введены (п-3) сумматора, где п - разрядность дифференцируемой функции, три группы по п сумматоров-вы- 50 читателей, две группы по п вычитателей и п блоков суммирования, с первого по т-й входы коэффициентов аппроксимации дифференцируемой функции группы устройства, где т-разрядность коэффициентов аппроксиционным входам, начиная с (2/+ 1)-го первой группы /-Х сумматоров-вычитателей первой и второй групп, первый вход приращения аргумента дифференцируемой функции устройства подключен к синхровходу первого сумматора, -й вход приращения аргумента дифференцируемой функции устройства, где k 2,...,п, подключен к синхровходам /г-го сумматора, k-1)-го сумматора-вычитателя третьей группы и (k-1)-го вычита- теля первой группы, (я+1)-й вход приращения аргумента дифференцируемой функции устройства подключен к синхровходам п-го сумматора-вычитателя третьей группы и п-го вычитателя первой группы, выходы с первого по т-й i -ro сумматора, где / 1,..., п- 1, подключены соответственно к информационным входам, начиная с второго, второй группы (/4-l)-ro сумматора и к информационным входам первых групп /-го сумматора-вычитателя третьей группы, г-го вычитателя первой и г-го вычитателя Второй групп, выходы с первого по т-й л-го сумматора подключены соответственно к информационным входам первых групп п-го сумматора-вычитателя третьей группы, п-го вычитателя первой и п-го вычитателя второй групп, выходы с первого по т-й /-го сумматора вычитателя первой группы подключены соответственно к информационным входам, начиная со второго, второй группы (г +1)-го сумматора вычитателя первой группы и к информационным входам второй группы г -го сумматора- вычитателя третьей группы, выходы с первого по т-й п-го сумматора-вычитателя первой группы подключены соответственно к информационным входам второй группы п-го сумматора-вычитателя третьей группы, выходы с первого по т-й г -го сумматора-вычитателя второй группы подключены соответственно к информационным входам, начи ная со второго, второй группы (г +П-го сумматора-вычитателя второй группы и к информационным входам второй группы г -го вычитателя первой группы, выходы с первого по т-й п-го сумматора-вычитателя второй группы подключены соответственно к информационным входам группы п-го вычитателя первой группы, первый, второй, третий и четвертый входы коэффициентов д5 аппроксимации дифференцируемой функции второй группы устройства подключены к соответствующим информационным входам блоков суммирования с первого по л-й, с первого по п-й входы разрядов первого приращения дифференцируемой функции устройства подключены соответственно к первым управляющим входам блоков суммирования с первого по л-й, с первого по п-й входы разрядов второго приращения дифференцируемой функции устройства подключены соответственно к вторым управляющим входам бломации дифференцируемой функции, подклю- 55ков суммирования с первого по п-й, с первого

чены соответственно к информационнымпо п-й входы разрядов третьего приращевходам, начиная с 2 /-го, где / 1,...,п, пер-ния дифференцируемой функции устройствой группы /-ГО сумматора и к информа-ва подключены соответственно к третьим

5

0

.

,.

и

0

ционным входам, начиная с (2/+ 1)-го первой группы /-Х сумматоров-вычитателей первой и второй групп, первый вход приращения аргумента дифференцируемой функции устройства подключен к синхровходу первого сумматора, -й вход приращения аргумента дифференцируемой функции устройства, где k 2,...,п, подключен к синхровходам /г-го сумматора, k-1)-го сумматора-вычитателя третьей группы и (k-1)-го вычита- теля первой группы, (я+1)-й вход приращения аргумента дифференцируемой функции устройства подключен к синхровходам п-го сумматора-вычитателя третьей группы и п-го вычитателя первой группы, выходы с первого по т-й i -ro сумматора, где / 1,..., п- 1, подключены соответственно к информационным входам, начиная с второго, второй группы (/4-l)-ro сумматора и к информационным входам первых групп /-го сумматора-вычитателя третьей группы, г-го вычитателя первой и г-го вычитателя Второй групп, выходы с первого по т-й л-го сумматора подключены соответственно к информационным входам первых групп п-го сумматора-вычитателя третьей группы, п-го вычитателя первой и п-го вычитателя второй групп, выходы с первого по т-й /-го сумматора вычитателя первой группы подключены соответственно к информационным входам, начиная со второго, второй группы (г +1)-го сумматора вычитателя первой группы и к информационным входам второй группы г -го сумматора- вычитателя третьей группы, выходы с первого по т-й п-го сумматора-вычитателя первой группы подключены соответственно к информационным входам второй группы п-го сумматора-вычитателя третьей группы, выходы с первого по т-й г -го сумматора-вычитателя второй группы подключены соответственно к информационным входам, начи ная со второго, второй группы (г +П-го сумматора-вычитателя второй группы и к информационным входам второй группы г -го вычитателя первой группы, выходы с первого по т-й п-го сумматора-вычитателя второй группы подключены соответственно к информационным входам группы п-го вычитателя первой группы, первый, второй, третий и четвертый входы коэффициентов 5 аппроксимации дифференцируемой функции второй группы устройства подключены к соответствующим информационным входам блоков суммирования с первого по л-й, с первого по п-й входы разрядов первого приращения дифференцируемой функции устройства подключены соответственно к первым управляющим входам блоков суммирования с первого по л-й, с первого по п-й входы разрядов второго приращения дифференцируемой функции устройства подключены соответственно к вторым управляющим входам бло5ков суммирования с первого по п-й, с первого

управляющим входам блоков суммирования с первого по п-й, с первого по п-й входы разрядов четвертого приращения дифференцируемой функции устройства подключены соответственно к четвертым управляющим входам блоков суммирования с первого по /г-й, знаковый выход/-ГО блока суммирования подключен к /-му выходу первой группы результата устройства, к первым информационным входам /-Х вычитателей первой и второй групп и к первому управляющему входу /-ГО сумматора-вычитателя третьей группы, знаковый выход/-го вычитателя первой группы подключен к /-му выходу второй группы результата устройства, к второму управляющему входу/-го сумматора-вычитателя третьей группы и к управляющему входу /-ГО сумматора-вычитателя первой группы, знаковый выход /-го вычитателя второй группы подключен к /-му выходу третьей группы результата устройства, к второму

10

15

информационному входу/-го вычитателя пер вой группы, выход которого подключен к информационному входу j-ro (сумматора-вы читателя третьей группы, информационный выход i-ro сумматора-вычитателя третьей группы подключен к пятому информа ционному входу (i + 1)-го блока сум мирования, при этом каждый блок сум мирования содержит по два сумматора и вычитателя, причем в каждом блоке суммирования с первого по пятый информационные входы подключены соответственно к первому и второму информационным входам первого сумматора и к первым информационным входам первого вычитателя, второго сумматора и второго вычитателя, выход первого сумматора подключен к второму информационному входу первого вычитателя, выход которого подключен к второму информационному входу второго сумма тора, выход которого подключен к второму

-- -fJ I -- -.«,.., uuirtvj j, I vjpvjl w пидЛЛГиЧСМ 14 DIUUUIViy

информационному входу /-го вычитателя пер- 20 информационному входу второго вычитателя,

RO И -Л Ы Z лгтг%ог п тгм .......-

вой группы и к управляющему входу /-го сумматора-вычитателя второй группы, информационный выход /-ГО блока суммирования подключен к второму информационному входу вычитателя второй группы, информационный выход которого подключен к третьему

25

выход которого подключен к выходу блока суммирования, с первого по четвертый управляющие входы блока суммирования подключены соответственно к синхровходам первого сумматора, первого вычитателя, второго сумматора и второго вычитателя.

0

5

информационному входу/-го вычитателя первой группы, выход которого подключен к информационному входу j-ro (сумматора-вычитателя третьей группы, информационный выход i-ro сумматора-вычитателя третьей группы подключен к пятому информационному входу (i + 1)-го блока суммирования, при этом каждый блок суммирования содержит по два сумматора и вычитателя, причем в каждом блоке суммирования с первого по пятый информационные входы подключены соответственно к первому и второму информационным входам первого сумматора и к первым информационным входам первого вычитателя, второго сумматора и второго вычитателя, выход первого сумматора подключен к второму информационному входу первого вычитателя, выход которого подключен к второму информационному входу второго сумматора, выход которого подключен к второму

, uuirtvj j, I vjpvjl w пидЛЛГиЧСМ 14 DIUUUIViy

0 информационному входу второго вычитателя,

20 информационному входу второго вычитателя,

..-

25

выход которого подключен к выходу блока суммирования, с первого по четвертый управляющие входы блока суммирования подключены соответственно к синхровходам первого сумматора, первого вычитателя, второго сумматора и второго вычитателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Асинхронный матричный вычислитель обратных тригонометрических функций | 1982 |

|

SU1132286A1 |

| Декодер кода Рида-Маллера первого порядка по максимуму правдоподобия | 1990 |

|

SU1775857A1 |

| Аппроксимирующий функциональный преобразователь | 1983 |

|

SU1160430A1 |

| Вычислительное устройство | 1983 |

|

SU1083187A1 |

| Измерительный функциональный преобразователь | 1981 |

|

SU983704A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1983 |

|

SU1107134A2 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

Изобретение относится к вычислительной технике и может использоваться автономно или в комплексе с вычислительными системами для решения дифференциальных уравнений. Целью изобретения является увеличение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит п сумматоров 1, первую и вторую группы из п сумматоров-вычитате- лей 2 в каждой, п блоков 3 суммирования, первую и вторую группы по п вычитателей 4 и 5 в каждой, третью группу из п суммато- ров-вычитателей 6. 2 ил. (Л оо со СП со со ел

| Цифровое дифференцирующее устройство | 1980 |

|

SU955052A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровое дифференцирующее устройство | 1980 |

|

SU932492A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-29—Подача