гольных импульсов, выход которого подключен к первому входу первого элемента И, второй вход которого по ключен к выходу первого триггера, выход первого элемента И соединен с входом первого счетчика, выход которого подключен к входу второго счетчика, выход которого подключен к первому входу счетчика TaKtOB, выходы которого соединены соответст венно с входами первого дешифратора,, группа вых:одов которого соедине на с четвертым выходом блока, управляющий выход первого дешифратора подключен к третьему входу первого элемента И и к первы входам второг и третьего элементов И, вторые вход которых соединены с управляющим выходом второго дешифратора,.группа входов которого соединена с пятым выходом блока, входы второго дешифратора соединены с выходами счет чика циклов,.первый вход которого и первый вход первого элемента ИЛИ соединены с выходом элемента задерж 5 ки, вход которого и третий выход блока подключены к выходу второго элемента И| выход третьего элемента И соединен с первым входом первого триггера, второй вход которого является входом блока, выход первого триггера через одновибратор под-,; ключен к единичным входам второго и третьего триггеров, к второму входу счетчика циклов и к второму входу первого элемента ИЛИ,- выход которого соединен с вторым входом счетчика тактов, счетные входы второго и третьего триггеров соединены с выходом первого счетчика, единичный и нулевой выходы третьего триггера соединены соответственно с входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ, единичный и нулевой выходы третьего триггера соединены с первым выходом блока, единичный и нулевой выходы второго триггера соединены с вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Цифровое устройство для преобразования координат | 1981 |

|

SU960808A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Графический интерполятор | 1985 |

|

SU1401509A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Цифровой преобразователь координат | 1980 |

|

SU943715A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для обработки приращений вектора | 1984 |

|

SU1203510A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

1. УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ КООРДИНАТ, содержащее блок постоянной памяти, первая группа входов которого подключена к выходам дешифратора, два коммутатора и три регистра, первые входы которых являются соответственно первым, вторым и третьим информационными входами устройства, два сумматора-вычитателя, выходы которых соединены с вторыми входами первого и второго регистров и с первым и вторым выходами устройства, два переключающих элемента, выходы первого из которых соединены с первыми входами первого и второго сумматоров-вычитателей, выходы второго переключающего элемента соединены с вторыми вxoдa в первого и второго сумматоров-вычитателей, управляющие входы которых подключены к первому выходу блока управления , второй выход которого соединен с управляющими входами первого и второго переключающих элементов, первого и второго коммутаторов, выход первого коммутатора соединен с первым входом дешифратора, вход блока управления является управляющим входом устройства, отличающееся тем, что, с целью сокращения оборудования, оно содержит два сдвигателя/ группу дешифраторов и два мультиплексора, информационные входы которых соединены соответственно с информационными выходами первого и второго регистров, управляющие входы которых соединены с третьим выходом блока управления, четвертый выход которого подключен к управляющим входам первых и вторых мультиплексоров и сдвигателей, выходы первого и второго мультиплекссфов подключены к информационным входам второго коммутатора, информа(Л ционные входы первого коммутатора соединены с выходами знаковых разрядов первого и второго регистров, выход второго коммутатора подключен к второму входу дешифратора, выходы третьего регистра соединены с информационными входами группы дешифратсг-( рое, управляющие входы которых соединены с пятым выходом блока управления, ;с а выходы подключены к второй группе 4i входов блока постоянной памяти, пер4 вый и второй выходы которого соедисл нены с информационными входами первого и второго сдвигателей, выходы которых подключены к информационным входам первого и второго переключающих элементов. 2. Устройство по п. 1, о т л и ч аю щ е 6 с я тем, что блок управления содержит триггеры, элементы И, ИЛИ, задержки, счетчики, дешифраторы, счетчик тактов, счетчик циклов, одновибратор и генератор прямоу

1

Изобретение относится вычислительной технике и может быть использовано для аппаратурной реализации операций преобразования прямоугольных и полярных координат в прямоуголные в системах управления роботами, манипуляторами, а также в различных навигационных системах.

Известно устройство для вычисления координат вектора, содержащее четыре сдвигающих регистра, три сумматора-вычитателя, элемент И, два коммутатора и блок постоянной памяти П.

Недостатком устройства является относительно низкое быстродействие, 5 также деформация длины вектора в результате его поворота.

Наиболее близким по технической сущности к изобретению является цифровой преобразователь координат, содержащий блок постоянной памяти, устройство управления, два коммутатора и три регистра, входы первого и второго из которых соединены соответственно с выходами первого и второго сумматоров-вычитателей, выходы которых являются выходами устройства причем входы первого и второго элементов НЕ соединены с выходами

5 первого и второго регистров и с

одними входами первого и второго KOM мутаторов, а выходы через другие входы этих же коммутаторов соединены с входами третьего коммутатора,

10 управлякхций вход которого соединен с управляющими входами ключей и с соответствующим выходом устройства управления, а выход через дешифратор соединен с одной группой входов блока постоянной памяти, другая группа входов которого через распределитель соединена с соответствующими выходами разрядов третьего реги- , стра, а также через элемент ИЛИ-НЕ,

20 и устройство управления с управляющим входом распределителя, последний выход которого подключен к одному из входов устройства управления, соответствующий выход которого

25 соединен с управляющими входами сумматоров-вычитателей, одни входы ко3

торых через соответствующие выходы первого и второго ключей подключены к выходам блока постоянной памяти, а другие входы подключены соответственно к вторым выходам второго и

первого ключей, причем выходы старши разрядов первого и второго регистров соединены с управляющими входами первого и второго коммутаторов, атакже с соответствующими входами устройства управления 23.

Недостатками известного устройства являются большие затраты постоянной памяти, а также жесткая за симость между разрядностью устройства и его быстродействием.

Целью изобретения является сокращение оборудования. .

Поставленная цель достигается тем, что устройство для цифрового преобразования координат, содержаще блок постоянной памяти, первая группа входов которого подключена к выходам дешифратора, два /коммутатор и три регистра, первые входы которых являются соответственно первым, вторым и третьим информационными входами устройства, два сумматора вычйтателя, выходы кото рых соединены с вторыми входами первого и второго регистров и с первым и вторым выходами устройства два переключающих элемента, выходы первого из которых соединены с первыми входами первого и второго сумматоров-вычитателей, выходы второго переключающего элемента соединены с вторыми входами первого и второго сумматоров-вычитателей, управляющие входы которых подключены к первому выходу блока упраления, второй выход которого соединен с управляющими входами первого и второго переключающих элементов, первого и второго коммутаторов, выход первого коммутатора соединен с первым входом дешифра тора, вход блока управления является управляющим входом устройства, содержит два сдвигателя, группу дешифраторов и два мультиплексора, информационные входы которых соединены соответственно с информационными выходами первого и второго регистров, управляюиие входы коториых соединены с третьим выходом блока управления, четвертый выход которого подключен к управляющим входа первых и вторых мультиплексоров

kkS .

и сдвигателей, выходы первого и второго мультиплексоров подключены к информационным входам второго коммутатора, информационные вхоS ды первого коммутатора соединены с выходами знаковых разрядов первого и второго регистров, выход второго KOMMyTaTqja подключен к второму входу дешифратора, выходм третьего регистра соединены с ин0формационными входами группы деамфраторов, управляющие входы которых соединены с пятым аыходсм блока управления, а выходы подклюмефш к второй группе входов бярка постоянной

15 памяти, первый и втснэой выходы которого соединены с информацисмными входа-, ми первого н второго сдвигате1№Й, выходы которых подключены к информационным входам первого и второго

20 переключающих элементов.

Блок управления устройства содержит триггеры, элементы И, ИШ, задержки, счетчики ,д 1Ифраторы, счётчик Тактов, счетчик циклов, одновибратор и генератор г ямоугольных импульсов, выход которого подключен к первому входу первого элемента И, второйвход которого подключен к выходу первого триггера, выход первого

30 элемента И соединен с входом первого счетчика, выход которого подключен к входу второго счетчика, выход которсн о подключен к первому входу счетчика тактов, шдходы

35 которого соединены соответственно с входами педвого дешифратора, группа обходов которого соединена с четвертым выходом блока, управляющий выход первого дешифрато40ра подключен к третьему входу первого элемента И и к входам второго и третьего элементов И, вторые входы.кот{фых соединены с управляющим выходом второго деши(|фато45ра, группа выходов которого соединена с пятым выходом блока, входы второго дешифратора соединены с вы- . ходами счетчика циклов, першей которого и первый вход первого эле50мента ИЛИ соединены с выходом элемента Задержки, вход которого и третий выход блока подключены к выходу второго элемента И, выход третьего элемента И соединен с первым входом

55 первого триггера, второй вход которого является входом блока, выход первого триггера через одновибрато э подключен к единичным входам второго и третьего триггеров, к второму входу сметчика циклов и к второму входу первого элемента ИЛИ, выход которого соединен с вторым входом счетчика тактов, счетные входы второго и третьего триггеров соединены с выходом первого счетчика, единичный и нулевой выходы третьего триггера соединены соответственно с входами второго элемента ИЛИ., выходы первого и второго элементов ИЛИ, ещи ничный и нулевой выходы третьего (Триггера соединены соответственно с входами второго элемента ИЛИ выход первого и второго элементов ИЛИ, единичный и нулево( выходытретьего триггера соединены с первым выходом блока, единичный и нулевой выходы второго триггера соединены с вторым выходом блока.

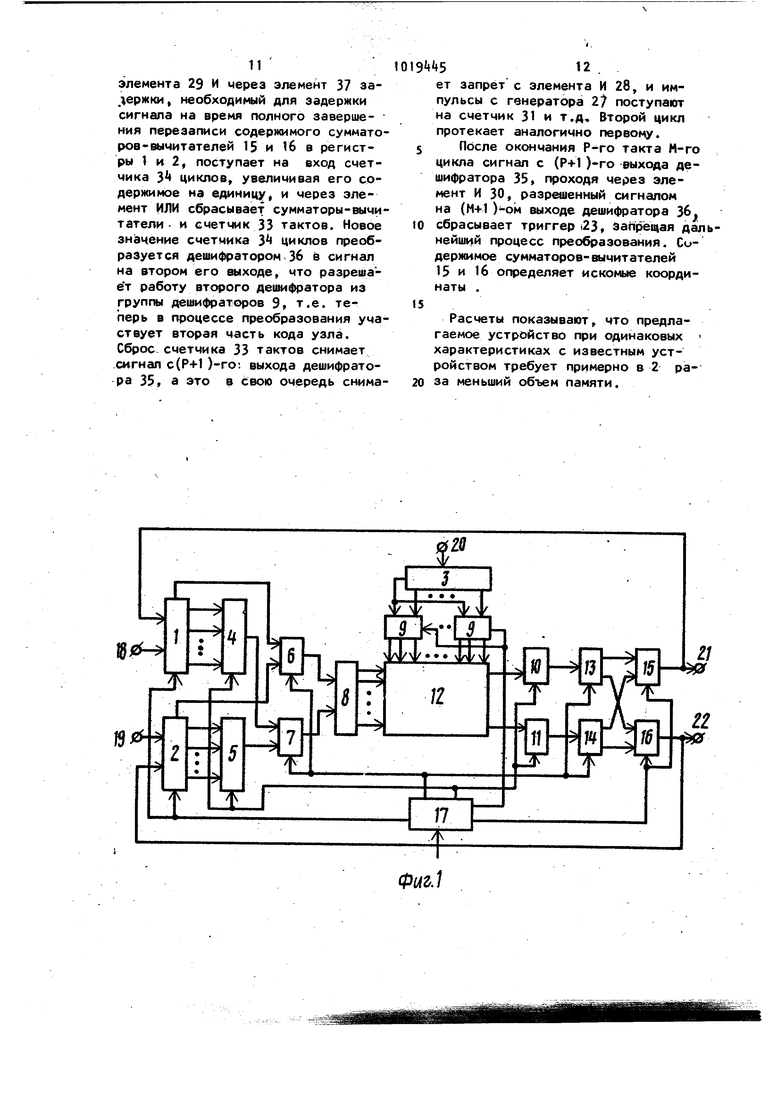

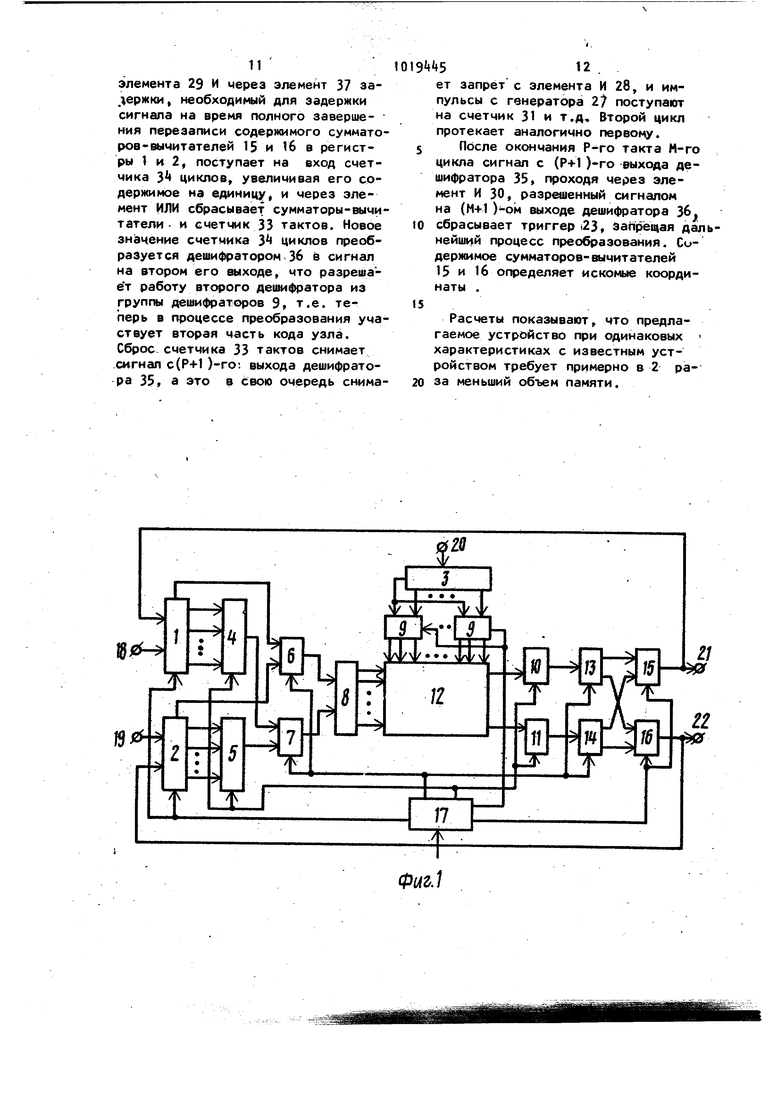

На фиг. 1 представлена структурна схема устройства цифрового преобразования координат; на фиг 2 - схема блока управления.

Устройство содержит регистры 1-3, мультиплексоры k и 5, коммутаторы 6 и 7. дешифратор 8, группу дешифраторов 9, сдвигатели 10 и 11, блок 12 постоянной памяти, переключающие элементы 1 3 и 1 , сумматорывычитатели 15 и 16, блок 17 управления, входы 18-20, выходы 21 и 22 устройства, триггеры 23-25, одновибратор 26, генератор 27 прямоугольных импульсов, элементы И 28-30, счетчики 31 и 32, счетчик 33 тактов, счетчик З циклов, дешифраторы 35 и 36, элемент 37 задержки, элементы ИЛИ 38 и 39, вход блока управления и выходы ii1- 5.

Принцип функционирования устройства основан на реализации выражений

x x-cosoi -у sinot.

sinoi . (1 )

с использованием постоянного запоминающего устройства (ПЗУ), имеющего следующую логическую схему работы

С oLj 0 С -sin d-j.

где i-я масть кодов (ли N при условии их представления в виде суммы

X ..+Х.+ ...+ Хр, У У2+...+У,+ . .. +УРoLj -J-часть кода угла N, причем код угла также представлен в виде суммы ., ..+ .. . # -признак приформирования ( по совокупности величин С и oty определяющих адрес, записывают слово двойной разрядности, первые п разрядов которого определяют значение С{ cosbLj, а вторые п разрядов С

Р,М-количество частей (равных по разрядности),на которые разбиваются соответственно коды М,, Ми N.

Подставляя значения кодов в виде суммы в выражения (1 ), а также i1cnoльзуя логическую схему работы ПЗУ,приходят к рекурентным соотношениям,по i которым функционирует устройство.

Вывод рекурентных соотношений. П р и м е р. Р 3, М 2.

Исходные данные записываются в виде

X Х2+ У У2+Уз5

Подставляя координаты в виде cyMMj а угол только первой части о, получают

X(,sin rf)-. (.,(Tt co3dL y 5 nd J,

x sin

jWS X si n otj+(, Sin et),

где результирующие координаты, полученные как результат поворота исходных координат X и У на

угол oL,

или

(x.cosot -v.sinoCJ,

3

5 (v.C05ot X.SiHOC). (1И)

С учётом основной задами сокращения объема памяти следует указать , что константы С cosot и C-jsinod, записанные в памяти, вычислены по существу только для диапазона измене- НИИ, старших частей кодов Н, или Ny. Поэтому при вводе в ПЗУ i-и масти кода Nj или Х ее абсолютная , величина автоматимески возрастает в 2 раз, где р п/р. Для компенсации этого увеличения считанные из ПЗУ константы должны уменьшаться во столько же раз. В связи с изложенным выражение (l.l) можно представить в общем виде ,-( ,.E:(ftx,2«-«,Kj -{i)P .|,, fc )p -ш , -{pj V VKJj - ), кг, где в квадратных показаны величины поступаю1чие на вход ПЗУ, а в фигурных - константы, считанные из ПЗУ. fk nyчeнныe вьфаження отражают ал горитм повсфота вектора с координат X и У на угол «|Ц, определяягфи этом координаты )rii У повернут го вектора. Но так как оС то необходи МО ве кт ор с координ ат ами У повернуть еще на угол что осуществляется с использованием выражений (1.2). Используя результаты примера, пр водят рекурентные выражения, в соот ветствйи с которыми функционирует устройство .2 ta-f ; .|(i.)p, / -{i-UP ,,(2.. ; |(,lot, (zr ,2,...P, ,2...M. Анализ алгоритма (2) показывает что содержимое круглых скобок опред ляет действия, необходимее для выполнения такта, состоящего из двух полутактов, результаты которых алгебраически суммируются. В течение i-ro. такта обрабатываются 1-е част Х и У; кодов координат, причем во время первого полутакта Х| , а во время второго - У|. Очевидно, что полная обработка координат осуществляется заР тактов, определяющих один цикл., В результате выполнения j-ro цикла вектор с координатами У иповорачивается на угол оС, 5 а полученные Х yO toBместно с углом + являются исходными данными следующего цикла и т.д. Полное преобразование завершается за M циклов, в течение которых осуществл яется последовательный поворот вектора на углы еИ.сСу, ot. Устройство работает следующим образом. В начальный момент координаты X , У и угол ot по входам 18-20 зано- . сятся в регистры 1-3 соответственно. Знаковые разряды регистров 1 и 2 поступают на вход коммутатора 6, а выходы значащих разрядов поступают на входы мультиплексоров j и 5 которые под управлением блока 17 пропускают на вход коммутатора 7 только первые части кодов Х° и У, т.е. первые Р разрядов кодов Х°и У°. Коммутаторы 6 и 7 устанавливаются блоком 17 управления в положения, соответствующие первому полутакту, при котором на вход дешифратора 8 поступают знаковый разряд и первая часть кода. Одновременно управляющий сигнал с блока 17 управления разрешает дешифрацию первой части оС. кода угла oL с использованием первого из деши(чэаторов группы дешифраторов 9. В результате совместной работы указанных дешифраторов из блока 12 постоянной памяти считываются константы Xjp созЫ-И Х sinoL, которые через сдайгатели 10 и 11, управляемые синхронно .с мультиплексорами и 5, и через переключающие элементы 13 и Н, управляемые синхронно с коммутаторами 6 и 7, поступают в сумматоры-вычитатели 15 и 16. При выполнении второго полутакта коммутаторы 6 и 7 и элементы 13 и k переключаются, и теперь на входы дешифратор.а 8 поступают знаковый разряд и старшая часть У L кода Считанньй из блока 12 постоянной памяти константы 0 и Y°sin dL через сдвигатели 10 и 11, элементы i 3 и 1 поступают на входы сумматоров-вычитателей 15 и 16,- где сумкмруются с результатами первого полутакта в соответствии с выражением (2). Для правильной реализации этого выражения элементы 13 и 14 в первом полутакте осуществляют передачу по прямым связям в сумматоры-вычитатели 15 и 16, устанавливаемые в режим суммирования, а во втором полутакте по перекрестным связям, причем сумпереводится в ре мат op-вычит ател ь жим вычитания.На этом nepBMti такт вычислительного процесса завершается. Второй такт начинается при переключении мультиплексоров J.S и сдвига телей 10 11 во вторые положения, при этом мультиплексоры и 5 подключают к входам коммутатора 7 втол rt И У л кодов координат рые части уО .. „о X и У°, а сдвигатели 10 и 11 в этом положении осуществляют сдвиг на Р разрядов вправо, т.е. уменьшают считанные константы в раз. Коммутаторы 6,7 и элементы Ufl устанавливаются в положение, соответствующее первому полутакту. Дальнейший процес выполнения второго такта аналогичен предудыщему. После завершения Р-го такта закан чивается первый цикл вычислений, в результате которого в сумматорах-вычитателях 15 и 16 будут сформированы в соответствии с выражением (2) величины У |отражающие значение координат вектора, повернутого на УГОЛ of. Для дальнейшего прео азования содержимое сумматоров-вычитателей 15 и 16 пересылается в регистры 1 и 2 соответственно а блок 17 управления включает теперь второй дешифратор из группы дешифраторов 9,т.е. во втором цикле будет осу ществляться поворот вектора на уголс Через М циклов процесс преобразования заканчивается , содержимое сумматоров-выч т.ателей 15 и 1б равно и .Эти значения передаются на выходы 21 и 22. Блок управления, осуществляющий координацию действий устройства, работает следующим образом. Первоначально исходные данные зан сятся в регистры 1-3. Вычислительный процесс начинается с подачи пускового импульса на вход 0 блока 17 управления, в результате чего три гер 23 устанавливается в единичное состояние, которое разрешает работу элемента И 28. Перепад из О в 1 триггера 23 запускает одновибратор 2 генерирующий одиночный импульс,который устанавливает триггеры 24 и 2$ в единичные состояния, первый из которых по выходу 41 устанавливает коммутаторы 6,7 и переключающие элементы 13,14 в положения, соответствующие выполнению первого полутакта, а второй - по выходу 42 переводит сумматоры-вычитатели 15 и 16 в «i режим суммирования. Импульс с одновибратора 2б также сбрасывает счетчик З циклов, а через элемент ИЛИ 39 счетчик 33 тактов. Нулевые значения счетчиков 33 и З преобразуются дешифраторами 35 и Зб.Сигнал на первом выходе дешифратора 35, снимаемый с выхода 43, устанавливает мультиплексоры i,5 и сдвигатели 10, 11 в первые положения, соответствующие первому такту вычислений. Сигнал на первом выходе дешифратора 36, снимаемый с выхода kS, разрешает дешифрацию первой части кода угла, т.е. разрешает работу первого дешифратора из группы дешифраторов 9. Импульсы с генератора 27 через разрешенный сигналом - с триггера 23 и отсутствием сигнала на {Р+1 )-м выходе дешифратора 35, элемент И 28 поступают на счетчик 31, коэффициент пересчета которого определяется временем, необходимым для выполнения одного полутакта. После выполнения первого полутакта на выходе счетчика 31 появляется импульс, который, поступая на счетные входы триггеров 2Ц и 25, опрокидывает их, а они в свою очередь переводят коммутаторы 6 и 7, элементы 13 и 14 и сумматорывычитатели 15 и 16 в положения, соответствующие второму полутакту. Одновременно импульс с выхода счетчика 31 поступает на вход счетчика 32, коэффициент которого равен 2, т.е. двум импульсам на входе соответствует один на выходе. Тогда после ; второго полутакта на выходе счетчика 32 появится импульс, увеличивающий счетчик 33 тактов на единицу. Новое значение счетчика 33 тактов преобразуется дешифратором 35 в сигнал на его втором выходе, устанавливающии мультиплексоры 4,5 и сдвигателями 10,11 во вторые положения. После выполнения Р-го такта на последнем (Р+1 )-м выходе дешифратора 35 появляется сигнал, который, во-первых, запрещает прохождение импульсов с генератора 27 через элемент И 28, а, во-вторых, через разрешенный отсутствием сигнала на (М+1 )-м выходе дешифратора Зб элемент И 29 поступает с выхода 44 на регистры 1 и 2, осуществляя запись в них содержимого сумматоров-вычитателей 15 и 16 соответственно. Далее сигнал с выхода

11

элемента 29 И через элемент 37 за,)ержки, необходимый для задержки сигнала на время полного заверше- ния перезаписи содержимого сумматоров -вычитателей 15 и V6 в регистры 1 и 2, поступает на вход счетчика З циклов, увеличивая его содержимое на единицу, и через элемент ИЛИ сбрасывает сумматоры-шлчитатели и счетчик 33 тактов. Новое значение счетчика 3 циклов преобразуется дешифратором 36 в сигнал на втором его выходе, что разрешает работу второго дешифратора из группы дешифраторов 9, т.е. теперь в процессе преобразования участвует вторая часть кода узла. Сброс, счетчика 33 тактов снимает .сигнал с(Р+1 )-го: выхода дешифратора 35, а это в свою очередь снима18 je «je 019 5 2 .

ет запрет с элемента И 28, и импульсы с генератора 27 поступают на счетчик 31 и т.д. Второй цикл протекает аналогично первому. 5 После окончания Р-го такта Н-го цикла сигнал с (Р+1)-го выхода дешифратора 35, г оходя через элемент И 30, разрешенный сигналом на (М+1 )-ом выходе дешифратора 36j, to сбрасывает триггер i23, зап|5ёщая дальнейший процесс преобразования. Содержимое сумматоров-вычитателей 15 и 16 определяет искомые координаты .

15

Расчеты показывают, что предлагаемое устройство при одинаковых характеристиках с известным устройством требует примерно в 2 раза меньший объем памяти.

Фаг.1

/

Фиг.2

/ 3

к 1,2

к ,5Л11

Авторы

Даты

1983-05-23—Публикация

1982-01-11—Подача