мирования.начальных значений операндов соединены с- шиной нулевого значения устройства, шина единичного . значения 1 оторого соединена с первым группами информационных входов сумматоров первой строки, первого..и второго вычитателей, вторые группы информационных входов сумматоров первой строки, первого и второго вычитателей, первого и второго узлов формирования начальных значений операндов соединены с шиной нулевого значения устройства, информационные входы первых сумматоров первой, второй и третьей строк соединены с шиной единичного значения устройства, с выходами первого, второго и третьего элементов НЕ соответственно первого, второго, и третьего узлов формирования начальных значений операндов и с выходом знакового разряда первого вычитателя, выход знакового разряда второго узла: формирования начальных значений операндов соединен с вторым входом первого элемента ИЛИ, первый и второй информационные входы первых сумматоров третьей и четвертой строк объединены и подключены к выходам элементов НЕ третьего узла формирования начальных значений операндов и шинам единичного и нулевого значений устройства, второй информационный вход первого сумматора второй строки соединен со сдвигом на разрядов с выходами элементов НЕ третьего узла формирования начальных значений операндов и шинами единичного и нулевого значений устройства, первый информационный вход первого сумматора второй строки соединен с, выходами элементов НЕ второго узла формирования начальных значений операндов и шинами единичного и нулевого значений устройства, выходы элементов НЕ второго узла формирования начальных значений; операндов и. шины единичного и нулевого значений устройства подключены со сдвигом на 2 разрядов к вторым информационным входам первого и второго сумматоров третьей и четвертой строк.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения в двоичной и двоично-десятичной системах счисления | 1990 |

|

SU1789980A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Устройство для сложения и вычитания | 1984 |

|

SU1193664A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Конвейерное устройство для одновременного выполнения арифметических операций над множеством чисел | 1977 |

|

SU922726A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕЙ НАРАБОТКИ НА ПОЛНЫЙ ОТКАЗ СТРУКТУРНО-СЛОЖНОЙ СИСТЕМЫ | 1992 |

|

RU2041493C1 |

| Устройство для деления | 1981 |

|

SU1051535A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

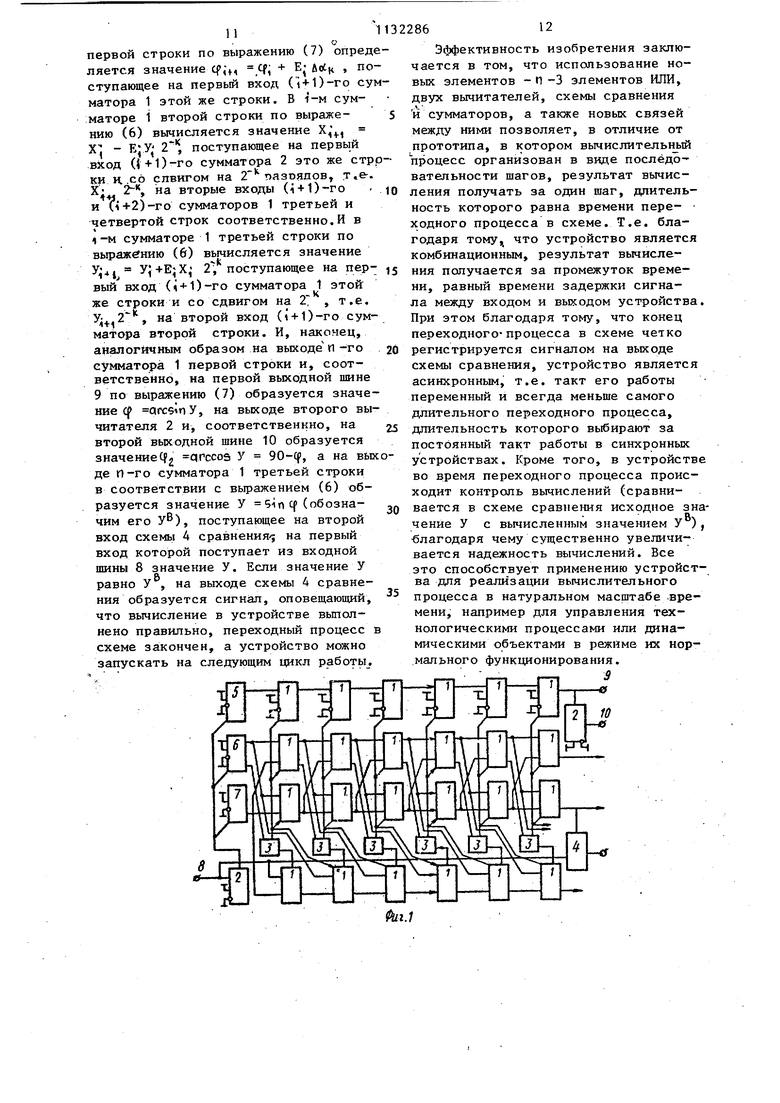

АСИНХРОННЫЙ МАТРИЧНЫЙ ВЫЧИСЛИТЕЛЬ ОБРАТНЫХ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ, содержащий первый, второй и третий элементы ИЛИ, первый и второй сумматоры, отличающийся тем, что, с целью увеличения быстродействия за счет сокращения последовательности шагов вычислений, в: гчислитель дополнительно содержит первый и второй вычитатели, -3 элементов ИЛИ, где и - разрядность устройства, узел сравнения значений операндов, первьш, второй и третий узлы формирования начальных значений операндов и 4h-2 сумматоров, причем сумматоры образуют матрицу из Р строк (где г 1,2,3 и 4) иЬ столбцов, информациоиньй выход 1-го ( i 1, 2, 3, ... .,h) сумматора Г-и строки соединен с первым входом (i + D-ro сумматора этой же строки, управляющие входы -го сумматора Р-и (Р 1,2,3) строки и (+1)-го сумматора четвертой строки объединены и подключены к выходу i-ro элемента ИЛИ, первый и второй иг ормационные входы которого подключены к выходам знаковых разрядов соответственно t -го и (i-l)-ro сумматоров соответственно четвертой и второй строк, первый информационный вход первого вычитателя соединен с .входной информационной шиной устройства, первым информащюнным входом первого сумматора четвертой строки и первым информационным входом-узла сравнения значений операндов, второй информационный вход которого подключен к выходу п -го сумматора третьей строки, информац11онный выход П-го сумматора первой строки соеди нен с первым выходом результата уст§ ройства и первым информационным входом второго бычитателя, выход котоW рого соединен с вторым выходом резуль т-ата устройства, вторые информационные входы («+1)-го и (i+2)-ro сумматоров соответственно третьей и четвертой строк соединены со сдвигом на 2 , к (J+2)/2 при i четном и к . (i+3)/2 при 1 нечетном, с информационным выходом i-ro сумматора второй строки, второй информационный вход

Изобретение относится к вычислительной технике и может быть применено в Качестве спецпроцессора или в комплексе с цифровой вычислительной машиной для оперативного вычисле

ния функций qrc 5in Ж иаг-ссой ж .

Известно устройство, содержащее два сумматора-вычитателя, блок памят блок управления, логический блок и блок возведения в квадрат,выход которого соединен с первым входом второго сумматора-вычитателя, соединенного своим выходом с первым входом блока возведения в квадрат и входом логического блока, подключенного сво им выходом к вторым входам первого и второго сумматоров-вычитателей l .

Недостатками известного устройства являются низкое быстродействие из-за последовательной организации вычислительного процесса, а также невысокая надежность вычислений, поскольку не организован контроль за результатом вычислений.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее генератор импульсов, делитель участка аппроксимации, дешифратор, счетчик участков аппроксимации, два шифратора, две группы элементов И,три элемента ИЛИ, два счетчика аргумента, два счетчика результата, два ключа,коммутатор и два сумматора, причем первые выходы коммутаторов подключены к первому и второму входампервого сумматора, вторые выходы коммутаторов соединены с первым и вторым входами второго сумматора, а выходы первого и второго сумматоров соединены соответственно с входами первого и второго счетчиков результата 2 .

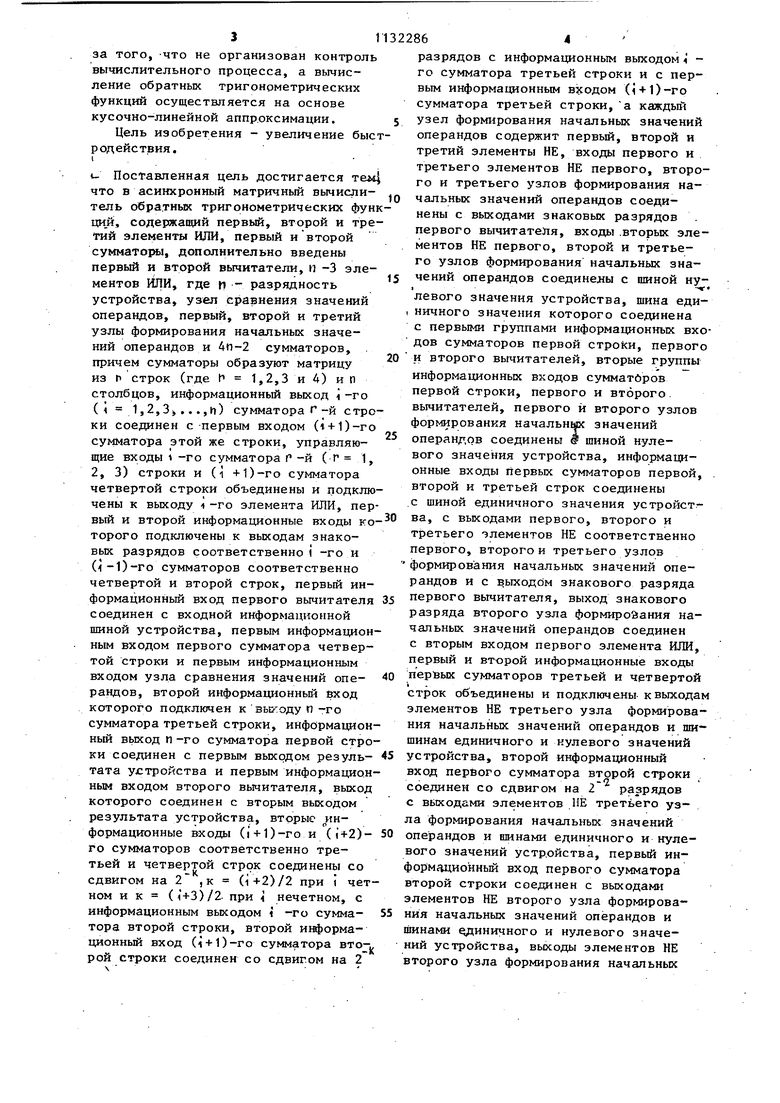

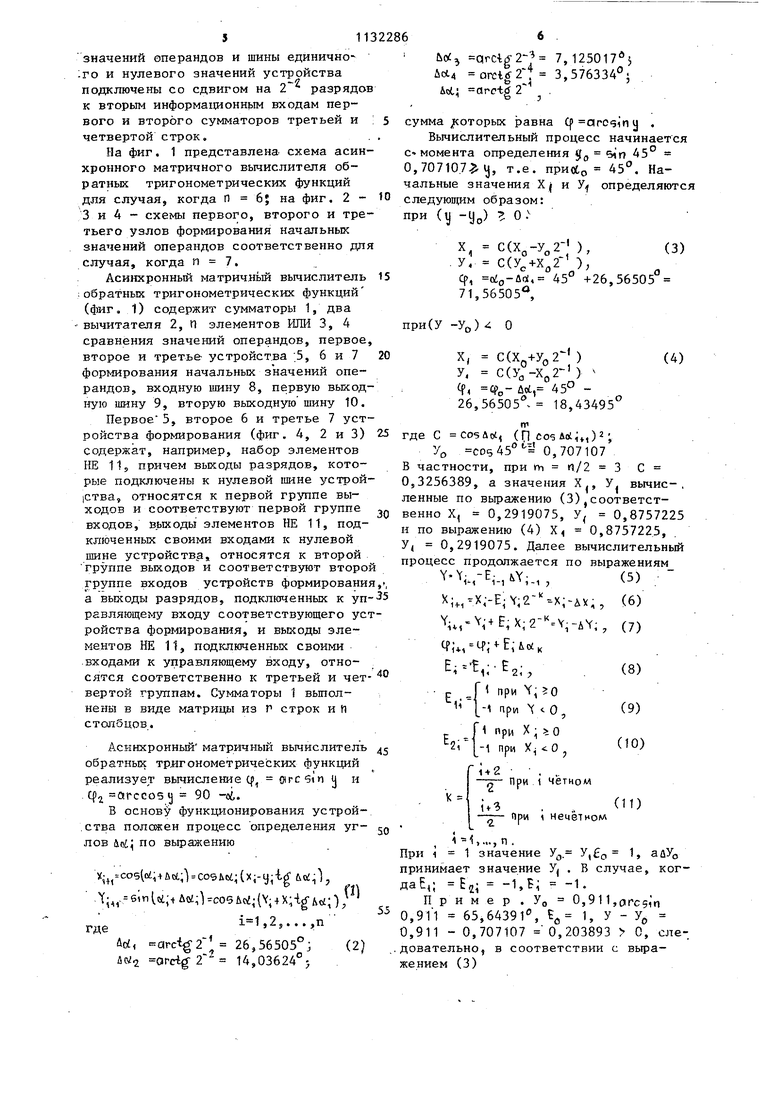

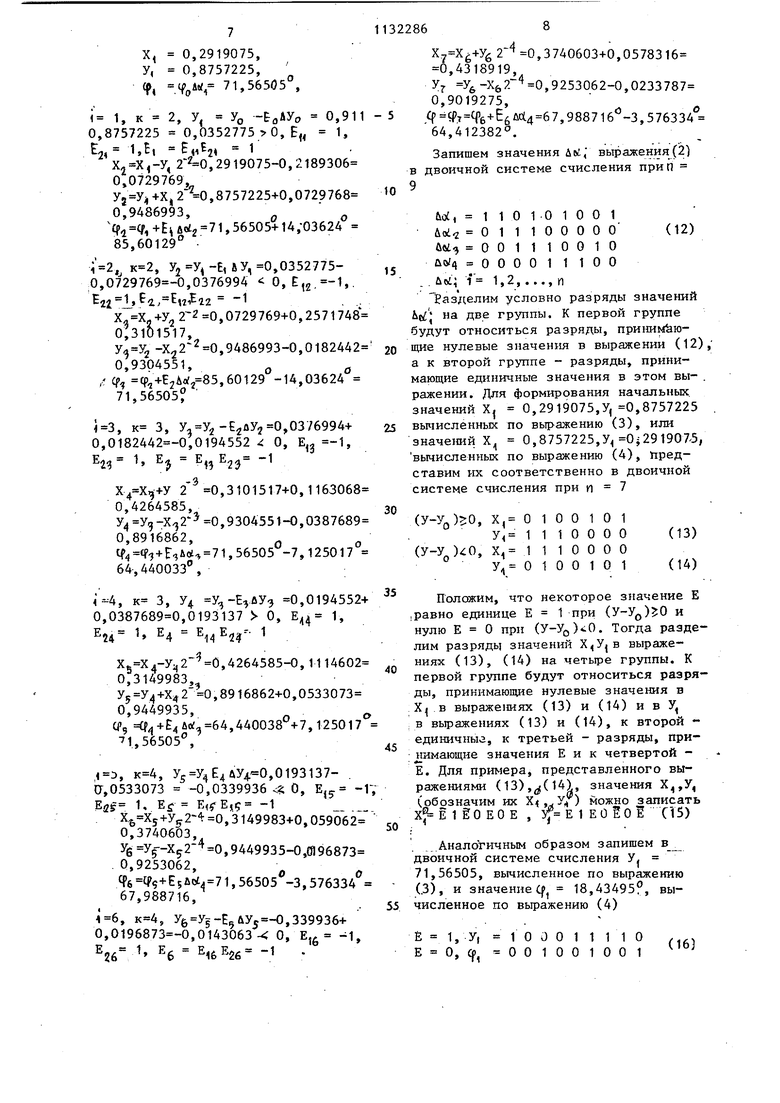

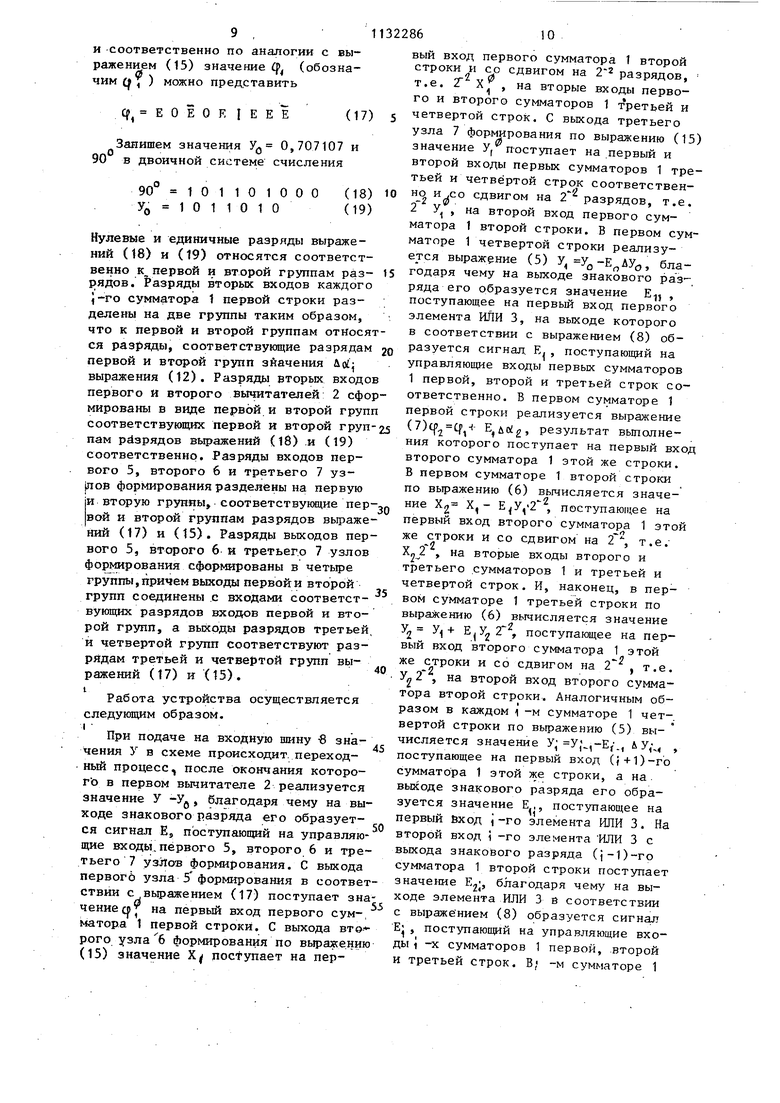

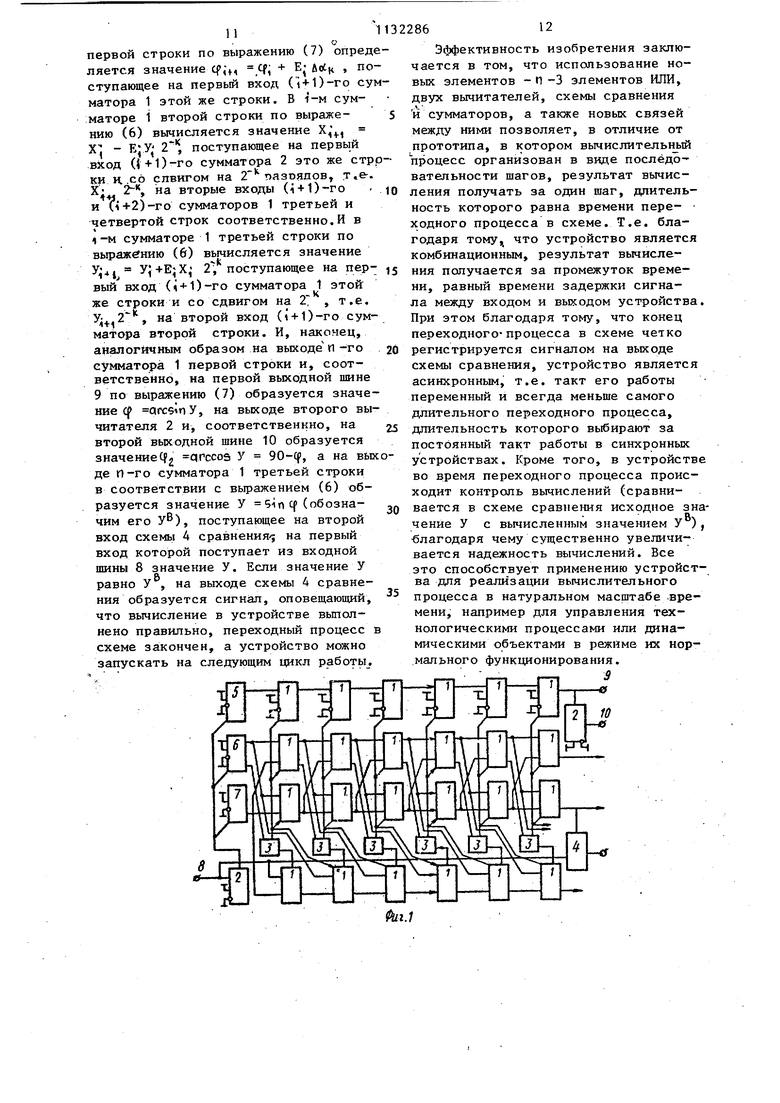

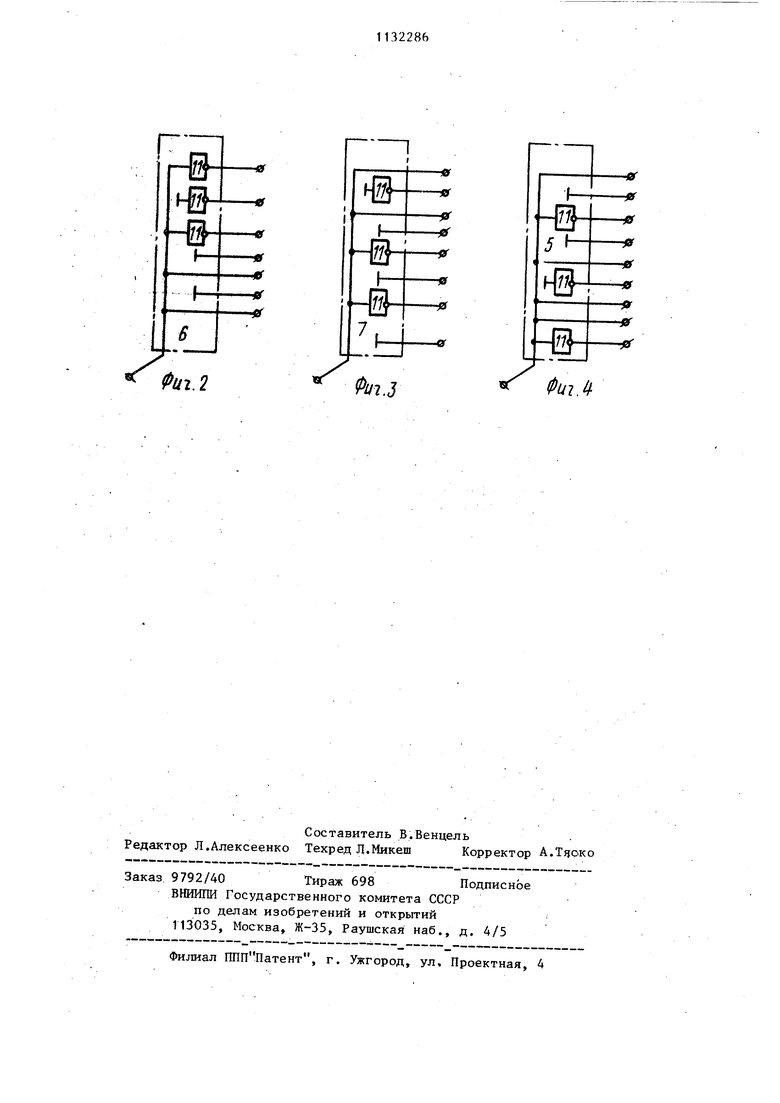

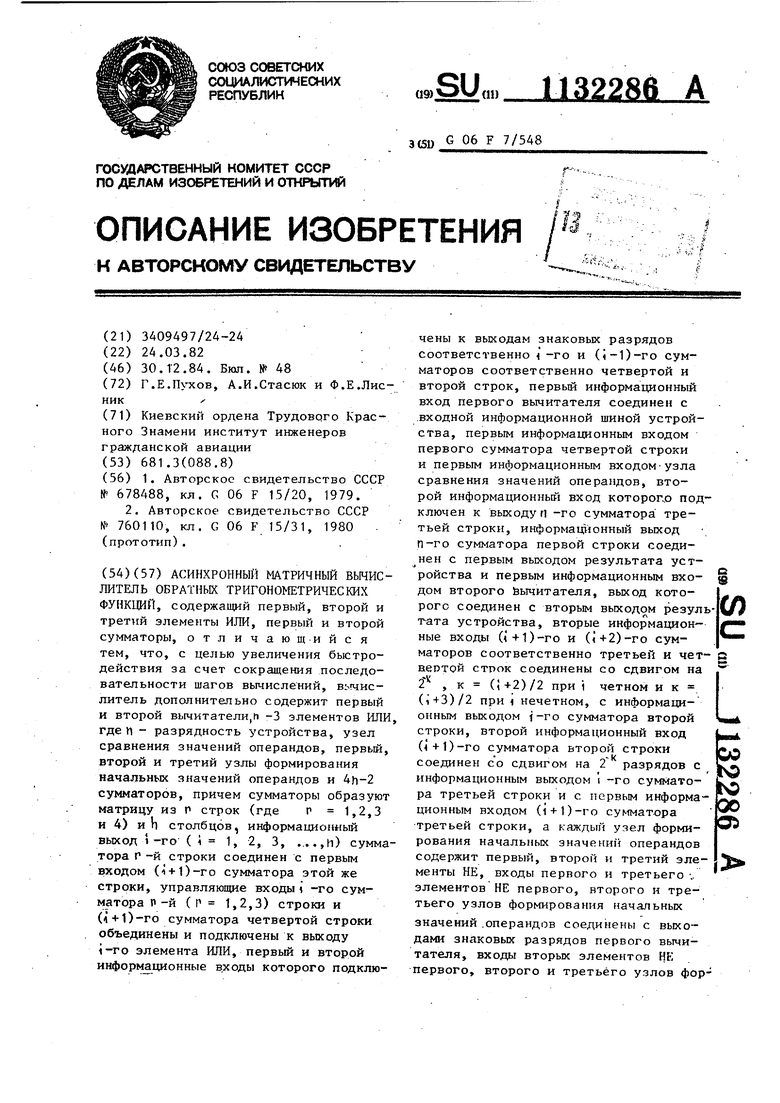

Недостатками известного устройства являются низкое быстродействие, определяемое тем, что вычислительный процесс организован в виде последователь ности шагов, а также относительно невысокая надежность и точность изза того, -что не организован контроль вычислительного процесса, а вычисление обратных тригонометрических функций осуществляется на основе кусочно-линейной аппроксимации. Цель изобретения - увеличение быс родействия. I t Поставленная цель достигается что в асинхронный матричный вычислитель обратных тригонометрических фун ци.й, содержащий первый, второй и тре тий элементы ИДИ, первый и второй сумматоры, дополнительно введены первый и второй вычитатели, п -3 элементов ИЛИ, где г - разрядность устройства, узел сравнения значений операндов, первый, второй и третий узлы формирования начальных значений операндов и 4п-2 сумматоров, причем сумматоры образуют матрицу из п строк (где h 1,2,3 и А) и п столбцов, информационный выход i-го ( i 1,2,3,, .. .,h) сумматора г-и стро ки соединен с-первым входом {i + 1)-ro сумматора этой же строки, управляющие входы 1 -го сумматора f-и ( Р 1, 2, 3) строки и (1 +1)-го сумматора четвертой строки объединены и подклю чены к выходу i-го элемента ИЛИ, пер вый и второй информационные входы ко торого подключены к выходам знаковых разрядов соответственно -го и (-i -1)-го сумматоров соответственно четвертой и второй строк, первый информационный вход первого вычитателя соединен с входной информационной шиной устройства, первым информацион ным входом первого сумматора четвертой строки и первым информационным входом узла сравнения значений операндов, второй информационньй вход которого подключен к вь&оду п -го сумматора третьей строки, информацион ный вькод п-го сумматора первой стро ки соединен с первым выходом результата yjcTpoHCTBa и первым информацион ным входом второго вьиитателя, выход которого соединен с вторым выходом результата устройства, вторые IHформацконные входы (i + 1)-ro и (|н-2)го сумматоров соответственно третьей и четвертой строк соединены со сдвигом на 2 )К (i+2)/2 при i чет ном и к (i+3)/2. при 1 нечетном, с информационным выходом i -го сумматора второй строки, второй информационный вход (i + 1)-ro сумматора BTOJ рой строки соединен со сдвигом на 2 разрядов с информационньм выходом го сумматора третьей строки и с первым информационным входом (i+1)-ro сумматора третьей строки,а каждый узел форм11рования начальных значений операндов содержит первый, второй и третий элементы НЕ, входы первого и третьего элементов НЕ первого, второго и третьего узлов формирования на- чальных значений операндов соединены с выходами знаковых разрядов первого вычитателя, входы .вторых элементов НЕ первого, второй и третьего узлов формирования начальных значений операндов соединены с шиной нулевого значения устройства, шина единичного значения которого соединена с первыми группами информационных входов сумматоров первой строки, первого и второго вычитателей, вторые группы информационных входов сумматбров первой строки, первого и второго вычитателей, первого и второго узлов формирования начальн значений операндов соединены шиной нулевого значения устройства, информационные входы первых сумматоров первой, . второй и третьей строк соединены с шиной единичного значения устройства, с выходами первого, второго и третьего элементов НЕ соответственно первого, второго и третьего узлов формирования начальных значений операндов и с выходом знакового разряда первого вычитателя, выход знакового разряда второго узла формиройания начальных значений операндов соединен с вторым входом первого элемента ИЛИ, первый и второй информационные входы первых сумматоров третьей и четвертой строк объединены и подключены- к выходам элементов НЕ третьего узла формирования начальных значений операндов и шишинам единичного и нулевого значений устройства, второй информационный вход первого сумматора второй строки соединен со сдвигом на 2 разрядов с выходами элементов ИВ третьего узла формирования начальных значений операндов и шинами единичного и нулевого значений устройства, первый информадионньш вход первого сумматора второй строки соединен с выходами элементов НЕ второго узла формироваНИН начальных значений операндов и шинами единичного и нулевого значений устройства, выходы элементов НЕ второго узла формирования начальных 51132286 значений операндов и шины единично 1го и нулевого значений устройства подключены со сдвигом на 2 разрядов к вторьм информациионньтм входам первого и второго сумматоров третьей и : 5 четвертой строк.. . На фиг. 1 представлена, схема асинхронного матричного вычислителя обратных тригонометрических функций для случая, когда П 6; на фиг. 2 - Ю 3 и А - схемы первого, второго и третьего узлов формирования начальных значений операндов соответственно для случая, когда п 7, Асинхронный матричньй вычислитель 15 ;обратньк тригонометрических функций (фиг, 1) содержит сумматоры 1, два - вычитателя 2, И элементов ИЛИ 3, 4 сравнения значений операндов, первое, второе и третье- устройства ;5, 6 и 7 20 формирования начальных значений операндов, входную шину 8, первую выходную шину 9, вторую выходную шину 10. Первое5, второе 6 и третье 7 устройства формирования (фиг, 4, 2 и 3) 25 содержат, например, набор элементов НЕ 11, причем выходы разрядов, которые подключены к нулевой шине устрой|ства, относятся к первой группе выходов и соответствуют первой группе входов, в.ыходы элементов НЕ 11, подключенных своими входами к нулевой шине устройства, относятся к второй группе выходов и соответствуют второй группе входов устройств формирования,-, а выходы разрядов, подключенных к уп-ЗЗ равляющему входу соответствующего устройства формирования, и выходы элементов НЕ 11, подключенных своими .входами к управляющему входу, относятся соответственно к третьей и четвертой группам. Сумматоры выполнены в виде матрицы из г строк и И столбцов. Асинхронный матричный вьиислитель дд обратных тригонометрических функций реализует вычисление qi, Ц и агссо5 90 -oi,. В основу функционирования устрой.ства полажен процесс определения углов &й по вьфансению + uo(,;l C05b6i;(x;-L)-ig Ьо:,., ;M- U;+i« ;bcoe -(V; + x;ig-&ciO 1- 1 ) jTl йЫ, -arcig2 26,56505 arcig- 2 14,03624 с с 0 ч с п пр гд В 0, ле ве и У пр Пр пр да 0, 0, .до же boi, Qrctg-2-2 7,125017 5 uct4 an:tg2: 3,576334°; Ы; arct| 2 а КОТОРЫХ равна Cj)arcgin4 ычислительный процесс начинается мента определения д eir 45° 7107 у, т.е. приоСр 45. Наные значения Xj и У определяются ующим образом: (V) -Уо) г ОX, С(Х„-У„2-; ), ); у, С(У,-ьХ,2Ср, oio-uof, 45 +26,56505 71,56505, У -УС,) -i О X, С(Х.,+У,, О О , у, С(У,-Хо2-) СРо- u(ir 45° 26,56505 . 18,43495 nn С С05Л( (Г соб Аы;,)2; 00545 0,707107 стности, при m п/2 3 С 56389, а значения X., У. вычис-, ые по выражению (3),соответсто X, 0,2919075, У 0,8757225 выражению (4) X, 0,8757225, 0,2919075. Далее вычислительный есс продолжается по выражениям Y-VrV Y;-., (5) -к .,Х,--ЕЧ;2---Х;-ЛУ,, ,,-AY;, Ср;,, Е- -f Е - -1, 2, : 1 при Y, о - при О, i При X О -1 при Х О ,, 1 + 2 . .. При 1 четном „ при нецетиом , ,..., л. 1 1 значение Уд. У,с1 U зйУо имает значение У| . В случае, ког; E2J -1,Bi -1. р и м е р . УО 0,911,с)1гс51П 1 65,64391 U У - УО 1 - 0,707107 0,203893 О, слетельно, в соответствии с выраем (3) X, 0,2919075, У, 0,8757225, (р, 71,56505°, i 1, к 2, У, УО -ЕоАУо 0,91 0,8757225 0,0352775 О, Е, 1, ЕЗ, 1,Е ЕиЧ 1 ,-У, ,2919075-0,2189306 0,0729769, ,+Х, 2 0,8757225+0,0729768 0,9486993, ,+E fiot2 71,56505+14;03624 85,60129° , , ,-Е, ay, 0,03527750,0729769 -0,0376994 О, Е,2,-1,. .2f-lZ 1, Х.Х2+У2 ,0729769+0,2571748 0,3101517, У У2-Х22 0,9486993-0,0182442 0,9304551, ,ср (р,+Е2Ао;г 5,60129 -14,03624 71,56505 , к 3, У У2-Е2ЛУ7 0,0376994+ 0,0182442 -0,0194552 О, Е, -1, 1 Е- - Е.. Е,1 ,+y 2 0,3101517+0,1163068 0,4264585, 0,9304551-0,0387689 0,8916862, % + ,56505 -7,125017° 64,440033, 4-4, к 3, У4 У, 0,0194552+ 0,0387689 0,0193137 О, 1, П 4 ,-У:, 2 0,4 264585-0, 1114602 0,3149983, У5 У4+Х42 0,8916862+0,0533073 0,9449935, О, а +Е4 «ч 6 И 0038°+7,125017 71,56505 , (:, , У5 У4Е4ЛУ 0,0193137СГ,0533073 -0,0339936 « О, E -Г 1, Е E,f Е,9 -1 ,3149983+0,059062 0,3740603, 0,9449935-0,0196873 0,9253062, Яб 5 uot.71,56505 -3,576334 67,988716, 6, , Уб У5-Е5йУ5 -0,339936+ 0,0196873 -0,0143063- О, Е, , %% 868 2 0.3740603+0,05783 16 0,4318919, 7 Уб-Хб2 0,9253062-0,0233787 0,9019275, .fp 47 %+E6UOt4 67,988716-3,576334 64,412382°. Запишем значения Дв, выражения (2 в двоичной системе счисления приП 9 w, 1 1 О 1 О 1 О О 1 uoi-z О 1 1 1 О О О О о(12) fiei.) О О 1 1 1 О О 1 О uofij 000011100 . . uei 1 1,2, . .., n ТРазделим условно разряды значений на две группы. К первой группе будут относиться разряды, принимйющие нулевые значения в выражении (12), а к второй группе - разряды, принимающие единичные значения в этом вы- . ражении. Для формирования начальных, значений Х 0,29 19075,У, 0,8757225 . вычисленных по выражению (3), или значений X, О,8757225,У 0 2919075, вычисленных по выражению (4), представим их соответственно в двоичной системе счисления при и 7 (У-Уо)50, Х, О 1 О О 1 О 1 У4 1 1 10000 (У-У ):0, Х 1 1 10000 у о 1 о о 1 о 1 Положим, что некоторое значение Е Iравно единице Е 1 при (У-Уд)0 и нулю Е О при (У-УО)О. Тогда разделим разрядь} значений Х, выражениях (13), (14) на четыре группы. К первой группе будут относиться разряды, принимающие нулевые значения в Х в выраже1шях (13) и (14) и в У, В выражениях (13) и (14), к второй единичные, к третьей - разряды, прииимающие значения Е и к четвертой Е. Для примера, представленного выражениями (13),(141, значения Х;,,У, (обозначим их Х , У., ) можно записать X ElgOEOE , Е 1 EOSO Е СТ5) .Аналогичным образом запишем в двоичной системе счисления У. 71,56505, вычисленное по выражению (3), и значение Cf, 18,43495, вычисленное по выражению (4) Ё 1, .у, 100011110 Е О, ср, 001001001 и -соответственно по аналогии с выражением (15) значение (обозначим Q I ) можно представить cf, EOEOK IEEE Занишем значения У 0,707107 и в двоичной системе счисления 101 101000 (18) 1011010 (19) Нулевые и единичные разряды выражений (18) и (19) относятся соответственно к первой и второй группам разрядов. 1азряды вторых входов каждого J-го сумматора 1 первой строки разделены на две группы таким образом, что к первой и второй группам относя ся разряды, соответствующие разрядам первой и второй групп зйачения &otвыражения (12). Разряды вторых входо первого Я второго вычитателей 2 сфо мированы в виде первой и второй груп соответствующих первой и второй груп ПаМ OdaDBnnn ПГ,1Г ЯТ1Г|3 НИИ 1ЙЧ м пам рёзрядов выражений (18) и (19) соответственно. Разряды входов первого 5, второго 6 и третьего 7 формирования разделены на первую и вторую груняы, соответствующие пер вой и второй группам разрядов вьфаже ний (17) и (15). Разряды выходов пер вого 5, второго 6 и третьего 7 узлов фop Iиpoвaния сформированы в четыре группы,причем выходы первойи второй групп соединены .с входами соответствующих разрядов входов первой и второй групп, а выходы разрядов третьей и четвертой групп соответствуют разрйдам третьей и четвертой групп выражений (17) и (15). Работа устройства осуществляется следующим образом. При подаче на входную шину -8 значения У в схеме происходит, переходный процесс, после окончания которого в первом вычитателе 2 реализуется значение У 0 благодаря чему на выходе знакового разряда его образуется сигнал Е, поступающий на управляющие входы.первого 5, второго 6 и третьего 7 узЛов формирования. С выхода первогб узла 5формирования в соответ ствии с вьфажением (17) поступает зна чение cpj на первый вход первого сум-. матора 1 первой строки. С выхода второго узла 6 формирования по выражению (15) значение Х jioctynaeT на пер(17) 286 вый вход первого сумматора 1 второй строки и со сдвигом на 2 разрядов, т.е. 2 X , на вторые входы первого и второго сумматоров 1 третьей и четвертой строк. С выхода третьего узла 7 формирования по выражению (15) значение У,%оступает на .первыГи „„ ,, (9 второй входы первых сумматоров 1 тре., 1 liJCРТ,1МТ т1-л™, f тьей и четвёртой строк соответственн сдвигом на 2 разрядов, но и ,со сдвигом на 2 У , на второй вход первого сумматора 1 второй строки. В первом сумматоре 1 четвертой строки реализуется выражение (5) У,, благодаря чему на выходе знакового раз ряда его образуется значение , поступающее на первый вход первого элемента ИЛИ 3, на выходе которого в соответствии с выражением (8) образуется сигнал Е., поступающий на управляющие входы первых сумматоров 1 первой, второй и третьей строк соответственно. В первом сумматоре 1 первой строки реализуется выражение --г-. . , реализуется выражени f-i,, -,. . (7)(f,,H , результат вьтолне ния которого поступает на первый вход Ичсг т/-,, второго сумматора 1 этой же строки, В первом сумматоре 1 второй строки по выражению (6) вычисляется значе- -- -ние X, , поступающее на первый вход второго сумматора 1 этой же строки и со сдвигом на 2 , т.е. Х„2 , на вторые входы второго и третьего сумматоров 1 и третьей и четвертой строк. И, наконец, в первом сумматоре 1 третьей строки по выражению (6) вычисляется значение ,. ,. - , поступающее на первый вход второго сумматора 1 этой е строки и со сдвигом на 2 , т.е. в. У„2 . на второй вход второго сумма. ,-, J -,. v v,ji-ji-ia. тора второй строки. Аналогичным обазом в каждом 1 -м сумматоре 1 четертой строки по выражению (3) выисляется значение У; У,-Е,., Л У, - - 1 - 14 J-1 оступающее на первый вход (;+1)-гЬ умматора 1 этой же строки, а на. ыходе знакового разряда его обрауется значение Е,,, поступающее на ервый вход i-го элемента ИЛИ 3. На торой вход 1 -го элемента ИЛИ 3 с ыхода знакового разряда (|-1)-го умматора 1 второй строки поступает начение , благодаря чему на выоде элемента ИЛИ 3 в соответствии выражением (8) образуется сигнал - , поступающий на управляющие вхоы i -X сумматоров 1 первой, второй третьей строк. В; -м сумматоре 1 первой строки по выражению (7) опред ляется значение q,-H Cf; + Ej , п ступающее на первый вход (i + D-ro су матора 1 этой же строки. В i-м сумматоре i второй строки по выражекию (6) вычисляется значение Х,, XI - Е:У i поступающее на первый вход (1+1)-го сумматора 2 это же ст ки и. .со слвигом на 2 пазояпов, т.& Х 2-% на вторые входы (4 + 1)-го и и+2)-го сумматоров 1 третьей и четвертой строк соответственно.И в 1-м сумматоре 1 третьей строки по выражению (6) вычисляется значение yi+EjX,- 2, поступающее на пер вый вход (-|-1)-го сумматора 1 этой же строки и со сдвигом на Т, , т.е. У 2, на второй вход {i + 1)-ro сум матора второй строки. И, наконец, аналогичным образом на выходеи-го сумматора 1 первой строки и, соответственно, на первой выходной шине 9 по выражению (7) образуется значе ние cj агс51пУ, на выходе второго вы читателя 2 и, соответственкно, на второй выходной шине 10 образуется значение 2 С(Гссо У , а на вы де П-го сумматора 1 третьей строки в соответствии с выражением (6) образуется значение У 5in cf (обозначим его У°), поступающее на второй вход схемы 4 сравнения-; на первый вход которой поступает из входной шины 8 значение У. Если значение У равно У , на выходе схемы 4 сравнения образуется сигнал, оповещающий, что вычисление в устройстве вьтолнено правильно, переходный процесс схеме закончен, а устройство можно запускать на следующим цикл работы. Эффективность изобретения заключается в том, что использование новых элементов -П -3 элементов ИЛИ, двух вьиитателей, схемы сравнения и сумматоров, а также новых связей между ними позволяет, в отличие от прототипа, в котором вычислительньй процесс организован в виде последовательности шагов, результат вычисления получать за один шаг, длительность которого равна времени переходного процесса в схеме. Т.е. благодаря тому что устройство является комбинационным, результат вычисления получается за промежуток времени, равный времени задержки сигнала между входом и выходом устройства. При этом благодаря тому, что конец переходного-процесса в схеме четко регистрируется сигналом на выходе схемы сравнения, устройство является асинхронным, т.е. такт его работы переменный и всегда меньше самого длительного переходного процесса, длительность которого выбирают за постоянный такт работы в синхронных устройствах. Кроме того, в устройстве во время переходного процесса происходит контроль вычислений (сравнивается в схеме сравнения исходное значение У с вычисленным значением У ), -благодаря чему существенно увеличивается надежность вычислений. Все это способствует применению устройства для реализации вычислительного процесса в натуральном масштабе .времени, например для управления технологическими процессами или динамическими объектами в режиме их нормального функционирования.

li/

Фи1.2

5 isT Z).

Фи1.3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU678488A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 760110, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-30—Публикация

1982-03-24—Подача