11

Изобретение относится к устройствам автоматики, измерительной и вычислительной технике и может быть использовано для коммутации и одновре- мемной выборки и хранения дискретных значений изменяющихся во времени напряжений, формируемых множеством измерительных объектов,

Цель изобретения - расширение функ циональных возможностей устройства путем обеспечения многоканальности при сохранении высокого быстродействия.

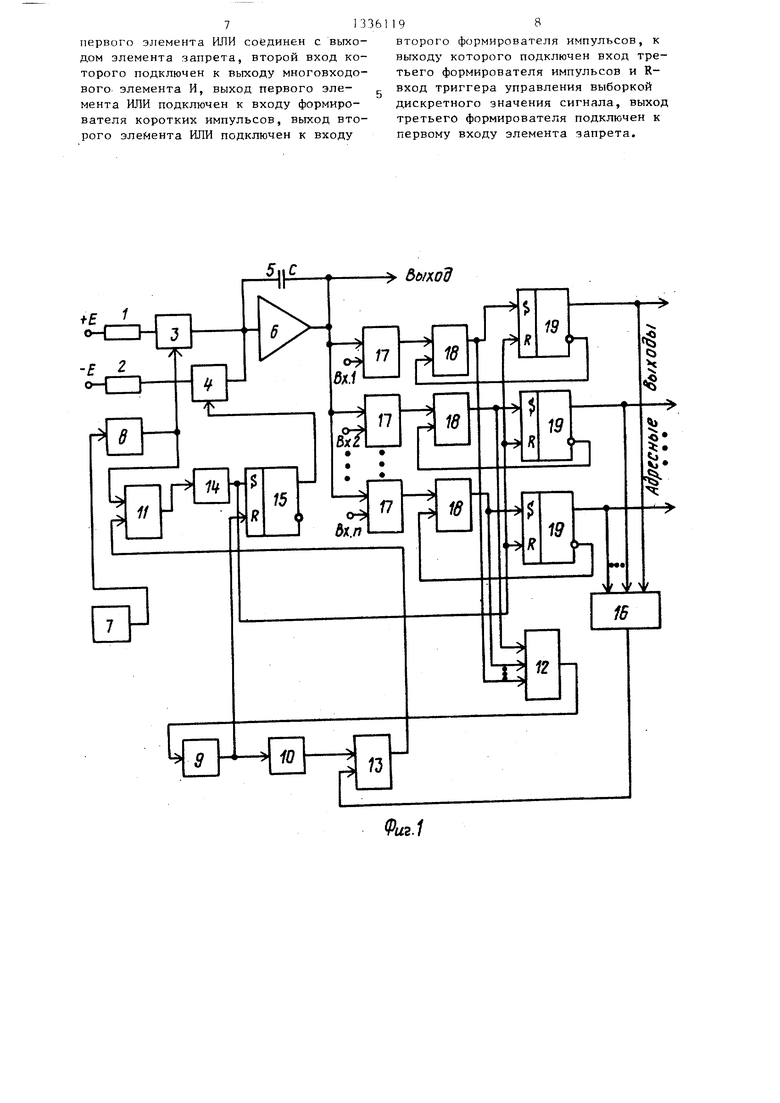

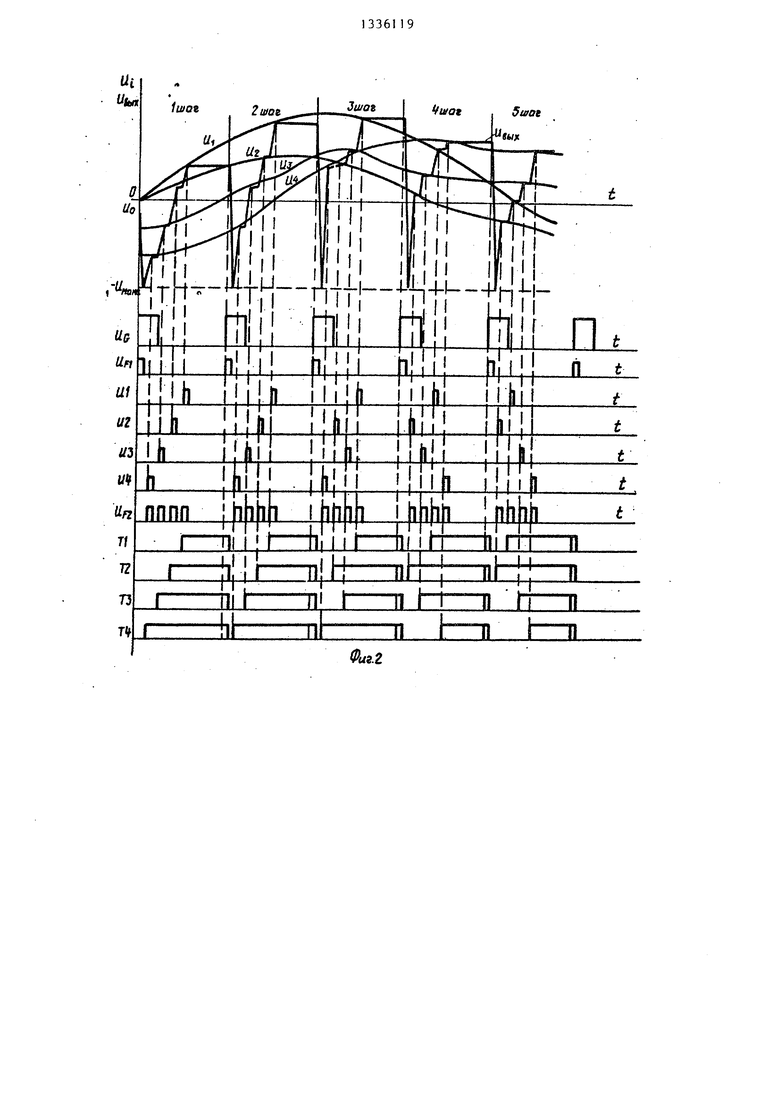

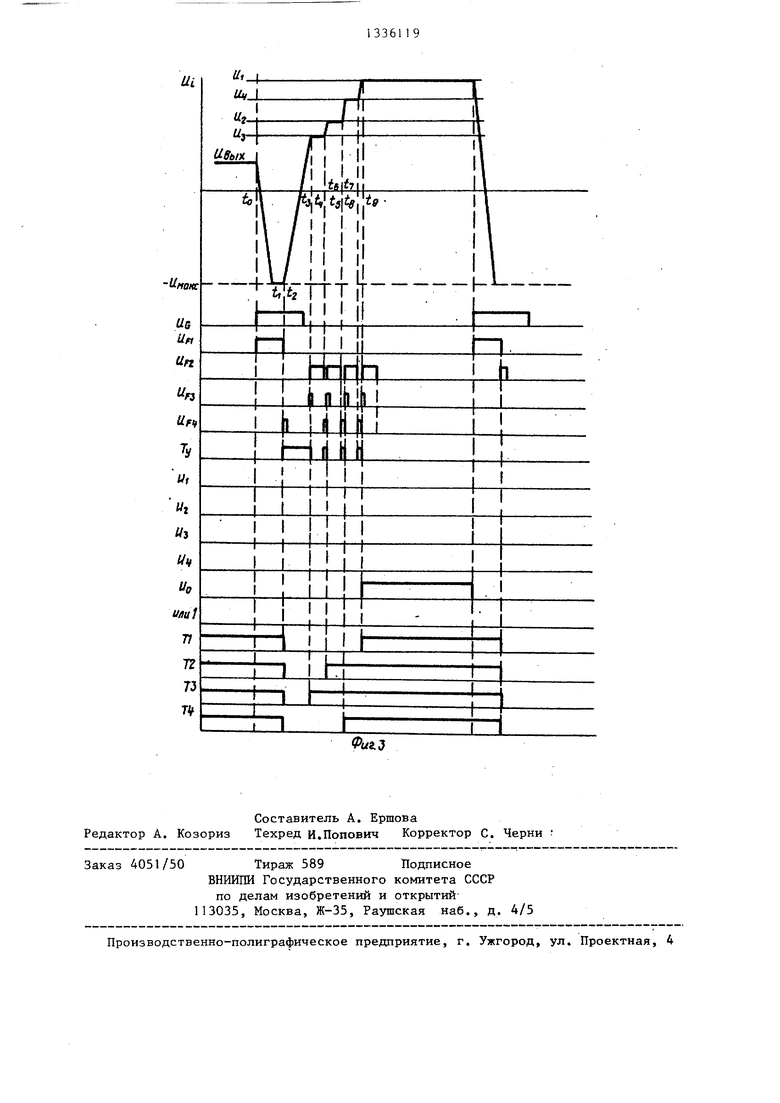

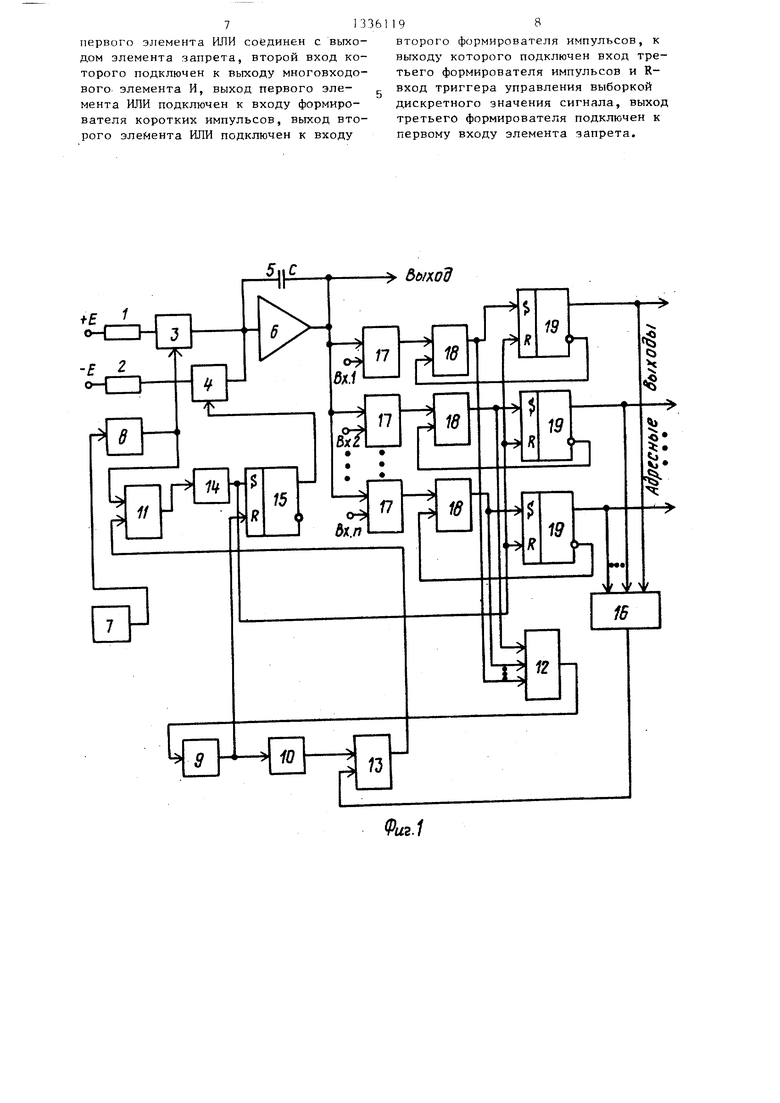

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временные диаграммы для случая четырехка- нального устройства в пределах нескольких шагов дискретизации;- на фиг. 3 - временная диаграмма в преде- лах одного шага дискретизации.

Устройство содержит мяг.ттабные резисторы 1 и 2, первый 3 и второй 4 аналоговые ключи, запоминающий конденсатор 5, операционный усилитель 6, генератор 7 импульсов, первый 8, второй 9 и третий 10 формирователи импульсов, первый 11 и второй 12 эле- м енты ИЛИ, элемент 13 запрета, формирователь 14 короткого импульса, триг- гер 15 управления выборкой дискретного значения сигнала, многовходовый элемент И 16, компаратор 17, элемент И 18, RS-триггер 19.

Устройство работает следующим об-

разом.

При поступлении в момент времени tjj импульса с генератора 7 импульсов по переднему фронту запускается первый формирователь 8 импульсов, кото- рый вырабатьлвает импульс, поступающий на вход аналогового ключа 3, который открьгоаясь, обеспечивает разряд запоминающего конденсатора 5. Длительность этого импульса должна быть та- кой, чтобы завершился перезаряд конденсатора 5 от положительного значения до отрицательного значения макс Таким образом устройство приводится в исходное состояние.- На фиг. 3 перезаряд конденсатора 5 заканчивается в момент времени t и исходное состояние длится до момента времени tj. Длительность импульса С tj - tTp первого формирователя 8 можно определить по формуле

/ iX ч 4.Ч ИЛИ

Е / 2U „„,,. С 2U,eRC/E.

0

5 о

Ь

о

5

192

В момент времени tj закрывается ключ 3, по заднему фронту импульса с формирователя 8 через первый элемент ИЛИ 11 запускается формирователь 14 короткого импульса, длительность которого должна быть достаточна для установки триггера 15 управления в единичное состояние и всех RS-триггеров 19 в нулевое состояние. Триггер 15 управления выборкой дискретного значения сигнала, установившись в единичное состояние практически с момента времени tj, открывает ключ 4 и начинается заряд конденсатора в положительную сторону относительно исходного значения -Uj,c,цc по линейному закону (фиг. 3, Ug,, ) в интервале t - tj . В момент времени tj Ug, onepa-ir ционного усилителя 6 до.стигает значения наименьшего из всех канальных напряжений (на фиг. 3 это напряжение и„ третьего канала) и срабатывает компаратор 17 третьего канала, на выходе которого появляется -уровень логической единицы. Так как на обоих

входах элемента И 18 третьего канала присутствуют сигналы логической единицы то на его выходе формируется сигнал, под действием которого RS- триггер 19 третьего канала установится в единичное состояние (практически с момента времени t,) до окончания цикла. При этом на второй вход элемента И 18 инверсного выхода RS-триг- гера третьего канала поступает логический нуль и этот элемент закрывается до очередного шага дискретизации. В результате этого на выходе этого элемента И 18 формируется всего один короткий импульс в момент равенства напряжений на входах компаратора 17 третьего канала. Сформированный на выходе элемента И 18 короткий импульс через второй элемент ИЛИ 12 запускает второй формирователь 9 импульса, вырабатывающий импульс, длительность которого должна быть достаточной для сброса Триггера 15 управления выборкой дискретного значения сигнала в исходное состояние. При этом закрывается аналоговый ключ 4 и прекращается заряд запоминающего конденсатора, что.свидетельствует об окончании процесса выборки дискретного значения сигнала по третьему каналу.

Под действием сигнала с выхода второго формирователя 9 импульсов

31

третий формирователь 10 импульсов вырабатывает импульс, длительность которого равна необходимому времени хранения выбранного дискретного зна- чения, в течение которого производится его обработка, к примеру аналого- цифровое преобразование или другие операции. Этот импульс через открытый элемент 13 запрета (на второй вход элемента с выхода многовходов.о- го элемента И 16 поступает логический нуль) и через первый элемент ИЛИ поступает на вход формирователя 14 короткого импульса. По заднему фронту импульса третьего формирователя 10, в момент времени t, формирователь 14 генерирует короткий импульс, устанавливающий триггер 15 в единич- ное состояние. При этом открывается ключ 4 и продолжается заряд конденсатора 5 в интервале по линей- ному закону через резистор 2 от источника напряжения -Е,

Б момент времени t , когда операционного усилителя 6 достигает значения наименьшего из оставшихся канальных напряжений (на фиг. 3 это напряжение U,;), срабатывает компаратор 17 второго канала. Элемент И 18 второго канала формирует перепад напряжения, под действием которого устанавливается в единичное состояние RS-триггер 19 второго канала, закрывающий элемент И 18. Короткий импульс с выхода элемента И 18 через второй элемент ИЛИ 12 запускает второй формирователь 9 импульсов и триггер сбрасьгеается в нулевое состояние При этом закрывается ключ 4 и прекращается заряд конденсатора 5, что свидетельствует об окончании процесса выборки дискретного значения второго канала. В интервале времени t третий формирователь 10 импульсов снова формирует импульс, длительност которого равна, как и на интервале tj-t,,, необходимому времени хранения в течение которого производится обработка этого дискретного значения. Б

момент времени tg по заднему фронту импульса, сформированного третьим формирователем 10 и прошедшего через открытый элемент 13 запрета и первый элемент ИЛИ 11, формирователь 14 вырабатывает импульс, который снова устанавливает триггер 15 в единичное Состояние. Снова при этом открывается аналоговый ключ 4 и на интервале t,

5

0

5

0

5

0

45

50

55

19 .

t производится заряд конденсатора 5 через резистор 2 от источника напряжения -Е. Б момент времени t, когда напряжение на выходе операционного усилителя 6 достигает значения наименьшего из оставшихся канальных напряжений (на фиг. 3 это напряжение 1)4), срабатывает компаратор 17 четвертого канала. Элемент И 18 четвертого канала формирует аналогичным образом импульс, устанавливающий в единичное состояние RS-триггер 19 и четвертого канала, закрывающий этот элемент И. Короткий импульс с выхода элемента И 18 четвертого канала через второй элемент 1ШИ 12 запускают в очередной раз первый формирователь

9импульсов и триггер 15 сбрасывается в нулевое состояние. Ключ 4 закрьг- вается и завершается заряд конденсатора 5, что свидетельствует об окончании очерёдного процесса выборки дискретного значения четвертого канала. На интервале t,-t,. формироваI о

тель 10 снова формирует импульс, длительность которого -соответствует необходимому времени хранения. Б момент времени t по заднему фронту импульса, поступившего с формирователя

10через открытьй элемент 13 запрета и первый элемент ИЛИ 11, формирователь 14 вырабатывает импульс, который устанавливает триггер 15 в единичное состояние на этом шаге дискретизации в последний раз. Открывается ключ 4 и на интервале tg-tg снова производится заряд конденсатора 5 от источника напряжения -Е. В момент времени tj, когда напряжение на выходе операционного усилителя 6 достигает значения последнего из оставшихся канальных напряжений (на фиг. 3 это напряжение U), срабатывает компаратор 17 первого канала. Элемент И 18 совпадения первого канала формирует импульс, устанавливающ1Й1 в единичное состояние RS-триггер 19 первого канала, закрывающий элемент И 18 совпадения, с выхода которого короткий импульс через второй элемент ИЛИ 12 запускает формирователь 9 импульсов

и триггер 15 сбрасьшается в нулевое состояние. Ключ 4 закрывается и прекращается заряд конденсатора 5,, что свидетельствует об окончании процесса выборки дискретного значения последнего из канальных напряжений U. Так как все канальные триггеры к но5

менту времени tg установлены в единичное Состояние, многовходовый элемент И 16 формирует импульс запрета, запрещающий прохождение импульса с выхода формирователя 10 через элемен 13 запрета. Поэтому не происходит .очередной установки триггера 15 в единичное состояние, ключи 3 и 4 за- крыты и перезаряд конденсатора 5 не- возможен. При этом на выходе операционного усилителя 6 с момента времени tj до окончания шага дискретизации будет поддерживаться напряжение, равное дискретному значению U .

Начиная с очередного момента дискретизации все процессы повторяются аналогично.

Предлагаемое устройство обеспечивает в пределах одного шага-дискре- тизации выборку и хранение дискретньг значений канальных напряжений последовательно не по номеру канала, а последовательно по значениям канальньгх напряжений, начиная с наименьшего из всех и заканчивая наибольшим. На фиг. 2 наблюдается следующий порядок выборки и хранения напряжений: 1-й шаг дискретизации - U, U, U, U ; 2-й шаг - U, U, Uj, U, ; 3-й шаг - U, Uj, Uj, U,; 4-Й mar - U,, , U , .U, и ; 5-й шаг - Uj, , U и т.д.

Число каналов может быть произвольным, однако необходимо учесть, что максимальное число каналов определяется максимальной скоростью изменени канальных напряжений (т.е. их динамикой), погрешностью дискретизации, выборки и хранения, а также взаиморасположением канальных напряжений, как функций времени, одно относительно другого.

RS-триггер с момента установки в единичное состояние служит индикатором того, дискретное значение какого канала с этого момента в течение времени хранения находится на выходе устройства. При необходимости эта информация может быть использована как служебная или адресная, индицирующая номер канала, подключенного к выходу устройства.

Формула изобретения

Аналоговое запоминающее устройство, содержащее запоминающий конденсатор, первый и второй аналоговые ключи, первый и второй масштабные резис

Q 5

0 5 о

Q

„

5

5

196

торы, операционный усилитель, генератор импульсов и триггер управления выборкой дискретного значения сигнала, причем вход операционного усилителя соединен с одной обкладкой запоминающего конденсатора и выходами первого и второго аналоговых ключей, входы которых соединены соответственно с первыми выводами первого и второго масштабных резисторов, вторые выводы которых подключены соответственно к положительному и отрицательному выводам источников опорного напряжения, вторая обкладка запоминающего конденсатора подключена к выходу операционного усилителя и является выходом устройства, прямой вьпсод триггера управления выборкой дискретного значения сигнала подключен к управляющему входу второго аналогового ключа, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения многоканальности при сохранении высокого быстродействия устройства, в не го введены первый, второй, третий формирователи импульсов, многовходовый элемент И, элемент запрета, формирователь короткого импульса, первый и второй элементы ИЛИ и п каналов, каждый из которьк состоит из компаратора, элемента И и RS-триггера, причем первые входы компараторов соединены и подключены к выходу операционного усилителя, а вторые входы являются информационными входами устройства, выходы компараторов соединены соответственно с первыми входами элементов И, выходы которых соединены с соответствующими входами второго элемента ИЛИ и с S-входами RS-триггеров, R-входы RS-триггеров соединены и подключены к выходу формирователя короткого импульса и S-входу триггера управления выборкой дискретного значения сигнала, прямые выходы RS-триггеров соединены с соответствующими входами многовходового элемента И и являются адресными выходами устройствя инверсные выходы RS-триггеров подключены соответственно к вторым входам элементов И, вход первого формирователя импульсов подключен к генератору импульсов, первьш вход первого элемента ИЛИ соединен с выходом первого формирователя импульсов и подключен к управляющему входу первого аналогового ключа, второй вход

713361

первого элемента ИЛИ соединен с выходом элемента запрета, второй вход которого подключен к выходу многовходо- вого элемента И, выход первого эле- g мента ИЛИ подключен к входу формирователя коротких импульсов, выход второго элемента ИЛИ подключен к входу

198

второго формирователя импульсов, к выходу которого подключен вход третьего формирователя импульсов и R- вход триггера управления выборкой дискретного значения сигнала, выход третьего формирователя подключен к первому входу элемента запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1986 |

|

SU1381603A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Система многопрограммного проводногоВЕщАНия | 1979 |

|

SU815932A1 |

| Способ преобразования скоростей вращения двух валов для измерения соотношения скоростей и устройство для его осуществления | 1989 |

|

SU1636774A1 |

| Устройство для выбора канала с экстремальным средним напряжением | 1990 |

|

SU1800636A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Устройство для измерения относительной разности скоростей вращения | 1986 |

|

SU1455322A1 |

| Многоканальный аналого-цифровой преобразователь | 2023 |

|

RU2815253C1 |

| Аналоговый измеритель скорости | 1985 |

|

SU1283666A1 |

| Канал связи для одновременной передачи напряжения питания, синхроимпульсов и информации | 1990 |

|

SU1737458A1 |

Изобретение относится к устрой- ствам автоматики, измерительной и вычислительной технике и может быть использовано в многоканальных системах сбора информации, обеспечивая коммутацию аналоговых сигналов и одновременную выборку, и хранение их дис- кретньпс значений поочередно в порядке их возрастания. Цель изобретения - расширение функциональных возможностей за счет обеспечения многоканаль- ноСти при сохранении высокого быстродействия. Устройство обеспечивает более высокое быстродействие системы- сбора данных, так как сигналы на вход АЦП (выход аналогового ЗУ) поступают подготовленными в определенной последовательности от минимального до максимального значения. Затраты времени на выборку двух минимальньи значений незначительны, после чего происходит один заряд/емкости при выборке одного из максимальных (или близких к нему) значений и далее практически отсутствуют зaтpatы времени при выборке последнего наибольшего значения, 3 ил. с сл с со ОО О5

П

Ui

Составитель А. Ершова Редактор А. Козориз Техред И.Попович Корректор С. Черни

Заказ 4051/50 Тираж 589 Подписное

ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Басалаев Г | |||

| Г., Глемба В, И | |||

| Многоканальная система сбора данных.- Приборы и техника эксперимента, 1984, № 2 | |||

| 1972 |

|

SU414634A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-04—Подача