СЛ

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации воспроизведения цифровой магнитной записи | 1986 |

|

SU1337918A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ОТ ТИРИСТОРНОГО ЭФФЕКТА | 2012 |

|

RU2510893C2 |

| УСТРОЙСТВО ДЛЯ СОГЛАСОВАННОГО СОЕДИНЕНИЯ ДВУХПРОВОДНОГО И ЧЕТЫРЕХПРОВОДНОГО ТРАКТОВ | 1992 |

|

RU2014735C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАРДИОСТИМУЛЯТОРА | 1990 |

|

RU2016588C1 |

| Преобразователь частоты групп телефонных каналов | 1980 |

|

SU862355A1 |

| Компаратор напряжения | 1989 |

|

SU1653149A1 |

| Стабилизированный источник питания | 1981 |

|

SU993228A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Устройство для воспроизведения с носителя магнитной записи | 1985 |

|

SU1319074A1 |

Изобретение относится к технике накопления информации, в частности к устройствам для выделения тактовой частоты при воспроизведении цифрового сигнала, и может применение при цифровой передаче информации. Цель изобретения - повышение точности выделения тактовой частоты за счет уменьшения статической фазовой ошибки и собственных шумов. Устройство для выделения тактовой частоты при воспроизведении цифрового сигнала отличается тем, что в него введены даа компаратора, четыре диода, шесть резисторов, три конденсатора, два варикапа, которые совместно с другими элементами схемы включены между входной и выходной шинами устройства. 1 ил.

Изобретение относится к технике накопления информации, в частности к устройствам для выделения тактовой частоты при воспроизведении цифрового сигнала, и может найти применение при цифровой передачи цифровой информации.

Известное устройство для выделения тактовой частоты при воспроизведении цифрбвого сигнала, содержащее фильтр и формирователь импульсов, включенные между входной и выходной шинами.

Недостаток известного устройства состоит в значительной зависимости результата выделения тактовой частоты от величины нестабильности следования тактовых импульсов цифрового сигнала.

Наиболее близким по своей технической сущности к предлагаемому устройству для выделения тактовой частоты при воспроизведении цифрового сигнала является

устройство для выделения тактовой частоты при воспроизведении цифрового сигнала, содержащее первый и второй транзисторы, эмиттеры которых соединены соответственно через первый и второй резисторы с первой шиной питания, подключенной к первому выводу третьего резистора, соединенного вторым выводом с первым выводом первого конденсатора, второй вывод которого подсоединен через катушку индуктивности к общей шине, соединенной с первым выводом четвертого резистора и с первым выводом пятого резистора, подключенного вторым выводом к первому выводу шестого резистора и к эмиттеру третьего транзистора, база которого подсоединена к первому выводу седьмого резистора, четвертый , транзистор, соединенный базой с первым выводом восьмого резистора и подсоединенный базой к первому выводу второго

-ч

Х|

О

ю

00

ел

конденсатора, пятый транзистор, соединенный базой с первым выводом девятого резистора, третий и четвертый конденсаторы, десятый и одиннадцатый резисторы, входную шику и вторую шину питания. Недостаток этого устройства для выделения тактовой частоты при воспроизведении цифрового сигнала состоит в малой точности результата выделения тактовой частоты, определяемой стад#1чеекой фазовой ошибкой и собственными фазовыми шумами. Известное устройство -не позволяет также обеспечить достаточную помехоустойчивость, Кроме того известное устройство не позволяет обеспечить высокую скорость следования тактовых импульсов при достаточно малом потреблении энергии.

Цель изобретения - повышение точности выделения тактовой частоты за счет уменьшения статической фазовой ошибки и собственных шумов.

С этой целью в устройство для выделения тактовой частоты при воспроизведении цифрового сигнала, содержащее первый и второй транзисторы, эмиттеры которых соединены соответственно через первый и второй резисторы с первой шиной питания, подключенной к первому выводу третьего резистора, соединенного вторым выводом с первым выводом первого конденсатора, второй вывод которого подсоединен через катушку индуктивности к общей шине, соединенной с первым выводом четвертого резистора и с первым выводом пятого резистора, подключенного вторым выводом к первому выводу шестого резистора и к эмиттеру третьего транзистора, база которого подсоединена к первому выводу седьмого резистора, четвертый транзистор, соединенный базой с первым выводом восьмого резистора и подсоединенный эмиттером к первому выводу второго конденсатора, пятый транзистор, соединенный базой с первым выводом девятого резистора, третий и четвертый конденсаторы, десятый и одиннадцатый резисторы, входную шину, выходную шину и вторую шину питания, зведенч первый компаратор, подсоединенный неинвертирующим входом к входной шине, второй компаратор, подключенный прямым выходом к выходной шине и соединенный неинвертирующим входом с вторым выводом шестого резистора и подсоединенный инвертирующим входом к первому выводу третьего конденсатора, первый м второй диоды, подключенные катодами к вторым выводам соответственно восьмого и девятого резисторов, третий и четвертый диоды, соединенные анодами с первыми выводами соответственно десятого и одиннадцатого резисторов, подключенных вторыми выводами к второй шине питания, двенадцатый резистор, подключенный первым выводом к коллектору первого транзистора и к коллектору третьего транзистора, тринадцатый резистор, включенный между первой шиной питания и вторым выводом четвертого резистора, соединенным с базой четвертого транзистора и с базой пятого транзистора, подключенного коллектором к базе первого транзистора и к базе и к коллектору второго транзистора; первый варикап, соединенный первым выводом с вторым выводом первого конденсатора, подключенного вторым выводом к первому

выводу четвертого конденсатора и к базе третьего транзистора четырнадцатый, пятнадцатый, шестнадцатый и семнадцатый резисторы, пятый, шестой и седьмой конденсаторы и второй варикап, подсоединенные первыми к общей шине, соединенной с вторым выводом третьего конденсатора, первый и второй триггеры и восемнадцатый, девятнадцатый и двадцатый резисторы, причем первый и второй диоды подключены

катодами к вторым выводам,соответственно четырнадцатого, пятнадцатого резисторов и соединены анодами с анодами соответственно третьего и четвертого диодов, подсоединенных катодами к инвертирующим

выходам соответственно первого и второго триггеров, подключенным к информационным входам соответственно второго и первого триггеров; которые соединены входами синхронизации соответственно с прямым и

инверсным выходами первого компаратора и подсоединены входами установки нуля соответственно к инверсному и прямому выходам второго компаратора, соединенного инвертирующим входом с вторым выводом

шестнадцатого резистора и с первым выводом восемнадцатого резистора, второй вывод которого подключен к первой шине питания, соединенной с коллектором третьего транзистора, подсоединенного базой к

второму выводу пятого конденсатора, а второй вывод двенадцатого резистора подключен к второму выводу седьмого резистора, соединен через девятнадцатый резистор с вторыми выводами первого и второго варикапов и подсоединен через двенадцатый ре- зистор и вторым выводом шестого конденсатора и семнадцатого резистора.

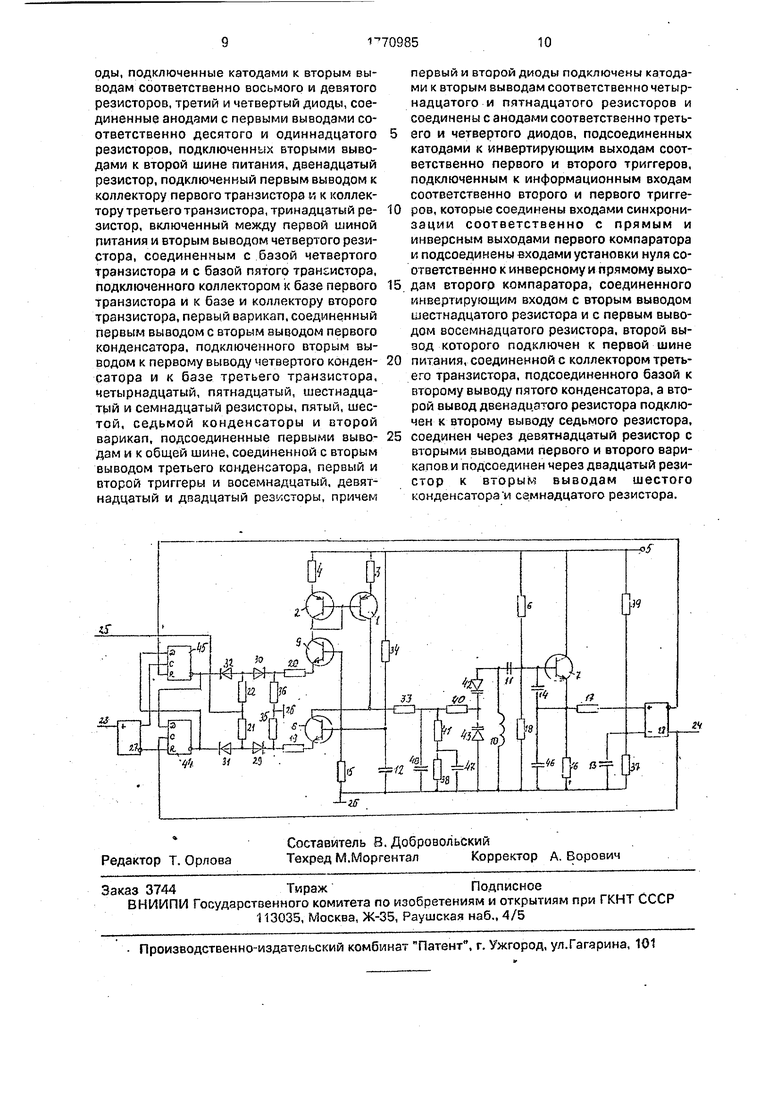

На чертеже изображен один из возможных вариантов предлагаемого устройства

для выделения тактовой частоты при воспроизведении цифрового сигнала.

Устройство для выделения тактовой частоты при воспроизведении цифрового сигнала содержит первый и второй

транзисторы 1 и 2, эмиттеры котор1.-ч соединены соответственно через первый и второй резисторы 3 и 4 с первой шиной 5 питания, подключенной к первому выводу третьего резистора 8, третий, четвертый и пятый транзисторы 7,8 и 9, катушку 10 индуктивности, первый, второй, третий и четвертый конденсаторы 11, 12, 13 и 14, четвертый, пятый, шестой, седьмой, восьмой, девятый. десятый и одиннадцатый резисторы 15, 16, 17. 18, 19, 20, 21, 22, входную шину 23, выходную шину 24 и вторую шину 25 питания и общую шину 26. Третий резистор б соединен вторым выводом с первым выводом первого конденсатора 11, второй вывод которого подсоединен через катушку 10 индуктивности к общей шине 26. соединенной с первым выводом четвертого .резистора 1Б и с первым выводом пятого резистора 16, подключенного вторым выводом к первому выводу шестого резистора 17 и к эмиттеру третьего транзистора 7. База i pe t ьего ран- зистора 7 подключена к первому выводу седьмого резистора 18. Четвертый транзистор 8 соединен базой с перьым выводом восьмого резистора 19 и подсоединим эмит- террм.к первому выводу второго конденсатора 12. Пятый транзистор 9 соединен базой с первым выводом десятого р9 -и.:тара 20. Устройство для выделений тактовой частоты при воспроизведении цифрового сигнала содержиттакже первый компаратор 27, подсоединенный неинвертирующим сходом к входной шине 23, второй компаратор 28, подключенный прямым вь ходом к входной шине 24 и соединенный неинвертирующим входом с вторым выводом шестого резистора 17 и подсоединенный инвертирующим входом к первому выводу третьего конденсатора 13, первый, второй, третий и четвертый диоды 29, 30, 31, 32, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый к двадцатый резисторы 33, 34, 35, 36, 37, 38, ЗЭ. 40, 41, первый и второй варикапы 42 и 43, первый и второй триггеры 44 и 45, пятый, шестой и седьмей конденсаторы 46, 47, 48, Первый и второй диоды 29 и 30 подключены катодами к вторым выводам соответственно восьмого и девятого резисторов 19 и 20. Третей и четвертый диоды 31 и 32 соединены анодами с первыми выводами соответстгенно десятого и одиннадцатого резисторов 21 и 22, подключенных вторыми выводами к второй шине 25 питания, двенадцатый резистор 33, подключенный первым выводом к коллектору .первого транзистора 1 и к коллектору третье о транзистора 8. Тринадцатый резистор 34 включен между первой шикой 5 питания и вторым выводом четвертого резистора 15, соединенным с базой четвертого транзистора 8 и с базой пятого транзистора 9, подключенного коллектором к базе перsoro транзистора 1 и к базе и к коллектору второго транзистора 2. Первый варикап 42 соединен анодом с вторым выводом первого конденсатора 11, подключенного вторым выводом к первому выводу четвертого кон0 денсатора 14 и к базе третьего транзистора 7, Чзтьшнздцгтый, пятнадцатый, шестнадцатый и семнадцатый резисторы 35,36,37 и 38; пятый, шестой и седьмой конденсаторы 46,47 и 48 второй вэржап 43 подсоединен

5 первыми выводами к общей шине 26, соединенной с вторым выводом третьего конденсатора 13. При этом второй варикап 43 чодсоединен анодом к общей шине 26. Первый к второй диоды 29 и 30 подключены

0 катодами к вторым выводам соответственно четырнадцатого и пятнадцатого резисторов 35 и 36 и соединены анодами с анодами соответственно третьего и четвертого диодов 31 и 32, подсоединенных катодами к

5 инвертирующим выходам соответственно первого и второго триггеров 44 и 45, подключенным к информационным входам со- отЕвтс. векно второго и первого триггеров 15 и 44. Втор /й л первый триггеры 45 и 44

0 соединены пходами синхронизации соответственно с прямым и инверсным выходами первого компаратора 27 и подсоединены входами установки нуля соответственно к инверсному и прямому выходам второго

5 компаратора 28. Второй ксмпаратор 28 соединен инвертор1, ющим входом с вторым выводом шестнадцатого резистора 37 и с первым выводом восемнадцатого резистора 39, второй ВУЗОД которого подключен к

0 первой шине 5 питания. Первая шина 5 питания соединена с коллв(чтором третьего транзистора 7, подсоединенного базой к второму выводу пятого конденсатора 46, Второй вывод двенадцатого резистора 33

5 подключен к второму выводу седьмого конденсатора 48, соединен через девятнадцатый резистор 40 е катодами первого и скорого варикапов 42 и 43 и подсоединен через двенадцатый резистор 41 к вторым

0 выводам шестого конденсатора 47 и семнадцатого резистора 38.

Работа предлагаемого устройства для выделения тактовой частоты при воспроизведении цифрового сигнала происходит

5 следующим образом. Входной цифровой сигнал, представляющий собой случайную последовательность наличие импульсов 1 неравной амплитуды и отсутствие импульсов О поступает на компаратор 27, который на своих виходах формирует взаимно

инверсные сигналы, имеющие нормализованную амплитуду, пригодную для дальнейшей обработки. Кроме того, компаратор 27 позволяет минимизировать сдвиг фронтов импульсов между взаимоинверсными сигналами Эти сигналы наступают на устано- вочный и синхронизирующий входы триггеров 44 и 45, а на соответствующие входы этих же триггеров 44 и 45 поступают взаимоикверсные сигналы с выходом компараторов 28, формирующего их из сигнала управляемого генератора на варикапах 42 и 43, индуктивности 10, конденсаторах 11,14,46 и транзисторе 7. Резисторы 8,16 и 18 определяют режим генератора по постоянному току, а резистор 17 уменьшает вли- яние неинвертирующего входа компаратора 28 на собственную стабильность генератора. Резисторы 37 и 39 и коммутатор,13увеличивают помехоустойчивость компаратора 28. Триггера 44 и 45 на своих инверсных выходах формируют сигналы логической 1 при совпадении фронтов импульсов на их синхронизирующих входах. 8 этом случае ключи на диодах 30 и 32, 29 и 31 формируют на эмиттерах транзисторов 8 и 9 более высокий потенциал, при котором транзисторы 1,2,8 и 9 запираются. Резисторы 15и34и конденсатор 12 формирует на базах транзисторов 8 и 9 напряжение, необходимое для переключения их от сигналов ключей на диодах 29,30,31 и 32, при отом резисторы 19,20,21,22,35 и 36 обеспечивают режим по постоянному току этих ключей. При запертых транзисторах 1 и 8 на их коллекторах запоминается напряжение, которое формировалось на них поело предыдущего открывания или транзистора 1, или транзистора 8, Напряжение запоминается конденсатором 48 пропорционально-интегрирующего фильтра на резисторах 33,38 и 41. Конденсатор 48 необходим для фильтрации переменной составляющей сигнала, формируемого при открывании транзисторов 1 и 8. Резистор 40 необходим для развязки по переменному току катодов варикапов 42 и 43 с пропорционально-интегрирующим фильтром. При несовпадении фронтов импульсов не синхронизирующих входах триггеров 44 и 45 на мнверсном выходе одного из них формируется импульс логического О, длительность которого определяется модулем разности фаз между фронтами импульсов на синхронизирующих входах .триггеров 44 я 45. Формирование импульса О на выходе или триггера 44, или триггера 45 определяется знаком разности фаз вышеуказанных импульсов. После переходного процесса включения большую

часть времени транзисторы 1 и 8 закрыты, а на выходной шине 24 формируется тактовая частота, равная номинальной частоте сигнала на входной шине 23, причем фаза импульсов совпадает с точностью до 10 не с фазой импульсов 1 на входной шине 23. В диапазоне фазового дрожания сигналов 1 на входной шине 23 не менее 20 кГц. В результате этого повышается точность выделения

0 тактовой частоты, так как статическая фазовая ошибка, возникающая при изменении параметров варикапов 42 и 43, индуктивности 10, и собственной нестабильности генератора на транзисторе 7, стремится к нулю,

5 а собственные фазовые шумы генератора на транзисторе 7 подавляются в значительной степени за счет формирования полосы пропускания цепи управления варикапами 42 и 43 более 20 кГц.

0

Формула изобретения Устройство для выделения тактовой частоты при воспроизведении цифрового сигнала, содержащее первый и второй

5 транзисторы, эмиттеры которых соединены соответственно через первый и второй резисторы с первой шиной питания, подключенной к первому выводу третьего резистора, соединенного вторым выводом с

0 первым выводом первого конденсатора, второй вывод которого подсоединен через катушку индуктивности к общей шине, соединенной с первым выводом четвертого резистора и с первым выводом пятого

5 резистора, подключенного вторым выводом к первому выводу шестого резистора и к эмиттеру третьего транзистора, база которого подсоединена к первому выводу седьмого резистора, четвертый транзистор,

0 соединенный базой с первым выводом восьмого резистора и подсоединенный эмиттером к первому выводу второго конденсатора, пятый транзистор, соединенный базой с первым выводом девятого рези5 стора, третий и четвертый конденсаторы, десятый и одиннадцатый резисторы, входную шину, выходную шину и вторую шину питания, отличающееся тем, что, с целью повышения точности выделения так0 товой частоты за счет уменьшения статической фазовой ошибки м собственных фазовых шумов, в него введены первый компаратор, подсоединенный неинвертирующим входом к входной шине, второй

5 компаратор, подключенный прямым выходом к выходной шине и соединенный неинвертирующим входом е вторым выводом шестого резистора и подсоединенный инвертирующим входом к первому выводу третьего конденсатора, первый и второй диоды, подключенные катодами к вторым выводам соответственно восьмого и девятого резисторов, третий и четвертый диоды, соединенные анодами с первыми выводами соответственно десятого и одиннадцатого резисторов, подключенных вторыми выводами к второй шине питания, двенадцатый резистор, подключенный первым выводом к коллектору первого транзистора и к коллектору третьего транзистора, тринадцатый ре- зистор, включенный между первой шиной питания и вторым выводом четвертого резистора, соединенным с базой четвертого транзистора и с базой пятого транзистора, подключенного коллектором к базе первого транзистора и к базе и коллектору второго транзистора, первый варикап, соединенный первым выводом с вторым выводом первого конденсатора, подключенного вторым выводом к первому выводу четвертого конден- сатора и к базе третьего транзистора, четырнадцатый, пятнадцатый, шестнадцатый и семнадцатый резисторы, пятый, шестой, седьмой конденсаторы и второй варикап, подсоединенные первыми выво- дам и к общей шине, соединенной с вторым выводом третьего конденсатора, первый и второй триггеры и восемнадцатый, девятнадцатый и двадцатый резисторы, причем

первый и второй диоды подключены катодами к вторым выводам соответственно четырнадцатого и пятнадцатого резисторов и соединены с анодами соответственно третьего и четвертого диодов, подсоединенных катодами к инвертирующим выходам соответственно первого и второго триггеров, подключенным к информационным входам соответственно второго и первого триггеров, которые соединены входами синхронизации соответственно с прямым и инверсным выходами первого компаратора и подсоединены входами установки нуля соответственно к инверсному и прямому выходам второго компаратора, соединенного инвертирующим входом с вторым выводом иестнадцатого резистора и с первым выводом восемнадцатого резистора, второй вы- зод которого подключен к первой шине питания, соединенной с коллектором третьего транзистора, подсоединенного базой к второму выводу пятого конденсатора, а второй вывод двенадцатого резистора подключен к второму выводу седьмого резистора, соединен через девятнадцатый резистор с вторыми выводами первого и второго варикапов и подсоединен через двадцатый резистор к вторым выводам шестого конденсатора и семнадцатого резистора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Л.Н.Голубев и др | |||

| Кровля из глиняных обожженных плит с арматурой из проволочной сетки | 1921 |

|

SU120A1 |

| Способ закалки пил | 1915 |

|

SU140A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-10-23—Публикация

1991-01-08—Подача