Изобретение относится к программному управлению станками и предназначено для формирования корректирующих сигналов при компенсации систематических ошибок положения конечных звеньев станка, вызванных, например, кинематическими погрешностями передач, несоосностыо соединений и систематической погрешностью датчиков положения.

Цель изобретения - расишрение области применения.

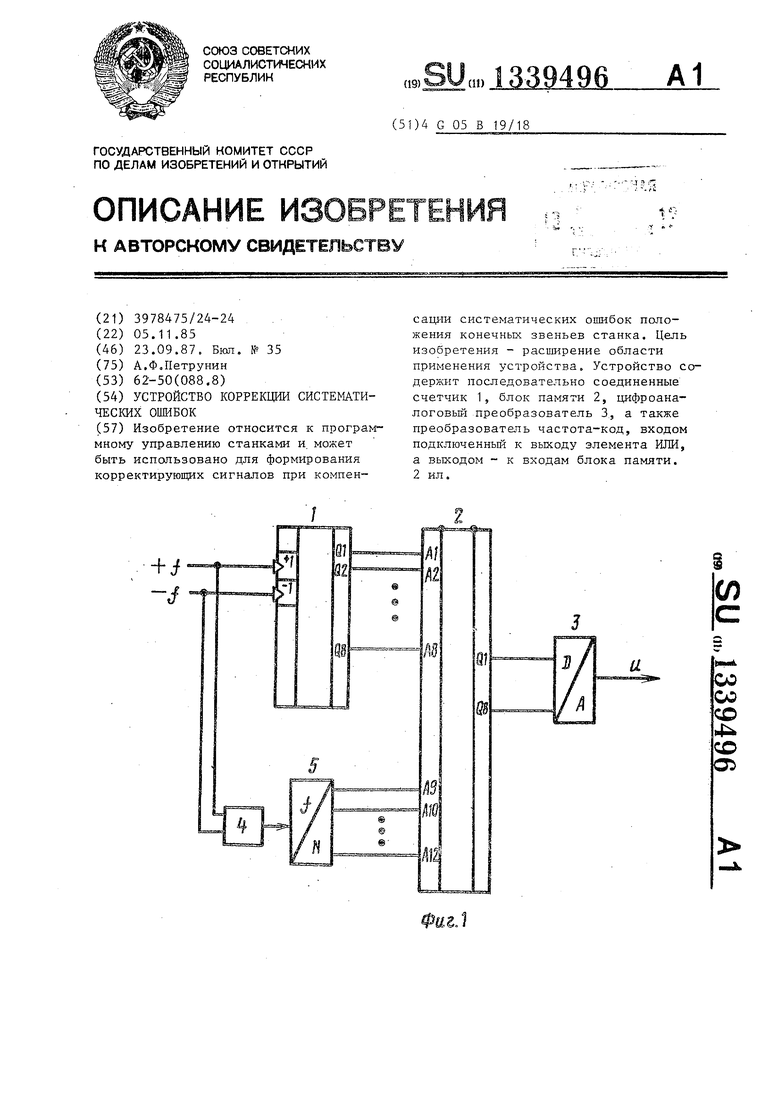

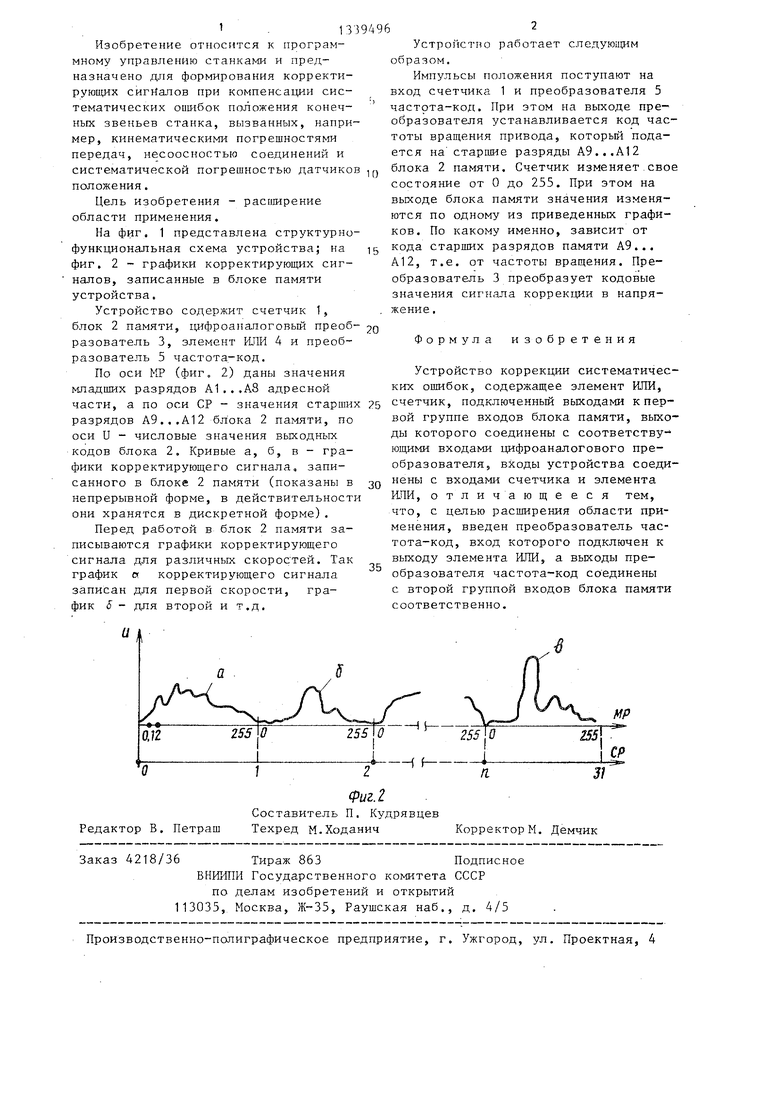

На фиг. 1 представлена структурно- функциональная схема устройства; на фиг. 2 - графики корректирующих сигналов, записанные в блоке памяти устройства.

Устройство содержит счетчик 1,

блок 2 памяти, цифроаналоговый преобразователь 3, элемент ИЛИ 4 и преобразователь 5 частота-код.

По оси МР (фиг. 2) даны значения младших разрядов А1..,А8 адресной

части, а по оси СР - значения старших 25 счетчик, подключенный выходами к перразрядов А9...А12 блока 2 памяти, по оси и - числовые значения выходных кодов блока 2. Кривые а, б, в - графики корректирующего сигнала, записанного в блоке 2 памяти (показаны в непрерывной форме, в действительност они хранятся в дискретной форме).

Перед работой в блок 2 памяти записываются графики корректирующего сигнала для различных скоростей. Так график о. корректирующего сигнала записан для первой скорости, график 5 - для второй и т.д.

и

Устройство работает следующим образом.

Импульсы положения поступают на вход счетчика 1 и преобразователя 5 частота-код. При этом на выходе преобразователя устанавливается код частоты вращения привода, которьпЧ подается на старшие разряды А9...А12 блока 2 памяти. Счетчик изменяет-свое состояние от О до 255. При этом на выходе блока памяти значения изменяются по одному из приведенных графиков. По какому именно, зависит от кода старших разрядов памяти А9... А12, т.е. от частоты вращения. Преобразователь 3 преобразует кодовые значения сигнала коррекции в напряжение.

Формула изобретения

Устройство коррекции систематических ошибок, содержащее элемент ИЛИ,

0

5

вой группе входов блока памяти, выходы которого соединены с cooTBeTCTBy- ющими входами цифроаналогового преобразователя, входы устройства соединены с входами счетчика и элемента ИЛИ, отличающееся тем, что, с целью расширения области применения, введен преобразователь частота-код, вход которого подключен к выходу элемента ИЛИ, а выходы преобразователя частота-код соединены с второй группой входов блока памяти соответственно.

а

.Т

л .. Х

МР

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ параметрической компенсации циклических погрешностей привода подач станка с ЧПУ | 1986 |

|

SU1403017A1 |

| Устройство для коррекции циклических ошибок | 1986 |

|

SU1359770A1 |

| Устройство для коррекции циклических ошибок | 1985 |

|

SU1293697A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1987 |

|

SU1548845A2 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2024192C1 |

| Устройство для автоматического переключения однофазных нагрузок в низковольтных распределительных сетях | 1981 |

|

SU1026234A1 |

| НЕЙРОСЕТЕВОЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2008 |

|

RU2380752C2 |

| Преобразователь активной мощности в цифровой код | 1987 |

|

SU1451615A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

Изобретение относится к программному управлению станками и. может быть использовано для формирования корректирующих сигналов при компен+ -J f ul сации систематических ошибок положения конечных звеньев станка. Цель изобретения - расширение области применения устройства. Устройство содержит последовательно соединенные счетчик 1, блок памяти 2, 1Щфроана- логовый преобразователь 3., а также преобразователь частота-код, входом подключенный к выходу элемента ИЛИ, а выходом - к входам блока памяти. 2 ил. с д детд:@Й1ив: Л/ (Л и оо со СО 4: СО О5

Заказ 4218/36 Тираж 863Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Авторы

Даты

1987-09-23—Публикация

1985-11-05—Подача