Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода в ЭВМ аналоговых сигнапов и для их распределения на устройстве отображения в системах автоматизированного сбора обработки и отображения информации, в частности в системах сбора, обработки и отображения физиологической информации, для которых характерны прием и обработка большого числа аналоговых сигналов, а также регистрация на устройствах отображения (осциллоскоп,, самописец) входных физиологических сигналов в неизмененном виде,

Цель изобретения - увеличение быстродействия устро1 ства за счет обеспечения процесса ввода и вывода аналоговой информации в автономном режиме.

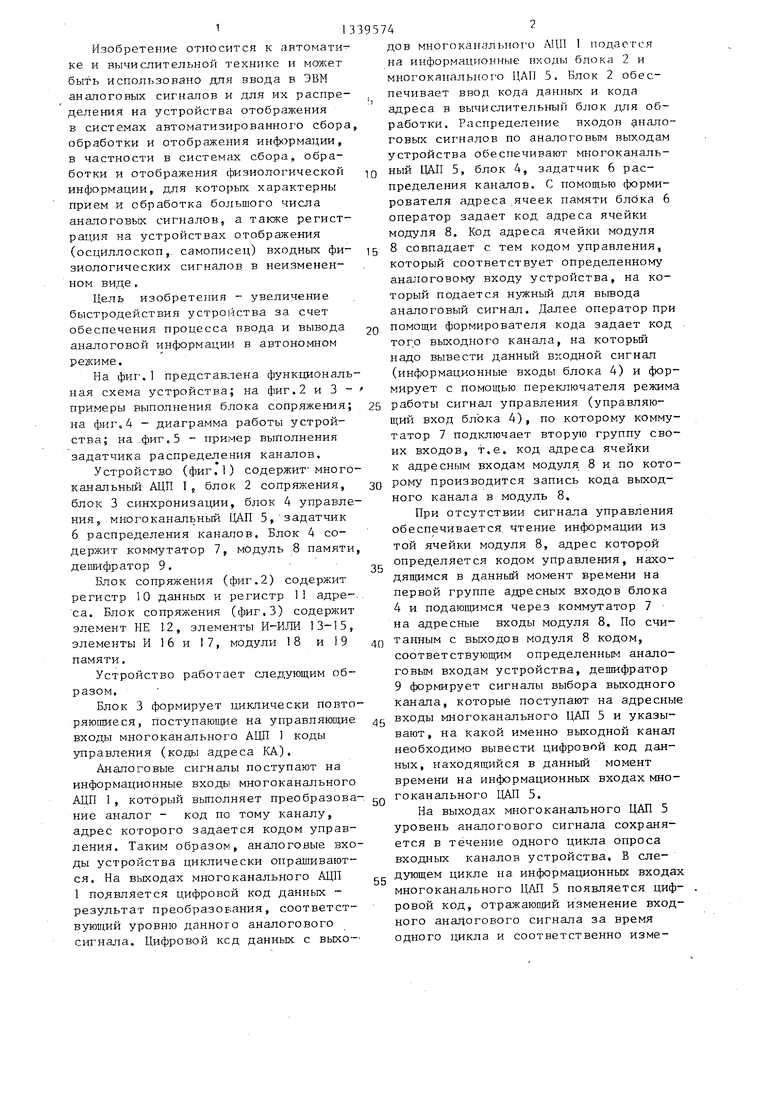

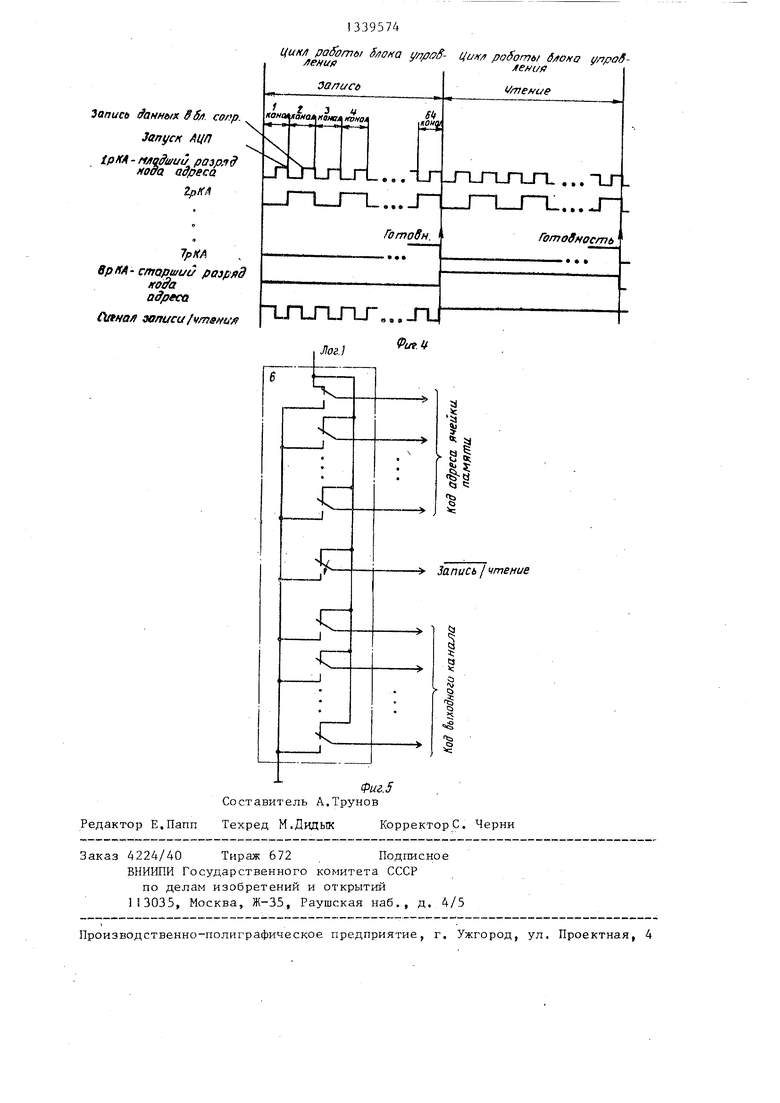

На фиг,1 представлена функциональная схема устройства; на фиг.2 и 3 - примеры выполнения блока сопряжения; на фиг.4 - диаграмма работы устройства; на -фиг.5 - пример выполнения задатчика распределения каналов.

Устройство (фиг.О содержит многоканальный АЦП 1, блок 2 сопряжения, блок 3 синхронизации, блок 4 управления, многоканальный ДП 5, задатчик 6 распределения канапов. Блок 4 содержит коммутатор 7, модуль 8 памяти депифратор 9,

Блок сопряжения (фиг.2) содержит регистр 10 данных и регистр 11 адреса. Блок сопряжения (фиг.З) содержит элемент НЕ. 12, элементы И-ИЛИ 13-15, элементы И 16 и 17, модули 18 и 19 памяти.

Устройство работает следующим образом.

Блок 3 формирует циклически повторяющиеся, поступающие на управляющие входы многоканального АЦП 1 коды управления (коды адреса КА).

Аналоговые сигналы поступают на

При отсутствии с обеспечивается, чтен той ячейки модуля 8 определяется кодом дящимся в данный мо первой группе адрес 4 и подающимся чере на адресные входы танным с выходов мо соответствуюш 1м оп говым входам устрой 9 формирует сигналы канала, которь е пос входы многоканально вают, на какой имен необходимо вывести ных, находящийся в времени на информац

информационные входы многоканального

АДП 1 , который вьшолняет преобразова-. gQ гоканального ЦАП 5. ние аналог - код по тому каналу, адрес которого задается кодом управления. Таким образом, аналоговые входы устройства циклически опрашиваются. На выходах многоканаль 1ого АЦП 1 появляется цифровой код данных - результат преобразон ания, соответствующий уровню данного аналогового сигнала. Цифровой кед данных с выхо-55

На выходах много уровень аналогового ется в течение одно входных каналов ус дующем цикле на инф многоканального ЦАП ровой код, отражающ ного аналогового си одного цикла и соот

дов многоканальтюго ЛИП подастся на информацт-гонные входы блока 2 и многоканального ЦАП 5. Блок 2 обеспечивает ввод кода данных и кода адреса в вычислительный блок для обработки. Распределение входов налоговых сигналов по аналоговьм выходам устройства обеспечивают ньгогоканаль- ный ЦАП 5, блок 4, задатчик 6 распределения каналов. С помощью формирователя адреса ячеек памяти блока 6 оператор задает код адреса ячейки модуля 8. Код адреса ячейки модуля

8 совпадает с тем кодом управления, который соответствует определенному аналоговому входу устройства, на который подается нужный для вьтода аналоговый сигнал. Далее оператор при

помощи формирователя кода задает код тог.о выходного канала, на который надо вывести данный входной сигнал (информационные входы блока 4) и формирует с помощью переключателя режима

работы сигнал управления (управляющий вход блока 4), по которому коммутатор 7 подключает вторую группу своих входов, т,е. код адреса ячейки к адресным входам модуля 8 и по которому производится запись кода выходного канала в модуль 8,

При отсутствии сигнала управления обеспечивается, чтение информации из той ячейки модуля 8, адрес которой определяется кодом управления, находящимся в данный момент времени на первой группе адресных входов блока 4 и подающимся через коммутатор 7 на адресные входы модуля 8. По считанным с выходов модуля 8 кодом, соответствуюш 1м определенным аналоговым входам устройства, дешифратор 9 формирует сигналы выбора выходного канала, которь е поступают на адресные входы многоканального ЦАП 5 и указывают, на какой именно выходной канал необходимо вывести цифровой код данных, находящийся в данный момент времени на информационных входах мно

гоканального ЦАП 5.

На выходах многоканального ЦАП 5 уровень аналогового сигнала сохраняется в течение одного цикла опроса входных каналов устройства, В следующем цикле на информационных входах многоканального ЦАП 5 появляется цифровой код, отражающий изменение входного аналогового сигнала за время одного цикла и соответственно изме 13НЯС1 ся уровень аналоговог-о сиг нала па выходах многоканального ЦДП 5.

Подобным образом оператором задаются различные распределения входных аналоговых сигналов по всем выходным каналам устройства перед началом работы устройства или в процессе его работы.

Многоканальные АЦП 1 и ЦДЛ 5 могут быть реализованы по известным . схемам.

Блок 3 синхронизации содержит генератор импульсов, соединенный с кольцевым счетчиком, выходы которого являются выходами блока.

Задатчик 6 может быть вьтолнен в виде набора фиксируемых переключателей, позволяющих подавать на выход уровни логических нулей и единиц в зависимости от положения переключателей.

Блок 2 сопряжения может обеспечить, например пословный ввод цифрового кода данных и кода адреса аналогового входа устройства в вычислительный блок через его порты ввода для обработки (вариант I). При этом код данных и код адреса поступают на входы регистра 10 хранения данных и регистра 11 хранения кода адреса и по сигналу строба (младший разряд кода управления) запоминаются в них. Одновременно с этим сигнал строба поступает в вычислительный блок, извещая его о, готовности вводимой информации на выходах регистров 10 и 11 хранения.

Блок 2 сопряжения (вариант II) позволяет вводить в вычислительный блок информацию больщими массивами по одному сигналу Готовность ; Блок 2 имеет два модуля 18 и 19 памяти, каждый из которых содержит определенное число ячеек памяти, кратное числу информационных входов устройства. Данные, поступающие в блок 2, записываются в одну из ячеек памяти модуля 18 (19), одновременно с этим из другого модуля памяти 19 (18) обеспечивается считывание данных в вычислительный блок.

По окончании записи данных в модули 18 и 19 памяти вычислительный блок извещается об этом по линии Готовность. Переключение модулей 18 и 19 памяти на запись - чтение производится автоматически по входу восьмого разряда кода адреса через элементы И 16 и 17.

9574

Коды адресов через элемент И-КЛИ 13 (14) подаются на адресные входы модуля 18 (9) в зависимости от того,

,. на втором управляюп1ем входе которого из элементов И-ШЖ 13 (14) в данный момент находится разрешающий высокий потенциал, поступающий в блок 2 сопряжения на вход восьмого разряда

10 кода адреса. При этом на первом управляющем входе элемента И-ИЛИ 14 (15) инвертор 12 формирует запрещающий низкий потенциал. Одновременно с этим на первом управляющем входе другого

15 модуля 19 (18) памяти находится разрешающий потенциал, а на втором управляющем входе его - запрещающий потенциал с выхода инвертора 12. Поэтому на адресные входы другого мо20 дуля 19 (18) памяти из вычислительного блока через элемент И-ИЛИ 14 (13), поступают адреса тех ячеек памяти, из которых требуется считать данные . в вычислительный блок.

25 Подобным же образом заданием высокого или низкого потенциала на входе восьмого разряда кода адреса и на выходе инвертора 12 формируются сигналы записи - чтения на выходах эле30 ментов И 16 и 17. В случае записи данных в модуль 18 (19) памяти сигнал записи - чтения представляет собой инвертированный строб, поступающий в блок 2 сопряжения на вход первого разряда кода адреса. Низкий потенциал сигнала записи - чтения устанавливает модуль памяти 18 (19) в состояние Запись. При этом код данных на информационных входах мо4Q дуля 18 (19) загружается в ту ячейку памяти, адрес которой находится на адресных входах модуля памяти 18 (19). В случае чтения данных из модуля 19 (18) памяти сигнал записи

лс чтения представляет собой высокий потенциал, который устанавливает модуль 19 (18),памяти в состояние Чтение. При этом из модуля 19 (18) памяти считываются коды данных по адgQ ресу, находящемуся на его адресных входах.

35

55

Формула изобретения

1. Устройство для ввода и вывода аналоговой информации, содержащее многоканальный аналого-цифровой преобразователь, многоканальный цифро- аналоговый преобразователь и блок

ь1

сопряжения, входы многоканального аналого-цифрового преобразователя являются информационны1 1и входами устройства, выходы многоканального циф- роаналогового преобразователя являются информационными выходами устрой

ства, вьгкоды многоканального аналого цифрового преобразователя соединены с информационными входами блока сопряжения, отличающее ся тем, что, с целью автоматизации ввода и распределения ин(}юрмации, в него введены блок синхронизации, блок управления, задатчик )эаспределения каналов, выходы блока синхронизации соединены с входами управления многоканального аналого-цисЬрового преобразователя, адресными входами первой груццы блока сопряжения и блока управления, первая группа выходов за- датчика распределения каналов соединена с адресными входами второй группы блока управления, вторая группа выходов задатчика распределения капа лов соединена с информационными входами блока управления,, а выход - с управляющим входом блока управления, выходы блока управпения соединены с адресныг входами многоканального цифроаналогового преобразователя, информационные входы которого соединены с выходами многоканального аналого-цифрового преобразователя, адресные входы второй группы блока сопряжения являются адресными входа

39574

ми ycTpoi icTpa, PFiKOAM блокл сопряжения являются ипформационн 1мп В хода- ми устройства,

2, Устройство-по п.1, о т л и - ч а ю ш е е с я тем, что блок управления содеряотт коммутатор, модуль памяти, депшфратор, первая и вторая группы входов коммутатора являются

10 адресными входами первой и второй групп блока соответственно, управляющие входы коммутатора и модуля памяти являются управляющим входом блока, выходы коммутатора соединены

15 с адресными входами -модуля памяти, информационные входы которого являются информационными входами блока, выходы модуля памяти соединены с входами депшфратора, выходы которого

20 являются управляющими выходами блока.

3, Устройство по п.1, о т л и чающееся

тем, что задатчик

25

30

35

распределения каналов содержит формирователь адреса ячеек памяти, переключатель режима работы, формирователь кода выходного канала, выходы формирователя адреса ячеек памяти являются выходами первой группы задатчика распределения каналов, выход переключателя режима работы является выходом задатчика распределения каналов, выходы формирователя кода выходного канала являются выходами второй группы задатчика распределения каналов.

-z

IpKK.

Готовность

Ю

Ионные

Код адреса

11

Фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОДВИГАТЕЛЕМ СУДОВОЙ ЛЕБЕДКИ | 1994 |

|

RU2074501C1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2012 |

|

RU2524852C2 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Многоканальное устройство для ввода-вывода аналоговой информации | 1988 |

|

SU1564606A1 |

| Устройство для программного управления технологическим оборудованием | 1985 |

|

SU1325407A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода в ЭВМ аналоговых сигналов и их распределения на устройства отображения информации, в частности, в сн стемах сбора, обработки и отображения физиологической информации, для которых характерны обработка большого числа аналоговых сигналов и их регистрация. Целью изобретения является автоматизация ввода и распределение информации. Устройство содержит многоканальный аналого-цифровой и многоканальный цифроанапоговьй преобразователи, блок управления, блок синхронизации, блок сопряжения с ЭВМ и задатчик распределения каналов. Цоставленная цель достигается путем обеспечения возможности ввода и вывода многоканальной аналоговой информации в автономном режиме без учас- , тия ЭВМ. 2 з.п. ф-лы, 5 ил. в сл со со со сд 4

Код адреса

IpKA

ta

/pw

г

Го/по8нос/пь

i

Манные

/

Данные

-,

Г

в

и&.3

1339574

Цин/1 ра огпб/ S/fOHQ i/n/}oS- Цик/г роботы лени/уJisf uff

залисб

Записи ifoHHu/K ffS/t. coup.

t 3 яаналяонал канал

i//7ieMue

S

МНШ

Запуск АЦП

и раз, адреса

гркл

tpKA-HMffutuu разряд Hoffa адреса

Ln

... г

TrLrLrLr«,,JTJ

я )

Лог.

С

Готабн.

Готовности

I,

I

- Запись I чтение

Фиг.5 Составитель А.Трунов

Редактор Е.Папп Техред М.ДВДЫК ° ™; li; I LT

Заказ А224/40Тираж 672 .Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно

-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

« S

Авторы

Даты

1987-09-23—Публикация

1986-01-03—Подача