Изобретение относится к области вьгчислите г1ьиой техники и может быть использовано в системах цифровой обработки радиолокационных, сейсмических, гидроакустических, видео- и других сигналов.

Целью изобретен ия является повышение производительности.

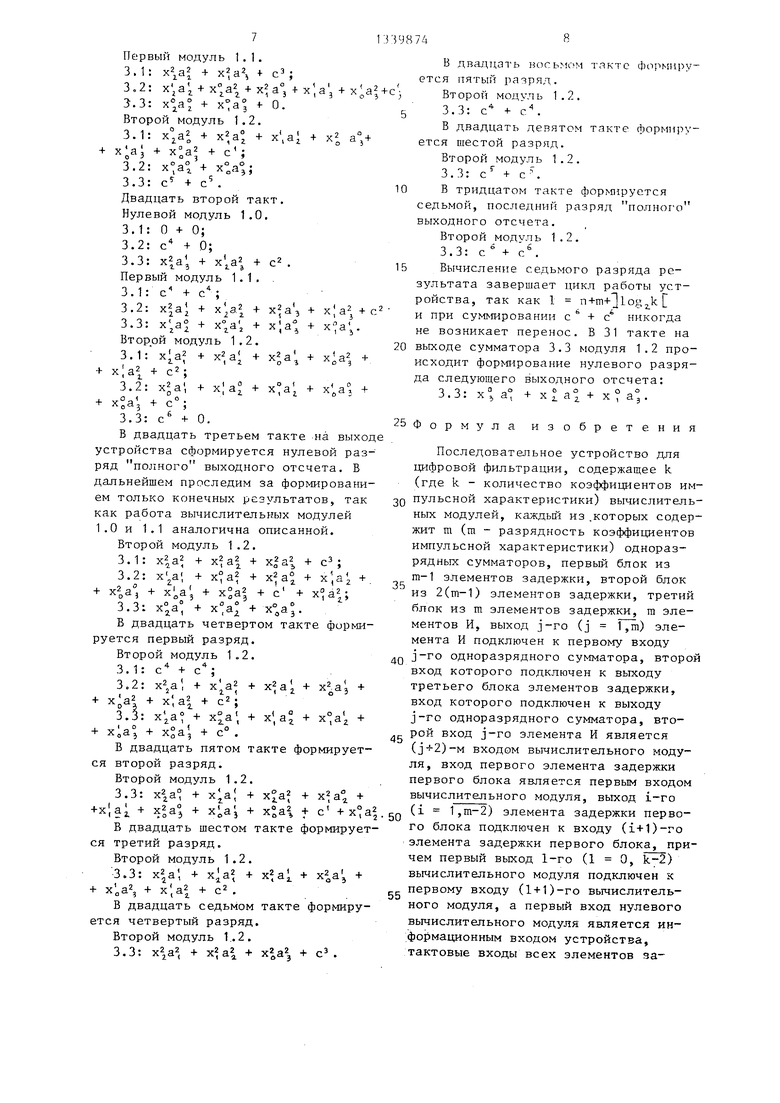

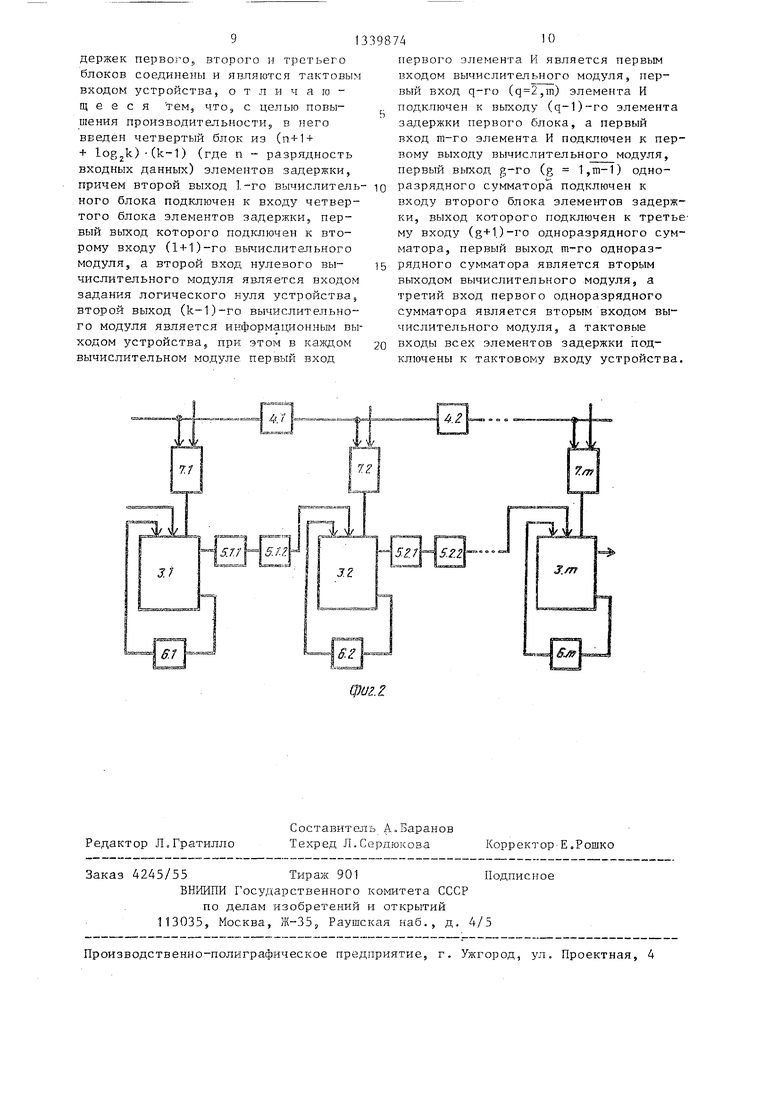

На фиг.1 представлена структурная схема последовательного устройства для цифровой фильтрации; на фиг.2 - структурная схема вычисли- Tej ibHoro модуля.

Последовательное устройство для цифровой фильтрации (фиг,1) содержит k вычислительных модулей 1,0,1.(k-1) блок из (п + 1+log 2() тактируемых элементов 2.1.1, 2 . 1(n+logjk+l) 2.2.2, .n-blog k+1 , . . .,2.k-1 xCn+log k+D задержки.

Каждая из вычислительных модулей содержит (фиг.2) одноразрядные сумматоры 3.1,3.т, блок из т-1 (тактируемых) элементов 4.1, 4 (т-1) задержки (первого уровня), блок из 2(т-1) (тактируемых) элементов 5.1.1 5.1 .2,5 (га-1) , 1., 5.(т-1).2, задержки (второго уровня), блок из ш (тактируемых) элементов 6.1,6.т задержки (третьего уровня)-, элементов И 7.1, 7.т. .

Информация во все элементы задержки принимается по переднему фронту синхросигнала.

Предлагаемое устройство выполняет операц;ию свертки По формуле

У„ ,Z1 а;х„.; ;

6 I Z:a;2

1 8 0

X

л - J

где а; - коэффициенты импульсной характеристики; входные данные; в-й разряд входного данного;

у„ - выходной отсчет. На вход устройства поразрядно поступают младшими разрядами вперед п-разрядные входные отсчеты ( ,

1-2 2 I о л тт

х 5о.,,Х;5 5С;, X, ) При ИХ умножении на km-разрядных коэффициентов импульсной характеристики получаем разрядность выходного результата n+m+jlog,k|. Для выравнивания разрядности входных отсчетов и получаемых результатов на вход устройства после подаем нулей

(,kГЧ . V . и ).

0

5

0

5

0

5

0

Для иллюстрации работы устройства рассмотрим случай, когда п 3, га 3, k 3. .

В начале работы все элементы задержки обнулены.

В первом такте работы на вход устройства подается младший разряд входного отсчета х°, а на второй вход каждого элемента И 7 - соответственно один разряд коэффициента импульсной характеристики а|, где k - номер коэффициента импульсной характеристики, m - номер разряда коэффициента импульсной характеристики. В этом же такте на элементе И 7.1 нулевого модуля 1.0 вычисляется произведение и суммируется на одноразрядном сумматоре 3.1 с нулем. Сумма х°а - О с выхода сумматора 3.1 поступает на вход первого элемента 5.1.1 задержки.

Во втором такте на вход устройства поступает следуюнщй разряд входного отсчета х, и принимается в элемент 5.1.1 задержки. На элементе И 7.1 вычисляется произведение , и на одноразрядном сумматоре 3.1 суммируется с нулем. На элемент И 7.2 поступает входной отсчет х° и вычисляется произведение х°а, которое суммируется на одноразрядном сумматоре 3.2 с нулем. Сумма с выхода сумматора 3.2 поступает на вход эле-, мента 5.2.1 задержки.

В третьем такте на выходах указанных элементов получаются следуюп1;ие результаты.

Нулевой модуль 1.0.

5

2 г,2

7. 1:

7.2: 7.3: х:а

ХрЗ

х а

ъ

}

ъ

3.1: 3.2; 3.3:

2 я2

xia

0;

+ х„а х°а 0.

3

в этом же такте входной отсчет х° поступает на первый вход модуля 1.1.

0

5

7.1: х

3.

+ О

0 г --. 1 . В четвертом такте на вход устройства в этом такте поступает нуль, а на выходах указанных элементов получаются следуюш 1е результаты. Нулевой модуль 1.0. 3.1: 0+0; 3.2: х2а;+ с , где с - перенос, возникающими при суммировании разрядов результата с свесом (1);

,+ х°а

Первый модуль 1.1,

3.1: х;а| + 0;

3.2: х°а; + 0.

В пятом такте на вход поступает ноль, а на выхных элементов получаются результаты.

Нулевой модуль 1.0.

3.1:0+0;

сз;

1а + с

3.2:

3.3: + х;а; +

Первый модуль 1.1.

3.1: х2а| + 0;15

3.2: + х°а + 0;

3.3: + 0.

Второй модуль 1.2.

3.1: + 0.

В шестом такте на вход устройства 20 оступает ноль, а на выходах указанных лементов получаются следующие реультаты.

Нулевой модуль 1.0.

3.1: 0+0;25

3.2: с + 0;

т ч- v2 я + Y я2 J. ,,2

J.J. + Xj.,a, + с . Первьм модуль 1.1. 3.1:0+0; 3.2:

,.а; + х а2 + с

3.3 + х;а;.

Второй модуль 1.2.

3.1: x af + 0;

3.2: х°а; + 0.

В седьмом такте на вход устройста поступает ноль, а на выходах укаанных элементов получаются следуюие результаты.

Нулевой модуль 1.0.

3.1: 0+0; 3.2: 0+0; 3.3: х1а + сз . Первый модуль 1.1. 3,1: 0+0;

35

40

10

30

-у Д

Xj,a

r2 ,

+ сз

х;а, +

й модуль 1.2.

х2а2 + 0;

х;а , +

х°а + 0.

х:а| + с

В восьмом такте на вход устройства поступает ноль, а на выходах, указанных элементов получаются следующие результаты.

Нулевой модуль 1.0.

3.1: 0+0;

3.2: 0+0;

3.3: с + с.

+ с2

5

0

5

5

0

5

0

5

Ь

0;

Первый модуль

3.1: О + 0;

3.2: с + 0; 3.3: + х:,а

Второй модуль 1.2.

3.1:О + 0;

3.2: + +

3.3: х ,а° + .

В девятом такте на вход устройства подается младший разряд следующего входного отсчета х .

Нулевой модуль 1.0.

3.1: х°а

3.2: О +

3.3: 0.

Первый модуль 1.1.

3.1:

3.2: 0+0;

а о. v - + гЗ J.J. -

Второй модуль 1.2. 3.1: О + 3.2: 3.3: + , Десятый такт. Нулевой модуль 1.0. 3.1: xi а2 + 0; 3.2: + 0; 3.3: 0+0.

0 Первый модуль 1.1. 3.1: 3.2: 0+0;

0;

+ сз

х1а; + х°а

x;a, + с

3

с + с

3.3:

Второй модуль 1.2.

3.1: 0+0;

3..2: с + 0;

3.3: + х;а2 + с

Одиннадцатый такт.

Нулевой модуль 1.0.

3.1; , +0;

т 9. J- -и-ОзЗ.

J./. + , 3.3: х°а° + 0. Первый модуль 1.1. 3.1: , + х;а; + 3,2: Klal + 0; 3,3: 0+0. Второй модуль 1.2. 3.1: x°ai + 0; 3.2: 0+0; 3.3: , + с . Двенадцатый такт. Нулевой модуль 1.0. 3.1; О + 0; 3„2:

3.3: х;а

х;а2 + сз

.

Первый модуль 1.1.

3.1: x|aj + х ,а| + xla + с ;

1 ) v° я + v я° + х°я

j.i. х,а т + XpSj, 3.3: 0+0.

5

Второй модуль 1.2.

3.1: х;а; + х°а;;

3.2: О + О;

3.3: с + с .

Тринадцатый такт.

Нулевой модуль 1.0.

3.1:0+0;

3.2: + с ;

3.3: , + + х°а

Перный модуль 1.1.

3.1: + + с

3.2: х;а1 + , + х а

3.3: х°,а1 + .

Второй модуль 1.2.3.1: +xiai + xla;+

3,2: + 0;

3.3: 0+0.

Четырнадцатый такт.

Нулевой модуль 1.0.

3.1: 0+0;

3.2: с + 0;

3.3: х2а; + + с.

Первый модуль 1.1.

3.1: с +

ЗЛ: х2а; +х2а; +х;а2 +x ,ai + с

3.3: х;а°, +х°а + + х°а; + с

Второй модуль 1.2.

т 1. v- p2 -(- v2o 4- Y p2 + „2 .

.5.1. х,а, + х.а -1- + с ,

3 9 . у я + v я ° 4- V ° я

3.3: 0+0.

Пятнадцатый такт.

Нулевой модуль 1.0.

3.1: О + 0;

3.2: 0+0;

3.3: + сз .

Первый модуль 1.1.

3.1: 0+0;

т 7 v2 а2 4. v2a2 4- /-3.

J.Z. x,a,j + х„а + с ,

3,3: + х|а , + + + х,а

Второй модуль 1.2.

3.1: х2а2 + ,, + с ;

3.2: xia; + + + + х:а

3.3: х°а +

Шестнадцатый такт.

Нулевой модуль 1.0.

3.1:0+0;

3.2: О + 0;

3.3: с/ + с .

Первый модуль 1.1.

3.1: 0+0;

3.2: с +

3.3: х,а; + х§а; + х + х .а, +

Второй модуль 1.2.

3.1: с + с ;

3.2: + а + + х ,а +

3.3: х;а° + х°а; + + +

j

5

5

0

5

0

5

0

Семиаддатьтй такт . Нулевой модуль 1.0. 3.1: х;а° + 0; 3.2: О + 0; 3.3: О + 0. Первый модуль 1.1. 3.1: + 0; 3.2: с + 0; 3.3: + Klal + с . Второй модуль 1.2. 3.1: О + 0;

3.2: х2а2 + + с ; 3.3: +х;а: + , + + , + х;а + с . Восемнадцатый такт. Нулевой модуль 1,0. 3.1: X 3.2: х;а,; 3.3: 0+0.

Первый модуль 1.1.

1

Ч

3.1: xia, + х°а;;

3.2: 0+0; 3.3: с + с. Второй модуль 1.2. 3,1: 0+0;

3.2: с +

3.3: +х;а2 + , + с2 .

Девятнадцатый такт.

Нулевой модуль 1,0.

-3 I . V-2 я2

J , I . ,, 3.2: х;а; + х°а2з; 3.3: х°а°з + 0. Первый модуль 1.1.

3.1: х°а2, + + х ,а; + , + c j 3.2: х°а + 0; 3.3: с + с . Второй модуль 1.2. 3.1: + 3.2: с + 0; 3.3: х2а2 + х2а2 + с ; Двадцатый такт. Нулевой модуль 1.0. 3.1: О + 0;

3.2: + + с ; 3.3: + х°а;„ Первый модуль 1.1. 3.1: + xfa; + xfa + с ; 3.2: + х .а; + ,; 3.3: 0+0. Второй модуль 1.2.

.1: al + + х ,а + + с°; 3.2: 0+0; 3.3: с + с. Двадцать первый такт. Нулевой модуль 1.0. 3.1:0+0; 3.2: + с ; 3.3: + , + , + с .

г(

3.2: у.а + + , +

К. а-.

10

Первый модуль 1.1. 3.1: + х2а2, + с ; 3 Л: + хХг + а° + xla , + 3.3: + х°аз 0. Второй модуль 1.2. 3.1: + + + х а х;а; + , + с ;

3 9 v°o° + V° Т°

J.Z. . т х„а, 3.3: с + с .

Двадцать второй такт. Нулевой модуль 1.0. 3.1: 0+0; 3.2: с- + 0;

3.3: х|а; + хХ + с .15

Первый модуль 1.1. . 3.1: с +

3.2: х2а + + , + xja +c2 3.3: х;а° + , + х;а , + . Вторрй модуль 1.2.20

3.1: + + + + X а + с

3.2: + xj а + х а , + +

+ г С S

3.3: с + 0.25

В двадцать третьем такте на выходе тройства сформируется нулевой разд полного выходного отсчета. В льнейшем проследим за формированитолько конечных результатов, так ЗО к работа вычислительных модулей 0 и 1.1 аналогична описанной.

Второй модуль 1.2.

3.1: х|а5 + + х|а| + с ;

3.2: , + х°а2 + х а° + х ,а 4 , + + + с + у.

3.3: х°а + + х°а;.

35

Б двадцать четвертом такте формиется первый разряд.

Второй модуль 1.2.40

3.1: с- +

J- v a2 J. -и- э -I- г-2«

+ x,aj с ,

iJ:

х ,а° + х°а; +

. я2

я2 4. ,-2

+ х;а; + , + с°.

В двадцать пятом тся второй разряд.

Второй модуль 1.2.

3.3: х|а° + + +х;а + х2а°з + х:,а +

В двадцать шестом ся третий разряд.

Второй модуль 1.2.

3.3: + +

+ , + х;а4 + с- .

В двадцать седьмом ется четвертый разряд Второй модуль 1..2. 3.3: х|а2, + +

В двш-щать BocbMiiM такте формируется пятый разряд.

Второй модуль 1.2.

3.3: с 4- с

В двадцать девятом такте формируется шестой разряд.

Второй модуль 1.2.

3.3: с + с- .

В тридцатом такте фop п pyeтcя седьмой, последний разряд полного выходного отсчета.

Второй модуль 1.2.

3.3: с ° + с

Вычисление седьмого разряда результата завершает цикл работы устройства, так как 1 n+m+Jlogj kL и при суммировании с + с никогда не возникает перенос. В 31 такте на выходе сумматора 3.3 модуля 1.2 происходит форм11рование нулевого разряда следующего выходного отсчета:

3.3: х,а° + х°а° + х

3

5

О

5

0

5

о

5

Формула изобретения

Последовательное устройство для цифровой фильтрации, содержащее k (где k - количество коэффициентов импульсной характеристики) вычислительных модулей, каждьп из .которых содержит m (т - разрядность коэффициентов импульсной характеристики) одноразрядных сумматоров, первый блок из т-1 элементов задержки, второй блок из 2(т-1) элементов задержки, третий блок из m элементов задержки, га элементов И, выход j-ro (j 1,m) элемента И подключен к первому входу j-ro одноразрядного сумматора, второй вход которого подключен к выходу третьего блока элементов задержки, вход которого подключен к выходу j-ro одноразрядного сумматора, второй вход j-ro элемента И является (j-f2)-M входом вычислительного модуля, вход первого элемента задержки первого блока является первым входом вычислительного модуля, выход i-ro (i 1,m-2) элемента задержки первого блока подключен к входу (i+1)-ro элемента задержки первого блока, при- чем первый выход 1-го (1 О, k-2) вычислительного модуля подключен к первому входу (1+1)-го вычислительного модуля, а первый вход нулевого вычислительного модуля является информационным входом устройства, тактовые входы всех элементов задержек первого, второго и третьего блоков соединены и яапяются тактовым входом устройства, отличающееся тем, что, с целью повышения производительности,, в него введен четвертый блок из (п+1+ + )-(k-l) (где п - разрядность входных данных) элементов задержки, причем второй выход 1-го вычислительного блока подключен к входу четвертого блока элементов задержки8 первый выход которого подключен к второму входу (1+1)-го вычислительного модуля, а второй в.ход нулевого вычислительного модуля является входом задания логического нуля устройства, второй выход (k-1)-ro вычислительного модуля является информационным выходом устройства, при этом в каждом вычислительном модуле первый вход

и

10

339874 О

первого элемента И является первым входом вычислительного модуля, первый вход q-ro (,m) элемента И подключен к выходу (q-l)-ro элемента задержки первого блока, а первый вход т-го элемента И подключен к первому выходу вычислительного модуля, первый выход -го (g 1,m-1) одноразрядного сумматора подключен к входу второго блока элементов задержки, выход которого подключен к третьему входу (g+1,)-ro одноразрядного сумматора, первый выход т-го одноразрядного сумматора является вторым выходом вычислительного модуля, а третий вход первого одноразрядного сумматора является вторым входом вычислительного модуля, а тактовые входы всех элементов задержки подключены к тактовому входу устройства.

15

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство умножения матрицы на вектор | 1984 |

|

SU1226484A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Устройство для цифровой фильтрации | 1987 |

|

SU1499374A1 |

| Цифровой фильтр | 1989 |

|

SU1693613A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1982 |

|

SU1086437A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1737441A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки радиолокационных, сейсмических, гидроакустических, видео и других сигналов. Целью изобретения является повьшение производительности. Поставленная цель достигается за счет того, что в состав устройства входит k вычислительных модулей I.O-l.(k-l) (k - число отсчетов импульсной характеристики) , блок из (n+l+log k) (k-1) (n - разрядность данных) элементов задержки 2.1-2.k-1.(n+log k +1) с соответствующими связями. 2 ил (Л 00 со со 00 4i сд,, 1

З.т

Редактор Л.Гратилло

Составитель А.Баранов Техред Л.Сердюкова

Заказ 4245/55Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35,, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Е.Рошко

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Peter R | |||

| Capello and Kenneth Steiglitz | |||

| Digital Signal Processing Applications of Systolic Algorithms | |||

| - VLSI Systems and Computations: H.T | |||

| Rung, R.F.Spronll and G.L.Stelle, Ir | |||

| Eds, Caruegic - Mellon University, Computer Science Press, Oct | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Льночесальная машина | 1923 |

|

SU245A1 |

Авторы

Даты

1987-09-23—Публикация

1986-05-20—Подача